Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | e200z4                                                                  |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 150MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 190                                                                     |

| Program Memory Size        | 4MB (4M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 192K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.14V ~ 1.32V                                                           |

| Data Converters            | A/D 40x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 324-BGA                                                                 |

| Supplier Device Package    | 324-PBGA (23x23)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc564a80b4cfay |

#### List of tables

| Table 49. | eQADC SSI timing characteristics (pads at 3.3 V or at 5.0 V) | 135 |

|-----------|--------------------------------------------------------------|-----|

| Table 50. | FlexCAN engine system clock divider threshold                | 136 |

| Table 51. | FlexCAN engine system clock divider                          | 136 |

| Table 52. | LQFP176 package mechanical data                              | 140 |

| Table 53. | LBGA208 mechanical data                                      | 141 |

| Table 54. | PBGA324 package mechanical data                              | 144 |

| Table 55. | Order codes                                                  | 145 |

| Table 56. | Revision history                                             | 147 |

**5**//

# **List of figures**

| Figure 1.  | SPC564A80 series block diagram                                                | 31  |

|------------|-------------------------------------------------------------------------------|-----|

| Figure 2.  | 176-pin LQFP pinout (top view)                                                |     |

| Figure 3.  | 208-pin LBGA package ballmap (viewed from above)                              | 36  |

| Figure 4.  | 324-pin PBGA package ballmap (northwest, viewed from above)                   | 37  |

| Figure 5.  | 324-pin PBGA package ballmap (southwest, viewed from above)                   | 38  |

| Figure 6.  | 324-pin PBGA package ballmap (northeast, viewed from above)                   | 39  |

| Figure 7.  | 324-pin PBGA package ballmap (southeast, viewed from above)                   | 40  |

| Figure 8.  | Core voltage regulator controller external components preferred configuration | 93  |

| Figure 9.  | Pad output delay                                                              |     |

| Figure 10. | Reset and Configuration Pin Timing                                            | 114 |

| Figure 11. | JTAG test clock input timing                                                  | 116 |

| Figure 12. | JTAG test access port timing                                                  | 116 |

| Figure 13. | JTAG JCOMP timing                                                             | 117 |

| Figure 14. | JTAG boundary scan timing                                                     | 118 |

| Figure 15. | Nexus output timing                                                           | 119 |

| Figure 16. | Nexus event trigger and test clock timings                                    | 120 |

| Figure 17. | Nexus TDI, TMS, TDO timing                                                    | 120 |

| Figure 18. | CLKOUT timing                                                                 |     |

| Figure 19. | Synchronous output timing                                                     | 124 |

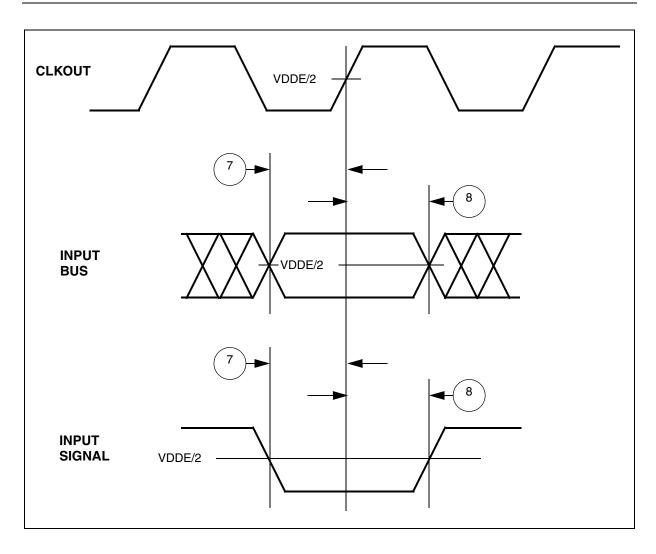

| Figure 20. | Synchronous input timing                                                      | 125 |

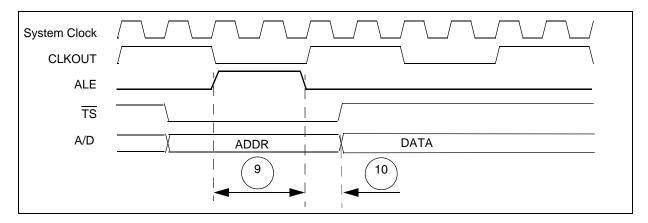

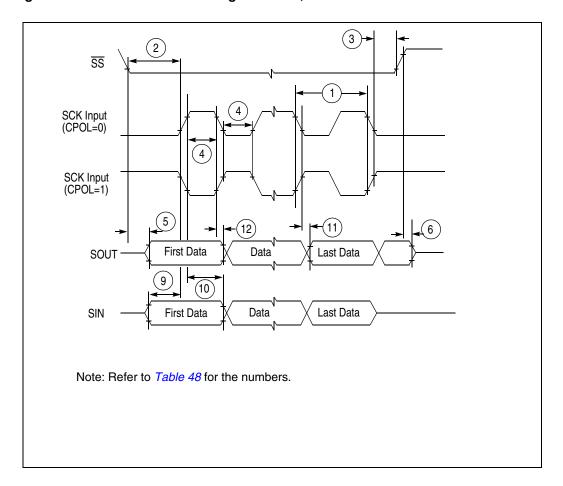

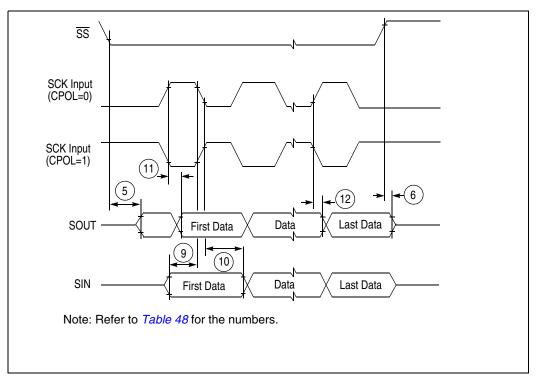

| Figure 21. | ALE signal timing                                                             | 125 |

| Figure 22. | External Interrupt Timing                                                     |     |

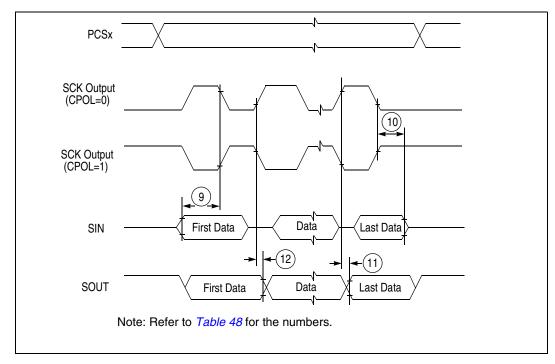

| Figure 23. | DSPI classic SPI timing — master, CPHA = 0                                    |     |

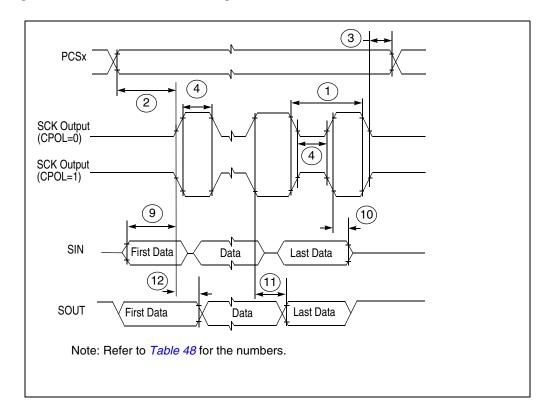

| Figure 24. | DSPI classic SPI timing — master, CPHA = 1                                    |     |

| Figure 25. | DSPI classic SPI timing — slave, CPHA = 0                                     |     |

| Figure 26. | DSPI classic SPI timing — slave, CPHA = 1                                     |     |

| Figure 27. | DSPI modified transfer format timing — master, CPHA = 0                       |     |

| Figure 28. | DSPI modified transfer format timing — master, CPHA = 1                       |     |

| Figure 29. | DSPI modified transfer format timing — slave, CPHA =0                         |     |

| Figure 30. | DSPI modified transfer format timing — slave, CPHA =1                         |     |

| Figure 31. | DSPI PCS strobe (PCSS) timing                                                 | 134 |

| Figure 32. | eQADC SSI timing                                                              |     |

| Figure 33. | LQFP176 package mechanical drawing                                            |     |

| Figure 34. | PBGA324 package mechanical drawing                                            | 143 |

| Figure 35  | Product code structure                                                        | 146 |

**577**

GPIO block provides uniform and discrete input/output control of the I/O pins of the MCU. The reset controller performs reset monitoring of internal and external reset sources, and drives the RSTOUT pin. Communication between the SIU and the e200z4 CPU core is via the crossbar switch. The SIU provides the following features:

- System configuration

- MCU reset configuration via external pins

- Pad configuration control for each pad

- Pad configuration control for virtual I/O via DSPI serialization

- System reset monitoring and generation

- Power-on reset support

- Reset status register provides last reset source to software

- Glitch detection on reset input

- Software controlled reset assertion

- External interrupt

- Rising or falling edge event detection

- Programmable digital filter for glitch rejection

- Critical Interrupt request

- Non-Maskable Interrupt request

- GPIO

- Centralized control of I/O and bus pins

- Virtual GPIO via DSPI serialization (requires external deserialization device)

- Dedicated input and output registers for setting each GPIO and Virtual GPIO pin

- Internal multiplexing

- Allows serial and parallel chaining of DSPIs

- Allows flexible selection of eQADC trigger inputs

- Allows selection of interrupt requests between external pins and DSPI

#### 1.5.8 Flash memory

The SPC564A80 provides up to 4 MB of programmable, non-volatile, flash memory. The non-volatile memory (NVM) can be used to store instructions or data, or both. The flash module includes a Fetch Accelerator that optimizes the performance of the flash array to match the CPU architecture. The flash module interfaces the system bus to a dedicated flash memory array controller. For CPU 'loads', DMA transfers and CPU instruction fetch, it supports a 64-bit data bus width at the system bus port, and 128- and 256-bit read data interfaces to flash memory. The module contains a prefetch controller which prefetches sequential lines of data from the flash array into the buffers. Prefetch buffer hits allow no-wait responses.

The flash memory provides the following features:

- Supports a 64-bit data bus for instruction fetch, CPU loads and DMA access. Byte, halfword, word and doubleword reads are supported. Only aligned word and doubleword writes are supported.

- Fetch Accelerator

- Architected to optimize the performance of the flash

- Configurable read buffering and line prefetch support

#### 1.5.17 FlexRay

The SPC564A80 includes one dual-channel FlexRay module that implements the FlexRay Communications System Protocol Specification, Version 2.1 Rev A. Features include:

- Single channel support

- FlexRay bus data rates of 10 Mbit/s, 8 Mbit/s, 5 Mbit/s, and 2.5 Mbit/s supported

- 128 message buffers, each configurable as:

- Receive message buffer

- Single buffered transmit message buffer

- Double buffered transmit message buffer (combines two single buffered message buffer)

- 2 independent receive FIFOs

- 1 receive FIFO per channel

- Up to 255 entries for each FIFO

- ECC support

### 1.5.18 System timers

The system timers include two distinct types of system timer:

- Periodic interrupts/triggers using the Periodic Interrupt Timer (PIT)

- Operating system task monitors using the System Timer Module (STM)

#### Periodic interrupt timer (PIT)

The PIT provides five independent timer channels, capable of producing periodic interrupts and periodic triggers. The PIT has no external input or output pins and is intended to provide system 'tick' signals to the operating system, as well as periodic triggers for eQADC queues. Of the five channels in the PIT, four are clocked by the system clock and one is clocked by the crystal clock. This one channel is also referred to as Real-Time Interrupt (RTI) and is used to wake up the device from low power stop mode.

The following features are implemented in the PIT:

- 5 independent timer channels

- Each channel includes 32-bit wide down counter with automatic reload

- 4 channels clocked from system clock

- 1 channel clocked from crystal clock (wake-up timer)

- Wake-up timer remains active when System STOP mode is entered; used to restart system clock after predefined time-out period

- Each channel optionally able to generate an interrupt request or a trigger event (to trigger eQADC queues) when timer reaches zero

#### System timer module (STM)

The System Timer Module (STM) is designed to implement the software task monitor as defined by AUTOSAR<sup>(b)</sup>. It consists of a single 32-bit counter, clocked by the system clock,

26/157 Doc ID 15399 Rev 9

b. AUTOSAR: AUTomotive Open System ARchitecture (see www.autosar.org)

and four independent timer comparators. These comparators produce a CPU interrupt when the timer exceeds the programmed value.

The following features are implemented in the STM:

- One 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

#### 1.5.19 Software watchdog timer (SWT)

The Software Watchdog Timer (SWT) is a second watchdog module to complement the standard Power Architecture watchdog integrated in the CPU core. The SWT is a 32-bit modulus counter, clocked by the system clock or the crystal clock, that can provide a system reset or interrupt request when the correct software key is not written within the required time window.

The following features are implemented:

- 32-bit modulus counter

- Clocked by system clock or crystal clock

- Optional programmable watchdog window mode

- Can optionally cause system reset or interrupt request on timeout

- Reset by writing a software key to memory mapped register

- Enabled out of reset

- Configuration is protected by a software key or a write-once register

### 1.5.20 Cyclic redundancy check (CRC) module

The CRC computing unit is dedicated to the computation of CRC off-loading the CPU. The CRC features:

- Support for CRC-16-CCITT (x25 protocol):

- $X^{16} + X^{12} + X^5 + 1$

- Support for CRC-32 (Ethernet protocol):

$$X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^{8} + X^{7} + X^{5} + X^{4} + X^{2} + X + 1$$

Zero wait states for each write/read operations to the CRC\_CFG and CRC\_INP registers at the maximum frequency

#### 1.5.21 Error correction status module (ECSM)

The ECSM provides a myriad of miscellaneous control functions regarding program-visible information about the platform configuration and revision levels, a reset status register, a software watchdog timer, wakeup control for exiting sleep modes, and information on platform memory errors reported by error-correcting codes and/or generic access error information for certain processor cores.

65/157

| Table 4. SPC564A80 signal properties (co | continued) |

|------------------------------------------|------------|

|------------------------------------------|------------|

|                                                                            |                                                                                | Р                     | PCR                      |            | 1/0                  | (5)                                                 | Sta           | tus <sup>(7)</sup> | Package pin # |     |      |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------|--------------------------|------------|----------------------|-----------------------------------------------------|---------------|--------------------|---------------|-----|------|

| Name                                                                       | Function <sup>(1)</sup>                                                        | A<br>G <sup>(2)</sup> | PA<br>Field<br>(3)       | PCR<br>(4) | I/O<br>Type          | Voltage <sup>(5)</sup> /<br>Pad Type <sup>(6)</sup> | During Reset  | After<br>Reset     | 176           | 208 | 324  |

| ETPUA30<br>DSPI_C_PCS[3]<br>ETPUA11_O <sup>(8)</sup><br>GPIO[144]          | eTPU A channel DSPI C peripheral chip select eTPU A channel (output only) GPIO | P<br>A1<br>A2<br>G    | 001<br>010<br>100<br>000 | 144        | I/O<br>O<br>O<br>I/O | VDDEH1<br>Medium                                    | — /<br>WKPCFG | — /<br>WKPCFG      | 22            | E1  | C1   |

| ETPUA31<br>DSPI_C_PCS[4]<br>ETPUA13_O <sup>(8)</sup><br>GPIO[145]          |                                                                                |                       | — /<br>WKPCFG            | 21         | E2                   | C2                                                  |               |                    |               |     |      |

|                                                                            | eMIOS                                                                          |                       |                          |            |                      |                                                     |               |                    |               |     |      |

| EMIOS0<br>ETPUA0_O <sup>(8)</sup><br>ETPUA25_O <sup>(8)</sup><br>GPIO[179] | eMIOS channel eTPU A channel (output only) eTPU A channel (output only) GPIO   | P<br>A1<br>A2<br>G    | 001<br>010<br>100<br>000 | 179        | I/O<br>O<br>O<br>I/O | VDDEH4<br>Slow                                      | — / Up        | — / Up             | 63            | T4  | AB10 |

| EMIOS1<br>ETPUA1_O <sup>(8)</sup><br>GPIO[180]                             | eMIOS channel<br>eTPU A channel (output only)<br>GPIO                          | P<br>A1<br>G          | 01<br>10<br>00           | 180        | I/O<br>O<br>I/O      | VDDEH4<br>Slow                                      | — / Up        | — / Up             | 64            | T5  | AB11 |

| EMIOS2<br>ETPUA2_O <sup>(8)</sup><br>RCH2_B<br>GPIO[181]                   | eMIOS channel eTPU A channel (output only) Reaction channel 2B GPIO            | P<br>A1<br>A2<br>G    | 001<br>010<br>100<br>000 | 181        | I/O<br>O<br>O<br>I/O | VDDEH4<br>Slow                                      | — / Up        | — / Up             | 65            | N7  | W12  |

| EMIOS3<br>ETPUA3_O <sup>(8)</sup><br>GPIO[182]                             | eMIOS channel<br>eTPU A channel (output only)<br>GPIO                          | P<br>A1<br>G          | 01<br>10<br>00           | 182        | I/O<br>O<br>I/O      | VDDEH4<br>Slow                                      | — /<br>WKPCFG | — /<br>WKPCFG      | 66            | R6  | AA11 |

| EMIOS4<br>ETPUA4_O <sup>(8)</sup><br>RCH2_C<br>GPIO[183]                   | eMIOS channel eTPU A channel (output only) Reaction channel 2C GPIO            | P<br>A1<br>A2<br>G    | 001<br>010<br>100<br>000 | 183        | I/O<br>O<br>O<br>I/O | VDDEH4<br>Slow                                      | — /<br>WKPCFG | — /<br>WKPCFG      | 67            | R5  | AB12 |

Table 4. SPC564A80 signal properties (continued)

|         |                         | Р                     | PCR                |            | I/O  | (5)                                                 | Sta          | tus <sup>(7)</sup> | Package pin #                                                                        |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                    |

|---------|-------------------------|-----------------------|--------------------|------------|------|-----------------------------------------------------|--------------|--------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name    | Function <sup>(1)</sup> | A<br>G <sup>(2)</sup> | PA<br>Field<br>(3) | PCR<br>(4) | Type | Voltage <sup>(5)</sup> /<br>Pad Type <sup>(6)</sup> | During Reset | After<br>Reset     | 176                                                                                  | 208                                                                                                                                                                                                   | 324                                                                                                                                                                                                                                                                                                |

| VDDEH7B | I/O Supply Input        | _                     |                    | _          | I    | 3.3 V - 5.0 V                                       | 1/—          | VDDEH7B            | 138                                                                                  | _                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                  |

| vss     | Ground                  | _                     |                    | _          | ı    | _                                                   | 1/—          | VSS                | 15,<br>29,<br>43,<br>57,<br>72,<br>90,<br>94,<br>96,<br>108,<br>115,<br>127,<br>133, | A1, A16,<br>B2, B15,<br>C3, C14,<br>D4, D13,<br>G7, G8,<br>G9,<br>G10,<br>H7, H8,<br>H9, H10,<br>J7, J8,<br>J9, J10,<br>K7,<br>K8, K9,<br>K10,<br>M16,<br>N4, N13,<br>P3, P14,<br>R2, R15,<br>T1, T16 | A1, A22, B2,<br>B21, C3, C20,<br>D4, D19, J9,<br>J10, J11, J12,<br>J13, K9, K10,<br>K11, K12,<br>K13, K14, L9,<br>L10, L11, L12,<br>L13, L14,<br>M11, M12,<br>M13, M14, N9,<br>N10, N12,<br>N13, N14, P9,<br>P10, P12,<br>P13, P14,<br>T21, T22,<br>W4,W19, Y3,<br>Y20, AA2,<br>AA21, AB1,<br>AB22 |

- 1. For each pin in the table, each line in the Function column is a separate function of the pin. For all I/O pins the selection of primary pin function or secondary function or GPIO is done in the SIU except where explicitly noted. See the Signal details table for a description of each signal.

- 2. The P/A/G column indicates the position a signal occupies in the muxing order for a pin—Primary, Alternate 1, Alternate 2, Alternate 3, or GPIO. Signals are selected by setting the PA field value in the appropriate PCR register in the SIU module. The PA field values are as follows: P 0b0001, A1 0b0010, A2 0b0100, A3 0b1000, or G 0b0000. Depending on the register, the PA field size can vary in length. For PA fields having fewer than four bits, remove the appropriate number of leading zeroes from these values.

- 3. The Pad Configuration Register (PCR) PA field is used by software to select pin function.

- 4. Values in the PCR No. column refer to registers in the System Integration Unit (SIU). The actual register name is "SIU\_PCR" suffixed by the PCR number. For example, PCR[190] refers to the SIU register named SIU\_PCR190.

- 5. The VDDE and VDDEH supply inputs are broken into segments. Each segment of slow I/O pins (VDDEH) may have a separate supply in the 3.3 V to 5.0 V range (-10%/+5%). Each segment of fast I/O (VDDE) may have a separate supply in the 1.8 V to 3.3 V range (+/- 10%).

- 6. See Table 5 for details on pad types.

- 7. The Status During Reset pin is sampled after the internal POR is negated. Prior to exiting POR, the signal has a high impedance. Terminology is O output, I input, Up weak pull up enabled, Down weak pull down enabled, Low output driven low, High output driven high. A dash for the function in this column denotes that both the input and output buffer are turned off. The signal name to the left or right of the slash indicates the pin is enabled.

- 8. Output only.

- 9. When used as ETRIG, this pin must be configured as an input. For GPIO it can be configured either as an input or output.

- 10. Maximum frequency is 50 kHz.

- 11. The SIU\_PCR219 register is unusual in that it controls pads for two separate device pins: GPIO[219] and MCKO. See the SPC564A80 Microcontroller Reference Manual (SIU chapter) for details.

- 12. Multivoltage pads are automatically configured in low swing mode when a JTAG or Nexus function is selected, otherwise they are high swing.

- 13. On LQFP176 and LBGA208 packages, this pin is tied low internally.

- 14. Nexus multivoltage pads default to 5 V operation until the Nexus module is enabled.

- 15. EVTO should be clamped to 3.3 V to prevent possible damage to external tools that only support 3.3 V.

- 16. Do not connect pin directly to a power supply or ground.

- 17. This signal name is used to support legacy naming.

- 18. During and just after POR negates, internal pull resistors can be enabled, resulting in as much as 4 mA of current draw. The pull resistors are disabled when the system clock propagates through the device.

- 19. For pins AN12-AN15, if the analog features are used the VDDEH7 input pins should be tied to VDDA because that segment must meet the VDDA specification to support analog input function.

- 20. Do not use VRC33 to drive external circuits.

- 21. VDDA0 and VDDA1 are shorted together internally in BGA packages. In the QFP package the two pads are double bonded on one pin called VDDA.

- 22. VSSA0 and VSSA1 are shorted together internally in BGA packages. In the QFP package the two pads are double bonded on one pin called VSSA.

- 23. VDDE2 and VDDE3 are shorted together in all production packages.

- 24. VDDE2 and VDDE3 are shorted together in all production packages.

- 25. VDDEH1A, VDDEH1B, and VDDEH1AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

- 26. VDDEH4, VDDEH4B, and VDDEH4B are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

- 27. VDDEH6, VDDEH6A, VDDEH6B, and VDDEH6AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

Table 6. Signal details (continued)

| Signal                           | Module or Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD_WR                            | EBI                | RD_WR indicates whether the current transaction is a read access or a write access.                                                                                                                                                                                                                                                                                                                                                 |

| TĀ                               | EBI                | $\overline{\text{TA}}$ is asserted to indicate that the slave has received the data (and completed the access) for a write cycle, or returned data for a read cycle. If the transaction is a burst read, $\overline{\text{TA}}$ is asserted for each one of the transaction beats. For write transactions, $\overline{\text{TA}}$ is only asserted once at access completion, even if more than one write data beat is transferred. |

| TS                               | EBI                | The Transfer Start signal (TS) is asserted by the SPC564A80 to indicate the start of a transfer.                                                                                                                                                                                                                                                                                                                                    |

| WE[2:3]                          | EBI                | Write enables are used to enable program operations to a particular memory. WE[2:3] are only asserted for write accesses                                                                                                                                                                                                                                                                                                            |

| WE[0:3]/BE[0:3]                  | EBI                | Write enables are used to enable program operations to a particular memory. These signals can also be used as byte enables for read and write operation by setting the WEBS bit in the appropriate EBI Base Register (EBI_BRn). WE[0:3] are only asserted for write accesses. BE[0:3] are asserted for both read and write accesses                                                                                                 |

| eMIOS[0:23]                      | eMIOS              | eMIOS I/O channels                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AN[0:39]                         | eQADC              | Single-ended analog inputs for analog-to-digital converter                                                                                                                                                                                                                                                                                                                                                                          |

| FCK                              | eQADC              | eQADC free running clock for eQADC SSI.                                                                                                                                                                                                                                                                                                                                                                                             |

| MA[0:2]                          | eQADC              | These three control bits are output to enable the selection for an external Analog Mux for expansion channels.                                                                                                                                                                                                                                                                                                                      |

| REFBYPC                          | eQADC              | Bypass capacitor input                                                                                                                                                                                                                                                                                                                                                                                                              |

| SDI                              | eQADC              | Serial data in                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SDO                              | eQADC              | Serial data out                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SDS                              | eQADC              | Serial data select                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VRH                              | eQADC              | Voltage reference high input                                                                                                                                                                                                                                                                                                                                                                                                        |

| VRL                              | eQADC              | Voltage reference low input                                                                                                                                                                                                                                                                                                                                                                                                         |

| SCI_A_RX<br>SCI_B_RX<br>SCI_C_RX | eSCI_A - eSCI_C    | eSCI receive                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SCI_A_TX<br>SCI_B_TX<br>SCI_C_TX | eSCI_A - eSCI_C    | eSCI transmit                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ETPU_A[0:31]                     | eTPU               | eTPU I/O channel                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                  | ·                  | •                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Table 6. Signal details (continued)

| Signal                                                                                                                                | Module or Function           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĪRQ[0:5]<br>ĪRQ[7:15]                                                                                                                 | SIU - External<br>Interrupts | The IRQ[0:15] pins connect to the SIU IRQ inputs. IMUX Select Register 1 is used to select the IRQ[0:15] pins as inputs to the IRQs.  See the SPC564A80 Microcontroller Reference Manual for more information.                                                                                                                                                                                                                                                                                                                                                                                               |

| NMI                                                                                                                                   | SIU - External<br>Interrupts | Non-Maskable Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GPIO[0:3]<br>GPIO[8:43]<br>GPIO[62:65]<br>GPIO[68:70]<br>GPIO[75:145]<br>GPIO[179:204]<br>GPIO[208:213]<br>GPIO[219]<br>GPIO[244:245] | SIU - GPIO                   | Configurable general purpose I/O pins. Each GPIO input and output is separately controlled by an 8-bit input (GPDI) or output (GPDO) register. Additionally, each GPIO pins is configured using a dedicated SIU_PCR register.  The GPIO pins are generally multiplexed with other I/O pin functions.  See The SPC564A80 Microcontroller Reference Manual for more information.                                                                                                                                                                                                                               |

| RESET                                                                                                                                 | SIU - Reset                  | The RESET pin is an active low input. The RESET pin is asserted by an external device during a power-on or external reset. The internal reset signal asserts only if the RESET pin asserts for 10 clock cycles. Assertion of the RESET pin while the device is in reset causes the reset cycle to start over.  The RESET pin has a glitch detector which detects spikes greater than two clock cycles in duration that fall below the switch point of the input buffer logic of the VDDEH input pins. The switch point lies between the maximum VIL and minimum VIH specifications for the VDDEH input pins. |

| RSTCFG                                                                                                                                | SIU - Reset                  | Used to enable or disable the PLLREF and the BOOTCFG[0:1] configuration signals.  0:Get configuration information from BOOTCFG[0:1] and PLLREF  1:Use default configuration of booting from internal flash with crystal clock source  For the 176-pin QFP and 208-ball BGA packages RSTCFG is always 0, so PLLREF and BOOTCFG signals are used.                                                                                                                                                                                                                                                              |

| RSTOUT                                                                                                                                | SIU - Reset                  | The RSTOUT pin is an active low output that uses a push/pull configuration. The RSTOUT pin is driven to the low state by the MCU for all internal and external reset sources. There is a delay between initiation of the reset and the assertion of the RSTOUT pin.                                                                                                                                                                                                                                                                                                                                          |

<sup>1.</sup> Do not connect pin directly to a power supply or ground.

78/157 Doc ID 15399 Rev 9

board. This model can be used to generate simple estimations and for computational fluid dynamics (CFD) thermal models.

To determine the junction temperature of the device in the application on a prototype board, use the thermal characterization parameter ( $\Psi_{JT}$ ) to determine the junction temperature by measuring the temperature at the top center of the package case using the following equation:

#### Equation 4 $T_J = T_T + (\Psi_{JT} \times P_D)$

where:

$T_T$  = thermocouple temperature on top of the package ( ${}^{\circ}$ C)

$\Psi_{JT}$  = thermal characterization parameter ( ${}^{\circ}C/W$ )

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured in compliance with the JESD51-2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. Position the thermocouple so that the thermocouple junction rests on the package. Place a small amount of epoxy on the thermocouple junction and approximately 1 mm of wire extending from the junction. Place the thermocouple wire flat against the package case to avoid measurement errors caused by the cooling effects of the thermocouple wire.

#### References:

Semiconductor Equipment and Materials International

3081 Zanker Road San Jose, CA 95134 USA (408) 943-6900

MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at 800-854-7179 or 303-397-7956.

JEDEC specifications are available on the WEB at http://www.jedec.org.

- C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47-54.

- G. Kromann, S. Shidore, and S. Addison, "Thermal Modeling of a PBGA for Air-Cooled Applications", Electronic Packaging and Production, pp. 53-58, March 1998.

- B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212-220.

## 3.9 I/O pad current specifications

The power consumption of an I/O segment depends on the usage of the pins on a particular segment. The power consumption is the sum of all output pin currents for a particular segment. The output pin current can be calculated from *Table 22* based on the voltage, frequency, and load on the pin. Use linear scaling to calculate pin currents for voltage, frequency, and load parameters that fall outside the values given in *Table 22*.

Table 22. I/O pad average I<sub>DDE</sub> specifications<sup>(1)</sup>

| Pad Type                         | Symbol                    |    | С | Period<br>(ns) | Load <sup>(2)</sup><br>(pF) | V <sub>DDE</sub><br>(V) | Drive/Slew<br>Rate Select | I <sub>DDE</sub> Avg<br>(mA) <sup>(3)</sup> | I <sub>DDE</sub> RMS<br>(mA) |

|----------------------------------|---------------------------|----|---|----------------|-----------------------------|-------------------------|---------------------------|---------------------------------------------|------------------------------|

|                                  |                           | CC | D | 37             | 50                          | 5.5                     | 11                        | 9                                           | _                            |

| Slow                             | I                         | CC | D | 130            | 50                          | 5.5                     | 01                        | 2.5                                         | _                            |

| Slow                             | I <sub>DRV_SSR_HV</sub>   | CC | D | 650            | 50                          | 5.5                     | 00                        | 0.5                                         | _                            |

|                                  |                           | СС | D | 840            | 200                         | 5.5                     | 00                        | 1.5                                         | _                            |

|                                  |                           | C  | D | 24             | 50                          | 5.5                     | 11                        | 14                                          | _                            |

| Medium                           | <br>                      | C  | D | 62             | 50                          | 5.5                     | 01                        | 5.3                                         | _                            |

| Mediaiii                         | I <sub>DRV_MSR_HV</sub>   | СС | D | 317            | 50                          | 5.5                     | 00                        | 1.1                                         | _                            |

|                                  |                           | C  | D | 425            | 200                         | 5.5                     | 00                        | 3                                           | _                            |

|                                  |                           | C  | D | 10             | 50                          | 3.6                     | 11                        | 22.7                                        | 68.3                         |

|                                  |                           | C  | D | 10             | 30                          | 3.6                     | 10                        | 12.1                                        | 41.1                         |

|                                  |                           | CC | D | 10             | 20                          | 3.6                     | 01                        | 8.3                                         | 27.7                         |

| Fast                             | lany so                   | CC | D | 10             | 10                          | 3.6                     | 00                        | 4.44                                        | 14.3                         |

| 1 431                            | I <sub>DRV_FC</sub>       | C  | D | 10             | 50                          | 1.98                    | 11                        | 12.5                                        | 31                           |

|                                  |                           | СС | D | 10             | 30                          | 1.98                    | 10                        | 7.3                                         | 18.6                         |

|                                  |                           | СС | D | 10             | 20                          | 1.98                    | 01                        | 5.42                                        | 12.6                         |

|                                  |                           | СС | D | 10             | 10                          | 1.98                    | 00                        | 2.84                                        | 6.4                          |

| N // IA:\ /                      |                           | C  | D | 20             | 50                          | 5.5                     | 11                        | 9                                           |                              |

| MultiV<br>(High                  | 1                         | СС | D | 30             | 50                          | 5.5                     | 01                        | 6.1                                         | _                            |

| Swing<br>Mode)                   | IDRV_MULTV_HV             | CC | D | 117            | 50                          | 5.5                     | 00                        | 2.3                                         | _                            |

|                                  |                           | СС | D | 212            | 200                         | 5.5                     | 00                        | 5.8                                         | _                            |

| MultiV<br>(Low<br>Swing<br>Mode) | I <sub>DRV_MULTV_HV</sub> | CC | D | 30             | 30                          | 5.5                     | 11                        | 3.4                                         | _                            |

<sup>1.</sup> Numbers from simulations at best case process, 150 °C.

<sup>2.</sup> All loads are lumped.

<sup>3.</sup> Average current is for pad configured as output only.

- f<sub>VCQ</sub> self clock range is 20–150 MHz. f<sub>SCM</sub> represents f<sub>SYS</sub> after PLL output divider (ERFD) of 2 through 16 in enhanced mode.

- 6. This value is determined by the crystal manufacturer and board design.

- Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>SYS</sub>.

Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via V<sub>DDPLL</sub> and V<sub>SSPLL</sub> and variation in crystal oscillator frequency increase the C<sub>JITTER</sub> percentage for a given interval.

- 8. Proper PC board layout procedures must be followed to achieve specifications.

- Values are with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of C<sub>JITTER</sub> and either f<sub>CS</sub> or f<sub>DS</sub> (depending on whether center spread or down spread modulation is enabled).

- 10. This value is determined by the crystal manufacturer and board design. For 4 MHz to 40 MHz crystals specified for this PLL, load capacitors should not exceed these limits.

- 11. Proper PC board layout procedures must be followed to achieve specifications.

- 12. This parameter is guaranteed by design rather than 100% tested.

- 13.  $V_{IHEXT}$  cannot exceed  $V_{RC33}$  in external reference mode.

- 14. This specification applies to the period required for the PLL to relock after changing the MFD frequency control bits in the synthesizer control register (SYNCR).

- 15. Modulation depth will be attenuated from depth setting when operating at modulation frequencies above 50 kHz.

## 3.11 Temperature sensor electrical characteristics

Table 27. Temperature sensor electrical characteristics

| Symbo | N.         | С | Parameter Conditions         |                                |     | Unit    |     |       |

|-------|------------|---|------------------------------|--------------------------------|-----|---------|-----|-------|

| Symbo | <i>,</i> 1 | ) | Parameter                    | Conditions                     | min | typical | max | Oille |

| _     | СС         | С | Temperature monitoring range |                                | -40 | _       | 150 | °C    |

| _     | СС         | С | Sensitivity                  |                                | _   | 6.3     | _   | mV/°C |

| _     | СС         | Р | Accuracy                     | T <sub>J</sub> = -40 to 150 °C | -10 |         | 10  | °C    |

#### 3.12 eQADC electrical characteristics

Table 28. eQADC conversion specifications (operating)

| Sum                | Symbol C |   | Parameter                              | Va   | Unit   |              |

|--------------------|----------|---|----------------------------------------|------|--------|--------------|

| Syli               | iboi     |   | raiametei                              | min  | max    |              |

| f <sub>ADCLK</sub> | SR       | _ | ADC clock (ADCLK) frequency            | 2    | 16     | MHz          |

| CC                 | CC       | D | Conversion cycles                      | 2+13 | 128+14 | ADCLK cycles |

| T <sub>SR</sub>    | CC       | С | Stop mode recovery time <sup>(1)</sup> | _    | 10     | μS           |

| f <sub>ADCLK</sub> | SR       | _ | ADC clock (ADCLK) frequency            | 2    | 16     | mV           |

<sup>1.</sup> Stop mode recovery time is the time from the setting of either of the enable bits in the ADC Control Register to the time that the ADC is ready to perform conversions. Delay from power up to full accuracy = 8 ms.

106/157 Doc ID 15399 Rev 9

## 3.13 Configuring SRAM wait states

Use the SWSC field in the ECSM\_MUDCR register to specify an additional wait state for the device SRAM. By default, no wait state is added.

Table 31. Cutoff frequency for additional SRAM wait state

| (1) | SWSC Value |

|-----|------------|

| 98  | 0          |

| 153 | 1          |

<sup>1.</sup> Max frequencies including 2% PLL FM.

Please see the device reference manual for details.

#### 3.14 Platform flash controller electrical characteristics

Table 32. APC, RWSC, WWSC settings vs. frequency of operation<sup>(1),(2)</sup>

| Max. Flash Operating<br>Frequency (MHz) <sup>(3)</sup> | APC <sup>(4)</sup> | RWSC <sup>(4)</sup> | wwsc |

|--------------------------------------------------------|--------------------|---------------------|------|

| 20 MHz                                                 | 0b000              | 0b000               | 0b11 |

| 61 MHz                                                 | 0b001              | 0b001               | 0b11 |

| 90 MHz                                                 | 0b010              | 0b010               | 0b11 |

| 123 MHz                                                | 0b011              | 0b011               | 0b11 |

| 153 MHz                                                | 0b100              | 0b100               | 0b11 |

APC, RWSC and WWSC are fields in the flash memory BIUCR register used to specify wait states for address pipelining and read/write accesses. Illegal combinations exist—all entries must be taken from the same row.

## 3.15 Flash memory electrical characteristics

Table 33. Flash program and erase specifications<sup>(1)</sup>

| # | Symbol                  |    | С | Parameter                                 | Min.<br>Value | Typical<br>Value | Initial<br>Max <sup>(2)</sup> | Max <sup>(3)</sup> | Unit |

|---|-------------------------|----|---|-------------------------------------------|---------------|------------------|-------------------------------|--------------------|------|

| 1 | T <sub>dwprogram</sub>  | СС | Р | Double Word (64 bits) Program Time        | _             | 45               | _                             | 500                | μS   |

| 2 | T <sub>pprogram</sub>   | ОО | Р | Page Program Time                         | _             | 55               | 160 <sup>(4)</sup>            | 500                | μS   |

| 3 | T <sub>16kpperase</sub> | ОО | Р | 16 KB Block Pre-program and Erase<br>Time | _             | 300              | 1000                          | 5000               | ms   |

<sup>2.</sup> TBD: To Be Defined.

<sup>3.</sup> Max frequencies including 2% PLL FM.

<sup>4.</sup> APC must be equal to RWSC.

Figure 20. Synchronous input timing

Figure 21. ALE signal timing

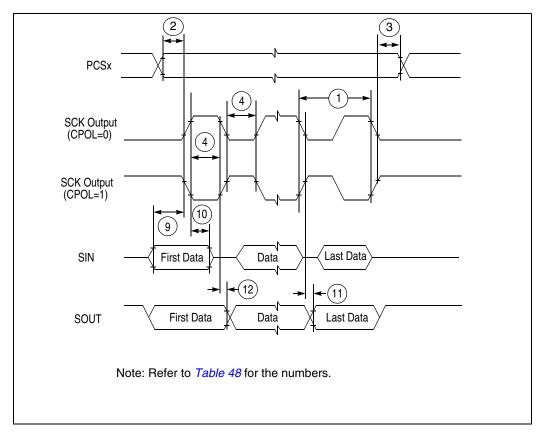

- 3. The minimum DSPI Cycle Time restricts the baud rate selection for given system clock rate. These numbers are calculated based on two SPC564A80 devices communicating over a DSPI link.

- 4. The actual minimum SCK cycle time is limited by pad performance.

- For DSPI channels using LVDS output operation, up to 40 MHz SCK cycle time is supported. For non-LVDS output, maximum SCK frequency is 20 MHz. Appropriate clock division must be applied.

- 6. The maximum value is programmable in DSPI\_CTARx[PSSCK] and DSPI\_CTARx[CSSCK].

- 7. Timing met when pcssck = 3(01), and cssck = 2(0000).

- 8. The maximum value is programmable in DSPI\_CTARx[PASC] and DSPI\_CTARx[ASC].

- 9. Timing met when ASC = 2 (0000), and PASC = 3 (01).

- 10. Timing met when pcssck = 3.

- 11. Timing met when ASC = 3.

- 12. This number is calculated assuming the SMPL\_PT bitfield in DSPI\_MCR is set to 0b10.

Figure 23. DSPI classic SPI timing — master, CPHA = 0

Figure 24. DSPI classic SPI timing — master, CPHA = 1

Figure 25. DSPI classic SPI timing — slave, CPHA = 0

Figure 26. DSPI classic SPI timing — slave, CPHA = 1

## 6 Document revision history

Table 56. Revision history

| Date        | Revision | Changes                                                                   |

|-------------|----------|---------------------------------------------------------------------------|

| 23-Feb-2009 | 1        | Initial release                                                           |

|             |          | Maximum device speed is 145 MHz (was 150 MHz)                             |

|             |          | 16-entry Memory Protection Unit (MPU). Was incorrectly listed as 8-entry. |

|             |          | 288-ball BGA package deleted                                              |

|             |          | Feature details section added                                             |

|             |          | Changes to signal summary table:                                          |

|             |          | - Added ANY function to AN[10]                                            |

|             |          | - Added ANW function to AN[8]                                             |

|             |          | Changes to 208 ball BGA ballmap:                                          |

|             |          | - A12 is AN12-SDS (was AN12)                                              |

|             |          | - A15 is VRC33 (was VDD33)                                                |

|             |          | - B12 is AN13-SDO (was AN13)                                              |

|             |          | - C12 is AN14SDI (was AN14)                                               |

|             |          | - C13 is AN15-FCK (was AN15)                                              |

|             |          | - D1 is VRC33 (was VDD33)                                                 |

|             |          | - F13 is VDDEH6AB (was VDDEH6)                                            |

|             |          | - H13 is GPIO99 (was PCSA3)                                               |

|             |          | - J15 is GPIO98 (was PCSA2)                                               |

|             |          | - K4 is now VDDEH1AB (was VDDEH1)                                         |

|             |          | - N6 is now VRC33 (was VDD33)                                             |

| 9-Dec-2009  | 2        | - N9 is VDDEH4AB (was VDDEH4)                                             |

|             |          | - N12 is now VRC33 (was VDD33)                                            |

|             |          | - P6 is now NC                                                            |

|             |          | - T13 is VDDE5 (was NC)                                                   |

|             |          | Changes to 324 ball BGA ballmap:                                          |

|             |          | - A6 is VDDA (was VDDA1)                                                  |

|             |          | - A7 is VSSA (was VSSA1)                                                  |

|             |          | - A15 is VSSA (was VSSA0)                                                 |

|             |          | - A16 is AN12_SDS (was AN12)                                              |

|             |          | - A17 is MDO11_ETPUA29O (was MDO11)                                       |

|             |          | - A18 is MDO10_ETPUA27O (was MDO10)                                       |

|             |          | - A19 is MDO8_ETPUA21O (was MDO8)                                         |

|             |          | - A21 is VRC33 (was VDD33)                                                |

|             |          | - B1 is VRC33 (was VDD33)                                                 |

|             |          | - B15 is VSSA (was VSSA0)                                                 |

|             |          | - B16 is AN13_SDO (was AN13)                                              |

|             |          | - B17 is MDO9_ETPUA25O (was MDO9)                                         |

|             |          | - B18 is MDO7_ETPUA19O (was MDO7)                                         |

|             |          | - B19 is MDO4_ETPUA2O (was MDO4)                                          |

|             |          | - B22 is NIC (was VDDE7)                                                  |

|             | 1        | l '                                                                       |

Table 56. Revision history (continued)

| Date                  | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10-Feb-2011<br>(cont) | 5 (cont) | Added DATA[0:15] to V <sub>DDE5</sub> in the "signal properties" table.  Updated VSTBY parameters in the "Power/ground segmentation" table.  Updated the parameter symbols and classifications throughout the document.  Updated footnote instances in the "Absolute maximum ratings" table.  Removed I <sub>MAXA</sub> footnote in the "Absolute Maximum Ratings" table.  Updated the footnote on V <sub>DDEG</sub> in the "Power management control (PMC) and power on reset (POR) electrical specifications" table.  Updated values for Vbg, Idd3p3, Por3.3V_r, Por3.3V_f, Por5V_r, and Por5V_f in the "PMC electrical characteristics" table.  Updated "Bandgap reference supply voltage variation" in the "PMC Electrical Characteristics" table.  Updated "Bandgap reference supply voltage variation" in the "PMC Electrical Characteristics" table.  Removed the "VRC electrical specifications" table as it contained redundant information.  Updated VCE <sub>SAT</sub> and V <sub>BE</sub> in the "Recommended power transistors" operating characteristics" table.  Updated VI <sub>LLS</sub> in the "DC electrical specifications" table.  Updated the V <sub>OH, LS</sub> min value in the "DC electrical specifications" table.  Updated the I <sub>DDS</sub> TBY and I <sub>DDS</sub> TBY150 in the "DC electrical specifications" table.  Updated the I <sub>DDS</sub> TBY and I <sub>DDS</sub> TBY150 in the "DC electrical specifications" table.  Updated Medium pad type I <sub>DD33</sub> values in the "I/O pad V <sub>RC33</sub> average I <sub>DDE</sub> specifications" table.  Updated Medium pad type I <sub>DD33</sub> values in the "I/O pad V <sub>RC33</sub> average I <sub>DDE</sub> specifications" table.  Updated values for V <sub>OD</sub> in the "DSPI LVDS pad specifications" table.  Removed the redundant "XTAL Load Capacitance" parameter instance from the "PLLMRFM electrical specifications" table.  Removed the rotnotes in the "PLLMRFM electrical specifications" table.  Updated values for OFFNC and GAINNC in the "eQADC conversion specifications (operating)" table.  Added DIFF <sub>max</sub> , DIFF <sub>max2</sub> , DIFF <sub>max4</sub> , and DIFF <sub>cmv</sub> parameters to the "eQADC conversion specifications (operating)" table.  Added the maximum operating frequency values in the "Cuto |