Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | e200z4                                                                  |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 190                                                                     |

| Program Memory Size        | 4MB (4M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 192K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.14V ~ 1.32V                                                           |

| Data Converters            | A/D 40x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 324-BGA                                                                 |

| Supplier Device Package    | 324-PBGA (23x23)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc564a80b4cfby |

- Four-entry 256-bit wide line read buffer

- Prefetch controller

- Hardware and software configurable read and write access protections on a per-master basis

- Interface to the flash array controller pipelined with a depth of one, allowing overlapped accesses to proceed in parallel for interleaved or pipelined flash array designs

- Configurable access timing usable in a wide range of system frequencies

- Multiple-mapping support and mapping-based block access timing (0-31 additional cycles) usable for emulation of other memory types

- Software programmable block program/erase restriction control

- Erase of selected block(s)

- Read page size of 128 bits (four words)

- ECC with single-bit correction, double-bit detection

- Program page size of 128 bits (four words) to accelerate programming

- ECC single-bit error corrections are visible to software

- Minimum program size is two consecutive 32-bit words, aligned on a 0-modulo-8 byte address, due to ECC

- Embedded hardware program and erase algorithm

- Erase suspend, program suspend and erase-suspended program

- Shadow information stored in non-volatile shadow block

- Independent program/erase of the shadow block

#### 1.5.9 BAM

The BAM (Boot Assist Module) is a block of read-only memory that is programmed once by ST and is identical for all SPC564A80 MCUs. The BAM program is executed every time the MCU is powered-on or reset in normal mode. The BAM supports different modes of booting. They are:

- Booting from internal flash memory

- Serial boot loading (A program is downloaded into RAM via eSCI or the FlexCAN and then executed)

- Booting from external memory on external bus

The BAM also reads the reset configuration half word (RCHW) from internal flash memory and configures the SPC564A80 hardware accordingly. The BAM provides the following features:

- Sets up MMU to cover all resources and mapping of all physical addresses to logical addresses with minimum address translation

- Sets up MMU to allow user boot code to execute as either Power Architecture embedded category (default) or as VLE code

- Location and detection of user boot code

- Automatic switch to serial boot mode if internal flash is blank or invalid

- Supports user programmable 64-bit password protection for serial boot mode

- Supports serial bootloading via FlexCAN bus and eSCI using standard protocol

- Supports serial bootloading via FlexCAN bus and eSCI with auto baud rate sensing

- Supports serial bootloading of either Power Architecture code (default) or VLE code

- SPRAM shared between host CPU and eTPU2, supporting communication either between channels and host or inter-channel

- Hardware implementation of four semaphores support coherent parameter sharing between both eTPU engines

- Dual-parameter coherency hardware support allows atomic access to two parameters by host

- Test and development support features:

- Nexus Class 1 debug, supporting single-step execution, arbitrary microinstruction execution, hardware breakpoints and watchpoints on several conditions

- Software breakpoints

- SCM continuous signature-check built-in self test (MISC multiple input signature calculator), runs concurrently with eTPU2 normal operation

### 1.5.12 Reaction module

The reaction module provides the ability to modulate output signals to manage closed loop control without CPU assistance. It works in conjunction with the eQADC and eTPU2 to increase system performance by removing the CPU from the current control loop.

The reaction module has the following features:

- Six reaction channels

- Each channel output is a bus of three signals, providing ability to control 3 inputs.

- Each channel can implement a peak and hold waveform, making it possible to implement up to six independent peak and hold control channels

Target applications include solenoid control for direct injection systems and valve control in automatic transmissions

#### 1.5.13 eQADC

The enhanced queued analog to digital converter (eQADC) block provides accurate and fast conversions for a wide range of applications. The eQADC provides a parallel interface to two on-chip analog to digital converters (ADC), and a single master to single slave serial interface to an off-chip external device. Both on-chip ADCs have access to all the analog channels.

The eQADC prioritizes and transfers commands from six command conversion command 'queues' to the on-chip ADCs or to the external device. The block can also receive data from the on-chip ADCs or from an off-chip external device into the six result queues, in parallel, independently of the command queues. The six command queues are prioritized with Queue\_0 having the highest priority and Queue\_5 the lowest. Queue\_0 also has the added ability to bypass all buffering and queuing and abort a currently running conversion on either ADC and start a Queue\_0 conversion. This means that Queue\_0 will always have a deterministic time from trigger to start of conversion, irrespective of what tasks the ADCs were performing when the trigger occurred. The eQADC supports software and external hardware triggers from other blocks to initiate transfers of commands from the queues to the on-chip ADCs or to the external device. It also monitors the fullness of command queues and result queues, and accordingly generates DMA or interrupt requests to control data movement between the queues and the system memory, which is external to the eQADC.

The ADCs also support features designed to allow the direct connection of high impedance acoustic sensors that might be used in a system for detecting engine knock. These features

include differential inputs; integrated variable gain amplifiers for increasing the dynamic range; programmable pull-up and pull-down resistors for biasing and sensor diagnostics.

The eQADC also integrates a programmable decimation filter capable of taking in ADC conversion results at a high rate, passing them through a hardware low pass filter, then down-sampling the output of the filter and feeding the lower sample rate results to the result FIFOs. This allows the ADCs to sample the sensor at a rate high enough to avoid aliasing of out-of-band noise; while providing a reduced sample rate output to minimize the amount DSP processing bandwidth required to fully process the digitized waveform.

The eQADC provides the following features:

- Dual on-chip ADCs

- 2 × 12-bit ADC resolution

- Programmable resolution for increased conversion speed (12-bit, 10-bit, 8-bit)

- 12-bit conversion time: 938 ns (1 M sample/sec)

- 10-bit conversion time: 813 ns (1.2 M sample/second)

- 8-bit conversion time: 688 ns (1.4 M sample/second)

- Up to 10-bit accuracy at 500 KSample/s and 8-bit accuracy at 1 MSample/s

- Differential conversions

- Single-ended signal range from 0 to 5 V

- Variable gain amplifiers on differential inputs (×1, ×2, ×4)

- Sample times of 2 (default), 8, 64 or 128 ADC clock cycles

- Provides time stamp information when requested

- Allows time stamp information relative to eTPU clock sources, such as an angle clock

- Parallel interface to eQADC CFIFOs and RFIFOs

- Supports both right-justified unsigned and signed formats for conversion results

- 40 single-ended input channels, expandable to 56 channels with external multiplexers (supports four external 8-to-1 muxes)

- 8 channels can be used as 4 pairs of differential analog input channels

- Differential channels include variable gain amplifier for improved dynamic range

- Differential channels include programmable pull-up and pull-down resistors for biasing and sensor diagnostics (200 k $\Omega$ , 100 k $\Omega$ , 5 k $\Omega$ )

- Additional internal channels for monitoring voltages (such as core voltage, I/O voltage, LVI voltages, etc.) inside the device

- An internal bandgap reference to allow absolute voltage measurements

- Silicon die temperature sensor

- Provides temperature of silicon as an analog value

- Read using an internal ADC analog channel

- May be read with either ADC

- 2 Decimation Filters

- Programmable decimation factor (1 to 16)

- Selectable IIR or FIR filter

- Up to 4th order IIR or 8th order FIR

- Programmable coefficients

5//

The FlexCAN modules provide the following features:

- Full Implementation of the CAN protocol specification, Version 2.0B

- Standard data and remote frames

- Extended data and remote frames

- Zero to eight bytes data length

- Programmable bit rate up to 1 Mbit/s

- Content-related addressing

- 64 message buffers of zero to eight bytes data length

- Individual Rx Mask Register per message buffer

- Each message buffer configurable as Rx or Tx, all supporting standard and extended messages

- Includes 1088 bytes of embedded memory for message buffer storage

- Includes 256-byte memory for storing individual Rx mask registers

- Full featured Rx FIFO with storage capacity for six frames and internal pointer handling

- Powerful Rx FIFO ID filtering, capable of matching incoming IDs against 8 extended, 16 standard or 32 partial (8 bits) IDs, with individual masking capability

- Selectable backwards compatibility with previous FlexCAN versions

- Programmable clock source to the CAN Protocol Interface, either system clock or oscillator clock

- Listen only mode capability

- Programmable loop-back mode supporting self-test operation

- 3 programmable Mask Registers

- Programmable transmit-first scheme: lowest ID, lowest buffer number or highest priority

- Time Stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Warning interrupts when the Rx and Tx Error Counters reach 96

- Independent of the transmission medium (an external transceiver is assumed)

- Multi-master concept

- High immunity to EMI

- Short latency time due to an arbitration scheme for high-priority messages

- Low power mode, with programmable wake-up on bus activity

The Error Correction Status Module supports a number of miscellaneous control functions for the platform. The ECSM includes these features:

- Registers for capturing information on platform memory errors if error-correcting codes (ECC) are implemented

- For test purposes, optional registers to specify the generation of double-bit memory errors are enabled on the SPC564A80.

The sources of the ECC errors are:

- Flash

- SRAM

- Peripheral RAM (FlexRay, CAN, eTPU2 Parameter RAM)

## 1.5.22 External bus interface (EBI)

The SPC564A80 device features an external bus interface that is available in PBGA324 and calibration packages.

The EBI supports operation at frequencies of system clock /1, /2 and /4, with a maximum frequency support of 80 MHz. Customers running the device at 120 MHz or 132 MHz will use the /2 divider, giving an EBI frequency of 60 MHz or 66 MHz. Customers running the device at 80 MHz will be able to use the /1 divider to have the EBI run at the full 80 MHz frequency.

#### Features include:

- 1.8 V to 3.3 V ± 10% I/O (1.6 V to 3.6 V)

- Memory controller with support for various memory types

- 16-bit data bus, up to 22-bit address bus

- Pin muxing included to support 32-bit muxed bus

- Selectable drive strength

- Configurable bus speed modes

- Bus monitor

- Configurable wait states

#### 1.5.23 Calibration EBI

The Calibration EBI controls data transfer across the crossbar switch to/from memories or peripherals attached to the calibration tool connector in the calibration address space. The Calibration EBI is only available in the calibration tool.

#### Features include:

- 1.8 V to 3.3 V ± 10% I/O (1.6 V to 3.6 V)

- Memory controller supports various memory types

- 16-bit data bus, up to 22-bit address bus

- Pin muxing supports 32-bit muxed bus

- Selectable drive strength

- Configurable bus speed modes

- Bus monitor

- Configurable wait states

577

### 1.5.24 Power management controller (PMC)

The power management controller contains circuitry to generate the internal 3.3 V supply and to control the regulation of 1.2 V supply with an external NPN ballast transistor. It also contains low voltage inhibit (LVI) and power-on reset (POR) circuits for the 1.2 V supply, the 3.3 V supply, the 3.3 V/5 V supply of the closest I/O segment (VDDEH1) and the 5 V supply of the regulators (VDDREG).

## 1.5.25 Nexus port controller

The NPC (Nexus Port Controller) block provides real-time Nexus Class3+ development support capabilities for the SPC564A80 Power Architecture-based MCU in compliance with the IEEE-ISTO 5001-2003 and 2010 standards. MDO port widths of 4 pins and 12 pins are available in all packages.

#### 1.5.26 JTAG

The JTAGC (JTAG Controller) block provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode. Testing is performed via a boundary scan technique, as defined in the IEEE 1149.1-2001 standard. All data input to and output from the JTAGC block is communicated in serial format. The JTAGC block is compliant with the IEEE 1149.1-2001 standard and supports the following features:

- IEEE 1149.1-2001 Test Access Port (TAP) interface 4 pins (TDI, TMS, TCK, and TDO)

- A 5-bit instruction register that supports the following IEEE 1149.1-2001 defined instructions:

- BYPASS, IDCODE, EXTEST, SAMPLE, SAMPLE/PRELOAD, HIGHZ, CLAMP

- A 5-bit instruction register that supports the additional following public instructions:

- ACCESS AUX TAP NPC

- ACCESS AUX TAP ONCE

- ACCESS\_AUX\_TAP\_eTPU

- ACCESS CENSOR

- 3 test data registers to support JTAG Boundary Scan mode

- Bypass register

- Boundary scan register

- Device identification register

- A TAP controller state machine that controls the operation of the data registers, instruction register and associated circuitry

- Censorship Inhibit Register

- 64-bit Censorship password register

- If the external tool writes a 64-bit password that matches the Serial Boot password stored in the internal flash shadow row, Censorship is disabled until the next system reset.

## 1.5.27 Development Trigger Semaphore (DTS)

SPC564A80 devices include a system development feature, the Development Trigger Semaphore (DTS) module, that enables software to signal an external tool by driving a persistent (affected only by reset or an external tool) signal on an external device pin. There

# 2 Pinout and signal description

This section contains the pinouts for all production packages for the SPC564A80 family of devices.

Caution:

Any pins labeled "NC" are to be left unconnected. Any connection to an external circuit or voltage may cause unpredictable device behavior or damage.

# 2.2 LBGA208 ballmap

Figure 3. 208-pin LBGA package ballmap (viewed from above)

|   | 1       | 2       | 3       | 4        | 5       | 6       | 7                      | 8       | 9                       | 10                      | 11                     | 12       | 13                 | 14              | 15              | 16              |   |

|---|---------|---------|---------|----------|---------|---------|------------------------|---------|-------------------------|-------------------------|------------------------|----------|--------------------|-----------------|-----------------|-----------------|---|

| Α | VSS     | AN9     | AN11    | VDDA1    | VSSA1   | AN1     | AN5                    | VRH     | VRL                     | AN27                    | VSSA0                  | AN12-SDS | MDO2               | MDO0            | VRC33           | VSS             | А |

| В | VDD     | VSS     | AN8     | AN21     | AN0     | AN4     | REFBYPC                | AN22    | AN25                    | AN28                    | VDDA0                  | AN13-SDO | MDO3               | MDO1            | VSS             | VDD             | В |

| С | VSTBY   | VDD     | VSS     | AN17     | AN34    | AN16    | AN3                    | AN7     | AN23                    | AN32                    | AN33                   | AN14-SDI | AN15-FCK           | VSS             | MSEO0           | TCK             | С |

| D | VRC33   | AN39    | VDD     | VSS      | AN18    | AN2     | AN6                    | AN24    | AN30                    | AN31                    | AN35                   | VDDEH7   | VSS                | TMS             | EVTO            | NC              | D |

| Ε | ETPUA30 | ETPUA31 | AN37    | VDD      |         |         |                        |         |                         |                         |                        |          | NC                 | TDI             | EVTI            | MSEO1           | E |

| F | ETPUA28 | ETPUA29 | ETPUA26 | AN36     |         |         |                        |         |                         |                         |                        |          | VDDEH6AB           | TDO             | мско            | JCOMP           | F |

| G | ETPUA24 | ETPUA27 | ETPUA25 | ETPUA21  |         |         | VSS                    | VSS     | VSS                     | VSS                     |                        |          | DSPI_B_<br>SOUT    | DSPI_B_<br>PCS3 | DSPI_B_<br>SIN  | DSPI_B_<br>PCS0 | G |

| Н | ETPUA23 | ETPUA22 | ETPUA17 | ETPUA18  |         |         | VSS                    | VSS     | VSS                     | VSS                     |                        |          | GPIO99             | DSPI_B_<br>PCS4 | DSPI_B_<br>PCS2 | DSPI_B_<br>PCS1 | н |

| J | ETPUA20 | ETPUA19 | ETPUA14 | ETPUA13  |         |         | VSS                    | VSS     | VSS                     | VSS                     |                        |          | DSPI_B_<br>PCS5    | SCI_A_TX        | GPIO98          | DSPI_B_<br>SCK  | J |

| K | ETPUA16 | ETPUA15 | ETPUA7  | VDDEH1AB |         |         | VSS                    | VSS     | VSS                     | VSS                     |                        |          | CAN_C_TX           | SCI_A_R<br>X    | RSTOUT          | VDDREG          | к |

| L | ETPUA12 | ETPUA11 | ETPUA6  | TCRCLKA  |         |         |                        |         |                         |                         | •                      |          | SCI_B_TX           | CAN_C_<br>RX    | WKPCFG          | RESET           | L |

| М | ETPUA10 | ETPUA9  | ETPUA1  | ETPUA5   |         |         |                        |         |                         |                         |                        |          | SCI_B_RX           | PLLREF          | BOOTCFG1        | VSS             | М |

| N | ETPUA8  | ETPUA4  | ETPUA0  | VSS      | VDD     | VRC33   | EMIOS2                 | EMIOS10 | VDDEH4AB                | EMIOS12                 | MDO7_<br>ETPUA19_<br>O | VRC33    | VSS <sup>(1)</sup> | VRCCTL          | NC              | EXTAL           | N |

| Р | ETPUA3  | ETPUA2  | VSS     | VDD      | GPIO207 | NC      | EMIOS6                 | EMIOS8  | MDO11_<br>ETPUA29_<br>O | MDO4_<br>ETPUA2_O       | MDO8_<br>ETPUA21_<br>O | CAN_A_TX | VDD                | VSS             | NC              | XTAL            | Р |

| R | NC      | VSS     | VDD     | GPIO206  | EMIOS4  | EMIOS3  | EMIOS9                 | EMIOS11 | EMIOS14                 | MDO10_<br>ETPUA27_<br>O | EMIOS23                | CAN_A_RX | CAN_B_RX           | VDD             | VSS             | VDDPLL          | R |

| Т | VSS     | VDD     | NC      | EMIOS0   | EMIOS1  | GPIO219 | MDO9_<br>ETPUA25_<br>O | EMIOS13 | EMIOS15                 | MDO5_<br>ETPUA4_O       | MDO6_<br>ETPUA13_<br>O | CAN_B_TX | VDDE5              | ENGCLK          | VDD             | VSS             | Т |

|   | 1       | 2       | 3       | 4        | 5       | 6       | 7                      | 8       | 9                       | 10                      | 11                     | 12       | 13                 | 14              | 15              | 16              | • |

<sup>1.</sup> This pin (N13) should be tied low.

Doc ID 15399 Rev 9

2.3

PBGA324 ballmap

Н

ETPUA16

ETPUA12

ETPUA8

ETPUA4

ETPUA15

ETPUA11

ETPUA7

ETPUA3

ETPUA10

ETPUA6

ETPUA2

ETPUA0

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

|   | 1       | 2       | 3       | 4       | 5    | 6          | 7     | 8           | 9    | 10      | 11   |

|---|---------|---------|---------|---------|------|------------|-------|-------------|------|---------|------|

| А | VSS     | VDD     | VSTBY   | AN37    | AN11 | VDDA0      | VSSA0 | AN1         | AN5  | VRH     | VRL  |

| В | VRC33   | VSS     | VDD     | AN36    | AN39 | AN19       | AN16  | AN0         | AN4  | REFBYPC | AN23 |

| С | ETPUA30 | ETPUA31 | VSS     | VDD     | AN38 | AN17       | AN20  | AN21        | AN3  | AN7     | AN22 |

| D | ETPUA28 | ETPUA29 | ETPUA26 | VSS     | VDD  | AN8<br>ANW | AN9   | AN10<br>ANY | AN18 | AN2     | AN6  |

| E | ETPUA24 | ETPUA27 | ETPUA25 | ETPUA21 |      |            |       |             |      |         |      |

| F | ETPUA23 | ETPUA22 | ETPUA17 | ETPUA18 |      |            |       |             |      |         |      |

| G | ETPUA20 | ETPUA19 | ETPUA14 | ETPUA13 |      |            |       |             |      |         |      |

Figure 4. 324-pin PBGA package ballmap (northwest, viewed from above)

VDDEH1AB

ETPUA9

ETPUA5

ETPUA1

47/157

|                                                                          |                                                                               | Р                     | PCR               |            |                 | (5)                                                 | Sta          | tus <sup>(7)</sup> |     | Packag | e pin # |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------|-------------------|------------|-----------------|-----------------------------------------------------|--------------|--------------------|-----|--------|---------|

| Name                                                                     | Function <sup>(1)</sup>                                                       | A<br>G <sup>(2)</sup> | Field<br>(3)      | PCR<br>(4) | I/O<br>Type     | Voltage <sup>(5)</sup> /<br>Pad Type <sup>(6)</sup> | During Reset | After<br>Reset     | 176 | 208    | 324     |

| BDIP<br>GPIO[63]                                                         | External burst data in progress GPIO                                          | P<br>G                | 01<br>00          | 63         | O<br>I/O        | VDDE2<br>Fast                                       | — / Up       | — / Up             | _   | _      | M1      |

| WE[0]/BE[0]<br>GPIO[64]                                                  | External write/byte enable GPIO                                               | P<br>G                | 01<br>00          | 64         | O<br>I/O        | VDDE2<br>Fast                                       | — / Up       | — / Up             | _   | _      | N4      |

| WE[1]/BE[1]<br>GPIO[65]                                                  | External write/byte enable GPIO                                               | P<br>G                | 01<br>00          | 65         | O<br>I/O        | VDDE2<br>Fast                                       | — / Up       | — / Up             | _   | _      | N3      |

| OE<br>GPIO[68]                                                           | External output enable GPIO                                                   | P<br>G                | 01<br>00          | 68         | O<br>I/O        | VDDE2<br>Fast                                       | — / Up       | — / Up             | _   | _      | AB9     |

| TS<br>ALE<br>GPIO[69]                                                    | External transfer start Address latch enable GPIO[69]                         | P<br>A1<br>G          | 001<br>010<br>000 | 69         | I/O<br>O<br>I/O | VDDE2<br>Fast                                       | — / Up       | — / Up             | _   | _      | T4      |

| TA<br>TS <sup>(8)</sup><br>GPIO[70]                                      | External transfer acknowledge External transfer start GPIO                    | P<br>A1<br>G          | 001<br>010<br>000 | 70         | I/O<br>O<br>I/O | VDDE2<br>Fast                                       | — / Up       | — / Up             | _   | _      | R4      |

|                                                                          |                                                                               |                       |                   |            | Calibra         | tion Bus                                            |              |                    |     |        | •       |

| CAL_CS0                                                                  | Calibration chip select                                                       | Р                     | 01                | 336        | 0               | VDDE12<br>Fast                                      |              | -/-                | _   | _      | _       |

| CAL_ <u>CS2</u><br>CAL_ADDR[10]<br>CAL_ <u>WE</u> [2]/ <u>BE</u> [2]     | Calibration chip select Calibration address bus Calibration write/byte enable | P<br>A<br>A2          | 001<br>010<br>100 | 338        | 0<br>I/O<br>0   | VDDE12<br>Fast                                      |              | -/-                | _   | _      | _       |

| CAL_ <del>CS3</del><br>CAL_ADDR[11]<br>CAL_ <u>WE[</u> 3]/ <u>BE</u> [3] | Calibration chip select Calibration address bus Calibration write/byte enable | P<br>A<br>A2          | 001<br>010<br>100 | 339        | 0<br>I/O<br>0   | VDDE12<br>Fast                                      |              | -/-                | _   | _      | _       |

| CAL_ADDR[12]<br>CAL_WE[2]/BE[2]                                          | Calibration address bus Calibration write/byte enable                         | P<br>A                | 01<br>10          | 340        | I/O<br>O        | VDDE12<br>Fast                                      |              | -/-                | _   | _      | _       |

| CAL_ADDR[13]                                                             | Calibration address bus                                                       | Р                     | 01                | 340        | I/O             | VDDE12                                              |              | —/—                |     | _      | _       |

0

10

Fast

CAL\_WE[3]/BE[3]

Calibration write/byte enable

Table 4. SPC564A80 signal properties (continued)

|                                             |                                                                        | Р                     | PCR                |            | 1/0             | (E) .                                               | Sta          | tus <sup>(7)</sup> |     | Packag | e pin # |

|---------------------------------------------|------------------------------------------------------------------------|-----------------------|--------------------|------------|-----------------|-----------------------------------------------------|--------------|--------------------|-----|--------|---------|

| Name                                        | Function <sup>(1)</sup>                                                | A<br>G <sup>(2)</sup> | PA<br>Field<br>(3) | PCR<br>(4) | I/O<br>Type     | Voltage <sup>(5)</sup> /<br>Pad Type <sup>(6)</sup> | During Reset | After<br>Reset     | 176 | 208    | 324     |

| DSPI_B_SOUT<br>DSPI_C_PCS[5]<br>GPIO[104]   | DSPI B data output<br>DSPI C peripheral chip select<br>GPIO            | P<br>A1<br>G          | 01<br>10<br>00     | 104        | O<br>O<br>I/O   | VDDEH6<br>Medium                                    | — / Up       | — / Up             | 113 | G13    | J19     |

| DSPI_B_PCS[0]<br>DSPI_D_PCS[2]<br>GPIO[105] | DSPI B peripheral chip select<br>DSPI D peripheral chip select<br>GPIO | P<br>A1<br>G          | 01<br>10<br>00     | 105        | I/O<br>O<br>I/O | VDDEH6<br>Medium                                    | — / Up       | — / Up             | 111 | G16    | J21     |

| DSPI_B_PCS[1]<br>DSPI_D_PCS[0]<br>GPIO[106] | DSPI B peripheral chip select<br>DSPI D peripheral chip select<br>GPIO | P<br>A1<br>G          | 01<br>10<br>00     | 106        | O<br>I/O<br>I/O | VDDEH6<br>Medium                                    | — / Up       | — / Up             | 109 | H16    | J22     |

| DSPI_B_PCS[2]<br>DSPI_C_SOUT<br>GPIO[107]   | DSPI B peripheral chip select<br>DSPI C data output<br>GPIO            | P<br>A1<br>G          | 01<br>10<br>00     | 107        | O<br>O<br>I/O   | VDDEH6<br>Medium                                    | — / Up       | — / Up             | 107 | H15    | K22     |

| DSPI_B_PCS[3]<br>DSPI_C_SIN<br>GPIO[108]    | DSPI B peripheral chip select<br>DSPI C data input<br>GPIO             | P<br>A1<br>G          | 01<br>10<br>00     | 108        | O<br>I<br>I/O   | VDDEH6<br>Medium                                    | — / Up       | — / Up             | 114 | G14    | J20     |

| DSPI_B_PCS[4]<br>DSPI_C_SCK<br>GPIO[109]    | DSPI B peripheral chip select<br>SPI clock pin for DSPI module<br>GPIO | P<br>A1<br>G          | 01<br>10<br>00     | 109        | O<br>I/O<br>I/O | VDDEH6<br>Medium                                    | — / Up       | — / Up             | 105 | H14    | K20     |

| DSPI_B_PCS[5]<br>DSPI_C_PCS[0]<br>GPIO[110] | DSPI B peripheral chip select<br>DSPI C peripheral chip select<br>GPIO | P<br>A1<br>G          | 01<br>10<br>00     | 110        | O<br>I/O<br>I/O | VDDEH6<br>Medium                                    | — / Up       | — / Up             | 104 | J13    | L19     |

|                                             |                                                                        |                       |                    |            | eQ              | ADC                                                 |              |                    |     |        |         |

| AN0 <sup>(18)</sup><br>DAN0+                | Single Ended Analog Input<br>Positive Terminal Diff. Input             | Р                     | _                  | _          | l<br>I          | VDDA<br>Analog                                      | 1/—          | AN[0] / —          | 172 | B5     | B8      |

| AN1 <sup>(18)</sup><br>DAN0-                | Single Ended Analog Input<br>Negative Terminal Diff. Input             | Р                     | _                  | _          | l<br>I          | VDDA<br>Analog                                      | 1/—          | AN[1] / —          | 171 | A6     | A8      |

| AN2 <sup>(18)</sup><br>DAN1+                | Single Ended Analog Input<br>Positive Terminal Diff. Input             | Р                     | _                  | _          | l<br>I          | VDDA<br>Analog                                      | 1/—          | AN[2] / —          | 170 | D6     | D10     |

Doc ID 15399 Rev 9

65/157

| Table 4. SPC564A80 signal properties (co | continued) |

|------------------------------------------|------------|

|------------------------------------------|------------|

|                                                                            |                                                                                | Р                     | PCR                      |            | 1/0                  | (E) .                                               | Status <sup>(7)</sup> |                |     | Packag | je pin # |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------|--------------------------|------------|----------------------|-----------------------------------------------------|-----------------------|----------------|-----|--------|----------|

| Name                                                                       | Function <sup>(1)</sup>                                                        | A<br>G <sup>(2)</sup> | PA<br>Field<br>(3)       | PCR<br>(4) | I/O<br>Type          | Voltage <sup>(5)</sup> /<br>Pad Type <sup>(6)</sup> | During Reset          | After<br>Reset | 176 | 208    | 324      |

| ETPUA30<br>DSPI_C_PCS[3]<br>ETPUA11_O <sup>(8)</sup><br>GPIO[144]          | eTPU A channel DSPI C peripheral chip select eTPU A channel (output only) GPIO | P<br>A1<br>A2<br>G    | 001<br>010<br>100<br>000 | 144        | I/O<br>O<br>O<br>I/O | VDDEH1<br>Medium                                    | — /<br>WKPCFG         | — /<br>WKPCFG  | 22  | E1     | C1       |

| ETPUA31<br>DSPI_C_PCS[4]<br>ETPUA13_O <sup>(8)</sup><br>GPIO[145]          | eTPU A channel DSPI C peripheral chip select eTPU A channel (output only) GPIO | P<br>A1<br>A2<br>G    | 001<br>010<br>100<br>000 | 145        | I/O<br>O<br>O<br>I/O | VDDEH1<br>Medium                                    | — /<br>WKPCFG         | — /<br>WKPCFG  | 21  | E2     | C2       |

|                                                                            |                                                                                |                       |                          |            | eM                   | IOS                                                 |                       |                |     |        |          |

| EMIOS0<br>ETPUA0_O <sup>(8)</sup><br>ETPUA25_O <sup>(8)</sup><br>GPIO[179] | eMIOS channel eTPU A channel (output only) eTPU A channel (output only) GPIO   | P<br>A1<br>A2<br>G    | 001<br>010<br>100<br>000 | 179        | I/O<br>O<br>O<br>I/O | VDDEH4<br>Slow                                      | — / Up                | — / Up         | 63  | T4     | AB10     |

| EMIOS1<br>ETPUA1_O <sup>(8)</sup><br>GPIO[180]                             | eMIOS channel<br>eTPU A channel (output only)<br>GPIO                          | P<br>A1<br>G          | 01<br>10<br>00           | 180        | I/O<br>O<br>I/O      | VDDEH4<br>Slow                                      | — / Up                | — / Up         | 64  | T5     | AB11     |

| EMIOS2<br>ETPUA2_O <sup>(8)</sup><br>RCH2_B<br>GPIO[181]                   | eMIOS channel eTPU A channel (output only) Reaction channel 2B GPIO            | P<br>A1<br>A2<br>G    | 001<br>010<br>100<br>000 | 181        | I/O<br>O<br>O<br>I/O | VDDEH4<br>Slow                                      | — / Up                | — / Up         | 65  | N7     | W12      |

| EMIOS3<br>ETPUA3_O <sup>(8)</sup><br>GPIO[182]                             | eMIOS channel<br>eTPU A channel (output only)<br>GPIO                          | P<br>A1<br>G          | 01<br>10<br>00           | 182        | I/O<br>O<br>I/O      | VDDEH4<br>Slow                                      | — /<br>WKPCFG         | — /<br>WKPCFG  | 66  | R6     | AA11     |

| EMIOS4<br>ETPUA4_O <sup>(8)</sup><br>RCH2_C<br>GPIO[183]                   | eMIOS channel eTPU A channel (output only) Reaction channel 2C GPIO            | P<br>A1<br>A2<br>G    | 001<br>010<br>100<br>000 | 183        | I/O<br>O<br>O<br>I/O | VDDEH4<br>Slow                                      | — /<br>WKPCFG         | — /<br>WKPCFG  | 67  | R5     | AB12     |

Table 4. SPC564A80 signal properties (continued)

|                                                            |                                                                            | P                     | PCR                      |            | 1/0                  | (E) .                                               | Sta           | tus <sup>(7)</sup> |     | Packag | e pin # |

|------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------|--------------------------|------------|----------------------|-----------------------------------------------------|---------------|--------------------|-----|--------|---------|

| Name                                                       | Function <sup>(1)</sup>                                                    | A<br>G <sup>(2)</sup> | PA<br>Field<br>(3)       | PCR<br>(4) | I/O<br>Type          | Voltage <sup>(5)</sup> /<br>Pad Type <sup>(6)</sup> | During Reset  | After<br>Reset     | 176 | 208    | 324     |

| EMIOS13<br>DSPI_D_SOUT<br>GPIO[192]                        | eMIOS channel<br>DSPI D data output<br>GPIO                                | P<br>A1<br>G          | 01<br>10<br>00           | 192        | I/O<br>O<br>I/O      | VDDEH4<br>Medium                                    | — /<br>WKPCFG | — /<br>WKPCFG      | 77  | Т8     | AA14    |

| EMIOS14<br>IRQ[0]<br>ETPUA29_O <sup>(8)</sup><br>GPIO[193] | eMIOS channel External interrupt request eTPU A channel (output only) GPIO | P<br>A1<br>A2<br>G    | 001<br>010<br>100<br>000 | 193        | I/O<br>I<br>O<br>I/O | VDDEH4<br>Slow                                      | — / Down      | — / Down           | 78  | R9     | AB15    |

| EMIOS15<br>   TRQ[1]<br>   GPIO[194]                       | eMIOS channel External interrupt request GPIO                              | P<br>A1<br>G          | 01<br>10<br>00           | 194        | I/O<br>I<br>I/O      | VDDEH4<br>Slow                                      | — / Down      | — / Down           | 79  | Т9     | Y14     |

| EMIOS16<br>GPIO[195]                                       | eMIOS channel<br>GPIO                                                      | P<br>G                | 01<br>00                 | 195        | I/O<br>I/O           | VDDEH4<br>Slow                                      | — / Up        | — / Up             | _   | _      | AA15    |

| EMIOS17<br>GPIO[196]                                       | eMIOS channel<br>GPIO                                                      | P<br>G                | 01<br>00                 | 196        | I/O<br>I/O           | VDDEH4<br>Slow                                      | — / Up        | — / Up             | _   | _      | Y15     |

| EMIOS18<br>GPIO[197]                                       | eMIOS channel<br>GPIO                                                      | P<br>G                | 01<br>00                 | 197        | I/O<br>I/O           | VDDEH4<br>Slow                                      | — / Up        | — / Up             | _   | _      | AB16    |

| EMIOS19<br>GPIO[198]                                       | eMIOS channel<br>GPIO                                                      | P<br>G                | 01<br>00                 | 198        | I/O<br>I/O           | VDDEH4<br>Slow                                      | — /<br>WKPCFG | — /<br>WKPCFG      | _   | _      | AA16    |

| EMIOS20<br>GPIO[199]                                       | eMIOS channel<br>GPIO                                                      | P<br>G                | 01<br>00                 | 199        | I/O<br>I/O           | VDDEH4<br>Slow                                      | — /<br>WKPCFG | — /<br>WKPCFG      | _   | _      | AB17    |

| EMIOS21<br>GPIO[200]                                       | eMIOS channel<br>GPIO                                                      | P<br>G                | 01<br>00                 | 200        | I/O<br>I/O           | VDDEH4<br>Slow                                      | — /<br>WKPCFG | — /<br>WKPCFG      | _   | _      | W16     |

| EMIOS22<br>GPIO[201]                                       | eMIOS channel<br>GPIO                                                      | P<br>G                | 01<br>00                 | 201        | I/O<br>I/O           | VDDEH4<br>Slow                                      | — / Down      | — / Down           | _   | _      | Y16     |

| EMIOS23<br>GPIO[202]                                       | eMIOS channel<br>GPIO                                                      | P<br>G                | 01<br>00                 | 202        | I/O<br>I/O           | VDDEH4<br>Slow                                      | — / Down      | — / Down           | 80  | R11    | AA17    |

# 3.2 Maximum ratings

Table 9. Absolute maximum ratings<sup>(1)</sup>

| Symbol                               | Dovomotov | Conditions                                                 | Va                                   | alue                 | Unit                                     |      |

|--------------------------------------|-----------|------------------------------------------------------------|--------------------------------------|----------------------|------------------------------------------|------|

| Symbol                               |           | Parameter                                                  | Conditions                           | min                  | max                                      | Unit |

| V <sub>DD</sub>                      | SR        | 1.2 V core supply voltage <sup>(2)</sup>                   |                                      | -0.3                 | 1.32                                     | V    |

| V <sub>FLASH</sub>                   | SR        | Flash core voltage <sup>(3),(4)</sup>                      |                                      | -0.3                 | 3.6                                      | V    |

| V <sub>STBY</sub>                    | SR        | SRAM standby voltage <sup>(5)</sup>                        |                                      | -0.3                 | 6                                        | ٧    |

| V <sub>DDPLL</sub>                   | SR        | Clock synthesizer voltage                                  |                                      | -0.3                 | 1.32                                     | V    |

| V <sub>RC33</sub>                    | SR        | Voltage regulator control input voltage <sup>(4)</sup>     |                                      | -0.3                 | 3.6                                      | V    |

| V <sub>DDA</sub>                     | SR        | Analog supply voltage <sup>(5)</sup>                       | Reference to V <sub>SSA</sub>        | -0.3                 | 5.5                                      | ٧    |

| V <sub>DDE</sub>                     | SR        | I/O supply voltage <sup>(4),(6)</sup>                      |                                      | -0.3                 | 3.6                                      | V    |

| V <sub>DDEH</sub>                    | SR        | I/O supply voltage <sup>(5)</sup>                          |                                      | -0.3                 | 5.5                                      | V    |

|                                      |           |                                                            | V <sub>DDEH</sub> powered I/O pads   | -1.0 <sup>(8)</sup>  | V <sub>DDEH</sub> + 0.3 V <sup>(9)</sup> |      |

| V <sub>IN</sub>                      | SR        | DC input voltage <sup>(7)</sup>                            | V <sub>DDE</sub> powered I/O pads    | -1.0 <sup>(10)</sup> | V <sub>DDE</sub> + 0.3 V <sup>(10)</sup> | ٧    |

|                                      |           |                                                            | V <sub>DDA</sub> powered I/O pads    | -1.0                 | 5.5                                      |      |

| V <sub>DDREG</sub>                   | SR        | Voltage regulator supply voltage                           |                                      | -0.3                 | 5.5                                      | V    |

| V <sub>RH</sub>                      | SR        | Analog reference high voltage                              | Reference to VRL                     | -0.3                 | 5.5                                      | V    |

| V <sub>SS</sub> – V <sub>SSA</sub>   | SR        | V <sub>SS</sub> differential voltage                       |                                      | -0.1                 | 0.1                                      | V    |

| V <sub>RH</sub> – V <sub>RL</sub>    | SR        | V <sub>REF</sub> differential voltage                      |                                      | -0.3                 | 5.5                                      | ٧    |

| V <sub>RL</sub> – V <sub>SSA</sub>   | SR        | VRL to V <sub>SSA</sub> differential voltage               |                                      | -0.3                 | 0.3                                      | ٧    |

| V <sub>SSPLL</sub> – V <sub>SS</sub> | SR        | V <sub>SSPLL</sub> to V <sub>SS</sub> differential voltage |                                      | -0.1                 | 0.1                                      | V    |

| I <sub>MAXD</sub>                    | SR        | Maximum DC digital input current <sup>(11)</sup>           | Per pin, applies to all digital pins | -3                   | 3                                        | mA   |

| I <sub>MAXA</sub>                    | SR        | Maximum DC analog input current <sup>(12)</sup>            | Per pin, applies to all analog pins  | _                    | 5                                        | mA   |

82/157 Doc ID 15399 Rev 9

Table 10. Thermal characteristics for 176-pin QFP<sup>(1)</sup> (continued)

|   | Symbo              | ol | С | Parameter                                                  | Conditions | Value | Unit |

|---|--------------------|----|---|------------------------------------------------------------|------------|-------|------|

| Ī | $R_{\theta JCtop}$ | CC | D | Junction-to-Case <sup>(4)</sup>                            |            | 5     | °C/W |

|   | $\Psi_{JT}$        | СС | D | Junction-to-Package Top, Natural Convection <sup>(5)</sup> |            | 2     | °C/W |

- 1. Thermal characteristics are targets based on simulation that are subject to change per device characterization.

- Junction-to-Ambient Thermal Resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

- Junction-to-Board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

- 4. Junction-to-Case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

- Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

Table 11. Thermal characteristics for 208-pin LBGA<sup>(1)</sup>

| Symbo            | ol | C | Parameter                                                  | Conditions                                | Value | Unit |

|------------------|----|---|------------------------------------------------------------|-------------------------------------------|-------|------|

| $R_{	hetaJA}$    | СС | D | Junction-to-Ambient, Natural Convection <sup>(2),(3)</sup> | One layer board - 1s                      | 39    | °C/W |

| $R_{	hetaJA}$    | СС | D | Junction-to-Ambient, Natural Convection <sup>(2),(4)</sup> | Four layer board - 2s2p                   | 24    | °C/W |

| $R_{\theta JMA}$ | СС | D | Junction-to-Moving-Air, Ambient <sup>(2),(4)</sup>         | at 200 ft./min., one layer board          | 31    | °C/W |

| $R_{\theta JMA}$ | СС | D | Junction-to-Moving-Air, Ambient <sup>(2),(4)</sup>         | at 200 ft./min., four layer<br>board 2s2p | 20    | °C/W |

| $R_{\theta JB}$  | CC | D | Junction-to-board <sup>(5)</sup>                           | Four layer board - 2s2p                   | 13    | °C/W |

| $R_{\theta JC}$  | СС | D | Junction-to-case <sup>(6)</sup>                            |                                           | 6     | °C/W |

| $\Psi_{JT}$      | СС | D | Junction-to-package top natural convection <sup>(7)</sup>  |                                           | 2     | °C/W |

- 1. Thermal characteristics are targets based on simulation that are subject to change per device characterization.

- Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

- 4. Per JEDEC JESD51-6 with the board horizontal.

- 5. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature.

- Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

84/157 Doc ID 15399 Rev 9

| Symbo              | ol | С | Parameter                                                  | Conditions                                | Value | Unit |

|--------------------|----|---|------------------------------------------------------------|-------------------------------------------|-------|------|

| $R_{	hetaJA}$      | CC | D | Junction-to-Ambient, Natural Convection <sup>(2)</sup>     | Single layer board - 1s                   | 31    | °C/W |

| $R_{\theta JA}$    | СС | D | Junction-to-Ambient, Natural Convection <sup>(2)</sup>     | Four layer board - 2s2p                   | 23    | °C/W |

| $R_{	heta JMA}$    | СС | D | Junction-to-Moving-Air, Ambient <sup>(2)</sup>             | at 200 ft./min., single layer board       | 23    | °C/W |

| $R_{	heta JMA}$    | СС | D | Junction-to-Moving-Air, Ambient <sup>(2)</sup>             | at 200 ft./min., four layer<br>board 2s2p | 17    | °C/W |

| $R_{\theta JB}$    | СС | D | Junction-to-Board <sup>(3)</sup>                           |                                           | 11    | °C/W |

| $R_{\theta JCtop}$ | СС | D | Junction-to-Case <sup>(4)</sup>                            |                                           | 7     | °C/W |

| $\Psi_{JT}$        | СС | D | Junction-to-Package Top, Natural Convection <sup>(5)</sup> |                                           | 2     | °C/W |

Table 12. Thermal characteristics for 324-pin PBGA<sup>(1)</sup>

- 1. Thermal characteristics are targets based on simulation that are subject to change per device characterization.

- Junction-to-Ambient Thermal Resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets

JEDEC specification for this package.

- Junction-to-Board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

- 4. Junction-to-Case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

- Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

### 3.3.1 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>.1</sub>, can be obtained from the equation:

Equation 1

$$T_J = T_A + (R_{\theta JA} * P_D)$$

where:

$T_A$  = ambient temperature for the package ( ${}^{\circ}$ C)

R<sub>θ,JA</sub> = junction-to-ambient thermal resistance (°C/W)

P<sub>D</sub> = power dissipation in the package (W)

The thermal resistance values used are based on the JEDEC JESD51 series of standards to provide consistent values for estimations and comparisons. The difference between the values determined for the single-layer (1s) board compared to a four-layer board that has two signal layers, a power and a ground plane (2s2p), demonstrate that the effective thermal resistance is not a constant. The thermal resistance depends on the:

- Construction of the application board (number of planes)

- Effective size of the board which cools the component

- Quality of the thermal and electrical connections to the planes

- Power dissipated by adjacent components

Connect all the ground and power balls to the respective planes with one via per ball. Using fewer vias to connect the package to the planes reduces the thermal performance. Thinner planes also reduce the thermal performance. When the clearance between the vias leave the planes virtually disconnected, the thermal performance is also greatly reduced.

Table 21. DC electrical specifications (continued)

| Symbol                              |    |        | Parameter                                                                                       | Conditions                             |                         |     |                       |      |

|-------------------------------------|----|--------|-------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------|-----|-----------------------|------|

|                                     |    | С      |                                                                                                 |                                        | min                     | typ | max                   | Unit |

| V <sub>OL_HS</sub>                  | СС | Р      | Multi-voltage pad I/O<br>output low voltage in<br>high-swing mode <sup>(9)</sup>                |                                        | _                       | _   | 0.2*V <sub>DDEH</sub> | V    |

| V <sub>OH_S</sub>                   | СС | Р      | Slow/medium pad I/O output high voltage <sup>(9)</sup>                                          |                                        | 0.8 V <sub>DDEH</sub>   | _   | _                     | V    |

| V <sub>OH_F</sub>                   | СС | Р      | Fast pad I/O output high voltage <sup>(9)</sup>                                                 |                                        | 0.8 V <sub>DDE</sub>    | _   | _                     | V    |

| V <sub>OH_LS</sub>                  | СС | Р      | Multi-voltage pad I/O<br>output high voltage in<br>low-swing<br>mode <sup>(5),(6),(7),(8)</sup> | I <sub>OH_LS</sub> =<br>0.5 mA         | 2.1                     | 3.1 | 3.7                   | V    |

| V <sub>OH_HS</sub>                  | СС | Р      | Multi-voltage pad I/O<br>output high voltage in<br>high-swing mode <sup>(9)</sup>               |                                        | 0.8 V <sub>DDEH</sub>   | _   | _                     | V    |

| V <sub>HYS_S</sub>                  | СС | С      | Slow/medium/multi-<br>voltage I/O input<br>hysteresis                                           | _                                      | 0.1 * V <sub>DDEH</sub> | _   | _                     | V    |

| V <sub>HYS_F</sub>                  | СС | С      | Fast I/O input hysteresis                                                                       | _                                      | 0.1 * V <sub>DDE</sub>  | _   | _                     | V    |

| V <sub>HYS_LS</sub>                 | СС | С      | Low-Swing-Mode Multi-<br>Voltage I/O Input<br>Hysteresis                                        | hysteresis<br>enabled                  | 0.25                    | _   | _                     | ٧    |

|                                     | CC | P<br>P | Operating current 1.2 V                                                                         | V <sub>DD</sub> at 1.32 V at<br>80 MHz | _                       |     | 380                   | mA   |

| I <sub>DD</sub> +I <sub>DDPLL</sub> |    |        |                                                                                                 | V <sub>DD</sub> at 1.32V<br>at 120 MHz | _                       |     | 400                   | mA   |

|                                     |    |        |                                                                                                 | V <sub>DD</sub> at 1.32V<br>at 150 MHz | _                       |     | 445                   | mA   |

| IDDSTBY                             | СС | Т      | Operating current 0.95-<br>1.2 V                                                                | V <sub>STBY</sub> at 55 °C             | _                       | 35  | 100                   | μА   |

|                                     |    | Т      | Operating current 2–<br>5.5 V                                                                   | V <sub>STBY</sub> at 55 °C             | _                       | 45  | 110                   | μА   |

| I <sub>DDSTBY27</sub>               | 66 | Р      | Operating current 0.95-<br>1.2 V                                                                | V <sub>STBY</sub> 27 °C                |                         | 25  | 90                    | μА   |

|                                     | CC | Р      | Operating current 2-<br>5.5 V                                                                   | V <sub>STBY</sub> 27 °C                |                         | 35  | 100                   | μΑ   |

Table 21. DC electrical specifications (continued)

| Symbol                 |    |   | Parameter                                                                      | Conditions                                                                                 |      |     |     |        |

|------------------------|----|---|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|-----|-----|--------|

|                        |    | С |                                                                                |                                                                                            | min  | typ | max | - Unit |

| I <sub>ACT_MV_PD</sub> | СС | С | Multivoltage pad weak pulldown current                                         | V <sub>DDE</sub> =<br>3.0–3.6 V <sup>(5)</sup> ,<br>MultiV pad,<br>high swing<br>mode only | 10   | _   | 60  | μА     |

|                        |    | Р |                                                                                | 4.75 V – 5.25 V                                                                            | 25   | _   | 200 |        |

| I <sub>INACT_D</sub>   | СС | Р | I/O input leakage<br>current <sup>(16)</sup>                                   | _                                                                                          | -2.5 |     | 2.5 | μΑ     |

| I <sub>IC</sub>        | SR | Т | DC injection current (per pin)                                                 | _                                                                                          | -1.0 | _   | 1.0 | mA     |

|                        | SR | Р | Analog input current,<br>channel off, AN[0:7] <sup>(17)</sup>                  | _                                                                                          | -250 | _   | 250 |        |

| I <sub>INACT_</sub> A  |    | Р | Analog input current,<br>channel off, all other<br>analog pins <sup>(17)</sup> | _                                                                                          | -150 | _   | 150 | nA     |

| CL                     | СС | D |                                                                                | DSC(PCR[8:9])<br>= 0b00                                                                    | _    |     | 10  | pF     |

|                        |    | D | Load capacitance (fast I/O) <sup>(18)</sup>                                    | DSC(PCR[8:9])<br>= 0b01                                                                    | _    |     | 20  |        |

|                        |    | D |                                                                                | DSC(PCR[8:9])<br>= 0b10                                                                    | _    |     | 30  |        |

|                        |    | D |                                                                                | DSC(PCR[8:9])<br>= 0b11                                                                    | _    |     | 50  |        |

| C <sub>IN</sub>        | СС | D | Input capacitance<br>(digital pins)                                            | _                                                                                          | _    |     | 7   | pF     |

| C <sub>IN_A</sub>      | СС | D | Input capacitance (analog pins)                                                | _                                                                                          | _    |     | 10  | pF     |

| C <sub>IN_M</sub>      | СС | D | Input capacitance<br>(digital and analog<br>pins <sup>(19)</sup> )             | _                                                                                          | _    |     | 12  | pF     |

| R <sub>PUPD200K</sub>  | SR | Р | Weak Pull-Up/Down Resistance $^{(20)}$ , 200 k $\Omega$ Option                 | _                                                                                          | 130  | _   | 280 | kΩ     |

| R <sub>PUPD100K</sub>  | SR | Р | Weak Pull-Up/Down Resistance $^{(20)}$ , 100 k $\Omega$ Option                 | _                                                                                          | 65   | _   | 140 | kΩ     |

| #  | Symbol             |    | С | Characteristic                                                                 | Min. Value           | Max. Value | Unit |

|----|--------------------|----|---|--------------------------------------------------------------------------------|----------------------|------------|------|

| 9  | t <sub>TCYC</sub>  | CC | D | TCK Cycle Time                                                                 | 4 <sup>(6),(7)</sup> | _          | tcyc |

| 9a | t <sub>TCYC</sub>  | СС | D | Absolute Minimum TCK Cycle Time                                                | 100 <sup>(8)</sup>   | _          | ns   |

| 10 | t <sub>TDC</sub>   | СС | D | TCK Duty Cycle                                                                 | 40                   | 60         | %    |

| 11 | t <sub>NTDIS</sub> | СС | D | TDI Data Setup Time                                                            | 5                    | _          | ns   |

| 12 | t <sub>NTDIH</sub> | СС | D | TDI Data Hold Time                                                             | 25                   | _          | ns   |

| 13 | t <sub>NTMSS</sub> | СС | D | TMS Data Setup Time                                                            | 5                    | _          | ns   |

| 14 | t <sub>NTMSH</sub> | СС | D | TMS Data Hold Time                                                             | 25                   | _          | ns   |

| 15 | _                  | СС | D | TDO propagation delay from falling edge of TCK                                 | _                    | 19.5       | ns   |

| 16 | _                  | СС | D | TDO hold time with respect to TCK falling edge (minimum TDO propagation delay) | 5.25                 | _          | ns   |

Table 39. Nexus debug port timing<sup>(1)</sup> (continued)

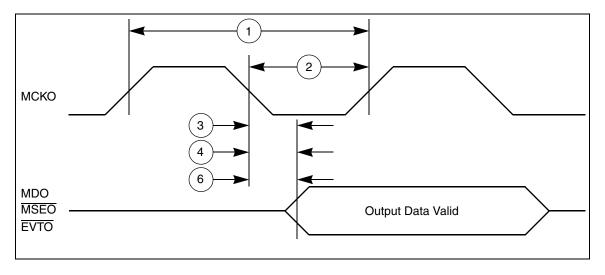

- 1. All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal. Nexus timing specified at V<sub>DD</sub> = 1.14 V to 1.32 V, V<sub>DDEH</sub> = 4.5 V to 5.5 V with multi-voltage pads programmed to Low-Swing mode, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>, and C<sub>L</sub> = 30 pF with DSC = 0b10.

- 2. Achieving the absolute minimum MCKO cycle time may require setting the MCKO divider to more than its minimum setting (NPC\_PCR[MCKO\_DIV] depending on the actual system frequency being used.

- 3. This is a functionally allowable feature. However, this may be limited by the maximum frequency specified by the Absolute minimum MCKO period specification.

- This may require setting the MCO divider to more than its minimum setting (NPC\_PCR[MCKO\_DIV]) depending on the actual system frequency being used.

- 5. MDO, MSEO, and EVTO data is held valid until next MCKO low cycle.

- 6. Achieving the absolute minimum TCK cycle time may require a maximum clock speed (system frequency / 8) that is less than the maximum functional capability of the design (system frequency / 4) depending on the actual system frequency being used.

- This is a functionally allowable feature. However, this may be limited by the maximum frequency specified by the Absolute minimum TCK period specification.

- 8. This may require a maximum clock speed (system frequency / 8) that is less than the maximum functional capability of the design (system frequency / 4) depending on the actual system frequency being used.

Figure 15. Nexus output timing

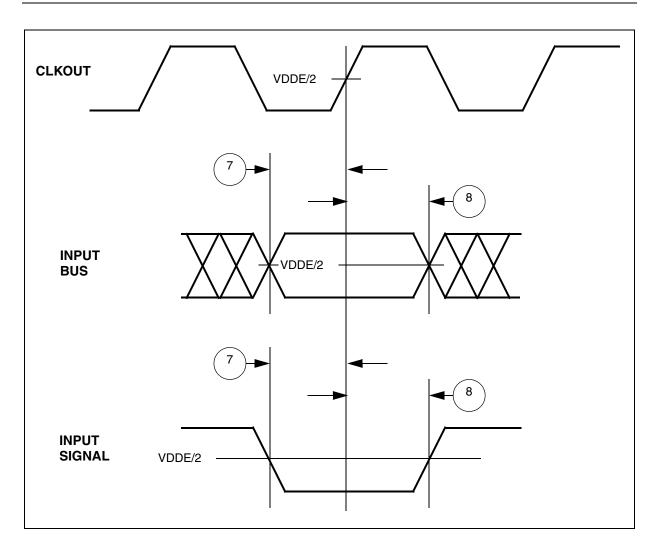

Figure 20. Synchronous input timing

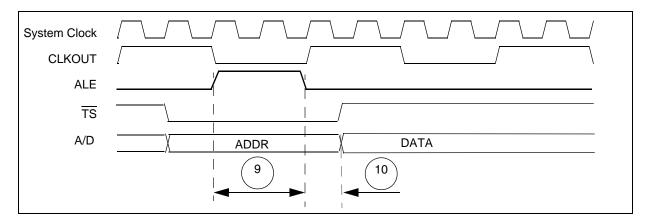

Figure 21. ALE signal timing