#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z4                                                                  |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 118                                                                     |

| Program Memory Size        | 4MB (4M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                |                                                                         |

| RAM Size                   | 192K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.14V ~ 1.32V                                                           |

| Data Converters            | A/D 34x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 176-LQFP                                                                |

| Supplier Device Package    | 176-LQFP (24x24)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc564a80l7cfbr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 4 slave ports

- Flash

- Calibration and EBI bus

- SRAM

- Peripheral bridge

- 32-bit internal address, 64-bit internal data paths

# 1.5.3 eDMA

The enhanced direct memory access (eDMA) controller is a second-generation module capable of performing complex data movements via 64 programmable channels, with minimal intervention from the host processor. The hardware micro-architecture includes a DMA engine which performs source and destination address calculations, and the actual data movement operations, along with an SRAM-based memory containing the transfer control descriptors (TCD) for the channels. This implementation is utilized to minimize the overall block size. The eDMA module provides the following features:

- All data movement via dual-address transfers: read from source, write to destination

- Programmable source and destination addresses, transfer size, plus support for enhanced addressing modes

- Transfer control descriptor organized to support two-deep, nested transfer operations

- An inner data transfer loop defined by a "minor" byte transfer count

- An outer data transfer loop defined by a "major" iteration count

- Channel activation via one of three methods:

- Explicit software initiation

- Initiation via a channel-to-channel linking mechanism for continuous transfers

- Peripheral-paced hardware requests (one per channel)

- Support for fixed-priority and round-robin channel arbitration

- Channel completion reported via optional interrupt requests

- One interrupt per channel, optionally asserted at completion of major iteration count

- Error termination interrupts optionally enabled

- Support for scatter/gather DMA processing

- Ability to suspend channel transfers by a higher priority channel

# 1.5.4 Interrupt controller

The INTC (interrupt controller) provides priority-based preemptive scheduling of interrupt requests, suitable for statically scheduled hard real-time systems.

For high priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR needs to be executed. It also provides an ample number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

When multiple tasks share a resource, coherent accesses to that resource need to be supported. The INTC supports the priority ceiling protocol for coherent accesses. By

The FlexCAN modules provide the following features:

- Full Implementation of the CAN protocol specification, Version 2.0B

- Standard data and remote frames

- Extended data and remote frames

- Zero to eight bytes data length

- Programmable bit rate up to 1 Mbit/s

- Content-related addressing

- 64 message buffers of zero to eight bytes data length

- Individual Rx Mask Register per message buffer

- Each message buffer configurable as Rx or Tx, all supporting standard and extended messages

- Includes 1088 bytes of embedded memory for message buffer storage

- Includes 256-byte memory for storing individual Rx mask registers

- Full featured Rx FIFO with storage capacity for six frames and internal pointer handling

- Powerful Rx FIFO ID filtering, capable of matching incoming IDs against 8 extended, 16 standard or 32 partial (8 bits) IDs, with individual masking capability

- Selectable backwards compatibility with previous FlexCAN versions

- Programmable clock source to the CAN Protocol Interface, either system clock or oscillator clock

- Listen only mode capability

- Programmable loop-back mode supporting self-test operation

- 3 programmable Mask Registers

- Programmable transmit-first scheme: lowest ID, lowest buffer number or highest priority

- Time Stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Warning interrupts when the Rx and Tx Error Counters reach 96

- Independent of the transmission medium (an external transceiver is assumed)

- Multi-master concept

- High immunity to EMI

- Short latency time due to an arbitration scheme for high-priority messages

- Low power mode, with programmable wake-up on bus activity

and four independent timer comparators. These comparators produce a CPU interrupt when the timer exceeds the programmed value.

The following features are implemented in the STM:

- One 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

# 1.5.19 Software watchdog timer (SWT)

The Software Watchdog Timer (SWT) is a second watchdog module to complement the standard Power Architecture watchdog integrated in the CPU core. The SWT is a 32-bit modulus counter, clocked by the system clock or the crystal clock, that can provide a system reset or interrupt request when the correct software key is not written within the required time window.

The following features are implemented:

- 32-bit modulus counter

- Clocked by system clock or crystal clock

- Optional programmable watchdog window mode

- Can optionally cause system reset or interrupt request on timeout

- Reset by writing a software key to memory mapped register

- Enabled out of reset

- Configuration is protected by a software key or a write-once register

# 1.5.20 Cyclic redundancy check (CRC) module

The CRC computing unit is dedicated to the computation of CRC off-loading the CPU. The CRC features:

- Support for CRC-16-CCITT (x25 protocol):

- $X^{16} + X^{12} + X^5 + 1$

- Support for CRC-32 (Ethernet protocol):

- $X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^8 + X^7 + X^5 + X^4 + X^2 + X + 1$

- Zero wait states for each write/read operations to the CRC\_CFG and CRC\_INP registers at the maximum frequency

# 1.5.21 Error correction status module (ECSM)

The ECSM provides a myriad of miscellaneous control functions regarding program-visible information about the platform configuration and revision levels, a reset status register, a software watchdog timer, wakeup control for exiting sleep modes, and information on platform memory errors reported by error-correcting codes and/or generic access error information for certain processor cores.

# **1.5.24 Power management controller (PMC)**

The power management controller contains circuitry to generate the internal 3.3 V supply and to control the regulation of 1.2 V supply with an external NPN ballast transistor. It also contains low voltage inhibit (LVI) and power-on reset (POR) circuits for the 1.2 V supply, the 3.3 V supply, the 3.3 V/5 V supply of the closest I/O segment (VDDEH1) and the 5 V supply of the regulators (VDDREG).

# 1.5.25 Nexus port controller

The NPC (Nexus Port Controller) block provides real-time Nexus Class3+ development support capabilities for the SPC564A80 Power Architecture-based MCU in compliance with the IEEE-ISTO 5001-2003 and 2010 standards. MDO port widths of 4 pins and 12 pins are available in all packages.

# 1.5.26 JTAG

The JTAGC (JTAG Controller) block provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode. Testing is performed via a boundary scan technique, as defined in the IEEE 1149.1-2001 standard. All data input to and output from the JTAGC block is communicated in serial format. The JTAGC block is compliant with the IEEE 1149.1-2001 standard and supports the following features:

- IEEE 1149.1-2001 Test Access Port (TAP) interface 4 pins (TDI, TMS, TCK, and TDO)

- A 5-bit instruction register that supports the following IEEE 1149.1-2001 defined instructions:

- BYPASS, IDCODE, EXTEST, SAMPLE, SAMPLE/PRELOAD, HIGHZ, CLAMP

- A 5-bit instruction register that supports the additional following public instructions:

- ACCESS\_AUX\_TAP\_NPC

- ACCESS\_AUX\_TAP\_ONCE

- ACCESS\_AUX\_TAP\_eTPU

- ACCESS\_CENSOR

- 3 test data registers to support JTAG Boundary Scan mode

- Bypass register

- Boundary scan register

- Device identification register

- A TAP controller state machine that controls the operation of the data registers, instruction register and associated circuitry

- Censorship Inhibit Register

- 64-bit Censorship password register

- If the external tool writes a 64-bit password that matches the Serial Boot password stored in the internal flash shadow row, Censorship is disabled until the next system reset.

# 1.5.27 Development Trigger Semaphore (DTS)

SPC564A80 devices include a system development feature, the Development Trigger Semaphore (DTS) module, that enables software to signal an external tool by driving a persistent (affected only by reset or an external tool) signal on an external device pin. There

|                                            |                                                                                   | Р                     | PCR                      |            |                        |                                                     | Sta          | tus <sup>(7)</sup> | Package pin # |     |    |  |

|--------------------------------------------|-----------------------------------------------------------------------------------|-----------------------|--------------------------|------------|------------------------|-----------------------------------------------------|--------------|--------------------|---------------|-----|----|--|

| Name                                       | Function <sup>(1)</sup>                                                           | A<br>G <sup>(2)</sup> | PA<br>Field<br>(3)       | PCR<br>(4) | l/O<br>Type            | Voltage <sup>(5)</sup> /<br>Pad Type <sup>(6)</sup> | During Reset | After<br>Reset     | 176           | 208 | 32 |  |

| ADDR12<br>GPIO[8]                          | External address bus<br>GPIO                                                      | P<br>G                | 01<br>00                 | 8          | I/O<br>I/O             | VDDE3<br>Fast                                       | — / Up       | — / Up             | _             | _   | тз |  |

| ADDR13<br>WE[2]<br>GPIO[9]                 | External address bus<br>Write/byte enable<br>GPIO                                 | P<br>A2<br>G          | 001<br>100<br>000        | 9          | I/O<br>O<br>I/O        | VDDE3<br>Fast                                       | — / Up       | — / Up             | _             | _   | U3 |  |

| ADDR14<br>WE[3]<br>GPIO[10]                | External address bus<br>Write/byte enables<br>GPIO                                | P<br>A2<br>G          | 001<br>100<br>000        | 10         | I/O<br>O<br>I/O        | VDDE3<br>Fast                                       | — / Up       | — / Up             | _             |     | U4 |  |

| ADDR15<br>GPIO[11]                         | External address bus<br>GPIO                                                      | P<br>G                | 01<br>00                 | 11         | I/O<br>I/O             | VDDE3<br>Fast                                       | — / Up       | — / Up             | _             | _   | V3 |  |

| ADDR16<br>FR_A_TX<br>DATA16<br>GPIO[12]    | External address bus<br>Flexray TX data channel A<br>External data bus<br>GPIO    | P<br>A1<br>A2<br>G    | 001<br>010<br>100<br>000 | 12         | I/O<br>O<br>I/O<br>I/O | VDDE-EH<br>Medium                                   | — / Up       | — / Up             | _             | _   | P1 |  |

| ADDR17<br>FR_A_TX_EN<br>DATA17<br>GPIO[13] | External address bus<br>FlexRay ch. A TX data enable<br>External data bus<br>GPIO | P<br>A1<br>A2<br>G    | 001<br>010<br>100<br>000 | 13         | I/O<br>O<br>I/O<br>I/O | VDDE-EH<br>Medium                                   | — / Up       | — / Up             | _             | _   | P2 |  |

| ADDR18<br>FR_A_RX<br>DATA18<br>GPIO[14]    | External address bus<br>Flexray RX data ch. A<br>External data bus<br>GPIO        | P<br>A1<br>A2<br>G    | 001<br>010<br>100<br>000 | 14         | I/O<br>I<br>I/O<br>I/O | VDDE-EH<br>Medium                                   | — / Up       | — / Up             | _             | _   | R1 |  |

| ADDR19<br>FR_B_TX<br>DATA19<br>GPIO[15]    | External address bus<br>Flexray TX data ch. B<br>External data bus<br>GPIO        | P<br>A1<br>A2<br>G    | 001<br>010<br>100<br>000 | 15         | I/O<br>O<br>I/O<br>I/O | VDDE-EH<br>Medium                                   | — / Up       | — / Up             | _             | _   | R2 |  |

| ADDR20<br>FR_B_TX_EN<br>DATA20             | External address bus<br>Flexray TX data enable for ch. B<br>External data bus     | P<br>A1<br>A2         | 001<br>010<br>100        | 16         | I/O<br>O<br>I/O        | VDDE-EH<br>Medium                                   | — / Up       | — / Up             | _             | _   | T1 |  |

#### Table 4. SPC564A80 signal properties (continued)

43/157

Doc ID 15399 Rev 9

DATA20

GPIO[16]

External data bus

GPIO

A2

G

100

000

I/O

I/O

324

| Table 4. | SPC564A80 signal properties ( | conti | nued) |     |     |    |

|----------|-------------------------------|-------|-------|-----|-----|----|

|          |                               | Р     |       | PCB | I/O | Ve |

|                                                         |                                                    | Р                     | PCR                | PCR        | I/O           | Voltage <sup>(5)</sup> /                            | Sta          | tus <sup>(7)</sup>   | Package pin # |     |     |  |

|---------------------------------------------------------|----------------------------------------------------|-----------------------|--------------------|------------|---------------|-----------------------------------------------------|--------------|----------------------|---------------|-----|-----|--|

| Name                                                    | Function <sup>(1)</sup>                            | A<br>G <sup>(2)</sup> | PA<br>Field<br>(3) | PCR<br>(4) | Туре          | Voltage <sup>(3)</sup> /<br>Pad Type <sup>(6)</sup> | During Reset | After<br>Reset       | 176           | 208 | 324 |  |

| CAN_C_RX<br>DSPI_D_PCS[4]<br>GPIO[88]                   | FlexCAN C RXPDSPI D peripheral chip selectA1GPIOG  |                       | 01<br>10<br>00     | 88         | <br>0<br> /0  | VDDEH6<br>Slow                                      | — / Up       | — / Up               | 98            | L14 | R20 |  |

|                                                         | -                                                  |                       |                    |            | eS            | SCI                                                 |              |                      |               |     |     |  |

| SCI_A_TX<br>EMIOS13 <sup>(8)</sup><br>GPIO[89]          | eSCI A TX<br>eMIOS channel<br>GPIO                 |                       | 01<br>10<br>00     | 89         | 0<br>0<br>I/O | VDDEH6<br>Medium                                    | — / Up       | — / Up               | 100           | J14 | N20 |  |

| SCI_A_RX<br>EMIOS15 <sup>(8)</sup><br>GPIO[90]          | eSCI A RX<br>eMIOS channel<br>GPIO                 | P<br>A1<br>G          | 01<br>10<br>00     | 90         | <br>0<br> /0  | VDDEH6<br>Medium                                    | — / Up       | — / Up               | 99            | K14 | P20 |  |

| SCI_B_TX<br>DSPI_D_PCS[1]<br>GPIO[91]                   | eSCI B TX<br>DSPI D peripheral chip select<br>GPIO | P<br>A1<br>G          | 01<br>10<br>00     | 91         | 0<br>0<br>I/O | VDDEH6<br>Medium                                    | — / Up       | —/Up —/Up 87 L13 R21 |               |     |     |  |

| SCI_B_RX<br>DSPI_D_PCS[5]<br>GPIO[92]                   | eSCI B RX<br>DSPI D peripheral chip select<br>GPIO | P<br>A1<br>G          | 01<br>10<br>00     | 92         | <br>0<br> /0  | VDDEH6<br>Medium                                    | — / Up       | — / Up               | 84            | M13 | T19 |  |

| SCI_C_TX<br>GPIO[244]                                   | eSCI C TX<br>GPIO                                  | P<br>G                | 01<br>00           | 244        | 0<br>I/O      | VDDEH6<br>Medium                                    | — / Up       | — / Up               | _             | _   | W18 |  |

| SCI_C_RX<br>GPIO[245]                                   | eSCI C RX<br>GPIO                                  | P<br>G                | 01<br>00           | 245        | l<br>I/O      | VDDEH6<br>Medium                                    | — / Up       | — / Up               | _             | _   | Y19 |  |

|                                                         |                                                    |                       |                    |            | DS            | SPI                                                 |              |                      |               |     |     |  |

| DSPI_A_SCK <sup>(17)</sup><br>DSPI_C_PCS[1]<br>GPIO[93] | —<br>DSPI C peripheral chip select<br>GPIO         | —<br>A1<br>G          | —<br>10<br>00      | 93         | —<br>0<br>I/O | VDDEH7<br>Medium                                    | — / Up       | — / Up               | _             | _   | L22 |  |

| DSPI_A_SIN <sup>(17)</sup><br>DSPI_C_PCS[2]<br>GPIO[94] | —<br>DSPI C peripheral chip select<br>GPIO         |                       |                    | _          | L21           |                                                     |              |                      |               |     |     |  |

SPC564A74L7, SPC564A80B4, SPC564A80L7

Pinout and signal description

54/157

Doc ID 15399 Rev 9

| Table 4. | SPC564A80 signal properties (continued) |

|----------|-----------------------------------------|

|----------|-----------------------------------------|

|                          |                               | Р                     | PCR                 | DOD        | I/O         |                                                     | Sta          | tus <sup>(7)</sup> | Package pin # |     |      |  |

|--------------------------|-------------------------------|-----------------------|---------------------|------------|-------------|-----------------------------------------------------|--------------|--------------------|---------------|-----|------|--|

| Name                     | Function <sup>(1)</sup>       | A<br>G <sup>(2)</sup> | PA<br>Field<br>(3)  | PCR<br>(4) | і/О<br>Туре | Voltage <sup>(5)</sup> /<br>Pad Type <sup>(6)</sup> | During Reset | After<br>Reset     | 176           | 208 | 324  |  |

| ETPUA30                  | eTPU A channel                | Р                     | 001                 |            | I/O         |                                                     |              |                    |               |     |      |  |

| DSPI_C_PCS[3]            | DSPI C peripheral chip select | A1                    | 010                 | 144        | 0           | VDDEH1                                              | _/           | <u> </u>           | 22            | E1  | C1   |  |

| ETPUA11_O <sup>(8)</sup> | eTPU A channel (output only)  | A2                    | 100                 | 144        | 0           | Medium                                              | WKPCFG       | WKPCFG             | 22            |     | 01   |  |

| GPIO[144]                | GPIO                          | G                     | 000                 |            | I/O         |                                                     |              |                    |               |     |      |  |

| ETPUA31                  | eTPU A channel                | Р                     | 001                 |            | I/O         |                                                     |              |                    |               |     |      |  |

| DSPI_C_PCS[4]            | DSPI C peripheral chip select |                       | 010                 |            | 0           | VDDEH1                                              | _/           | — /                | 21            | E2  |      |  |

| ETPUA13_O <sup>(8)</sup> | eTPU A channel (output only)  | A2                    | A2 100 145<br>G 000 |            | 0           | Medium                                              | WKPCFG       | WKPCFG             |               |     | C2   |  |

| GPIO[145]                | GPIO                          | G                     |                     |            | I/O         |                                                     |              |                    |               |     |      |  |

|                          |                               |                       |                     |            | eM          | IOS                                                 |              |                    |               |     | 1    |  |

| EMIOS0                   | eMIOS channel                 | Р                     | 001                 |            | I/O         |                                                     |              |                    |               |     |      |  |

| ETPUA0_O <sup>(8)</sup>  | eTPU A channel (output only)  | A1                    | 010                 |            | 0           | VDDEH4                                              |              |                    |               |     |      |  |

| ETPUA25_O <sup>(8)</sup> | eTPU A channel (output only)  | A2                    | 100                 | 179        | 0           | Slow                                                | — / Up       | — / Up             | 63            | T4  | AB10 |  |

| GPIO[179]                | GPIO                          | G                     | 000                 |            | I/O         |                                                     |              |                    |               |     |      |  |

| EMIOS1                   | eMIOS channel                 | Р                     | 01                  |            | I/O         |                                                     |              |                    |               |     |      |  |

| ETPUA1_O <sup>(8)</sup>  | eTPU A channel (output only)  | A1                    | 10                  | 180        | 0           | VDDEH4                                              | — / Up       | — / Up             | 64            | T5  | AB11 |  |

| GPIO[180]                | GPIO                          | G                     | 00                  |            | I/O         | Slow                                                |              |                    |               |     |      |  |

| EMIOS2                   | eMIOS channel                 | Р                     | 001                 |            | I/O         |                                                     |              |                    |               |     |      |  |

| ETPUA2_O <sup>(8)</sup>  | eTPU A channel (output only)  | A1                    | 010                 |            | 0           | VDDEH4                                              | <i>.</i>     | <i>.</i>           |               |     |      |  |

| RCH2_B                   | Reaction channel 2B           | A2                    | 100                 | 181        | 0           | Slow                                                | — / Up       | — / Up             | 65            | N7  | W12  |  |

| GPIO[181]                | GPIO                          | G                     | 000                 |            | I/O         |                                                     |              |                    |               |     |      |  |

| EMIOS3                   | eMIOS channel                 | Р                     | 01                  |            | I/O         |                                                     | ,            |                    |               |     |      |  |

| ETPUA3_O <sup>(8)</sup>  | eTPU A channel (output only)  | A1                    | 10                  | 182        | 0           | VDDEH4                                              | —/           | —/                 | 66            | R6  | AA11 |  |

| GPIO[182]                | GPIO                          | G                     | 00                  |            | I/O         | Slow                                                | WKPCFG       | WKPCFG             |               |     |      |  |

| EMIOS4                   | eMIOS channel                 | Р                     | 001                 |            | I/O         |                                                     |              |                    |               |     |      |  |

| ETPUA4_O <sup>(8)</sup>  | eTPU A channel (output only)  | A1                    | 010                 |            | 0           | VDDEH4                                              | /            | <u> </u>           |               |     |      |  |

| RCH2_C                   | Reaction channel 2C           | A2                    | 100                 | 183        | 0           | Slow                                                | WKPCFG       | WKPCFG             | 67            | R5  | AB12 |  |

| GPIO[183]                | GPIO                          | G                     | 000                 |            | I/O         |                                                     |              |                    |               |     |      |  |

5

Pinout and signal description

| Table 6. Signal det                                    | able 6. Signal details (continued) |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|--------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Signal                                                 | Module or Function                 | Description                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| DSPI_C_SCK_LVDS-<br>DSPI_C_SCK_LVDS+                   | DSPI                               | LVDS pair used for DSPI_C TSB mode transmission                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| DSPI_C_SOUT_LVDS-<br>DSPI_C_SOUT_LVDS+                 | DSPI                               | LVDS pair used for DSPI_C TSB mode transmission                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| PCS_B[0]<br>PCS_C[0]<br>PCS_D[0]                       | DSPI_B - DSPI_D                    | Peripheral chip select when device is in master mode—slave select when used in slave mode                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| PCS_B[1:5]<br>PCS_C[1:5] DSPI_B - DSPI_D<br>PCS_D[1:5] |                                    | Peripheral chip select when device is in master mode—not used in slave mode                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| SCK_B<br>SCK_C DSPI_B - DSPI_<br>SCK_D                 |                                    | DSPI clock—output when device is in master mode; input when in slave mode                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| SIN_B<br>SIN_C<br>SIN_D                                | DSPI_B - DSPI_D                    | DSPI data in                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| SOUT_B<br>SOUT_C<br>SOUT_D                             | DSPI_B - DSPI_D                    | DSPI data out                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| ADDR[10:31]                                            | EBI                                | The ADDR[10:31] signals specify the physical address of the<br>bus transaction.<br>The 26 address lines correspond to bits 3-31 of the EBI's 32-bit<br>internal address bus.<br>ADDR[15:31] can be used as Address and Data signals when<br>configured appropriately for a multiplexed external bus. This<br>allows 32-bit data operations, or 16-bit data operations without<br>using DATA[0:15] signals. |  |  |  |  |  |  |  |

| ALE                                                    | EBI                                | The Address Latch Enable (ALE) signal is used to demultiplex<br>the address from the data bus. It is asserted while the least<br>significant 16 bits of the address are present in the multiplexed<br>address/data bus.                                                                                                                                                                                    |  |  |  |  |  |  |  |

| BDIP                                                   | EBI                                | BDIP is asserted to indicate that the master is requesting another data beat following the current one.                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| <u>CS</u> [0:3]                                        | EBI                                | $\overline{\text{CS}}$ x is asserted by the master to indicate that this transaction is targeted for a particular memory bank on the Primary external bus.                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| DATA[0:31]                                             | EBI                                | The DATA[0:31] signals contain the data to be transferred for the current transaction.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| ŌĒ                                                     | EBI                                | $\overline{OE}$ is used to indicate when an external memory is permitted to drive back read data. External memories must have their data output buffers off when $\overline{OE}$ is negated. $\overline{OE}$ is only asserted for chip-select accesses.                                                                                                                                                    |  |  |  |  |  |  |  |

## Table 6. Signal details (continued)

| ID | Name    | е  |   | Parameter                                                     | Min              | Тур     | Max              | Unit | Notes |

|----|---------|----|---|---------------------------------------------------------------|------------------|---------|------------------|------|-------|

| 9  | Por5V_r | сс |   | Nominal POR for rising 5 V<br>V <sub>DDREG</sub> supply       | _                | 2.67    | _                | V    |       |

| 9a | _       | сс | С | Variation of POR for rising<br>5 V V <sub>DDREG</sub> supply  | Por5V_r<br>- 35% | Por5V_r | Por5V_r<br>+ 50% | V    |       |

| 9b | Por5V_f | сс |   | Nominal POR for falling 5 V<br>V <sub>DDREG</sub> supply      | _                | 2.47    | _                | V    |       |

| 9c |         | сс | С | Variation of POR for falling<br>5 V V <sub>DDREG</sub> supply | Por5V_f<br>- 35% | Por5V_f | Por5V_f<br>+ 50% | V    |       |

Table 16.

PMC Electrical Characteristics (continued)

1. Using external ballast transistor.

- 2. Min range is extended to 10% since Lvi1p2 is reprogrammed from 1.2 V to 1.16 V after power-on reset.

- 3. LVI for falling supply is calculated as LVI rising LVI hysteresis.

- Lvi1p2 tracks DC target variation of internal Vdd regulator. Minimum and maximum Lvi1p2 correspond to minimum and maximum Vdd DC target respectively.

- 5. Minimum loading (<10 mA) for reading trim values from flash, powering internal RC oscillator, and IO consumption during POR.

- 6. No external load is allowed, except for use as a reference for an external tool.

- 7. This value is valid only when the internal regulator is bypassed. When the internal regulator is enabled, the maximum external load allowed on the Nexus pads is 30 pF at 40 MHz.

- 8. Lvi3p3 tracks DC target variation of internal Vdd33 regulator. Minimum and maximum Lvi3p3 correspond to minimum and maximum Vdd33 DC target respectively.

# 3.6.1 Regulator Example

In designs where the SPC564A80 microcontroller's internal regulators are used, a ballast is required for generation of the 1.2 V internal supply. No ballast is required when an external 1.2 V supply is used.

# 3.8 DC electrical specifications

| Table 21. DC electrical specification |

|---------------------------------------|

|---------------------------------------|

| Ormetral                             |          |          | Baurantan                                                     | O a malibilita ma      |                       | Value |                        | 11   |

|--------------------------------------|----------|----------|---------------------------------------------------------------|------------------------|-----------------------|-------|------------------------|------|

| Symbol                               |          | С        | Parameter                                                     | Conditions             | min                   | typ   | max                    | Unit |

| V <sub>DD</sub>                      | SR       | <b>—</b> | Core supply voltage                                           | _                      | 1.14                  |       | 1.32                   | V    |

| V <sub>DDE</sub>                     | SR       | —        | I/O supply voltage                                            | _                      | 1.62                  |       | 3.6                    | V    |

| V <sub>DDEH</sub>                    | SR       | —        | I/O supply voltage                                            | _                      | 3.0                   |       | 5.25                   | V    |

| V <sub>DDE-EH</sub>                  | SR       | _        | I/O supply voltage                                            | —                      | 3.0                   |       | 5.25                   | V    |

| V <sub>RC33</sub>                    | SR       | _        | 3.3 V regulated voltage <sup>(1)</sup>                        | _                      | 3.0                   | _     | 3.6                    | V    |

| V <sub>DDA</sub>                     | SR       | —        | Analog supply voltage                                         |                        | 4.75 <sup>(2)</sup>   | _     | 5.25                   | V    |

| V <sub>INDC</sub>                    | SR       | —        | Analog input voltage                                          | _                      | V <sub>SSA</sub> -0.3 |       | V <sub>DDA</sub> +0.3  | V    |

| $V_{SS} - V_{SSA}$                   | SR       | —        | V <sub>SS</sub> differential voltage                          | _                      | -100                  | _     | 100                    | mV   |

| V <sub>RL</sub>                      | SR       |          | Analog reference low voltage                                  | _                      | V <sub>SSA</sub>      |       | V <sub>SSA</sub> +0.1  | V    |

| V <sub>RL</sub> – V <sub>SSA</sub>   | SR       | —        | VRL differential voltage                                      |                        | -100                  | _     | 100                    | mV   |

| V <sub>RH</sub>                      | SR       | _        | Analog reference high voltage                                 | _                      | V <sub>DDA</sub> -0.1 | _     | V <sub>DDA</sub>       | V    |

| V <sub>RH</sub> – V <sub>RL</sub>    | SR       | _        | V <sub>REF</sub> differential voltage                         | _                      | 4.75                  | _     | 5.25                   | V    |

| V <sub>DDF</sub>                     | SR       | _        | Flash operating<br>voltage <sup>(3)</sup>                     | _                      | 1.14                  | _     | 1.32                   | V    |

| V <sub>FLASH</sub> <sup>(4)</sup>    | SR       | —        | Flash read voltage                                            | _                      | 3.0                   |       | 3.6                    | V    |

| N                                    |          |          | SRAM standby voltage                                          | Unregulated mode       | 0.95                  |       | 1.2                    | V    |

| V <sub>STBY</sub>                    | SR       | -        | Keep-out Range: 1.2V–<br>2V                                   | Regulated mode         | 2.0                   |       | 5.5                    | V    |

| V <sub>DDREG</sub>                   | SR       | _        | Voltage regulator supply voltage                              | _                      | 4.75                  | _     | 5.25                   | V    |

| V <sub>DDPLL</sub>                   | SR       | _        | Clock synthesizer<br>operating voltage                        | _                      | 1.14                  | _     | 1.32                   | V    |

| V <sub>SSPLL</sub> – V <sub>SS</sub> | SR       | _        | V <sub>SSPLL</sub> to V <sub>SS</sub><br>differential voltage | _                      | -100                  | _     | 100                    | mV   |

| V                                    | <u> </u> | с        | Slow/medium I/O pad                                           | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3  |       | 0.35*V <sub>DDEH</sub> | V    |

| V <sub>IL_S</sub>                    | СС       | Р        | input low voltage                                             | Hysteresis<br>disabled | V <sub>SS</sub> -0.3  | _     | 0.40*V <sub>DDEH</sub> | V    |

| Pad<br>Type | Symbo   | I  | с | Period<br>(ns) | Load<br><sup>(2)</sup><br>(pF) | V <sub>RC33</sub><br>(V) | V <sub>DDE</sub><br>(V) | Drive<br>Select | I <sub>DD33</sub> Avg<br>(μΑ) | I <sub>DD33</sub> RMS<br>(μA) |

|-------------|---------|----|---|----------------|--------------------------------|--------------------------|-------------------------|-----------------|-------------------------------|-------------------------------|

|             |         | СС | D | 10             | 50                             | 3.6                      | 3.6                     | 11              | 2.35                          | 6.12                          |

|             |         | СС | D | 10             | 30                             | 3.6                      | 3.6                     | 10              | 1.75                          | 4.3                           |

|             |         | СС | D | 10             | 20                             | 3.6                      | 3.6                     | 01              | 1.41                          | 3.43                          |

| Fast        |         | СС | D | 10             | 10                             | 3.6                      | 3.6                     | 00              | 1.06                          | 2.9                           |

| rasi        | IDRV_FC | СС | D | 10             | 50                             | 3.6                      | 1.98                    | 11              | 1.75                          | 4.56                          |

|             |         | СС | D | 10             | 30                             | 3.6                      | 1.98                    | 10              | 1.32                          | 3.44                          |

|             |         | СС | D | 10             | 20                             | 3.6                      | 1.98                    | 01              | 1.14                          | 2.95                          |

|             |         | СС | D | 10             | 10                             | 3.6                      | 1.98                    | 00              | 0.95                          | 2.62                          |

Table 24. V<sub>RC33</sub> pad average DC current<sup>(1)</sup>

1. These are typical values that are estimated from simulation and not tested. Currents apply to output pins only.

2. All loads are lumped.

# 3.9.2 LVDS pad specifications

LVDS pads are implemented to support the MSC (Microsecond Channel) protocol which is an enhanced feature of the DSPI module. The LVDS pads are compliant with LVDS specifications and support data rates up to 50 MHz.

| Table 25. | DSPI LVDS pad specification |

|-----------|-----------------------------|

|-----------|-----------------------------|

| # | Characteristic                     | Symbol                         |     | Characteristic Symb |                     | с    | Condition | Min.<br>Value | Typ.<br>Value | Max.<br>Value | Unit |

|---|------------------------------------|--------------------------------|-----|---------------------|---------------------|------|-----------|---------------|---------------|---------------|------|

|   |                                    |                                | Dat | a Ra                | te                  |      |           |               |               |               |      |

| 4 | Data Frequency                     | f <sub>LVDSCLK</sub>           | СС  | D                   | —                   |      | 50        |               | MHz           |               |      |

|   | Driver Specs                       |                                |     |                     |                     |      |           |               |               |               |      |

|   |                                    | V <sub>OD</sub>                | сс  | Ρ                   | SRC=0b00<br>or 0b11 | 150  |           | 400           |               |               |      |

| 5 | Differential output voltage        |                                | СС  | Ρ                   | SRC=0b01            | 90   |           | 320           | mV            |               |      |

|   |                                    |                                | СС  | Ρ                   | SRC=0b10            | 160  |           | 480           |               |               |      |

| 6 | Common mode voltage<br>(LVDS), VOS | V <sub>OD</sub>                | сс  | Ρ                   |                     | 1.06 | 1.2       | 1.39          | V             |               |      |

| 7 | Rise/Fall time                     | T <sub>R</sub> /T <sub>F</sub> | СС  | D                   | _                   |      | 2         |               | ns            |               |      |

| 8 | Propagation delay (Low to High)    | T <sub>PLH</sub>               | сс  | D                   |                     |      | 4         |               | ns            |               |      |

| 9 | Propagation delay (High to Low)    | T <sub>PHL</sub>               | сс  | D                   |                     |      | 4         |               | ns            |               |      |

| C                    | hal  | • | Devenuet                                                                         |                                 | Va                                             | Unit                                           |        |  |

|----------------------|------|---|----------------------------------------------------------------------------------|---------------------------------|------------------------------------------------|------------------------------------------------|--------|--|

| Sym                  | IDOI | С | Paramete                                                                         | er                              | min                                            | max                                            | Unit   |  |

|                      | CC   | _ | Variable gain ampli                                                              | ifier accurad                   | cy (gain=2) <sup>(2)</sup>                     |                                                |        |  |

|                      | СС   | D | INL                                                                              | 8 MHz<br>ADC                    | -5                                             | 5                                              | Counts |  |

| GAINVGA2             | СС   | D |                                                                                  | 16 MHz<br>ADC                   | -8                                             | 8                                              | Counts |  |

|                      | СС   | D |                                                                                  | 8 MHz<br>ADC                    | -3                                             | 3                                              | Counts |  |

|                      | СС   | D | DNL                                                                              | 16 MHz<br>ADC                   | -3                                             | 3                                              | Counts |  |

|                      | CC   | _ | Variable gain ampli                                                              | ifier accurac                   | cy (gain=4) <sup>(2)</sup>                     |                                                |        |  |

|                      | СС   | D | INL                                                                              | 8 MHz<br>ADC                    | -7                                             | 7                                              | Counts |  |

| GAINVGA4             | СС   | D |                                                                                  | 16 MHz<br>ADC                   | -8                                             | 8                                              | Counts |  |

|                      | СС   | D |                                                                                  | 8 MHz<br>ADC                    | -4                                             | 4                                              | Counts |  |

|                      | СС   | D | DNL                                                                              | 16 MHz<br>ADC                   | -4                                             | 4                                              | Counts |  |

| DIFF <sub>max</sub>  | СС   | С | Maximum                                                                          | PREGAIN<br>set to 1X<br>setting | _                                              | (VRH - VRL)/2                                  | v      |  |

| DIFF <sub>max2</sub> | СС   | С | differential voltage<br>(DANx+ - DANx-)<br>or (DANx                              | PREGAIN<br>set to 2X<br>setting | _                                              | (VRH - VRL)/4                                  | v      |  |

| DIFF <sub>max4</sub> | СС   | С | DANx+) <sup>(5)</sup>                                                            | PREGAIN<br>set to 4X<br>setting | _                                              | (VRH - VRL)/8                                  | V      |  |

| DIFF <sub>cmv</sub>  | СС   | С | Differential input<br>Common mode<br>voltage (DANx- +<br>DANx+)/2 <sup>(5)</sup> | _                               | (V <sub>RH</sub> + V <sub>RL</sub> )/2 -<br>5% | (V <sub>RH</sub> + V <sub>RL</sub> )/2 +<br>5% | v      |  |

| Table 30. | eQADC differential ended convers | ion specifications (o | perating) (continued) |

|-----------|----------------------------------|-----------------------|-----------------------|

|-----------|----------------------------------|-----------------------|-----------------------|

1. Applies only to differential channels.

Variable gain is controlled by setting the PRE\_GAIN bits in the ADC\_ACR1-8 registers to select a gain factor of ×1, ×2, or ×4. Settings are for differential input only. Tested at ×1 gain. Values for other settings are guaranteed by as indicated.

3. At  $V_{RH}-V_{RL}$  = 5.12 V, one LSB = 1.25 mV.

4. Guaranteed 10-bit mono tonicity.

5. Voltages between VRL and VRH will not cause damage to the pins. However, they may not be converted accurately if the differential voltage is above the maximum differential voltage. In addition, conversion errors may occur if the common mode voltage of the differential signal violates the Differential Input common mode voltage specification.

| # | Symbol                   |        | Symbol |                                             | С   | Parameter | Min.<br>Value | Typical<br>Value | Initial<br>Max <sup>(2)</sup> | Max <sup>(3)</sup> | Unit |

|---|--------------------------|--------|--------|---------------------------------------------|-----|-----------|---------------|------------------|-------------------------------|--------------------|------|

| 5 | T <sub>64kpperase</sub>  | C<br>C | Ρ      | 64 KB Block Pre-program and Erase<br>Time   | _   | 800       | 1800          | 5000             | ms                            |                    |      |

| 6 | T <sub>128kpperase</sub> | C<br>C | Ρ      | 128 KB Block Pre-program and Erase<br>Time  | _   | 1500      | 3000          | 7500             | ms                            |                    |      |

| 7 | T <sub>256kpperase</sub> | C<br>C | Ρ      | 256 KB Block Pre-program and Erase<br>Time  | _   | 3000      | 5300          | 15000            | ms                            |                    |      |

| 8 | T <sub>psrt</sub>        | SR     | —      | Program suspend request rate <sup>(5)</sup> | 100 | —         | —             | —                | μs                            |                    |      |

| 9 | T <sub>esrt</sub>        | SR     | —      | Erase suspend request rate <sup>(6)</sup>   | 10  |           |               |                  | ms                            |                    |      |

Table 33.

Flash program and erase specifications<sup>(1)</sup> (continued)

1. Typical program and erase times assume nominal supply values and operation at 25 °C. All times are subject to change pending device characterization.

2. Initial factory condition: ≤ 100 program/erase cycles, 25 °C, typical supply voltage, 80 MHz minimum system frequency.

- 3. The maximum erase time occurs after the specified number of program/erase cycles. This maximum value is characterized but not guaranteed.

- 4. Page size is 128 bits (4 words).

- 5. Time between program suspend resume and the next program suspend request.

- 6. Time between erase suspend resume and the next erase suspend request.

## Table 34. Flash module life

| Symbo                | Symbol C |     | Parameter                                                                                                                                         | Conditions                                 | Val     | Unit    |               |

|----------------------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------|---------|---------------|

| Symbo                |          |     | Fatameter                                                                                                                                         | Conditions                                 | min     | typ     | Onic          |

| P/E                  | СС       | с   | Number of program/erase<br>cycles per block for 16 KB,<br>48 KB, and 64 Kbyte blocks<br>over the operating<br>temperature range (T <sub>J</sub> ) | _                                          | 100,000 | _       | P/E<br>cycles |

| P/E                  | сс       | С   | Number of program/erase<br>cycles per block for<br>128 Kbyte and 256 Kbyte<br>blocks over the operating<br>temperature range (T <sub>J</sub> )    | _                                          | 1,000   | 100,000 | P/E<br>cycles |

|                      |          |     |                                                                                                                                                   | Blocks with 0 – 1,000<br>P/E cycles        | 20      | _       | years         |

| Data<br>Retention CC | сс       | c c | Minimum data retention at<br>85 °C average ambient<br>temperature <sup>(1)</sup>                                                                  | Blocks with 1,001 –<br>10,000 P/E cycles   | 10      | _       | years         |

|                      |          |     |                                                                                                                                                   | Blocks with 10,001 –<br>100,000 P/E cycles | 5       | _       | years         |

1. Ambient temperature averaged over duration of application, not to exceed product operating temperature range.

# **3.16 AC** specifications

# 3.16.1 Pad AC specifications

## Table 35. Pad AC specifications (5.0 V)<sup>(1)</sup>

| Name                          |     |   | Output Delay<br>(ns) <sup>(2),(3)</sup><br>Low-to-High / High-<br>to-Low |           | Rise/Fall Ec | lge (ns) <sup>(3),(4)</sup> | Drive Load<br>(pF) | SRC/DSC           |

|-------------------------------|-----|---|--------------------------------------------------------------------------|-----------|--------------|-----------------------------|--------------------|-------------------|

|                               |     |   | Min                                                                      | Max       | Min          | Мах                         |                    | MSB,LSB           |

|                               | CC  | D | 4.6/3.7                                                                  | 12/12     | 2.2/2.2      | 7/7                         | 50                 | 11 <sup>(8)</sup> |

| Medium <sup>(5),(6),(7)</sup> |     |   |                                                                          |           | N/A          |                             |                    | 10 <sup>(9)</sup> |

| Medium                        | CC  | D | 12/13                                                                    | 28/34     | 5.6/6        | 15/15                       | 50                 | 01                |

|                               | CC  | D | 69/71                                                                    | 152/165   | 34/35        | 74/74                       | 50                 | 00                |

|                               | CC  | D | 7.3/5.7                                                                  | 19/18     | 4.4/4.3      | 14/14                       | 50                 | 11 <sup>(8)</sup> |

| Slow <sup>(7),(10)</sup>      | N/A |   |                                                                          |           |              |                             |                    | 10 <sup>(9)</sup> |

| Slow                          | CC  | D | 26/27                                                                    | 61/69     | 13/13        | 34/34                       | 50                 | 01                |

|                               | CC  | D | 137/142                                                                  | 320/330   | 72/74        | 164/164                     | 50                 | 00                |

|                               | CC  | D | 4.1/3.6                                                                  | 10.3/8.9  | 3.28/2.98    | 8/8                         | 50                 | 11 <sup>(8)</sup> |

| MultiV <sup>(11)</sup>        | N/A |   |                                                                          |           |              |                             |                    | 10 <sup>(9)</sup> |

| (High Swing Mode)             | CC  | D | 8.38/6.11                                                                | 16/12.9   | 5.48/4.81    | 11/11                       | 50                 | 01                |

|                               | CC  | D | 61.7/10.4                                                                | 92.2/24.3 | 42.0/12.2    | 63/63                       | 50                 | 00                |

| MultiV<br>(Low Swing Mode)    | сс  | D | 2.31/2.34                                                                | 7.62/6.33 | 1.26/1.67    | 6.5/4.4                     | 30                 | 11 <sup>(8)</sup> |

| Fast <sup>(12)</sup>          | N/A |   |                                                                          |           |              |                             |                    |                   |

| pad_i_hv <sup>(13)</sup>      | СС  | D | 0.5/0.5                                                                  | 1.9/1.9   | 0.3/0.3      | ±1.5/1.5                    | 0.5                | N/A               |

| pull_hv                       | CC  | D | NA                                                                       | 6000      |              | 5000/5000                   | 50                 | N/A               |

1. These are worst case values that are estimated from simulation and not tested. The values in the table are simulated at  $V_{DD}$  = 1.14 V to 1.32 V,  $V_{DDEH}$  = 4.5 V to 5.5 V,  $T_A$  =  $T_L$  to  $T_H$

- 2. This parameter is supplied for reference and is not guaranteed by design and not tested.

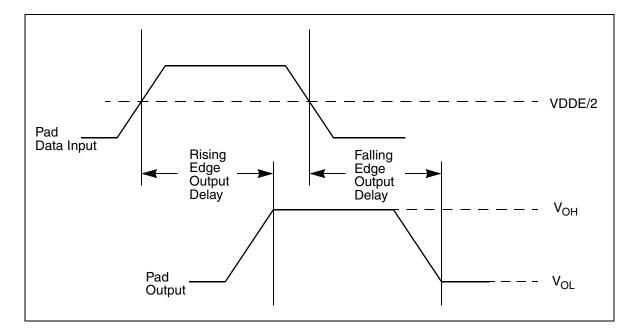

- 3. Delay and rise/fall are measured to 20% or 80% of the respective signal.

- 4. This parameter is guaranteed by characterization before qualification rather than 100% tested.

- 5. In high swing mode, high/low swing pad Vol and Voh values are the same as those of the slew controlled output pads

- 6. Medium Slew-Rate Controlled Output buffer. Contains an input buffer and weak pullup/pulldown.

- 7. Output delay is shown in *Figure 9: Pad output delay*. Add a maximum of one system clock to the output delay for delay with respect to system clock.

- 8. Can be used on the tester.

- 9. This drive select value is not supported. If selected, it will be approximately equal to 11.

- 10. Slow Slew-Rate Controlled Output buffer. Contains an input buffer and weak pullup/pulldown.

- 11. Selectable high/low swing IO pad with selectable slew in high swing mode only.

- 12. Fast pads are 3.3 V pads.

- 13. Stand alone input buffer. Also has weak pull-up/pull-down.

- 4. This parameter is guaranteed by characterization before qualification rather than 100% tested.

- 5. In high swing mode, high/low swing pad Vol and Voh values are the same as those of the slew controlled output pads

- 6. Medium Slew-Rate Controlled Output buffer. Contains an input buffer and weak pullup/pulldown.

- 7. Output delay is shown in *Figure 9*. Add a maximum of one system clock to the output delay for delay with respect to system clock.

- 8. Can be used on the tester.

- 9. This drive select value is not supported. If selected, it will be approximately equal to 11.

- 10. Slow Slew-Rate Controlled Output buffer. Contains an input buffer and weak pullup/pulldown.

- 11. Selectable high/low swing IO pad with selectable slew in high swing mode only.

- 12. Stand alone input buffer. Also has weak pull-up/pull-down.

Figure 9. Pad output delay

| #  | Symb               | vmbol C |   | Characteristic                                                                 | Min. Value                  | Max. Value | Unit |

|----|--------------------|---------|---|--------------------------------------------------------------------------------|-----------------------------|------------|------|

| 9  | t <sub>TCYC</sub>  | CC      | D | TCK Cycle Time                                                                 | 4 <sup>(6),(7)</sup>        | —          | tCYC |

| 9a | t <sub>TCYC</sub>  | СС      | D | Absolute Minimum TCK Cycle Time                                                | 100 <sup>(8)</sup>          | —          | ns   |

| 10 | t <sub>TDC</sub>   | СС      | D | TCK Duty Cycle                                                                 | 40                          | 60         | %    |

| 11 | t <sub>NTDIS</sub> | СС      | D | TDI Data Setup Time                                                            | 5                           | —          | ns   |

| 12 | t <sub>NTDIH</sub> | СС      | D | TDI Data Hold Time                                                             | 25                          | —          | ns   |

| 13 | t <sub>NTMSS</sub> | СС      | D | TMS Data Setup Time                                                            | 5                           | —          | ns   |

| 14 | t <sub>NTMSH</sub> | СС      | D | TMS Data Hold Time                                                             | FMS Data Hold Time   25   — |            | ns   |

| 15 | _                  | сс      | D | TDO propagation delay from falling edge of TCK                                 |                             |            | ns   |

| 16 | _                  | сс      | D | TDO hold time with respect to TCK falling edge (minimum TDO propagation delay) | 5.25                        | _          | ns   |

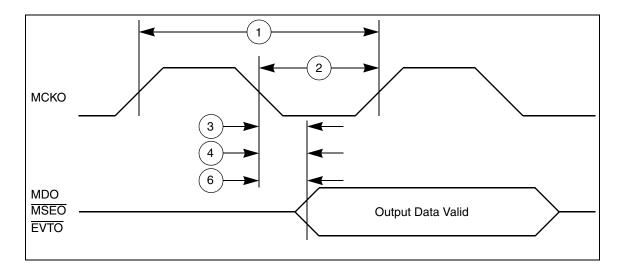

| Table 39. | Nexus debug port timing <sup>(1)</sup> (continued |

|-----------|---------------------------------------------------|

| Table 39. | Nexus debug port timing <sup>v</sup> (continued   |

1. All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal. Nexus timing specified at  $V_{DD} = 1.14$  V to 1.32 V,  $V_{DDEH} = 4.5$  V to 5.5 V with multi-voltage pads programmed to Low-Swing mode,  $T_A = T_L$  to  $T_H$ , and  $C_L = 30$  pF with DSC = 0b10.

- 2. Achieving the absolute minimum MCKO cycle time may require setting the MCKO divider to more than its minimum setting (NPC\_PCR[MCKO\_DIV] depending on the actual system frequency being used.

- 3. This is a functionally allowable feature. However, this may be limited by the maximum frequency specified by the Absolute minimum MCKO period specification.

- 4. This may require setting the MCO divider to more than its minimum setting (NPC\_PCR[MCKO\_DIV]) depending on the actual system frequency being used.

- 5. MDO, MSEO, and EVTO data is held valid until next MCKO low cycle.

- Achieving the absolute minimum TCK cycle time may require a maximum clock speed (system frequency / 8) that is less than the maximum functional capability of the design (system frequency / 4) depending on the actual system frequency being used.

- 7. This is a functionally allowable feature. However, this may be limited by the maximum frequency specified by the Absolute minimum TCK period specification.

- 8. This may require a maximum clock speed (system frequency / 8) that is less than the maximum functional capability of the design (system frequency / 4) depending on the actual system frequency being used.

Figure 15. Nexus output timing

57

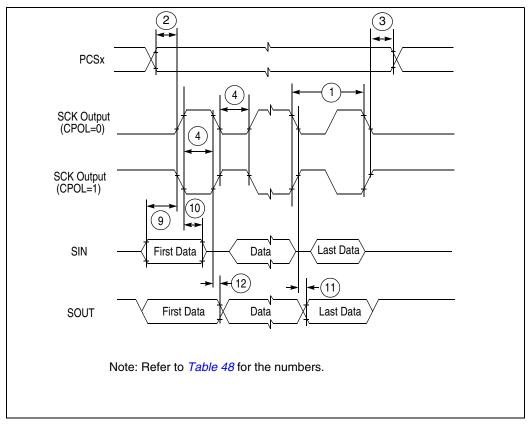

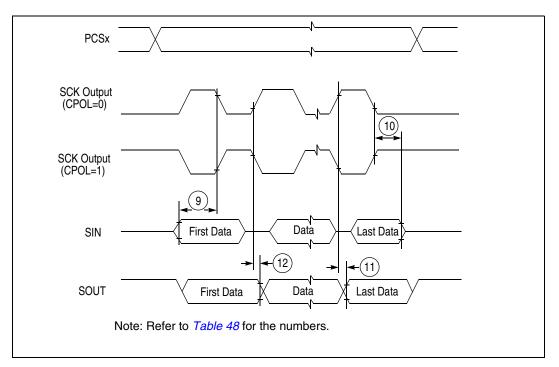

- 3. The minimum DSPI Cycle Time restricts the baud rate selection for given system clock rate. These numbers are calculated based on two SPC564A80 devices communicating over a DSPI link.

- 4. The actual minimum SCK cycle time is limited by pad performance.

- 5. For DSPI channels using LVDS output operation, up to 40 MHz SCK cycle time is supported. For non-LVDS output, maximum SCK frequency is 20 MHz. Appropriate clock division must be applied.

- 6. The maximum value is programmable in DSPI\_CTARx[PSSCK] and DSPI\_CTARx[CSSCK].

- 7. Timing met when pcssck = 3(01), and cssck = 2 (0000).

- 8. The maximum value is programmable in DSPI\_CTARx[PASC] and DSPI\_CTARx[ASC].

- 9. Timing met when ASC = 2 (0000), and PASC = 3 (01).

- 10. Timing met when pcssck = 3.

- 11. Timing met when ASC = 3.

- 12. This number is calculated assuming the SMPL\_PT bitfield in DSPI\_MCR is set to 0b10.

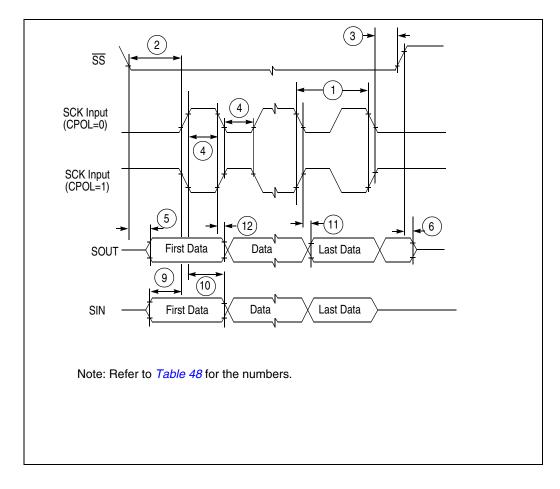

Figure 23. DSPI classic SPI timing — master, CPHA = 0

Figure 24. DSPI classic SPI timing — master, CPHA = 1

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02-Apr-2010 | 3        | Internal release.<br>Changes to Signal Properties table (changes apply to Revision 2 and later devices:<br>EBI changes:<br>- WE_BE[2] (A2) and CAL_WE_BE[2] (A3) signals added to CS[2] (PCR 2)<br>- WE_BE[3] (A2) and CAL_WE_BE[3] (A3) signals added to CS[3] (PCR 3)<br>Calibration bus changes:<br>- CAL_WE[3/BE[2] (A2) signal added to CAL_CS[2] (PCR 338)<br>- CAL_WE[3/BE[3] (A2) signal added to CAL_CS[3] (PCR 339)<br>- CAL_ALE (A1) added to CAL_ADDR[15] (PCR 340)<br>eQADC changes:<br>- AN[8] and AN[38] pins swapped. AN[8] Is now on pins 9 (176-pin), B3 (208-ball) and<br>D6 (324-ball). AN[8] was on C5 (324-ball) on previous devices. AN[38] Is now on C5<br>(324-ball). AN[38] was on pins 9 (176-pin), B3 (208-ball) and<br>D6 (324-ball). AN[38] was on pins 9 (176-pin), B3 (208-ball) and<br>D6 (324-ball). AN[38] was on pins 9 (176-pin), B3 (208-ball) and D6 (324-ball) on<br>previous devices.<br>- ANZ function added to AN11 pin<br>Reaction channels added to ETPU_A[14] (PCR 128)<br>- RCH0_A (A3) added to ETPU_A[12] (PCR 134)<br>- RCH0_C (A2) added to ETPU_A[12] (PCR 135)<br>- RCH1_A (A2) added to ETPU_A[12] (PCR 123)<br>- RCH1_A (A2) added to ETPU_A[13] (PCR 123)<br>- RCH1_C (A2) added to ETPU_A[16] (PCR 130)<br>- RCH3_A (A2) added to ETPU_A[17] (PCR 131)<br>- RCH4_A (A2) added to ETPU_A[16] (PCR 132))<br>- RCH4_B (A2) added to ETPU_A[17] (PCR 132))<br>- RCH4_B (A2) added to ETPU_A[18] (PCR 132))<br>- RCH4_B (A2) added to ETPU_A[19] (PCR 133)<br>- RCH5_B (A2) added to ETPU_A[28] (PCR 142)<br>- RCH5_C (A2) added to ETPU_A[28] (PCR 143)<br>- RCH5_B (A2) added to ETPU_A[28] (PCR 143)<br>- RCH5_B (A2) added to EMIOS[2] (PCR 181)<br>- RCH2_B (A2) added to EMIOS[2] (PCR 183)<br>- RCH3_B (A2) added to EMIOS[2] (PCR 183)<br>- RCH3_B (A2) added to EMIOS[4] (PCR |

## Table 56. Revision history (continued)

# Table 56. Revision history (continued)