Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                 |

|----------------------------|----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                     |

| Speed                      | 80MHz                                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                             |

| Number of I/O              | 38                                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 64K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                           |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                                  |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 48-LQFP                                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l433cbt6                  |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 27.3.4  | Capture/compare channels                          | 784 |

|------|---------|---------------------------------------------------|-----|

|      | 27.3.5  | Input capture mode                                | 786 |

|      | 27.3.6  | PWM input mode                                    | 787 |

|      | 27.3.7  | Forced output mode                                | 788 |

|      | 27.3.8  | Output compare mode                               | 789 |

|      | 27.3.9  | PWM mode                                          | 790 |

|      | 27.3.10 | Asymmetric PWM mode                               | 793 |

|      | 27.3.11 | Combined PWM mode                                 | 794 |

|      | 27.3.12 | Clearing the OCxREF signal on an external event   | 795 |

|      | 27.3.13 | One-pulse mode                                    | 797 |

|      | 27.3.14 | Retriggerable one pulse mode (OPM)                | 798 |

|      | 27.3.15 | Encoder interface mode                            | 799 |

|      | 27.3.16 | UIF bit remapping                                 | 801 |

|      | 27.3.17 | Timer input XOR function                          | 801 |

|      | 27.3.18 | Timers and external trigger synchronization       | 802 |

|      | 27.3.19 | Timer synchronization                             | 805 |

|      | 27.3.20 | DMA burst mode                                    | 809 |

|      | 27.3.21 | Debug mode                                        | 810 |

| 27.4 | TIM2/TI | IM3 registers                                     | 811 |

|      | 27.4.1  | TIMx control register 1 (TIMx_CR1)                | 811 |

|      | 27.4.2  | TIMx control register 2 (TIMx_CR2)                | 812 |

|      | 27.4.3  | TIMx slave mode control register (TIMx_SMCR)      | 814 |

|      | 27.4.4  | TIMx DMA/Interrupt enable register (TIMx_DIER)    | 817 |

|      | 27.4.5  | TIMx status register (TIMx_SR)                    | 818 |

|      | 27.4.6  | TIMx event generation register (TIMx_EGR)         | 819 |

|      | 27.4.7  | TIMx capture/compare mode register 1 (TIMx_CCMR1) | 820 |

|      | 27.4.8  | TIMx capture/compare mode register 2 (TIMx_CCMR2) | 824 |

|      | 27.4.9  | TIMx capture/compare enable register (TIMx_CCER)  | 826 |

|      | 27.4.10 | TIMx counter (TIMx_CNT)                           | 827 |

|      | 27.4.11 | TIMx prescaler (TIMx_PSC)                         | 828 |

|      | 27.4.12 | TIMx auto-reload register (TIMx_ARR)              | 828 |

|      | 27.4.13 | TIMx capture/compare register 1 (TIMx_CCR1)       | 829 |

|      | 27.4.14 | TIMx capture/compare register 2 (TIMx_CCR2)       | 829 |

|      | 27.4.15 | TIMx capture/compare register 3 (TIMx_CCR3)       | 830 |

|      | 27.4.16 | TIMx capture/compare register 4 (TIMx_CCR4)       | 830 |

|      | 27.4.17 | TIMx DMA control register (TIMx_DCR)              | 831 |

|      | 27.4.18 | TIMx DMA address for full transfer (TIMx_DMAR)    | 831 |

DocID027295 Rev 3

## 7.3.4 Frequency error evaluation and automatic trimming

The measured frequency error is evaluated by comparing its value with a set of limits:

- TOLERANCE LIMIT, given directly in the FELIM field of the CRS\_CFGR register

- WARNING LIMIT, defined as 3 \* FELIM value

- OUTRANGE (error limit), defined as 128 \* FELIM value

The result of this comparison is used to generate the status indication and also to control the automatic trimming which is enabled by setting the AUTOTRIMEN bit in the CRS\_CR register:

- When the frequency error is below the tolerance limit, it means that the actual trimming

value in the TRIM field is the optimal one and that then, no trimming action is

necessary.

- SYNCOK status indicated

- TRIM value not changed in AUTOTRIM mode

- When the frequency error is below the warning limit but above or equal to the tolerance limit, it means that some trimming action is necessary but that adjustment by one trimming step is enough to reach the optimal TRIM value.

- SYNCOK status indicated

- TRIM value adjusted by one trimming step in AUTOTRIM mode

- When the frequency error is above or equal to the warning limit but below the error limit, it means that a stronger trimming action is necessary, and there is a risk that the optimal TRIM value will not be reached for the next period.

- SYNCWARN status indicated

- TRIM value adjusted by two trimming steps in AUTOTRIM mode

- When the frequency error is above or equal to the error limit, it means that the frequency is out of the trimming range. This can also happen when the SYNC input is not clean or when some SYNC pulse is missing (for example when one USB SOF is corrupted).

- SYNCERR or SYNCMISS status indicated

- TRIM value not changed in AUTOTRIM mode

- Note: If the actual value of the TRIM field is so close to its limits that the automatic trimming would force it to overflow or underflow, then the TRIM value is set just to the limit and the TRIMOVF status is indicated.

In AUTOTRIM mode (AUTOTRIMEN bit set in the CRS\_CR register), the TRIM field of CRS\_CR is adjusted by hardware and is read-only.

## 7.3.5 CRS initialization and configuration

## **RELOAD** value

The RELOAD value should be selected according to the ratio between the target frequency and the frequency of the synchronization source after prescaling. It is then decreased by one in order to reach the expected synchronization on the zero value. The formula is the following:

$RELOAD = (f_{TARGET} / f_{SYNC}) - 1$

The reset value of the RELOAD field corresponds to a target frequency of 48 MHz and a synchronization signal frequency of 1 kHz (SOF signal from USB).

Bits 31:17 Reserved, must be kept at reset value.

Bit 16 LCKK: Lock key

This bit can be read any time. It can only be modified using the lock key write sequence.

0: Port configuration lock key not active

1: Port configuration lock key active. The GPIOx\_LCKR register is locked until the next MCU reset or peripheral reset.

LOCK key write sequence:

WR LCKR[16] = '1' + LCKR[15:0] WR LCKR[16] = '0' + LCKR[15:0] WR LCKR[16] = '1' + LCKR[15:0]

RD LCKR

- RD LCKR[16] = '1' (this read operation is optional but it confirms that the lock is active)

- Note: During the LOCK key write sequence, the value of LCK[15:0] must not change. Any error in the lock sequence aborts the lock.

After the first lock sequence on any bit of the port, any read access on the LCKK bit will return '1' until the next MCU reset or peripheral reset.

Bits 15:0 **LCKy:** Port x lock bit y (y= 0..15)

These bits are read/write but can only be written when the LCKK bit is '0.

- 0: Port configuration not locked

- 1: Port configuration locked

## 8.4.9 GPIO alternate function low register (GPIOx\_AFRL) (x = A..E and H)

Address offset: 0x20

Reset value: 0x0000 0000

| 31 | 30    | 29      | 28 | 27 | 26    | 25      | 24 | 23 | 22    | 21      | 20 | 19 | 18   | 17      | 16 |

|----|-------|---------|----|----|-------|---------|----|----|-------|---------|----|----|------|---------|----|

|    | AFSEI | _7[3:0] |    |    | AFSEL | _6[3:0] |    |    | AFSEI | _5[3:0] |    |    | AFSE | L4[3:0] |    |

| rw | rw    | rw      | rw | rw | rw    | rw      | rw | rw | rw    | rw      | rw | rw | rw   | rw      | rw |

| 15 | 14    | 13      | 12 | 11 | 10    | 9       | 8  | 7  | 6     | 5       | 4  | 3  | 2    | 1       | 0  |

|    | AFSEI | _3[3:0] |    |    | AFSEL | .2[3:0] |    |    | AFSEI | _1[3:0] |    |    | AFSE | L0[3:0] |    |

| rw | rw    | rw      | rw | rw | rw    | rw      | rw | rw | rw    | rw      | rw | rw | rw   | rw      | rw |

Bits 31:0 **AFSELy[3:0]:** Alternate function selection for port x pin y (y = 0..7) These bits are written by software to configure alternate function I/Os

AFSELy selection:

| 0000: AF0 | 1000: AF8  |

|-----------|------------|

| 0001: AF1 | 1001: AF9  |

| 0010: AF2 | 1010: AF10 |

| 0011: AF3 | 1011: AF11 |

| 0100: AF4 | 1100: AF12 |

| 0101: AF5 | 1101: AF13 |

| 0110: AF6 | 1110: AF14 |

| 0111: AF7 | 1111: AF15 |

|           |            |

The QUADSPI IP is configured using the QUADSPI\_CR. The user shall configure the clock prescaler division factor and the sample shifting settings for the incoming data.

DDR mode can be set through the DDRM bit. Once enabled, the address and the alternate bytes are sent on both clock edges and the data are sent/received on both clock edges. Regardless of the DDRM bit setting, instructions are always sent in SDR mode.

The DMA requests are enabled setting the DMAEN bit. In case of interrupt usage, their respective enable bit can be also set during this phase.

FIFO level for either DMA request generation or interrupt generation is programmed in the FTHRES bits.

If timeout counter is needed, the TCEN bit can be set and the timeout value programmed in the QUADSPI\_LPTR register.

Dual-flash mode can be activated by setting DFM to 1.

#### QUADSPI Flash memory configuration

The parameters related to the targeted external Flash memory are configured through the QUADSPI\_DCR register. The user shall program the Flash memory size in the FSIZE bits, the Chip Select minimum high time in the CSHT bits, and the functional mode (Mode 0 or Mode 3) in the MODE bit.

## 15.3.11 QUADSPI usage

The operating mode is selected using FMODE[1:0] (QUADSPI\_CCR[27:26]).

#### Indirect mode procedure

When FMODE is programmed to 00, indirect write mode is selected and data can be sent to the Flash memory. With FMODE = 01, indirect read mode is selected where data can be read from the Flash memory.

When the QUADSPI is used in indirect mode, the frames are constructed in the following way:

- 1. Specify a number of data bytes to read or write in the QUADSPI\_DLR.

- 2. Specify the frame format, mode and instruction code in the QUADSPI\_CCR.

- 3. Specify optional alternate byte to be sent right after the address phase in the QUADSPI\_ABR.

- 4. Specify the operating mode in the QUADSPI\_CR. If FMODE = 00 (indirect write mode) and DMAEN = 1, then QUADSPI\_AR should be specified before QUADSPI\_CR, because otherwise QUADSPI\_DR might be written by the DMA before QUADSPI\_AR is updated (if the DMA controller has already been enabled)

- 5. Specify the targeted address in the QUADSPI\_AR.

- 6. Read/Write the data from/to the FIFO through the QUADSPI\_DR.

## 16.4.5 Slave AHB interface

The ADC implements an AHB slave port for control/status register and data access. The features of the AHB interface are listed below:

- Word (32-bit) accesses

- Single cycle response

- Response to all read/write accesses to the registers with zero wait states.

The AHB slave interface does not support split/retry requests, and never generates AHB errors.

# 16.4.6 ADC Deep-power-down mode (DEEPPWD) & ADC Voltage Regulator (ADVREGEN)

By default, the ADC is in Deep-power-down mode where its supply is internally switched off to reduce the leakage currents (the reset state of bit DEEPPWD is 1 in the ADC\_CR register).

To start ADC operations, it is first needed to exit Deep-power-down mode by setting bit DEEPPWD=0.

Then, it is mandatory to enable the ADC internal voltage regulator by setting the bit ADVREGEN=1 into ADC\_CR register. The software must wait for the startup time of the ADC voltage regulator ( $T_{ADCVREG\_STUP}$ ) before launching a calibration or enabling the ADC. This delay must be implemented by software.

For the startup time of the ADC voltage regulator, please refer to device datasheet for  $T_{ADCVREG\ STUP}$  parameter.

After ADC operations are complete, the ADC can be disabled (ADEN=0). It is possible to save power by also disabling the ADC voltage regulator. This is done by writing bit ADVREGEN=0.

Then, to save more power by reducing the leakage currents, it is also possible to re-enter in ADC Deep-power-down mode by setting bit DEEPPWD=1 into ADC\_CR register. This is particularly interesting before entering STOP mode.

*Note:* Writing DEEPPWD=1 automatically disables the ADC voltage regulator and bit ADVREGEN is automatically cleared.

When the internal voltage regulator is disabled (ADVREGEN=0), the internal analog calibration is kept.

In ADC Deep-power-down mode (DEEPPWD=1), the internal analog calibration is lost and it is necessary to either relaunch a calibration or re-apply the calibration factor which was previously saved (refer to *Section 16.4.8: Calibration (ADCAL, ADCALDIF, ADC\_CALFACT)*).

| RES<br>(bits) | T <sub>SAR</sub><br>(ADC clock cycles) | T <sub>SAR</sub> (ns) at<br>F <sub>ADC</sub> =80 MHz | T <sub>CONV</sub> (ADC clock cycles)<br>(with Sampling Time=<br>2.5 ADC clock cycles) | T <sub>CONV</sub> (ns) at<br>F <sub>ADC</sub> =80 MHz |

|---------------|----------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------|

| 12            | 12.5 ADC clock cycles                  | 156.25 ns                                            | 15 ADC clock cycles                                                                   | 187.5 ns                                              |

| 10            | 10.5 ADC clock cycles                  | 131.25 ns                                            | 13 ADC clock cycles                                                                   | 162.5 ns                                              |

| 8             | 8.5 ADC clock cycles                   | 106.25 ns                                            | 11 ADC clock cycles                                                                   | 137.5 ns                                              |

| 6             | 6.5 ADC clock cycles                   | 81.25 ns                                             | 9 ADC clock cycles                                                                    | 112.5 ns                                              |

Table 60. T<sub>SAR</sub> timings depending on resolution

## 16.4.23 End of conversion, end of sampling phase (EOC, JEOC, EOSMP)

The ADC notifies the application for each end of regular conversion (EOC) event and each injected conversion (JEOC) event.

The ADC sets the EOC flag as soon as a new regular conversion data is available in the ADC\_DR register. An interrupt can be generated if bit EOCIE is set. EOC flag is cleared by the software either by writing 1 to it or by reading ADC\_DR.

The ADC sets the JEOC flag as soon as a new injected conversion data is available in one of the ADC\_JDRy register. An interrupt can be generated if bit JEOCIE is set. JEOC flag is cleared by the software either by writing 1 to it or by reading the corresponding ADC\_JDRy register.

The ADC also notifies the end of Sampling phase by setting the status bit EOSMP (for regular conversions only). EOSMP flag is cleared by software by writing 1 to it. An interrupt can be generated if bit EOSMPIE is set.

## 16.4.24 End of conversion sequence (EOS, JEOS)

The ADC notifies the application for each end of regular sequence (EOS) and for each end of injected sequence (JEOS) event.

The ADC sets the EOS flag as soon as the last data of the regular conversion sequence is available in the ADC\_DR register. An interrupt can be generated if bit EOSIE is set. EOS flag is cleared by the software either by writing 1 to it.

The ADC sets the JEOS flag as soon as the last data of the injected conversion sequence is complete. An interrupt can be generated if bit JEOSIE is set. JEOS flag is cleared by the software either by writing 1 to it.

| Source | Туре                 | TSELx[2:0] |

|--------|----------------------|------------|

| EXTI9  | External pin         | 110        |

| SWTRIG | Software control bit | 111        |

| Table 72. DAC trigger | selection | (continued) |

|-----------------------|-----------|-------------|

|-----------------------|-----------|-------------|

1. Reserved on STM32L45xxx and STM32L46xxx devices.

## 17.4.7 DMA request

Each DAC channel has a DMA capability. Two DMA channels are used to service DAC channel DMA requests.

A DAC DMA request is generated when an external trigger (but not a software trigger) occurs while the DMAENx bit is set. The value of the DAC\_DHRx register is then transferred into the DAC\_DORx register.

In dual mode, if both DMAENx bits are set, two DMA requests are generated. If only one DMA request is needed, you should set only the corresponding DMAENx bit. In this way, the application can manage both DAC channels in dual mode by using one DMA request and a unique DMA channel.

## DMA underrun

The DAC DMA request is not queued so that if a second external trigger arrives before the acknowledgment for the first external trigger is received (first request), then no new request is issued and the DMA channelx underrun flag DMAUDRx in the DAC\_SR register is set, reporting the error condition. The DAC channelx continues to convert old data.

The software should clear the DMAUDRx flag by writing "1", clear the DMAEN bit of the used DMA stream and re-initialize both DMA and DAC channelx to restart the transfer correctly. The software should modify the DAC trigger conversion frequency or lighten the DMA workload to avoid a new DMA underrun. Finally, the DAC conversion could be resumed by enabling both DMA data transfer and conversion trigger.

For each DAC channelx, an interrupt is also generated if its corresponding DMAUDRIEx bit in the DAC\_CR register is enabled.

## 17.4.8 Noise generation

In order to generate a variable-amplitude pseudonoise, an LFSR (linear feedback shift register) is available. DAC noise generation is selected by setting WAVEx[1:0] to "01". The preloaded value in LFSR is 0xAAA. This register is updated three APB1 clock cycles after each trigger event, following a specific calculation algorithm.

| 31   | 30   | 29   | 28   | 27   | 26   | 25             | 24   | 23   | 22   | 21   | 20   | 19        | 18        | 17        | 16        |

|------|------|------|------|------|------|----------------|------|------|------|------|------|-----------|-----------|-----------|-----------|

| Res.           | Res. | Res. | Res. | Res. | Res. | Res.      | Res.      | Res.      | Res.      |

|      |      |      |      |      |      |                |      |      |      |      |      |           |           |           |           |

|      |      | •    |      |      |      |                |      |      |      |      |      |           |           |           |           |

| 15   | 14   | 13   | 12   | 11   | 10   | 9              | 8    | 7    | 6    | 5    | 4    | 3         | 2         | 1         | 0         |

| 15   | 14   | 13   | 12   | 11   | -    | 9<br>DHR[11:0] |      | 7    | 6    | 5    | 4    | 3<br>Res. | 2<br>Res. | 1<br>Res. | 0<br>Res. |

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:4 **DACC1DHR[11:0]**: DAC channel1 12-bit left-aligned data

These bits are written by software which specifies 12-bit data for DAC channel1.

Bits 3:0 Reserved, must be kept at reset value.

# 17.6.5 DAC channel1 8-bit right aligned data holding register (DAC\_DHR8R1)

Address offset: 0x10

Reset value: 0x0000 0000

| 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20    | 19       | 18   | 17   | 16   |

|------|------|------|------|------|------|------|------|------|------|------|-------|----------|------|------|------|

| Res.  | Res.     | Res. | Res. | Res. |

|      |      |      |      |      |      |      |      |      |      |      |       |          |      |      |      |

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4     | 3        | 2    | 1    | 0    |

| Res. |      |      |      | DACC1 | DHR[7:0] |      |      |      |

|      |      |      |      |      |      |      |      | rw   | rw   | rw   | rw    | rw       | rw   | rw   | rw   |

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 DACC1DHR[7:0]: DAC channel1 8-bit right-aligned data

These bits are written by software which specifies 8-bit data for DAC channel1.

## 17.6.6 DAC channel2 12-bit right aligned data holding register (DAC\_DHR12R2)

Address offset: 0x14

Reset value: 0x0000 0000

| 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22     | 21       | 20   | 19   | 18   | 17   | 16   |

|------|------|------|------|------|------|------|------|------|--------|----------|------|------|------|------|------|

| Res.   | Res.     | Res. | Res. | Res. | Res. | Res. |

|      |      |      |      |      |      |      |      |      |        |          |      |      |      |      |      |

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6      | 5        | 4    | 3    | 2    | 1    | 0    |

| Res. | Res. | Res. | Res. |      |      |      |      |      | DACC2D | HR[11:0] |      |      |      |      |      |

|      |      |      |      | rw   | rw   | rw   | rw   | rw   | rw     | rw       | rw   | rw   | rw   | rw   | rw   |

Bits 31:12 Reserved, must be kept at reset value.

Bits 11:0 DACC2DHR[11:0]: DAC channel2 12-bit right-aligned data

These bits are written by software which specifies 12-bit data for DAC channel2.

## 25.5.2 Cipher block chaining (CBC)

In cipher-block chaining (CBC) mode, each block of plain text is XORed with the previous cipher text block before being encrypted. To make each message unique, an initialization vector (AES\_IVRx) is used during the first block processing.

The initialization vector is XORed after the swapping management block during encryption mode and before it in decryption mode (refer to *Figure 139* and *Figure 140*).

#### Suspended mode for a given message

It is possible to suspend a message if another message with a higher priority needs to be processed. After sending this highest priority message, the suspended message may be resumed in both encryption or decryption mode. This feature is available only when the data transfer is done by CPU accesses to the AES\_DOUTR and AES\_DINR registers. It is advised to not use it when the DMA controller is managing the data transfer.

For correct operation, the message must be suspended at the end of a block processing (after the fourth read of the AES\_DOUTR register and before the next AES\_DINR write access corresponding to the input of the next block to be processed).

The AES should be disabled writing bit EN = 0 in the AES\_CR register. The software has to read the AES\_IVRx which contains the latest value to be used for the chaining XOR operation before message interruption. This value has to be stored for reuse by writing the AES\_IVRx registers as soon as the interrupted message has to be resumed (when AES is disabled).

*Note:* This does not break the chaining operation and the message processing can be resumed as soon as the AES is enabled again to send the next 128-bit data block.

Note: This behavior is valid whatever the AES configuration (encryption or decryption mode).

*Figure 141* gives an example of a message 1 which is suspended in order to send a higher priority message 2, shorter than message 1. At the end of the 128-bit block processing, AES is disabled. The AES\_IVR register is read back to store the value to be retrieved later on when the message is resumed, in order not to break the chaining operation. Then, the AES is configured to send message 2 and it is enabled to start processing. At the end of message 2 processing, AES has to be disabled again and the AES\_IVRx registers have to be loaded with the value previously stored when the message 1 was interrupted. Then software has to restart from the input value corresponding to block 4 as soon as AES is enabled to resume message 1.

The OPM waveform is defined by writing the compare registers (taking into account the clock frequency and the counter prescaler).

- The t<sub>DELAY</sub> is defined by the value written in the TIMx\_CCR1 register.

- The t<sub>PULSE</sub> is defined by the difference between the auto-reload value and the compare value (TIMx\_ARR - TIMx\_CCR1).

- Let's say you want to build a waveform with a transition from '0' to '1' when a compare match occurs and a transition from '1' to '0' when the counter reaches the auto-reload value. To do this you enable PWM mode 2 by writing OC1M=111 in the TIMx\_CCMR1 register. You can optionally enable the preload registers by writing OC1PE='1' in the TIMx\_CCMR1 register and ARPE in the TIMx\_CR1 register. In this case you have to write the compare value in the TIMx\_CCR1 register, the auto-reload value in the TIMx\_ARR register, generate an update by setting the UG bit and wait for external trigger event on TI2. CC1P is written to '0' in this example.

You only want 1 pulse, so you write '1' in the OPM bit in the TIMx\_CR1 register to stop the counter at the next update event (when the counter rolls over from the auto-reload value back to 0).

#### Particular case: OCx fast enable

In One-pulse mode, the edge detection on TIx input set the CEN bit which enables the counter. Then the comparison between the counter and the compare value makes the output toggle. But several clock cycles are needed for these operations and it limits the minimum delay  $t_{\text{DELAY}}$  min we can get.

If you want to output a waveform with the minimum delay, you can set the OCxFE bit in the TIMx\_CCMRx register. Then OCxRef (and OCx) are forced in response to the stimulus, without taking in account the comparison. Its new level is the same as if a compare match had occurred. OCxFE acts only if the channel is configured in PWM1 or PWM2 mode.

## 28.4.15 UIF bit remapping

The IUFREMAP bit in the TIMx\_CR1 register forces a continuous copy of the Update Interrupt Flag UIF into bit 31 of the timer counter register (TIMxCNT[31]). This allows to atomically read both the counter value and a potential roll-over condition signaled by the UIFCPY flag. In particular cases, it can ease the calculations by avoiding race conditions caused for instance by a processing shared between a background task (counter reading) and an interrupt (Update Interrupt).

There is no latency between the assertions of the UIF and UIFCPY flags.

#### Bit 13 BKP: Break polarity

0: Break input BRK is active low

1: Break input BRK is active high

*Note:* **1:** This bit can not be modified as long as LOCK level 1 has been programmed (LOCK bits in TIMx\_BDTR register).

2: Any write operation to this bit takes a delay of 1 APB clock cycle to become effective.

Bit 12 BKE: Break enable

0: Break inputs (BRK and CCS clock failure event) disabled

1; Break inputs (BRK and CCS clock failure event) enabled

This bit cannot be modified when LOCK level 1 has been programmed (LOCK bits in TIMx\_BDTR register).

Note: Any write operation to this bit takes a delay of 1 APB clock cycle to become effective.

Bit 11 OSSR: Off-state selection for Run mode

This bit is used when MOE=1 on channels that have a complementary output which are configured as outputs. OSSR is not implemented if no complementary output is implemented in the timer.

See OC/OCN enable description for more details (*Section 28.5.8: TIM15 capture/compare enable register (TIM15\_CCER) on page 883*).

0: When inactive, OC/OCN outputs are disabled (the timer releases the output control which is taken over by the AFIO logic, which forces a Hi-Z state)

1: When inactive, OC/OCN outputs are enabled with their inactive level as soon as CCxE=1 or CCxNE=1 (the output is still controlled by the timer).

Note: This bit can not be modified as soon as the LOCK level 2 has been programmed (LOCK bits in TIMx\_BDTR register).

Bit 10 **OSSI**: Off-state selection for Idle mode

This bit is used when MOE=0 on channels configured as outputs. See OC/OCN enable description for more details (*Section 28.5.8: TIM15 capture/compare enable register (TIM15\_CCER) on page 883*).

0: When inactive, OC/OCN outputs are disabled (OC/OCN enable output signal=0) 1: When inactive, OC/OCN outputs are forced first with their idle level as soon as CCxE=1 or CCxNE=1. OC/OCN enable output signal=1)

Note: This bit can not be modified as soon as the LOCK level 2 has been programmed (LOCK bits in TIMx\_BDTR register).

#### Bits 9:8 LOCK[1:0]: Lock configuration

These bits offer a write protection against software errors.

00: LOCK OFF - No bit is write protected

01: LOCK Level 1 = DTG bits in TIMx\_BDTR register, OISx and OISxN bits in TIMx\_CR2 register and BKE/BKP/AOE bits in TIMx\_BDTR register can no longer be written 10: LOCK Level 2 = LOCK Level 1 + CC Polarity bits (CCxP/CCxNP bits in TIMx\_CCER register, as long as the related channel is configured in output through the CCxS bits) as well as OSSR and OSSI bits can no longer be written.

11: LOCK Level 3 = LOCK Level 2 + CC Control bits (OCxM and OCxPE bits in TIMx\_CCMRx registers, as long as the related channel is configured in output through the CCxS bits) can no longer be written.

Note: The LOCK bits can be written only once after the reset. Once the TIMx\_BDTR register has been written, their content is frozen until the next reset.

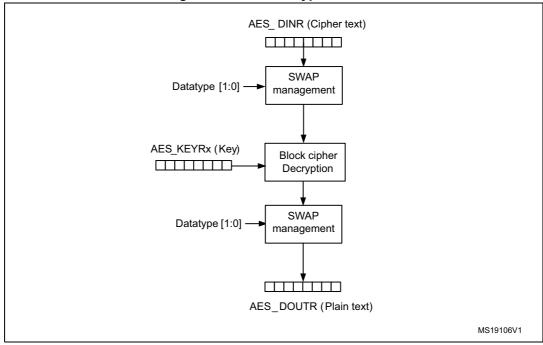

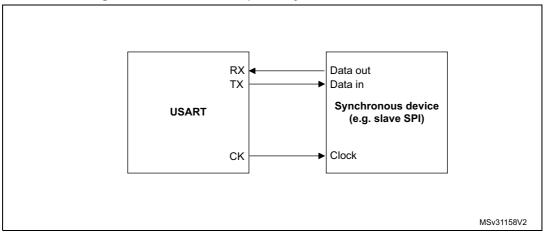

Note: The CK pin works in conjunction with the TX pin. Thus, the clock is provided only if the transmitter is enabled (TE=1) and data is being transmitted (the data register USART\_TDR written). This means that it is not possible to receive synchronous data without transmitting data.

The LBCL, CPOL and CPHA bits have to be selected when the USART is disabled (UE=0) to ensure that the clock pulses function correctly.

#### Figure 358. USART example of synchronous transmission

Figure 359. USART data clock timing diagram (M bits = 00)

RS232 RTS and CTS flow control can be enabled independently by writing the RTSE and CTSE bits respectively to 1 (in the USART\_CR3 register).

## RS232 RTS flow control

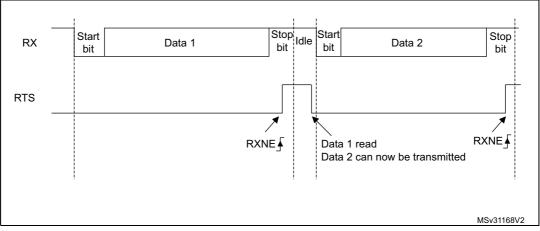

If the RTS flow control is enabled (RTSE=1), then RTS is asserted (tied low) as long as the USART receiver is ready to receive a new data. When the receive register is full, RTS is deasserted, indicating that the transmission is expected to stop at the end of the current frame. *Figure 369* shows an example of communication with RTS flow control enabled.

Figure 369. RS232 RTS flow control

## **RS232 CTS flow control**

If the CTS flow control is enabled (CTSE=1), then the transmitter checks the CTS input before transmitting the next frame. If CTS is asserted (tied low), then the next data is transmitted (assuming that data is to be transmitted, in other words, if TXE=0), else the transmission does not occur. when CTS is de-asserted during a transmission, the current transmission is completed before the transmitter stops.

When CTSE=1, the CTSIF status bit is automatically set by hardware as soon as the CTS input toggles. It indicates when the receiver becomes ready or not ready for communication. An interrupt is generated if the CTSIE bit in the USART\_CR3 register is set. *Figure 370* shows an example of communication with CTS flow control enabled.

## LPUART register map

The table below gives the LPUART register map and reset values.

Table 179. LPUART register map and reset values

| Image: constraint of the |        |                |      |      |       |            |      |      | _     |       |       |       |       | 3     |          |         |       |       |      | 116  |      | -      |      |       |       |      |                                              |      |        |        |       |      |       |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|------|------|-------|------------|------|------|-------|-------|-------|-------|-------|-------|----------|---------|-------|-------|------|------|------|--------|------|-------|-------|------|----------------------------------------------|------|--------|--------|-------|------|-------|------|

| Reset value         I         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th< th=""><th>Offset</th><th>Register</th><th>31</th><th>30</th><th>29</th><th>28</th><th>27</th><th>26</th><th>25</th><th>24</th><th>23</th><th>22</th><th>21</th><th>20</th><th>19</th><th>18</th><th>17</th><th>16</th><th>15</th><th>14</th><th>13</th><th>12</th><th>11</th><th>10</th><th>6</th><th>8</th><th>7</th><th>9</th><th>5</th><th>4</th><th>e</th><th>2</th><th>1</th><th>0</th></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Offset | Register       | 31   | 30   | 29    | 28         | 27   | 26   | 25    | 24    | 23    | 22    | 21    | 20    | 19       | 18      | 17    | 16    | 15   | 14   | 13   | 12     | 11   | 10    | 6     | 8    | 7                                            | 9    | 5      | 4      | e     | 2    | 1     | 0    |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x00   |                | Res. | Res. | Res.  | M1         | Res. | Res. | DEAT4 | DEAT3 | DEAT2 | DEAT1 | DEAT0 | DEDT4 | DEDT3    | DEDT2   | DEDT1 | DEDT0 | Res. | CMIE | MME  | Μ      | WAKE | PCE   | PS    | PEIE | TXEIE                                        | TCIE | RXNEIE | IDLEIE | TE    | RE   | UESM  | UE   |

| Reset value         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <t <="" td=""><td></td><td>Reset value</td><td></td><td></td><td></td><td>0</td><td></td><td></td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td></td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td></t>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | Reset value    |      |      |       | 0          |      |      | 0     | 0     | 0     | 0     | 0     | 0     | 0        | 0       | 0     | 0     |      | 0    | 0    | 0      | 0    | 0     | 0     | 0    | 0                                            | 0    | 0      | 0      | 0     | 0    | 0     | 0    |

| LPUART_CR3       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I <thi< td=""><td>0x04</td><td>LPUART_<br/>CR2</td><td>A</td><td>٩DD</td><td>0[7:4</td><td><b>!</b>]</td><td>ļ</td><td>٩DD</td><td>0[3:0</td><td>]</td><td>Res.</td><td>Res.</td><td>Res.</td><td>Res.</td><td>MSBFIRST</td><td>DATAINV</td><td>TXINV</td><td>RXINV</td><td>SWAP</td><td>Res.</td><td></td><td></td><td>Res.</td><td>Res.</td><td>Res.</td><td>Res.</td><td>Res.</td><td>Res.</td><td>Res.</td><td>ADDM7</td><td>Res.</td><td>Res.</td><td>Res.</td><td>Res.</td></thi<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0x04   | LPUART_<br>CR2 | A    | ٩DD  | 0[7:4 | <b>!</b> ] | ļ    | ٩DD  | 0[3:0 | ]     | Res.  | Res.  | Res.  | Res.  | MSBFIRST | DATAINV | TXINV | RXINV | SWAP | Res. |      |        | Res. | Res.  | Res.  | Res. | Res.                                         | Res. | Res.   | ADDM7  | Res.  | Res. | Res.  | Res. |

| Reset value       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I <th< td=""><td></td><td>Reset value</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td></td><td></td><td></td><td></td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td></td><td>0</td><td>0</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>0</td><td></td><td></td><td></td><td></td></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | Reset value    | 0    | 0    | 0     | 0          | 0    | 0    | 0     | 0     |       |       |       |       | 0        | 0       | 0     | 0     | 0    |      | 0    | 0      |      |       |       |      |                                              |      |        | 0      |       |      |       |      |

| LPUART_BRR       Image: Set value       Image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x08   |                | Res. | Res. | Res.  | Res.       | Res. | Res. | Res.  | Res.  | UCESM | WUFIE |       |       | Res.     | Res.    | Res.  | Res.  | DEP  | DEM  | DDRE | OVRDIS | Res. | CTSIE | CTSE  | RTSE | DMAT                                         | DMAR | Res.   | Res.   | HDSEL | Res. | Res.  | EIE  |

| OxOC         BRR         BRR <td></td> <td>Reset value</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td></td> <td></td> <td></td> <td></td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td></td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td></td> <td></td> <td>0</td> <td></td> <td></td> <td>0</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | Reset value    |      |      |       |            |      |      |       |       | 0     | 0     | 0     | 0     |          |         |       |       | 0    | 0    | 0    | 0      |      | 0     | 0     | 0    | 0                                            | 0    |        |        | 0     |      |       | 0    |

| 0x10-<br>0x14       LPUART_RQR       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x0C   |                | Res. | Res. | Res.  | Res.       | Res. | Res. | Res.  | Res.  | Res.  | Res.  | Res.  | Res.  |          |         |       |       |      |      |      |        | В    | RR[   | 19:0  | 0]   |                                              | 1    |        |        | 1     |      |       |      |

| 0x14       LPUART_RQR       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       a       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | Reset value    |      |      |       |            |      |      |       |       |       |       |       |       |          |         |       |       |      | 0    | 0    | 0      | 0    | 0     | 0     | 0    | 0                                            | 0    | 0      | 0      | 0     | 0    | 0     | 0    |

| Reset value       Image: Constraint of the c                 |        |                |      |      |       |            |      |      |       |       |       |       |       |       | R        | ese     | rveo  | ł     |      |      |      |        |      |       |       |      |                                              |      |        |        |       |      |       |      |

| Ox1C       LPUART_ISR       Image: Sector conditions and the sector conditions anditerations and the sector conditions and th                          | 0x18   |                | Res. | Res. | Res.  | Res.       | Res. | Res. | Res.  | Res.  | Res.  | Res.  | Res.  | Res.  | Res.     | Res.    | Res.  | Res.  | Res. | Res. | Res. | Res.   | Res. | Res.  | Res.  | Res. | Res.                                         | Res. | Res.   | Res.   | RXFRQ | MMRQ | SBKRQ | Res. |

| Reset value         0         0         0         0         0         0         0         0         0         0         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th< td=""><td></td><td>Reset value</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>0</td><td>0</td><td>0</td><td></td></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | Reset value    |      |      |       |            |      |      |       |       |       |       |       |       |          |         |       |       |      |      |      |        |      |       |       |      |                                              |      |        |        | 0     | 0    | 0     |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x1C   | LPUART_ISR     | Res. | Res. | Res.  | Res.       | Res. | Res. | Res.  | Res.  | Res.  | REACK | TEACK | WUF   | RWU      | SBKF    | CMF   | BUSY  | Res. | Res. | Res. | Res.   | Res. | CTS   | CTSIF | Res. | TXE                                          | TC   | RXNE   | IDLE   | ORE   | NF   | FE    | PE   |

| UPUART_ICR         Image: Constraint of the second sec         |        | Reset value    |      |      |       |            |      |      |       |       |       |       |       | 0     | 0        | 0       | 0     | 0     |      |      |      |        |      | 0     | 0     |      | 1                                            | 1    | 0      | 0      | 0     | 0    | 0     | 0    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x20   | LPUART_ICR     | Res. | Res. | Res.  | Res.       | Res. | Res. | Res.  | Res.  | Res.  | Res.  | Res.  | WUCF  | Res.     | Res.    | CMCF  | Res.  | Res. | Res. | Res. | Res.   | Res. | Res.  | CTSCF | Res. | Res.                                         | TCCF | Res.   | Res.   | ORECF | NCF  | FECF  | PECF |

| Reset value         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th< td=""><td></td><td>Reset value</td><td>F</td><td></td><td>F</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>0</td><td></td><td></td><td>0</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>0</td><td></td><td></td><td></td><td>0</td><td>0</td><td>0</td></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        | Reset value    | F    |      | F     |            |      |      |       |       |       |       |       | 0     |          |         | 0     |       |      |      |      |        |      |       |       |      |                                              | 0    |        |        |       | 0    | 0     | 0    |

| 0x24 LPUART_RDR 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x24   |                | Res. | Res. | Res.  | Res.       | Res. | Res. | Res.  | Res.  | Res.  | Res.  | Res.  | Res.  | Res.     | Res.    | Res.  | Res.  | Res. | Res. | Res. | Res.   | Res. | Res.  | Res.  |      | <u>.                                    </u> | 1    | R      | DR[8   | 3:0]  |      |       |      |

| Reset value         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X <th< td=""><td></td><td>Reset value</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>х</td><td>х</td><td>х</td><td>х</td><td>х</td><td>х</td><td>х</td><td>х</td><td>х</td></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | Reset value    |      |      |       |            |      |      |       |       |       |       |       |       |          |         |       |       |      |      |      |        |      |       |       | х    | х                                            | х    | х      | х      | х     | х    | х     | х    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x28   | LPUART_<br>TDR | Res. | Res. | Res.  | Res.       | Res. | Res. | Res.  | Res.  | Res.  | Res.  | Res.  | Res.  | Res.     | Res.    | Res.  | Res.  | Res. | Res. | Res. | Res.   | Res. | Res.  | Res.  |      |                                              | 1    | TC     | DR[8   | 3:0]  |      |       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | Reset value    |      |      |       |            |      |      |       |       |       |       |       |       |          |         |       |       |      |      |      |        |      |       |       | х    | х                                            | х    | х      | х      | х     | х    | х     | х    |

Refer to Section 2.2 on page 62 for the register boundary addresses.

1192/1415

37.7.10

DocID027295 Rev 3

RM0394

#### Bit 2 SSOE: SS output enable

0: SS output is disabled in master mode and the SPI interface can work in multimaster configuration

1: SS output is enabled in master mode and when the SPI interface is enabled. The SPI interface cannot work in a multimaster environment.

Note: This bit is not used in SPI TI mode.

#### Bit 1 TXDMAEN: Tx buffer DMA enable

When this bit is set, a DMA request is generated whenever the TXE flag is set.

- 0: Tx buffer DMA disabled

- 1: Tx buffer DMA enabled

#### Bit 0 **RXDMAEN:** Rx buffer DMA enable

When this bit is set, a DMA request is generated whenever the RXNE flag is set.

- 0: Rx buffer DMA disabled

- 1: Rx buffer DMA enabled

### **Frame length**

Master mode

The audio frame length can be configured to up to 256 bit clock cycles, by setting FRL[7:0] field in the SAI\_xFRCR register.

If the frame length is greater than the number of declared slots for the frame, the remaining bits to transmit will be extended to 0 or the SD line will be released to HI-z depending the state of bit TRIS in the SAI\_xCR2 register (refer to *Section : FS signal role*). In reception mode, the remaining bit is ignored.

If bit NODIV is cleared, (FRL+1) must be equal to a power of 2, from 8 to 256, to ensure that an audio frame contains an integer number of MCLK pulses per bit clock cycle.

If bit NODIV is set, the (FRL+1) field can take any value from 8 to 256. Refer to *Section 39.4.8: SAI clock generator*".

Slave mode

The audio frame length is mainly used to specify to the slave the number of bit clock cycles per audio frame sent by the external master. It is used mainly to detect from the master any anticipated or late occurrence of the Frame synchronization signal during an on-going audio frame. In this case an error will be generated. For more details refer to *Section 39.4.13: Error flags*.

In slave mode, there are no constraints on the FRL[7:0] configuration in the SAI\_xFRCR register.

The number of bits in the frame is equal to FRL[7:0] + 1.

The minimum number of bits to transfer in an audio frame is 8.

## Frame synchronization polarity

FSPOL bit in the SAI\_xFRCR register sets the active polarity of the FS pin from which a frame is started. The start of frame is edge sensitive.