Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                 |

|----------------------------|----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                     |

| Speed                      | 80MHz                                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                             |

| Number of I/O              | 38                                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 64K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                           |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                                  |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 48-LQFP                                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l433cbt7                  |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3 Embedded Flash memory (FLASH)

# 3.1 Introduction

The Flash memory interface manages CPU AHB ICode and DCode accesses to the Flash memory. It implements the erase and program Flash memory operations and the read and write protection mechanisms.

The Flash memory interface accelerates code execution with a system of instruction prefetch and cache lines.

# 3.2 FLASH main features

- Up to 512 KByte of Flash memory (single bank)

- Memory organization:

- Main memory: up to 512 Kbyte

- Information block: 32 Kbyte

- 72-bit wide data read (64 bits plus 8 ECC bits)

- 72-bit wide data write (64 bits plus 8 ECC bits)

- Page erase (2 Kbyte) and mass erase

Flash memory interface features:

- Flash memory read operations

- Flash memory program/erase operations

- Read protection activated by option (RDP)

- 2 Write protection areas selected by option (WRP)

- 1 proprietary code read protection area selected by option (PCROP)

- Flash empty check

- Prefetch on ICODE

- Instruction Cache: 32 cache lines of 4 x 64 bits on ICode (1 KB RAM)

- Data Cache: 8 cache lines of 4 x 64 bits on DCode (256B RAM)

- Error Code Correction (ECC): 8 bits for 64-bit double-word

- Option byte loader

- Low-power mode

# 3.3 FLASH functional description

# 3.3.1 Flash memory organization

The Flash memory is organized as 72-bit wide memory cells (64 bits plus 8 ECC bits) that can be used for storing both code and data constants.

# 3.4 FLASH option bytes

## 3.4.1 Option bytes description

The option bytes are configured by the end user depending on the application requirements. As a configuration example, the watchdog may be selected in hardware or software mode (refer to *Section 3.4.2: Option bytes programming*).

A double word is split up as follows in the option bytes:

|                            |                            |                            | option byte it             | //mat            |                  |                  |                  |

|----------------------------|----------------------------|----------------------------|----------------------------|------------------|------------------|------------------|------------------|

| 63-24                      | 23-16                      | 15 -8                      | 7-0                        | 31-24            | 23-16            | 15 -8            | 7-0              |

| Complemented option byte 3 | Complemented option byte 2 | Complemented option byte 1 | Complemented option byte 0 | Option<br>byte 3 | Option<br>byte 2 | Option<br>byte 1 | Option<br>byte 0 |

The organization of these bytes inside the information block is as shown in *Table 10: Option byte organization*.

The option bytes can be read from the memory locations listed in *Table 10: Option byte organization* or from the Option byte registers:

- Flash option register (FLASH\_OPTR)

- Flash PCROP Start address register (FLASH\_PCROP1SR)

- Flash PCROP End address register (FLASH\_PCROP1ER)

- Flash WRP area A address register (FLASH\_WRP1AR)

- Flash WRP area B address register (FLASH\_WRP1BR)

|  | - |  |

|--|---|--|

|  | • |  |

|             |                             |                      |          | -       | -              | <u> </u>  |         |                     |        |                |

|-------------|-----------------------------|----------------------|----------|---------|----------------|-----------|---------|---------------------|--------|----------------|

| Address     | 63                          | [62:56]              | [55:48]  | [47:40] | [39:32]        | 31        | [30:24] | [23:16]             | [15:8] | [7:0]          |

| 0x1FFF 7800 |                             | Ū                    | ISER OPT |         | RDP            |           | U       | SER OPT             |        | RDP            |

| 0x1FFF 7808 |                             | Unu                  | sed      | PCROP   | 1_STRT         |           | Unus    | sed                 | PCRO   | P1_STRT        |

| 0x1FFF 7810 | PCROP_RDP                   | Ur                   | nused    | PCROF   | P1_END         | PCROP_RDP | Ur      | nused               | PCRC   | P1_END         |

| 0x1FFF 7818 | ι                           | Unused WRP1A<br>_END |          | Unused  | WRP1A<br>_STRT | Unused    |         | nused WRP1A_<br>END |        | WRP1A<br>_STRT |

| 0x1FFF 7820 | Unused Unused Unused Unused |                      |          | Unused  | WRP1B<br>_STRT | ι         | Jnused  | WRP1B_<br>END       | Unused | WRP1B<br>_STRT |

### Table 10. Option byte organization

## User and read protection option bytes

Flash memory address: 0x1FFF 7800 ST production value: 0xFFEF F8AA

software. Setting OBL\_LAUNCH generates a reset so the option byte loading is performed under system reset.

Each option bit has also its complement in the same double word. During option loading, a verification of the option bit and its complement allows to check the loading has correctly taken place.

During option byte loading, the options are read by double word with ECC. If the word and its complement are matching, the option word/byte is copied into the option register.

If the comparison between the word and its complement fails, a status bit OPTVERR is set. Mismatch values are forced into the option registers:

- For USR OPT option, the value of mismatch is all options at '1', except for BOR\_LEV which is "000" (lowest threshold)

- For WRP option, the value of mismatch is the default value "No protection"

- For RDP option, the value of mismatch is the default value "Level 1"

- For PCROP, the value of mismatch is "all memory protected"

On system reset rising, internal option registers are copied into option registers which can be read and written by software (FLASH\_OPTR, FLASH\_PCROP1SR,

FLASH\_PCROP1ER, FLASH\_WRP1AR, FLASH\_WRP1BR). These registers are also used to modify options. If these registers are not modified by user, they reflects the options states of the system. See *Section : Modifying user options* for more details.

# 5 Power control (PWR)

## 5.1 **Power supplies**

The STM32L43xxx/44xxx/45xxx/46xxx devices require a 1.71 V to 3.6 V operating supply voltage (V<sub>DD</sub>). Several peripherals are supplied through independent power domains: V<sub>DDA</sub>, V<sub>DDUSB</sub>, V<sub>LCD</sub>. Those supplies must not be provided without a valid operating supply on the V<sub>DD</sub> pin.

• V<sub>DD</sub> = 1.71 V to 3.6 V

$V_{DD}$  is the external power supply for the I/Os, the internal regulator and the system analog such as reset, power management and internal clocks. It is provided externally through VDD pins.

- V<sub>DD12</sub> = 1.05 V to 1.32 V External power supply, connected to V<sub>CORE</sub>, bypassing internal regulator when connected to an external SMPS. It is provided externally through VDD12 pins and only available on packages with the external SMPS supply option.

- V<sub>DDA</sub> = 1.62 V (ADCs/COMPs) / 1.8 V (DACs/OPAMPs) / 2.4 V (VREFBUF) to 3.6 V

$V_{DDA}$  is the external analog power supply for A/D converters, D/A converters, voltage reference buffer, operational amplifiers and comparators. The  $V_{DDA}$  voltage level is independent from the  $V_{DD}$  voltage.  $V_{DDA}$  should be preferably connected to  $V_{DD}$  when these peripherals are not used.

V<sub>DDUSB</sub> = 3.0 V to 3.6 V (available on STM32L4x2xx and STM32L4x3xx devices only)

V<sub>DDUSB</sub> is the external independent power supply for USB transceivers. The V<sub>DDUSB</sub> voltage level is independent from the V<sub>DD</sub> voltage. V<sub>DDUSB</sub> should be preferably connected to V<sub>DD</sub> when the USB is not used.

On small packages,  $V_{DDUSB}$  power supply may not be present as a dedicated pin and is internally bonded to  $V_{DD}$ . For such devices,  $V_{DD}$  has to respect the  $V_{DDUSB}$  supply range when USB is used.

• V<sub>LCD</sub> = 2.5 V to 3.6 V (available on STM32L4x3xx devices only)

The LCD controller can be powered either externally through VLCD pin, or internally from an internal voltage generated by the embedded step-up converter. VLCD is multiplexed with PC3 which can be used as GPIO when the LCD is not used.

On small packages, VDDUSB power supply may not be present as a dedicated pin, but is internally bonded to VDD. For such devices, VDD has to respect the VDDUSB supply range when USB is used.

• V<sub>BAT</sub> = 1.55 V to 3.6 V

$V_{BAT}$  is the power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when  $V_{DD}$  is not present. VBAT is internally bonded to VDD for small packages without dedicated pin.

$V_{\text{BAT}}$  is internally bonded to  $V_{\text{DD}}$  for small packages without dedicated pin.

• VREF-, VREF+

$V_{\mathsf{REF+}}$  is the input reference voltage for ADCs and DACs. It is also the output of the internal voltage reference buffer when enabled.

When  $V_{DDA}$  < 2 V,  $V_{REF+}$  must be equal to  $V_{DDA}$ .

It is recommended to manage the queue overflows as described below:

- After each P context write into JSQR register, flag JQOVF shows if the write has been ignored or not (an interrupt can be generated).

- Avoid Queue overflows by writing the third context (P3) only once the flag JEOS of the previous context P2 has been set. This ensures that the previous context has been consumed and that the queue is not full.

### Queue of context: Behavior when the queue becomes empty

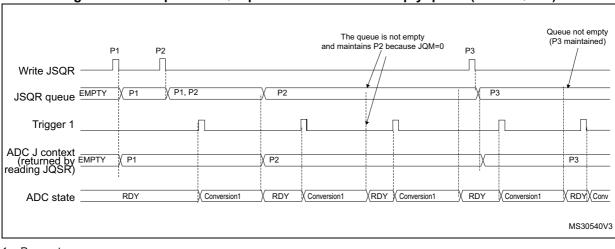

Figure 55 and Figure 56 show the behavior of the context Queue when the Queue becomes empty in both cases JQM=0 or 1.

### Figure 55. Example of JSQR queue of context with empty queue (case JQM=0)

1. Parameters:

P1: sequence of 1 conversion, hardware trigger 1 P2: sequence of 1 conversion, hardware trigger 1

P3: sequence of 1 conversion, hardware trigger 1

Note: When writing P3, the context changes immediately. However, because of internal resynchronization, there is a latency and if a trigger occurs just after or before writing P3, it can happen that the conversion is launched considering the context P2. To avoid this situation, the user must ensure that there is no ADC trigger happening when writing a new context that applies immediately.

Note: The data in this register can be updated any time, however the new values are applied only at the beginning of the next frame (except for UDDIE, SOFIE that affect the device behavior immediately).

The new value of CC[2:0] bits is also applied immediately but its effect on device is delayed at the beginning of next frame by the voltage generator.

Reading this register obtains the last value written in the register and not the configuration used to display the current frame.

Note: When BUFEN bit is set in the LCD\_CR register, low resistor divider network is automatically disabled whatever the HD or PON[2:0] bits configuration.

### 22.6.3 LCD status register (LCD\_SR)

Address offset: 0x08

Reset value: 0x0000 0020

| 31         | 30         | 29         | 28         | 27         | 26         | 25        | 24        | 23        | 22        | 21         | 20       | 19       | 18       | 17       | 16       |

|------------|------------|------------|------------|------------|------------|-----------|-----------|-----------|-----------|------------|----------|----------|----------|----------|----------|

| Res.       | Res.       | Res.       | Res.       | Res.       | Res.       | Res.      | Res.      | Res.      | Res.      | Res.       | Res.     | Res.     | Res.     | Res.     | Res.     |

|            |            |            |            |            |            |           |           |           |           |            |          |          |          |          |          |

|            |            |            |            |            |            |           |           |           |           |            |          |          |          |          |          |

| 15         | 14         | 13         | 12         | 11         | 10         | 9         | 8         | 7         | 6         | 5          | 4        | 3        | 2        | 1        | 0        |

| 15<br>Res. | 14<br>Res. | 13<br>Res. | 12<br>Res. | 11<br>Res. | 10<br>Res. | 9<br>Res. | 8<br>Res. | 7<br>Res. | 6<br>Res. | 5<br>FCRSF | 4<br>RDY | 3<br>UDD | 2<br>UDR | 1<br>SOF | 0<br>ENS |

Bits 31:6 Reserved, must be kept at reset value

Bit 5 **FCRSF**: LCD Frame Control Register Synchronization flag

This bit is set by hardware each time the LCD\_FCR register is updated in the LCDCLK domain. It is cleared by hardware when writing to the LCD\_FCR register.

- 0: LCD Frame Control Register not yet synchronized

- 1: LCD Frame Control Register synchronized

- Bit 4 **RDY**: Ready flag

- This bit is set and cleared by hardware. It indicates the status of the step-up converter.

- 0: Not ready

- 1: Step-up converter is enabled and ready to provide the correct voltage.

- Bit 3 UDD: Update Display Done

This bit is set by hardware. It is cleared by writing 1 to the UDDC bit in the LCD\_CLR register. The bit set has priority over the clear.

- 0: No event

- 1: Update Display Request done. A UDD interrupt is generated if the UDDIE bit in the LCD FCR register is set.

- Note: If the device is in Stop mode (PCLK not provided) UDD will not generate an interrupt even if UDDIE = 1.

If the display is not enabled the UDD interrupt will never occur.

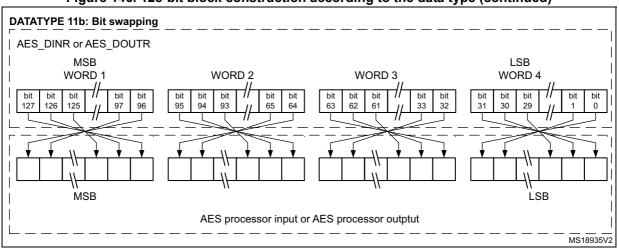

Figure 146. 128-bit block construction according to the data type (continued)

# 25.9 Operating modes

## 25.9.1 Mode 1: encryption

- 1. Disable the AES by resetting EN bit in the AES\_CR register.

- Configure the mode 1 by programming MODE[1:0] = 00 in the AES\_CR register and select which type of chaining mode needs to be performed by programming the CHMOD[2:0] bits.

- 3. Select key length 128-bits or 256-bits via KEYSIZE bits configuration in AES\_CR register.

- 4. Write the AES\_KEYRx registers (128-bit or 256-bit with encryption key) and the AES\_IVRx registers if CTR, CBC or GCM mode is selected. For ECB mode, the AES\_IVRx register is not used.

- 5. Enable the AES by setting the EN bit in the AES\_CR register.

- 6. Write the AES\_DINR register 4 times to input the plain text (MSB first) as shown in *Figure 147: Mode 1: encryption with 128-bit key length.*

- 7. Wait until the CCF flag is set in the AES\_SR register.

- 8. Read the AES\_DOUTR register 4 times to get the cipher text (MSB first) as shown in *Figure 147: Mode 1: encryption with 128-bit key length*.

- 9. Repeat steps 6,7,8 to process all the blocks with the same encryption key.

#### Bit 3 OC1PE: Output Compare 1 preload enable

0: Preload register on TIMx\_CCR1 disabled. TIMx\_CCR1 can be written at anytime, the new value is taken in account immediately.

1: Preload register on TIMx\_CCR1 enabled. Read/Write operations access the preload register. TIMx\_CCR1 preload value is loaded in the active register at each update event.

Note: **1:** These bits can not be modified as long as LOCK level 3 has been programmed (LOCK bits in TIMx\_BDTR register) and CC1S='00' (the channel is configured in output).

**2:** The PWM mode can be used without validating the preload register only in one pulse mode (OPM bit set in TIMx\_CR1 register). Else the behavior is not guaranteed.

#### Bit 2 OC1FE: Output Compare 1 fast enable

This bit is used to accelerate the effect of an event on the trigger in input on the CC output. 0: CC1 behaves normally depending on counter and CCR1 values even when the trigger is ON. The minimum delay to activate CC1 output when an edge occurs on the trigger input is 5 clock cycles.

1: An active edge on the trigger input acts like a compare match on CC1 output. Then, OC is set to the compare level independently from the result of the comparison. Delay to sample the trigger input and to activate CC1 output is reduced to 3 clock cycles. OCFE acts only if the channel is configured in PWM1 or PWM2 mode.

#### Bits 1:0 CC1S: Capture/Compare 1 selection

This bit-field defines the direction of the channel (input/output) as well as the used input.

- 00: CC1 channel is configured as output

- 01: CC1 channel is configured as input, IC1 is mapped on TI1

- 10: CC1 channel is configured as input, IC1 is mapped on TI2

11: CC1 channel is configured as input, IC1 is mapped on TRC. This mode is working only if an internal trigger input is selected through TS bit (TIMx\_SMCR register)

Note: CC1S bits are writable only when the channel is OFF (CC1E = '0' in TIMx\_CCER).

#### Input capture mode

- Bits 31:16 Reserved, must be kept at reset value.

- Bits 15:12 IC2F: Input capture 2 filter

- Bits 11:10 IC2PSC[1:0]: Input capture 2 prescaler

- Bits 9:8 CC2S: Capture/Compare 2 selection

This bit-field defines the direction of the channel (input/output) as well as the used input.

- 00: CC2 channel is configured as output

- 01: CC2 channel is configured as input, IC2 is mapped on TI2

- 10: CC2 channel is configured as input, IC2 is mapped on TI1

11: CC2 channel is configured as input, IC2 is mapped on TRC. This mode is working only if an internal trigger input is selected through TS bit (TIMx\_SMCR register)

Note: CC2S bits are writable only when the channel is OFF (CC2E = '0' in TIMx\_CCER).

|         |          | Control b | its      |           | Output states <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                  |                                                                 |  |  |  |  |  |  |  |

|---------|----------|-----------|----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|--|--|--|

| MOE bit | OSSI bit | OSSR bit  | CCxE bit | CCxNE bit | OCx output state                                                                                                                                                                                                                                                                                                                                              | OCxN output state                                               |  |  |  |  |  |  |  |

|         |          | х         | 0        | 0         | Output disabled (not driven by the timer: Hi-Z)<br>OCx=0, OCxN=0                                                                                                                                                                                                                                                                                              |                                                                 |  |  |  |  |  |  |  |

|         |          | 0         | 0        | 1         | Output disabled (not driven<br>by the timer: Hi-Z)<br>OCx=0                                                                                                                                                                                                                                                                                                   | OCxREF + Polarity<br>OCxN = OCxREF xor CCxNP                    |  |  |  |  |  |  |  |

| 1       | х        | 0         | 1        | 0         | OCxREF + Polarity<br>OCx=OCxREF xor CCxP                                                                                                                                                                                                                                                                                                                      | Output Disabled (not driven by<br>the timer: Hi-Z)<br>OCxN=0    |  |  |  |  |  |  |  |

|         | ^        | х         | 1        | 1         | OCREF + Polarity + dead-<br>time                                                                                                                                                                                                                                                                                                                              | Complementary to OCREF (not<br>OCREF) + Polarity + dead-time    |  |  |  |  |  |  |  |

|         |          | 1         | 0        | 1         | Off-State (output enabled<br>with inactive state)<br>OCx=CCxP                                                                                                                                                                                                                                                                                                 | OCxREF + Polarity<br>OCxN = OCxREF x or CCxNP                   |  |  |  |  |  |  |  |

|         |          | 1         | 1        | 0         | OCxREF + Polarity<br>OCx=OCxREF xor CCxP                                                                                                                                                                                                                                                                                                                      | Off-State (output enabled with<br>inactive state)<br>OCxN=CCxNP |  |  |  |  |  |  |  |

|         | 0        |           | Х        | Х         | Output disabled (not driven by the timer anymore). The                                                                                                                                                                                                                                                                                                        |                                                                 |  |  |  |  |  |  |  |

|         |          |           | 0        | 0         | output state is defined by the GPIO controller and can b High, Low or Hi-Z.                                                                                                                                                                                                                                                                                   |                                                                 |  |  |  |  |  |  |  |

|         |          |           | 0        | 1         | Off-State (output enabled wi                                                                                                                                                                                                                                                                                                                                  |                                                                 |  |  |  |  |  |  |  |

| 0       |          | х         | 1        | 0         | Asynchronously: OCx=CCxP, OCxN=CCxNP (if BRK or BRK2 is triggered).                                                                                                                                                                                                                                                                                           |                                                                 |  |  |  |  |  |  |  |

| 0       | 1        | ~         | 1        | 1         | Then (this is valid only if BRK is triggered), if the clock is<br>present: OCx=OISx and OCxN=OISxN after a dead-time,<br>assuming that OISx and OISxN do not correspond to OCX<br>and OCxN both in active state (may cause a short circuit<br>when driving switches in half-bridge configuration).<br><b>Note</b> : BRK2 can only be used if OSSI = OSSR = 1. |                                                                 |  |  |  |  |  |  |  |

### Table 122. Output control bits for complementary OCx and OCxN channels with break feature

1. When both outputs of a channel are not used (control taken over by GPIO), the OISx, OISxN, CCxP and CCxNP bits must be kept cleared.

Note: The state of the external I/O pins connected to the complementary OCx and OCxN channels depends on the OCx and OCxN channel state and the GPIO registers.

Bits 7:4 IC1F: Input capture 1 filter

This bit-field defines the frequency used to sample TI1 input and the length of the digital filter applied to TI1. The digital filter is made of an event counter in which N consecutive events are needed to validate a transition on the output:

0000: No filter, sampling is done at  $\ensuremath{f_{\text{DTS}}}$

0001: f<sub>SAMPLING</sub>=f<sub>CK\_INT</sub>, N=2

0010: f<sub>SAMPLING</sub>=f<sub>CK\_INT</sub>, N=4

0011: f<sub>SAMPLING</sub>=f<sub>CK\_INT</sub>, N=8 0100: f<sub>SAMPLING</sub>=f<sub>DTS</sub>/2, N=6

0101: f<sub>SAMPLING</sub>=f<sub>DTS</sub>/2, N=8

- 0110: f<sub>SAMPLING</sub>=f<sub>DTS</sub>/4, N=6

- 0111: f<sub>SAMPLING</sub>=f<sub>DTS</sub>/4, N=8

- 1000: f<sub>SAMPLING</sub>=f<sub>DTS</sub>/8, N=6

- 1001: f<sub>SAMPLING</sub>=f<sub>DTS</sub>/8, N=8

- 1010: f<sub>SAMPLING</sub>=f<sub>DTS</sub>/16, N=5

- 1011: f<sub>SAMPLING</sub>=f<sub>DTS</sub>/16, N=6

- 1100: f<sub>SAMPLING</sub>=f<sub>DTS</sub>/16, N=8

- 1101: f<sub>SAMPLING</sub>=f<sub>DTS</sub>/32, N=5

- 1110: f<sub>SAMPLING</sub>=f<sub>DTS</sub>/32, N=6

- 1111: f<sub>SAMPLING</sub>=f<sub>DTS</sub>/32, N=8

Bits 3:2 IC1PSC: Input capture 1 prescaler

This bit-field defines the ratio of the prescaler acting on CC1 input (IC1). The prescaler is reset as soon as CC1E=0 (TIMx\_CCER register).

- 00: no prescaler, capture is done each time an edge is detected on the capture input

- 01: capture is done once every 2 events

- 10: capture is done once every 4 events

- 11: capture is done once every 8 events

- Bits 1:0 CC1S: Capture/Compare 1 selection

This bit-field defines the direction of the channel (input/output) as well as the used input. 00: CC1 channel is configured as output

- 01: CC1 channel is configured as input, IC1 is mapped on TI1

- 10: CC1 channel is configured as input, IC1 is mapped on TI2

- 11: CC1 channel is configured as input, IC1 is mapped on TRC. This mode is working only if an internal trigger input is selected through TS bit (TIMx\_SMCR register)

Note: CC1S bits are writable only when the channel is OFF (CC1E = 0 in TIMx\_CCER).

## 27.4.8 TIMx capture/compare mode register 2 (TIMx\_CCMR2)

Address offset: 0x1C

Reset value: 0x0000

Refer to the above CCMR1 register description.

| 31    | 30   | 29      | 28   | 27    | 26      | 25   | 24          | 23    | 22   | 21      | 20   | 19    | 18      | 17   | 16          |

|-------|------|---------|------|-------|---------|------|-------------|-------|------|---------|------|-------|---------|------|-------------|

| Res.  | Res. | Res.    | Res. | Res.  | Res.    | Res. | OC4M<br>[3] | Res.  | Res. | Res.    | Res. | Res.  | Res.    | Res. | OC3M<br>[3] |

|       |      |         |      |       |         |      | Res.        |       |      |         |      |       |         |      | Res.        |

|       |      |         |      |       |         |      | rw          |       |      |         |      |       |         |      | rw          |

| 15    | 14   | 13      | 12   | 11    | 10      | 9    | 8           | 7     | 6    | 5       | 4    | 3     | 2       | 1    | 0           |

| OC4CE | (    | C4M[2:0 | )]   | OC4PE | OC4FE   | 004  | 214.01      | OC3CE | (    | C3M[2:0 | )]   | OC3PE | OC3FE   | 000  | 214.01      |

|       | IC4F | [3:0]   |      | IC4PS | SC[1:0] | 004  | S[1:0]      |       | IC3F | [3:0]   |      | IC3PS | SC[1:0] | 003  | S[1:0]      |

| rw    | rw   | rw      | rw   | rw    | rw      | rw   | rw          | rw    | rw   | rw      | rw   | rw    | rw      | rw   | rw          |

DocID027295 Rev 3

### RM0394

## 29.4.9 TIM6/TIM7 register map

TIMx registers are mapped as 16-bit addressable registers as described in the table below:

| Offset        | Register    | 31             | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18   | 17  | 16  | 15  | 14  | 13  | 12  | 11       | 10  | 6   | 8    | 2    | 9   | 5            | 4   | 3   | 2   | 1    | 0   |

|---------------|-------------|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|-----|-----|-----|-----|-----|-----|----------|-----|-----|------|------|-----|--------------|-----|-----|-----|------|-----|

| 0x00          | TIMx_CR1    | Res            | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res  | Res | Res | Res | Res | Res | Res | UIFREMAP | Res | Res | Res  | ARPE | Res | Res          | Res | OPM | URS | NDIS | CEN |

|               | Reset value |                |     |     |     |     |     |     |     |     |     |     |     |     |      |     |     |     |     |     |     | 0        |     |     |      | 0    |     |              |     | 0   | 0   | 0    | 0   |

| 0x04          | TIMx_CR2    | Res            | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res  | Res | Res | Res | Res | Res | Res | Res      | Res | Res | Res  | Res  |     | ИМS<br>[2:0] |     | Res | Res | Res  | Res |

|               | Reset value |                |     |     |     |     |     |     |     |     |     |     |     |     |      |     |     |     |     |     |     |          |     |     |      |      | 0   | 0            | 0   |     |     |      |     |

| 0x08          |             |                |     |     |     |     |     |     |     |     |     |     |     | Re  | eser | ved |     |     |     |     |     |          |     |     |      |      |     |              |     |     |     |      |     |

| 0x0C          | TIMx_DIER   | Res            | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res  | Res | Res | Res | Res | Res | Res | Res      | Res | Res | DDE  | Res  | Res | Res          | Res | Res | Res | Res  | UIE |

|               | Reset value |                |     |     |     |     |     |     |     |     |     |     |     |     |      |     |     |     |     |     |     |          |     |     | 0    |      |     |              |     |     |     |      | 0   |

| 0x10          | TIMx_SR     | Res            | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res  | Res | Res | Res | Res | Res | Res | Res      | Res | Res | Res  | Res  | Res | Res          | Res | Res | Res | Res  | UIF |

|               | Reset value |                |     |     |     |     |     |     |     |     |     |     |     |     |      |     |     |     |     |     |     |          |     |     |      |      |     |              |     |     |     |      | 0   |

| 0x14          | TIMx_EGR    | Res            | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res  | Res | Res | Res | Res | Res | Res | Res      | Res | Res | Res  | Res  | Res | Res          | Res | Res | Res | Res  | NG  |

|               | Reset value |                |     |     |     |     |     |     |     |     |     |     |     |     |      |     |     |     |     |     |     |          |     |     |      |      |     |              |     |     |     |      | 0   |

| 0x18-<br>0x20 |             |                |     |     |     |     |     |     |     |     |     |     |     | Re  | eser | ved |     |     |     |     |     |          |     |     |      |      |     |              |     |     |     |      |     |

| 0x24          | TIMx_CNT    | UIFCPY or Res. | Res  | Res | Res |     |     |     |     |          |     | С   | NT[  | 15:0 | 0]  |              |     |     |     |      |     |

|               | Reset value | 0              |     |     |     |     |     |     |     |     |     |     |     |     |      |     |     | 0   | 0   | 0   | 0   | 0        | 0   | 0   | 0    | 0    | 0   | 0            | 0   | 0   | 0   | 0    | 0   |

| 0x28          | TIMx_PSC    | Res            | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res  | Res | Res |     |     |     |     |          |     | Ρ   | sc   | 15:0 | 0]  |              |     |     |     | 1    |     |

|               | Reset value |                |     |     |     |     |     |     |     |     |     |     |     |     |      |     |     | 0   | 0   | 0   | 0   | 0        | 0   | 0   | 0    | 0    | 0   | 0            | 0   | 0   | 0   | 0    | 0   |

| 0x2C          | TIMx_ARR    | Res            | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res  | Res | Res |     |     |     |     |          |     | A   | .RR[ | 15:  | 0]  |              |     |     |     |      |     |

|               | Reset value |                |     |     |     |     |     |     |     |     |     |     |     |     |      |     |     | 1   | 1   | 1   | 1   | 1        | 1   | 1   | 1    | 1    | 1   | 1            | 1   | 1   | 1   | 1    | 1   |

Table 133. TIM6/TIM7 register map and reset values

Refer to Section 2.2.2: Memory map and register boundary addresses for the register boundary addresses.

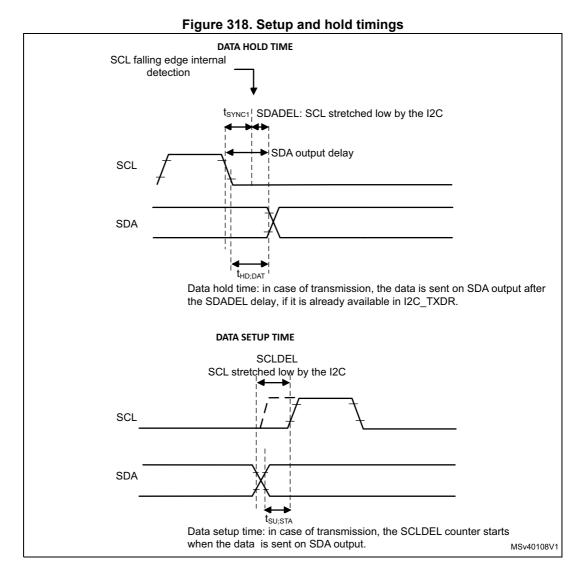

### I2C timings

The timings must be configured in order to guarantee a correct data hold and setup time, used in master and slave modes. This is done by programming the PRESC[3:0], SCLDEL[3:0] and SDADEL[3:0] bits in the I2C\_TIMINGR register.

The STM32CubeMX tool calculates and provides the I2C\_TIMINGR content in the I2C configuration window

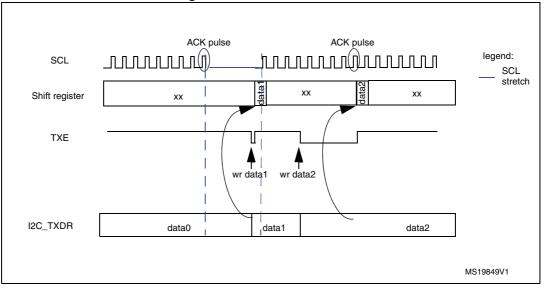

### Transmission

If the I2C\_TXDR register is not empty (TXE=0), its content is copied into the shift register after the 9th SCL pulse (the Acknowledge pulse). Then the shift register content is shifted out on SDA line. If TXE=1, meaning that no data is written yet in I2C\_TXDR, SCL line is stretched low until I2C\_TXDR is written. The stretch is done after the 9th SCL pulse.

### Hardware transfer management

The I2C has a byte counter embedded in hardware in order to manage byte transfer and to close the communication in various modes such as:

- NACK, STOP and ReSTART generation in master mode

- ACK control in slave receiver mode

- PEC generation/checking when SMBus feature is supported

The byte counter is always used in master mode. By default it is disabled in slave mode, but it can be enabled by software by setting the SBC (Slave Byte Control) bit in the I2C\_CR2 register.

The number of bytes to be transferred is programmed in the NBYTES[7:0] bit field in the I2C\_CR2 register. If the number of bytes to be transferred (NBYTES) is greater than 255, or if a receiver wants to control the acknowledge value of a received data byte, the reload mode must be selected by setting the RELOAD bit in the I2C\_CR2 register. In this mode, TCR flag is set when the number of bytes programmed in NBYTES has been transferred, and an interrupt is generated if TCIE is set. SCL is stretched as long as TCR flag is set. TCR is cleared by software when NBYTES is written to a non-zero value.

When the NBYTES counter is reloaded with the last number of bytes, RELOAD bit must be cleared.

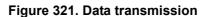

Four I/O pins are dedicated to SPI communication with external devices.

- **MISO:** Master In / Slave Out data. In the general case, this pin is used to transmit data in slave mode and receive data in master mode.

- **MOSI:** Master Out / Slave In data. In the general case, this pin is used to transmit data in master mode and receive data in slave mode.

- SCK: Serial Clock output pin for SPI masters and input pin for SPI slaves.

- NSS: Slave select pin. Depending on the SPI and NSS settings, this pin can be used to either:

- select an individual slave device for communication

- synchronize the data frame or

- detect a conflict between multiple masters

See Section 38.4.5: Slave select (NSS) pin management for details.

The SPI bus allows the communication between one master device and one or more slave devices. The bus consists of at least two wires - one for the clock signal and the other for synchronous data transfer. Other signals can be added depending on the data exchange between SPI nodes and their slave select signal management.

### 38.4.2 Communications between one master and one slave

The SPI allows the MCU to communicate using different configurations, depending on the device targeted and the application requirements. These configurations use 2 or 3 wires (with software NSS management) or 3 or 4 wires (with hardware NSS management). Communication is always initiated by the master.

#### **Full-duplex communication**

By default, the SPI is configured for full-duplex communication. In this configuration, the shift registers of the master and slave are linked using two unidirectional lines between the MOSI and the MISO pins. During SPI communication, data is shifted synchronously on the SCK clock edges provided by the master. The master transmits the data to be sent to the slave via the MOSI line and receives data from the slave via the MISO line. When the data frame transfer is complete (all the bits are shifted) the information between the master and slave is exchanged.

Figure 385. Full-duplex single master/ single slave application

1. The NSS pins can be used to provide a hardware control flow between master and slave. Optionally, the pins can be left unused by the peripheral. Then the flow has to be handled internally for both master and slave. For more details see *Section 38.4.5: Slave select (NSS) pin management*.

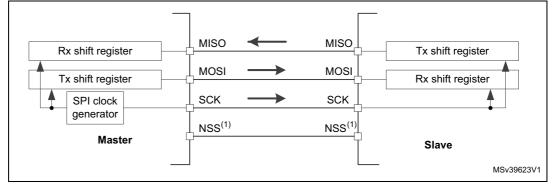

Figure 396. Master full-duplex communication with CRC

Assumptions for master full-duplex communication with CRC example:

- Data size = 16 bit

- CRC enabled

If DMA is used:

- Number of Tx frames transacted by DMA is set to 2

- Number of Rx frames transacted by DMA is set to 3

See also : *Communication diagrams on page 1208* for details about common assumptions and notes.

| Bit position | Width | Value | Description      |

|--------------|-------|-------|------------------|

| 47           | 1     | 0     | Start bit        |

| 46           | 1     | 0     | Transmission bit |

| [45:40]      | 6     | -     | Command index    |

| [39:8]       | 32    | -     | Argument         |

| [7:1]        | 7     | -     | CRC7(or 111111)  |

| 0            | 1     | 1     | End bit          |

#### Table 199. Short response format

### Table 200. Long response format

| Bit position | Width | Value  | Description                          |

|--------------|-------|--------|--------------------------------------|

| 135          | 1     | 0      | Start bit                            |

| 134          | 1     | 0      | Transmission bit                     |

| [133:128]    | 6     | 111111 | Reserved                             |

| [127:1]      | 127   | -      | CID or CSD (including internal CRC7) |

| 0            | 1     | 1      | End bit                              |

The command register contains the command index (six bits sent to a card) and the command type. These determine whether the command requires a response, and whether the response is 48 or 136 bits long (see *Section 41.8.4 on page 1339*). The command path implements the status flags shown in *Table 201*:

| Table 201. Command path status flags | Table 201. | Command | path status flags |

|--------------------------------------|------------|---------|-------------------|

|--------------------------------------|------------|---------|-------------------|

| Flag     | Description                                               |

|----------|-----------------------------------------------------------|

| CMDREND  | Set if response CRC is OK.                                |

| CCRCFAIL | Set if response CRC fails.                                |

| CMDSENT  | Set when command (that does not require response) is sent |

| CTIMEOUT | Response timeout.                                         |

| CMDACT   | Command transfer in progress.                             |

The CRC generator calculates the CRC checksum for all bits before the CRC code. This includes the start bit, transmitter bit, command index, and command argument (or card status). The CRC checksum is calculated for the first 120 bits of CID or CSD for the long response format. Note that the start bit, transmitter bit and the six reserved bits are not used in the CRC calculation.

The CRC checksum is a 7-bit value:

$\begin{aligned} & \text{CRC[6:0] = Remainder} \left[ (M(x) * x^7) / G(x) \right] \\ & \text{G}(x) = x^7 + x^3 + 1 \\ & \text{M}(x) = (\text{start bit}) * x^{39} + ... + (\text{last bit before CRC}) * x^0, \text{ or} \\ & \text{M}(x) = (\text{start bit}) * x^{119} + ... + (\text{last bit before CRC}) * x^0 \end{aligned}$

## 44.4.1 SWJ debug port pins

Five pins are used as outputs from the STM32L43xxx/44xxx/45xxx/46xxx for the SWJ-DP as *alternate functions* of general-purpose I/Os. These pins are available on all packages.

| SWJ-DP pin name     |      | JTAG debug port             |      | Pin<br>assign                                   |      |

|---------------------|------|-----------------------------|------|-------------------------------------------------|------|

| SwJ-DP pill liallie | Туре | Description                 | Туре | Debug assignment                                | ment |

| JTMS/SWDIO          | Ι    | JTAG Test Mode<br>Selection | Ю    | Serial Wire Data<br>Input/Output                | PA13 |

| JTCK/SWCLK          | Ι    | JTAG Test Clock             | I    | Serial Wire Clock                               | PA14 |

| JTDI                | Ι    | JTAG Test Data Input        | -    | -                                               | PA15 |

| JTDO/TRACESWO       | 0    | JTAG Test Data Output       | -    | TRACESWO if<br>asynchronous trace is<br>enabled | PB3  |

| NJTRST              | Ι    | JTAG Test nReset            | -    | -                                               | PB4  |

Table 244. SWJ debug port pins

## 44.4.2 Flexible SWJ-DP pin assignment

After RESET (SYSRESETn or PORESETn), all five pins used for the SWJ-DP are assigned as dedicated pins immediately usable by the debugger host (note that the trace outputs are not assigned except if explicitly programmed by the debugger host).

However, the STM32L43xxx/44xxx/45xxx/46xxx MCUs offer the possibility of disabling some or all of the SWJ-DP ports, and therefore the possibility of releasing the associated pins for general-purpose I/O (GPIO) usage. For more details on how to disable SWJ-DP port pins, please refer to *Section 8.3.2: I/O pin alternate function multiplexer and mapping*.

| Table 245. | Flexible | SWJ-DP | ' pin ass | ignment |  |

|------------|----------|--------|-----------|---------|--|

|            |          |        |           |         |  |

|                                               | SWJ IO pin assigned |                          |                |               |                |  |  |  |  |

|-----------------------------------------------|---------------------|--------------------------|----------------|---------------|----------------|--|--|--|--|

| Available debug ports                         |                     | PA14 /<br>JTCK/<br>SWCLK | PA15 /<br>JTDI | PB3 /<br>JTDO | PB4/<br>NJTRST |  |  |  |  |

| Full SWJ (JTAG-DP + SW-DP) - Reset State      | Х                   | Х                        | Х              | Х             | Х              |  |  |  |  |

| Full SWJ (JTAG-DP + SW-DP) but without NJTRST | Х                   | Х                        | Х              | Х             |                |  |  |  |  |

| JTAG-DP disabled and SW-DP enabled            | Х                   | Х                        |                |               | -              |  |  |  |  |

| JTAG-DP disabled and SW-DP disabled           |                     |                          | Rele           | ased          |                |  |  |  |  |

Note:

When the APB bridge write buffer is full, it takes one extra APB cycle when writing the AFIO\_MAPR register. This is because the deactivation of the JTAGSW pins is done in two cycles to guarantee a clean level on the nTRST and TCK input signals of the core.

- Cycle 1: the JTAGSW input signals to the core are tied to 1 or 0 (to 1 for nTRST, TDI and TMS, to 0 for TCK)

- Cycle 2: the GPIO controller takes the control signals of the SWJTAG IO pins (like controls of direction, pull-up/down, Schmitt trigger activation, etc.).

DocID027295 Rev 3

| DBGM<br>regi   |                         |                            |                                |                         |                           |                           |                    |                    |

|----------------|-------------------------|----------------------------|--------------------------------|-------------------------|---------------------------|---------------------------|--------------------|--------------------|

| TRACE<br>_IOEN | TRACE<br>_MODE<br>[1:0] | Pins<br>assigned for:      | <b>PB3 /</b> JTDO/<br>TRACESWO | <b>PE2 /</b><br>TRACECK | <b>PE3</b> /<br>TRACED[0] | <b>PE4</b> /<br>TRACED[1] | PE5 /<br>TRACED[2] | PE6 /<br>TRACED[3] |

| 1              | 01                      | Synchronous<br>Trace 1 bit |                                | TRACECK                 | TRACED[0]                 | -                         | -                  | -                  |

| 1              | 10                      | Synchronous<br>Trace 2 bit | Released (1)                   | TRACECK                 | TRACED[0]                 | TRACED[1]                 | -                  | -                  |

| 1              | 11                      | Synchronous<br>Trace 4 bit |                                | TRACECK                 | TRACED[0]                 | TRACED[1]                 | TRACED[2]          | TRACED[3]          |

### Table 258. Flexible TRACE pin assignment (continued)

1. When Serial Wire mode is used, it is released, but when JTAG is used, it is assigned to JTDO.

Note: By default, the TRACECLKIN input clock of the TPIU is tied to GND. It is assigned to HCLK two clock cycles after the bit TRACE\_IOEN has been set.

The debugger must then program the Trace Mode by writing the PROTOCOL[1:0] bits in the SPP\_R (Selected Pin Protocol) register of the TPIU.

- PROTOCOL=00: Trace Port Mode (synchronous)

- PROTOCOL=01 or 10: Serial Wire (Manchester or NRZ) Mode (asynchronous mode). Default state is 01

It then also configures the TRACE port size by writing the bits [3:0] in the CPSPS\_R (Current Synchronous Port Size Register) of the TPIU:

- 0x1 for 1 pin (default state)

- 0x2 for 2 pins

- 0x8 for 4 pins

## 44.17.3 TPUI formatter

The formatter protocol outputs data in 16-byte frames:

- seven bytes of data

- eight bytes of mixed-use bytes consisting of:

- 1 bit (LSB) to indicate it is a DATA byte ('0) or an ID byte ('1).

- 7 bits (MSB) which can be data or change of source ID trace.

- one byte of auxiliary bits where each bit corresponds to one of the eight mixed-use bytes:

- if the corresponding byte was a data, this bit gives bit0 of the data.

- if the corresponding byte was an ID change, this bit indicates when that ID change takes effect.

- *Note:* Refer to the ARM<sup>®</sup> CoreSight Architecture Specification v1.0 (ARM IHI 0029B) for further information

# L

| .CD_CLR        |

|----------------|

| .CD_CR         |

| .CD_RAM601     |

| .PTIM_ARR947   |

| .PTIM_CFGR943  |

| .PTIM_CMP      |

| .PTIM_CNT948   |

| .PTIM_CR946    |

| .PTIM_ICR941   |

| .PTIM_IER      |

| .PTIM_ISR      |

| .PTIM1_OR948   |

| .PTIM2_OR948   |

| PUART_BRR1185  |

| .PUART_CR11178 |

| .PUART_CR21181 |

| PUART_CR31183  |

| PUART_ICR1189  |

| _PUART_ISR1186 |

| PUART_RDR1190  |

| PUART_RQR1185  |

| PUART_TDR1190  |

|                |

# 0

| OPAMP1_CSR   | .517 |

|--------------|------|

| OPAMP1_LPOTR | .518 |

| OPAMP1_OTR   | .518 |

## Ρ

| purpose      |

|--------------|

| PWR_CR1155   |

| PWR_CR2156   |

| PWR_CR3157   |

| PWR_CR4158   |

| PWR_PDCRA    |

| PWR_PDCRB164 |

| PWR_PDCRC165 |

| PWR_PDCRD    |

| PWR_PDCRE167 |

| PWR_PDCRH168 |

| PWR_PUCRA162 |

| PWR_PUCRB163 |

| PWR_PUCRC164 |

| PWR_PUCRD165 |

| PWR_PUCRE166 |

|              |

| PWR_PUCRH 1 | 67 |

|-------------|----|

| PWR_SCR1    | 61 |

| PWR_SR1 1   | 59 |

| PWR SR2 1   | 60 |

# Q

| QUADSPI_PIR   | <br> | <br> | <br> | <br> |      | . 364 |

|---------------|------|------|------|------|------|-------|

| QUADSPI PSMAR | <br> | <br> | <br> | <br> |      | . 363 |

| QUADSPI_PSMKR | <br> | <br> | <br> | <br> |      | . 363 |

| QUADSPI_ABR   | <br> | <br> | <br> | <br> | <br> | . 362 |

| QUADSPI_AR    | <br> | <br> | <br> | <br> | <br> | . 361 |

| QUADSPI_CCR   | <br> | <br> | <br> | <br> | <br> | . 359 |

| QUADSPI_CR    | <br> | <br> | <br> | <br> | <br> | . 353 |

| QUADSPI_DCR   | <br> | <br> | <br> | <br> | <br> | . 356 |

| QUADSPI_DLR   | <br> | <br> | <br> | <br> | <br> | . 358 |

| QUADSPI_DR    | <br> | <br> | <br> | <br> |      | . 362 |

| QUADSPI_FCR   | <br> | <br> | <br> | <br> |      | . 358 |

| QUADSPI_LPTR  | <br> | <br> | <br> | <br> |      | . 364 |

| QUADSPI_SR    | <br> | <br> | <br> | <br> |      | . 357 |

## R

| RCC_AHB1ENR     | 212   |

|-----------------|-------|

| RCC_AHB1RSTR    | 212   |

|                 |       |

| RCC_AHB1SMENR   |       |

| RCC_AHB2ENR     | 214   |

| RCC_AHB2RSTR    |       |

| RCC_AHB2SMENR   |       |

| RCC_AHB3ENR     |       |

| RCC_AHB3RSTR    |       |

| RCC_AHB3SMENR   |       |

| RCC_APB1ENR1    |       |

| RCC_APB1ENR2    | . 218 |

| RCC_APB1RSTR1   | 207   |

| RCC APB1RSTR2   | . 210 |

| RCC APB1SMENR1  | . 224 |

| RCC_APB1SMENR2  | . 227 |

| RCC_APB2ENR     | 220   |

| RCC_APB2RSTR    | . 211 |

| RCC APB2SMENR   |       |

| RCC BDCR        |       |

| RCC CCIPR       |       |

| RCC CFGR        |       |

| RCC CICR        |       |

| RCC CIER        |       |

| RCC CIFR        |       |

| RCC_CR          |       |

| RCC CRRCR       |       |

| RCC_CSR         |       |

| RCC ICSCR       |       |

| —               |       |

| RCC_PLLCFGR     |       |

| RCC_PLLSAI1CFGR | 197   |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

DocID027295 Rev 3