Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                 |

| Core Processor             | ARM® Cortex®-M4                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                     |

| Speed                      | 80MHz                                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                             |

| Number of I/O              | 38                                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 64K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                           |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                                  |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 48-UFQFN Exposed Pad                                                                   |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l433cbu6                  |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Below is the initialization procedure to follow:

- 1. Configure the RCC to enable the clock to the Firewall module

- 2. Configure the RCC to enable the clock of the system configuration registers

- 3. Set the base address and length of each segment (CSSA, CSL, NVDSSA, NVDSL, VDSSA, VDSL registers)

- 4. Set the configuration register of the Firewall (FW\_CR register)

- 5. Enable the Firewall clearing the FWDIS bit in the system configuration register.

The Firewall configuration register (FW\_CR register) is the only one which can be managed in a dynamic way even if the Firewall is enabled:

- when the Non-Volatile data segment is undefined (meaning the NVDSL register is equal to 0), the accesses to this register are possible whatever the Firewall state (opened or closed).

- when the Non-Volatile data segment is defined (meaning the NVDSL register is different from 0), the accesses to this register are only possible when the Firewall is opened.

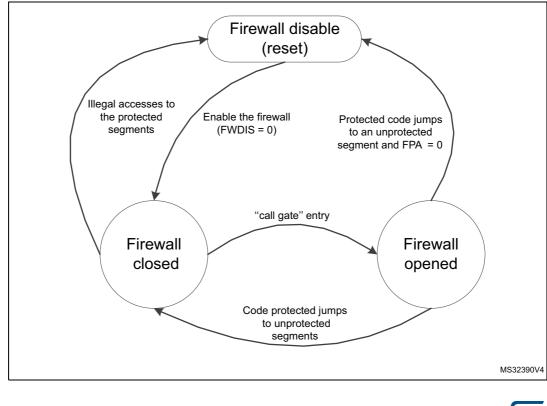

### 4.3.6 Firewall states

The Firewall has three different states as shown in Figure 6:

- Disabled: The FWDIS bit is set by default after the reset. The Firewall is not active.

- Closed: The Firewall protects the accesses to the three segments (Code, Non-volatile data, and Volatile data segments).

- Opened: The Firewall allows access to the protected segments as defined in Section 4.3.4: Segment accesses and properties.

#### Figure 6. Firewall functional states

DocID027295 Rev 3

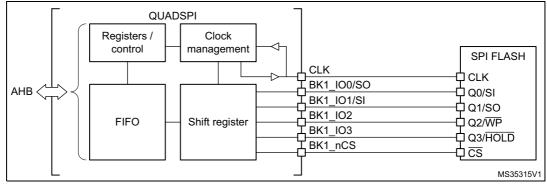

# 15 Quad-SPI interface (QUADSPI)

# 15.1 Introduction

The QUADSPI is a specialized communication interface targeting single, dual or quad SPI Flash memories. It can operate in any of the three following modes:

- indirect mode: all the operations are performed using the QUADSPI registers

- status polling mode: the external Flash memory status register is periodically read and an interrupt can be generated in case of flag setting

- memory-mapped mode: the external Flash memory is mapped to the microcontroller address space and is seen by the system as if it was an internal memory

Both throughput and capacity can be increased two-fold using dual-flash mode, where two Quad-SPI Flash memories are accessed simultaneously.

# 15.2 QUADSPI main features

- Three functional modes: indirect, status-polling, and memory-mapped

- Dual-flash mode, where 8 bits can be sent/received simultaneously by accessing two Flash memories in parallel.

- SDR and DDR support

- Fully programmable opcode for both indirect and memory mapped mode

- Fully programmable frame format for both indirect and memory mapped mode

- Integrated FIFO for reception and transmission

- 8, 16, and 32-bit data accesses are allowed

- DMA channel for indirect mode operations

- Interrupt generation on FIFO threshold, timeout, operation complete, and access error

# **15.3 QUADSPI functional description**

# 15.3.1 QUADSPI block diagram

### Figure 31. QUADSPI block diagram when dual-flash mode is disabled

# 15.5.2 QUADSPI device configuration register (QUADSPI\_DCR)

Address offset: 0x0004

Reset value: 0x0000 0000

| 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20   | 19   | 18    | 17   | 16          |

|------|------|------|------|------|------|------|------|------|------|------|------|------|-------|------|-------------|

| Res. |      |      | FSIZE |      |             |

|      |      |      |      |      |      |      |      |      |      |      | rw   | rw   | rw    | rw   | rw          |

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2     | 1    | 0           |

| Res. | Res. | Res. | Res. | Res. |      | CSHT |      | Res. | Res. | Res. | Res. | Res. | Res.  | Res. | CK-<br>MODE |

|      |      |      |      |      | rw   | rw   | rw   |      |      |      |      |      |       |      | rw          |

Bits 31: 21 Reserved, must be kept at reset value.

### Bits 20: 16 FSIZE[4:0]: Flash memory size

This field defines the size of external memory using the following formula: Number of bytes in Flash memory =  $2^{[FSIZE+1]}$

FSIZE+1 is effectively the number of address bits required to address the Flash memory. The Flash memory capacity can be up to 4GB (addressed using 32 bits) in indirect mode, but the addressable space in memory-mapped mode is limited to 256MB.

If DFM = 1, FSIZE indicates the total capacity of the two Flash memories together. This field can be modified only when BUSY = 0.

#### Bits 15: 11 Reserved, must be kept at reset value.

#### Bits 10:8 CSHT[2:0]: Chip select high time

CSHT+1 defines the minimum number of CLK cycles which the chip select (nCS) must remain high between commands issued to the Flash memory.

0: nCS stays high for at least 1 cycle between Flash memory commands

- 1: nCS stays high for at least 2 cycles between Flash memory commands

- ...

7: nCS stays high for at least 8 cycles between Flash memory commands This field can be modified only when BUSY = 0.

### Bits 7: 1 Reserved, must be kept at reset value.

### Bit 0 CKMODE: Mode 0 / mode 3

This bit indicates the level that CLK takes between commands (when nCS = 1). 0: CLK must stay low while nCS is high (chip select released). This is referred to as mode 0.

1: CLK must stay high while nCS is high (chip select released). This is referred to as mode 3.

This field can be modified only when BUSY = 0.

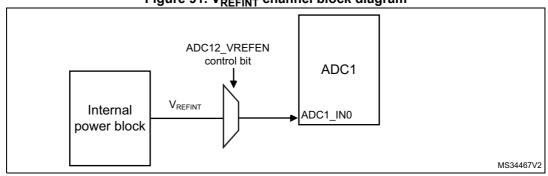

Figure 91. V<sub>REFINT</sub> channel block diagram

The VREFEN bit into ADC\_CCR register must be set to enable the conversion of internal channels ADC1\_IN0 (V<sub>REFINT</sub>).

### Calculating the actual $V_{DDA}$ voltage using the internal reference voltage

The V<sub>DDA</sub> power supply voltage applied to the microcontroller may be subject to variation or not precisely known. The embedded internal voltage reference (V<sub>REFINT</sub>) and its calibration data acquired by the ADC during the manufacturing process at V<sub>DDA</sub> = 3.0 V can be used to evaluate the actual V<sub>DDA</sub> voltage level.

The following formula gives the actual  $V_{\text{DDA}}$  voltage supplying the device:

V<sub>DDA</sub> = 3.0 V x VREFINT\_CAL / VREFINT\_DATA

where:

- VREFINT\_CAL is the VREFINT calibration value

- VREFINT\_DATA is the actual VREFINT output value converted by ADC

### Converting a supply-relative ADC measurement to an absolute voltage value

The ADC is designed to deliver a digital value corresponding to the ratio between the analog power supply and the voltage applied on the converted channel. For most application use cases, it is necessary to convert this ratio into a voltage independent of  $V_{DDA}$ . For applications where  $V_{DDA}$  is known and ADC converted values are right-aligned you can use the following formula to get this absolute value:

$$V_{CHANNELx} = \frac{V_{DDA}}{FULL_SCALE} \times ADCx_DATA$$

For applications where  $V_{DDA}$  value is not known, you must use the internal voltage reference and  $V_{DDA}$  can be replaced by the expression provided in *Section : Calculating the actual VDDA voltage using the internal reference voltage*, resulting in the following formula:

$V_{CHANNELx} = \frac{3.0 \text{ V} \times \text{VREFINT}_CAL \times \text{ADCx}_DATA}{\text{VREFINT}_DATA \times \text{FULL}_SCALE}$

Where:

- VREFINT\_CAL is the VREFINT calibration value

- ADC\_DATA is the value measured by the ADC on channel x (right-aligned)

- VREFINT\_DATA is the actual VREFINT output value converted by the ADC

- FULL\_SCALE is the maximum digital value of the ADC output. For example with 12-bit resolution, it will be 2<sup>12</sup> 1 = 4095 or with 8-bit resolution, 2<sup>8</sup> 1 = 255.

#### Bits 11:8 MAMP1[3:0]: DAC channel1 mask/amplitude selector

These bits are written by software to select mask in wave generation mode or amplitude in triangle generation mode.

- 0000: Unmask bit0 of LFSR/ triangle amplitude equal to 1

- 0001: Unmask bits[1:0] of LFSR/ triangle amplitude equal to 3

- 0010: Unmask bits[2:0] of LFSR/ triangle amplitude equal to 7

- 0011: Unmask bits[3:0] of LFSR/ triangle amplitude equal to 15

- 0100: Unmask bits[4:0] of LFSR/ triangle amplitude equal to 31

- 0101: Unmask bits[5:0] of LFSR/ triangle amplitude equal to 63

- 0110: Unmask bits[6:0] of LFSR/ triangle amplitude equal to 127

- 0111: Unmask bits[7:0] of LFSR/ triangle amplitude equal to 255

- 1000: Unmask bits[8:0] of LFSR/ triangle amplitude equal to 511

- 1001: Unmask bits[9:0] of LFSR/ triangle amplitude equal to 1023

- 1010: Unmask bits[10:0] of LFSR/ triangle amplitude equal to 2047

- ≥ 1011: Unmask bits[11:0] of LFSR/ triangle amplitude equal to 4095

#### Bits 7:6 **WAVE1[1:0]**: DAC channel1 noise/triangle wave generation enable

- These bits are set and cleared by software.

- 00: wave generation disabled

- 01: Noise wave generation enabled

- 1x: Triangle wave generation enabled

- *Note:* Only used if bit TEN1 = 1 (DAC channel1 trigger enabled).

#### Bits 5:3 TSEL1[2:0]: DAC channel1 trigger selection

- These bits select the external event used to trigger DAC channel1

- 000: Timer 6 TRGO event

- 001: Reserved

- 010: Timer 7 TRGO event (reserved on STM32L45xxx and STM32L46xxx)

- 011: Reserved

- 100: Timer 2 TRGO event

- 101: Reserved

- 110: External line9

- 111: Software trigger

- *Note:* Only used if bit TEN1 = 1 (DAC channel1 trigger enabled).

#### Bit 2 TEN1: DAC channel1 trigger enable

This bit is set and cleared by software to enable/disable DAC channel1 trigger. 0: DAC channel1 trigger disabled and data written into the DAC\_DHRx register are transferred one APB1 clock cycle later to the DAC\_DOR1 register

1: DAC channel1 trigger enabled and data from the DAC\_DHRx register are transferred three APB1 clock cycles later to the DAC\_DOR1 register

- Note: When software trigger is selected, the transfer from the DAC\_DHRx register to the DAC\_DOR1 register takes only one APB1 clock cycle.

- Bit 1 Reserved, must be kept at reset value.

- Bit 0 EN1: DAC channel1 enable

This bit is set and cleared by software to enable/disable DAC channel1.

- 0: DAC channel1 disabled

- 1: DAC channel1 enabled

# 23.6.6 TSC I/O analog switch control register (TSC\_IOASCR)

Address offset: 0x18

Reset value: 0x0000 0000

| 31     | 30     | 29     | 28     | 27     | 26     | 25     | 24     | 23     | 22     | 21     | 20     | 19     | 18     | 17     | 16     |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Res.   | Res.   | Res.   | Res.   | G7_IO4 | G7_103 | G7_IO2 | G7_IO1 | G6_IO4 | G6_IO3 | G6_IO2 | G6_IO1 | G5_IO4 | G5_IO3 | G5_IO2 | G5_IO1 |

|        |        |        |        | rw     |

| 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

| G4_I04 | G4_IO3 | G4_IO2 | G4_IO1 | G3_IO4 | G3_IO3 | G3_IO2 | G3_IO1 | G2_IO4 | G2_IO3 | G2_IO2 | G2_IO1 | G1_IO4 | G1_IO3 | G1_IO2 | G1_IO1 |

| rw     |

Bits 31:28 Reserved, must be kept at reset value.

Bits 27:0 Gx\_IOy: Gx\_IOy analog switch enable

These bits are set and cleared by software to enable/disable the Gx\_IOy analog switch.

0: Gx\_IOy analog switch disabled (opened)

1: Gx\_IOy analog switch enabled (closed)

Note: These bits control the I/O analog switch whatever the I/O control mode is (even if controlled by standard GPIO registers).

# 23.6.7 TSC I/O sampling control register (TSC\_IOSCR)

### Address offset: 0x20

Reset value: 0x0000 0000

| 31     | 30     | 29     | 28     | 27     | 26     | 25     | 24     | 23     | 22     | 21     | 20     | 19     | 18     | 17     | 16     |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Res.   | Res.   | Res.   | Res.   | G7_IO4 | G7_IO3 | G7_IO2 | G7_IO1 | G6_IO4 | G6_IO3 | G6_IO2 | G6_IO1 | G5_IO4 | G5_IO3 | G5_IO2 | G5_IO1 |

|        |        |        |        | rw     |

| 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

| G4_IO4 | G4_IO3 | G4_IO2 | G4_I01 | G3_IO4 | G3_IO3 | G3_IO2 | G3_IO1 | G2_IO4 | G2_IO3 | G2_IO2 | G2_IO1 | G1_IO4 | G1_IO3 | G1_IO2 | G1_IO1 |

| rw     |

### Bits 27:0 Gx\_IOy: Gx\_IOy sampling mode

These bits are set and cleared by software to configure the Gx\_IOy as a sampling capacitor I/O. Only one I/O per analog I/O group must be defined as sampling capacitor.

0: Gx\_IOy unused

1: Gx\_IOy used as sampling capacitor

Note: These bits must not be modified when an acquisition is ongoing.

During the acquisition phase and even if the TSC peripheral alternate function is not enabled, as soon as the TSC\_IOSCR bit is set, the corresponding GPIO analog switch is automatically controlled by the touch sensing controller.

Repeat (p), (q), (r) and (s) until ciphering or deciphering of all the payload blocks. Alternatively, DMA may be used.

- **GCM Final Phase:** In this last step, we generate the authentication tag.

- t) Choose the combination GCMPH[1:0] = 11 in AES\_CR.

- u) Write 4 times the input into the AES\_DINR register: the input must be composed of the length of header coded on 64 bits followed with the length of payload coded on 64 bits.

- v) Wait until the computation flag CCF in AES\_SR register is set to 1 (or use the corresponding interrupt).

- w) Read 4 times the AES\_DOUTR register: the output is the "auth tag".

- x) Clear CCF flag in AES\_SR register by setting CCFC bit in AES\_CR to 1.

- y) Disable AES processor by setting bit EN in AES\_CR to 0.

No need to disable / enable AES processor when moving from header phase to tag phase.

AES can move directly from init to payload or/and to tag (bypassing header phase or/and payload phase) in this case AES enable step should be added after selecting the next phase.

### **AES Galois message authentication code (GMAC)**

The AES processor supports also GMAC to authenticate the plaintext based on GCM algorithm for generating the corresponding TAG.

It is based on a multiplier over a fixed finite field for generating the TAG. It requires an initialization vector at the beginning.

Actually GMAC is the same as GCM applied on a message composed only by the header, so all steps and settings are the same except phase 3 will not be used.

### Suspend mode in GCM

In GCM algorithm, suspend mode can be performed during header phase and payload phase. It is advised to not use suspend mode in init phase or tag phase since suspend mode has no benefit in these phases:

Suspend mode during header phase: the user must respect the following steps:

- Before interrupting the current message:

- a) Make sure that CCF flag read from AES\_SR is set to 1.

- b) Clear CCF flag in AES\_SR register by setting CCFC in AES\_CR to 1.

- c) Save AES\_SUSPxR registers in the memory.

- d) Disable AES processor by setting EN in AES\_CR to 0.

- e) Save the current AES configuration in the memory.

- To resume:

- f) Make sure that AES processor is disabled by reading the bit EN in AES\_CR.

- g) Write back AES\_SUSPxR registers into their corresponding suspend registers.

- h) Re-configure AES with the initial setting values in CR register, IV register and key registers.

- i) Enable the AES processor by setting EN in AES\_CR register.

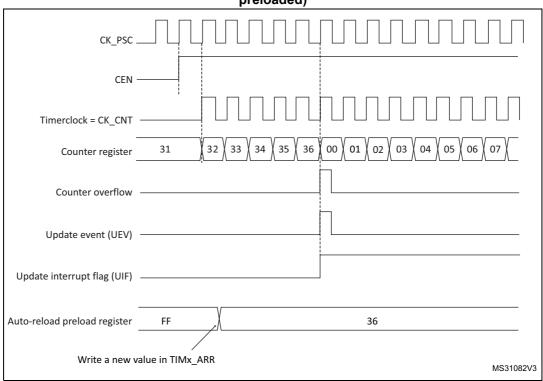

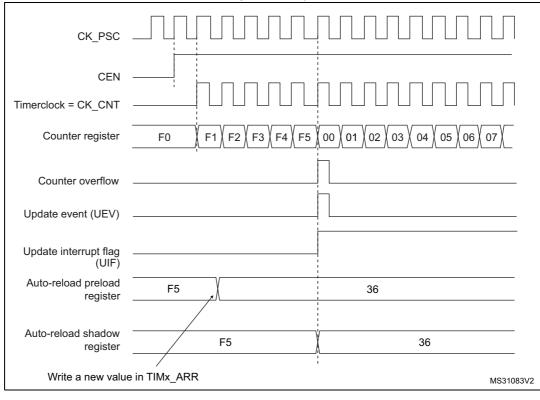

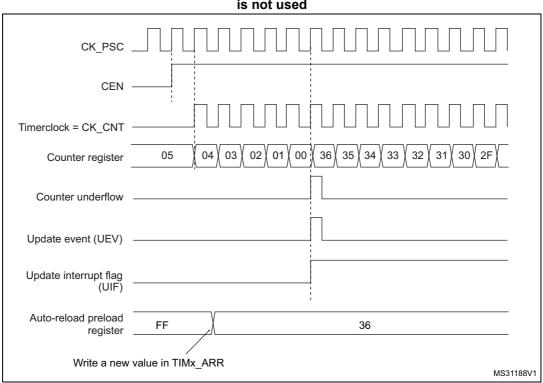

Figure 160. Counter timing diagram, update event when ARPE=0 (TIMx\_ARR not preloaded)

Figure 161. Counter timing diagram, update event when ARPE=1 (TIMx\_ARR preloaded)

DocID027295 Rev 3

### Center-aligned mode (up/down counting)

In center-aligned mode, the counter counts from 0 to the auto-reload value (content of the  $TIMx\_ARR$  register) – 1, generates a counter overflow event, then counts from the auto-reload value down to 1 and generates a counter underflow event. Then it restarts counting from 0.

Center-aligned mode is active when the CMS bits in TIMx\_CR1 register are not equal to '00'. The Output compare interrupt flag of channels configured in output is set when: the counter counts down (Center aligned mode 1, CMS = "01"), the counter counts up (Center aligned mode 2, CMS = "10") the counter counts up and down (Center aligned mode 3, CMS = "11").

In this mode, the direction bit (DIR from TIMx\_CR1 register) cannot be written. It is updated by hardware and gives the current direction of the counter.

The update event can be generated at each counter overflow and at each counter underflow or by setting the UG bit in the TIMx\_EGR register (by software or by using the slave mode controller) also generates an update event. In this case, the counter restarts counting from 0, as well as the counter of the prescaler.

The UEV update event can be disabled by software by setting the UDIS bit in TIMx\_CR1 register. This is to avoid updating the shadow registers while writing new values in the preload registers. Then no update event occurs until the UDIS bit has been written to 0. However, the counter continues counting up and down, based on the current auto-reload value.

In addition, if the URS bit (update request selection) in TIMx\_CR1 register is set, setting the UG bit generates an update event UEV but without setting the UIF flag (thus no interrupt or

CC2P=1 and CC2NP=0 in TIMx\_CCER register to validate the polarity (and detect low level only).

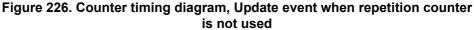

2. Configure the timer in trigger mode by writing SMS=110 in TIMx\_SMCR register. Select TI2 as the input source by writing TS=110 in TIMx\_SMCR register.

When a rising edge occurs on TI2, the counter starts counting on the internal clock and the TIF flag is set.

The delay between the rising edge on TI2 and the actual start of the counter is due to the resynchronization circuit on TI2 input.

### Figure 254. Control circuit in trigger mode

### Slave mode: External Clock mode 2 + trigger mode

The external clock mode 2 can be used in addition to another slave mode (except external clock mode 1 and encoder mode). In this case, the ETR signal is used as external clock input, and another input can be selected as trigger input when operating in reset mode, gated mode or trigger mode. It is recommended not to select ETR as TRGI through the TS bits of TIMx\_SMCR register.

In the following example, the upcounter is incremented at each rising edge of the ETR signal as soon as a rising edge of TI1 occurs:

- 1. Configure the external trigger input circuit by programming the TIMx\_SMCR register as follows:

- ETF = 0000: no filter

- ETPS=00: prescaler disabled

- ETP=0: detection of rising edges on ETR and ECE=1 to enable the external clock mode 2.

- 2. Configure the channel 1 as follows, to detect rising edges on TI:

- IC1F=0000: no filter.

- The capture prescaler is not used for triggering and does not need to be configured.

- CC1S=01in TIMx\_CCMR1 register to select only the input capture source

- CC1P=0 and CC1NP=0 in TIMx\_CCER register to validate the polarity (and detect rising edge only).

- 3. Configure the timer in trigger mode by writing SMS=110 in TIMx\_SMCR register. Select TI1 as the input source by writing TS=101 in TIMx\_SMCR register.

# 34.6.3 RTC control register (RTC\_CR)

Address offset: 0x08

Backup domain reset value: 0x0000 0000

System reset: not affected

| 31   | 30    | 29     | 28     | 27   | 26   | 25    | 24    | 23   | 22  | 21          | 20      | 19     | 18         | 17    | 16    |

|------|-------|--------|--------|------|------|-------|-------|------|-----|-------------|---------|--------|------------|-------|-------|

| Res. | Res.  | Res.   | Res.   | Res. | Res. | Res.  | ITSE  | COE  | OSE | L[1:0]      | POL     | COSEL  | BKP        | SUB1H | ADD1H |

|      |       |        |        |      |      |       | rw    | rw   | rw  | rw          | rw      | rw     | rw         | w     | w     |

| 15   | 14    | 13     | 12     | 11   | 10   | 9     | 8     | 7    | 6   | 5           | 4       | 3      | 2          | 1     | 0     |

| TSIE | WUTIE | ALRBIE | ALRAIE | TSE  | WUTE | ALRBE | ALRAE | Res. | FMT | BYPS<br>HAD | REFCKON | TSEDGE | WUCKSEL[2: |       | 2:0]  |

| rw   | rw    | rw     | rw     | rw   | rw   | rw    | rw    |      | rw  | rw          | rw      | rw     | rw         | rw    | rw    |

Bits 31:25 Reserved, must be kept at reset value.

- Bit 24 ITSE: timestamp on internal event enable 0: internal event timestamp disabled

- 1: internal event timestamp enabled

- Bit 23 COE: Calibration output enable

This bit enables the RTC\_CALIB output

- 0: Calibration output disabled

- 1: Calibration output enabled

- Bits 22:21 OSEL[1:0]: Output selection

These bits are used to select the flag to be routed to RTC\_ALARM output

- 00: Output disabled

- 01: Alarm A output enabled

- 10: Alarm B output enabled

- 11: Wakeup output enabled

- Bit 20 POL: Output polarity

- This bit is used to configure the polarity of RTC\_ALARM output

- 0: The pin is high when ALRAF/ALRBF/WUTF is asserted (depending on OSEL[1:0])

- 1: The pin is low when ALRAF/ALRBF/WUTF is asserted (depending on OSEL[1:0]).

#### Bit 19 **COSEL**: Calibration output selection

When COE=1, this bit selects which signal is output on RTC\_CALIB.

0: Calibration output is 512 Hz (with default prescaler setting)

1: Calibration output is 1 Hz (with default prescaler setting)

These frequencies are valid for RTCCLK at 32.768 kHz and prescalers at their default values (PREDIV\_A=127 and PREDIV\_S=255). Refer to *Section 34.3.15: Calibration clock output*

Bit 18 BKP: Backup

This bit can be written by the user to memorize whether the daylight saving time change has been performed or not.

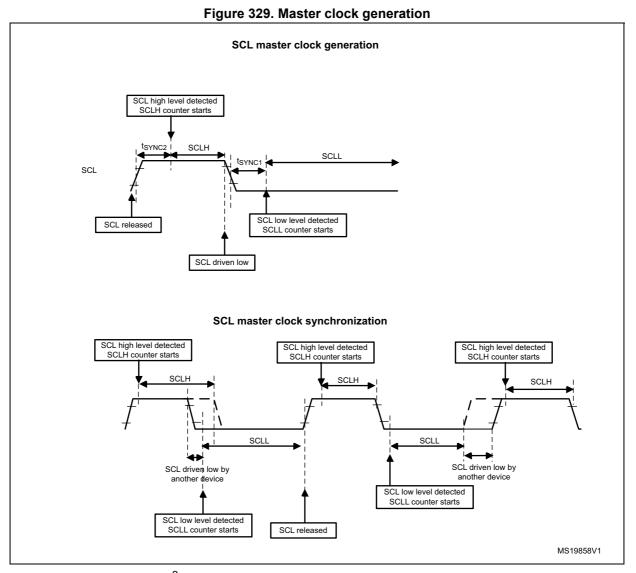

**Caution:** In order to be I<sup>2</sup>C or SMBus compliant, the master clock must respect the timings given below:

#### Bit 13 START: Start generation

This bit is set by software, and cleared by hardware after the Start followed by the address sequence is sent, by an arbitration loss, by a timeout error detection, or when PE = 0. It can also be cleared by software by writing '1' to the ADDRCF bit in the I2C\_ICR register.

- 0: No Start generation.

- 1: Restart/Start generation:

- If the I2C is already in master mode with AUTOEND = 0, setting this bit generates a Repeated Start condition when RELOAD=0, after the end of the NBYTES transfer.

- Otherwise setting this bit will generate a START condition once the bus is free.

- Note: Writing '0' to this bit has no effect.

The START bit can be set even if the bus is BUSY or I2C is in slave mode. This bit has no effect when RELOAD is set. In 10-bit addressing mode, if a NACK is received on the first part of the address, the START bit is not cleared by hardware and the master will resend the address sequence, unless the START bit is cleared by software

Bit 12 HEAD10R: 10-bit address header only read direction (master receiver mode)

0: The master sends the complete 10 bit slave address read sequence: Start + 2 bytes 10bit address in write direction + Restart + 1st 7 bits of the 10 bit address in read direction.

1: The master only sends the 1st 7 bits of the 10 bit address, followed by Read direction.

Note: Changing this bit when the START bit is set is not allowed.

Bit 11 **ADD10**: 10-bit addressing mode (master mode)

0: The master operates in 7-bit addressing mode,

1: The master operates in 10-bit addressing mode

Note: Changing this bit when the START bit is set is not allowed.

- Bit 10 RD\_WRN: Transfer direction (master mode)

- 0: Master requests a write transfer.

- 1: Master requests a read transfer.

Note: Changing this bit when the START bit is set is not allowed.

Bits 9:8 **SADD[9:8]**: Slave address bit 9:8 (master mode)

In 7-bit addressing mode (ADD10 = 0):

These bits are don't care

#### In 10-bit addressing mode (ADD10 = 1):

These bits should be written with bits 9:8 of the slave address to be sent *Note: Changing these bits when the START bit is set is not allowed.*

- Bits 7:1 SADD[7:1]: Slave address bit 7:1 (master mode)

- In 7-bit addressing mode (ADD10 = 0):

These bits should be written with the 7-bit slave address to be sent In 10-bit addressing mode (ADD10 = 1):

These bits should be written with bits 7:1 of the slave address to be sent. *Note: Changing these bits when the START bit is set is not allowed.*

Bit 0 SADD0: Slave address bit 0 (master mode)

In 7-bit addressing mode (ADD10 = 0):

This bit is don't care

In 10-bit addressing mode (ADD10 = 1):

This bit should be written with bit 0 of the slave address to be sent

Note: Changing these bits when the START bit is set is not allowed.

- In transmission, the USART inserts the Guard Time (as programmed in the Guard Time register) between two successive characters. As the Guard Time is measured after the stop bit of the previous character, the GT[7:0] register must be programmed to the desired CGT (Character Guard Time, as defined by the 7816-3 specification) minus 12 (the duration of one character).

- The assertion of the TC flag can be delayed by programming the Guard Time register. In normal operation, TC is asserted when the transmit shift register is empty and no further transmit requests are outstanding. In Smartcard mode an empty transmit shift register triggers the Guard Time counter to count up to the programmed value in the Guard Time register. TC is forced low during this time. When the Guard Time counter reaches the programmed value TC is asserted high.

- The TCBGT flag can be used to detect the end of data transfer without waiting for guard time completion. This flag is set just after the end of frame transmission and if no NACK has been received from the card.

- The de-assertion of TC flag is unaffected by Smartcard mode.

- If a framing error is detected on the transmitter end (due to a NACK from the receiver), the NACK is not detected as a start bit by the receive block of the transmitter. According to the ISO protocol, the duration of the received NACK can be 1 or 2 baud clock periods.

- On the receiver side, if a parity error is detected and a NACK is transmitted the receiver does not detect the NACK as a start bit.

- Note: A break character is not significant in Smartcard mode. A 0x00 data with a framing error is treated as data and not as a break.

No Idle frame is transmitted when toggling the TE bit. The Idle frame (as defined for the other configurations) is not defined by the ISO protocol.

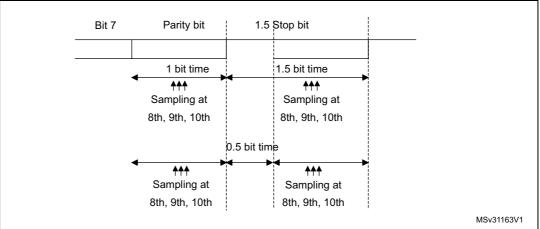

*Figure 363* details how the NACK signal is sampled by the USART. In this example the USART is transmitting data and is configured with 1.5 stop bits. The receiver part of the USART is enabled in order to check the integrity of the data and the NACK signal.

Figure 363. Parity error detection using the 1.5 stop bits

The USART can provide a clock to the smartcard through the CK output. In Smartcard mode, CK is not associated to the communication but is simply derived from the internal peripheral input clock through a 5-bit prescaler. The division ratio is configured in the prescaler register USART\_GTPR. CK frequency can be programmed from  $f_{CK}/2$  to  $f_{CK}/62$ , where  $f_{CK}$  is the peripheral input clock.

DocID027295 Rev 3

- Note: In order to provide correctly the CK clock to the Smartcard, the steps below must be respected:

- UE = 0

- SCEN = 1

- GTPR configuration

- CLKEN= 1

- UE = 1

- Bit 10 CPOL: Clock polarity

- This bit allows the user to select the polarity of the clock output on the CK pin in synchronous mode. It works in conjunction with the CPHA bit to produce the desired clock/data relationship

- 0: Steady low value on CK pin outside transmission window

- 1: Steady high value on CK pin outside transmission window

- This bit can only be written when the USART is disabled (UE=0).

- Note: If synchronous mode is not supported, this bit is reserved and forced by hardware to '0'. Please refer to Section 36.4: USART implementation on page 1085.

- Bit 9 CPHA: Clock phase

This bit is used to select the phase of the clock output on the CK pin in synchronous mode. It works in conjunction with the CPOL bit to produce the desired clock/data relationship (see *Figure 359* and *Figure 360*)

- 0: The first clock transition is the first data capture edge

- 1: The second clock transition is the first data capture edge

This bit can only be written when the USART is disabled (UE=0).

- Note: If synchronous mode is not supported, this bit is reserved and forced by hardware to '0'. Please refer to Section 36.4: USART implementation on page 1085.

- Bit 8 LBCL: Last bit clock pulse

This bit is used to select whether the clock pulse associated with the last data bit transmitted (MSB) has to be output on the CK pin in synchronous mode.

- 0: The clock pulse of the last data bit is not output to the CK pin

- 1: The clock pulse of the last data bit is output to the CK pin

- Caution: The last bit is the 7th or 8th or 9th data bit transmitted depending on the 7 or 8 or 9 bit format selected by the M bits in the USART\_CR1 register.

- This bit can only be written when the USART is disabled (UE=0).

- Note: If synchronous mode is not supported, this bit is reserved and forced by hardware to '0'. Please refer to Section 36.4: USART implementation on page 1085.

- Bit 7 Reserved, must be kept at reset value.

- Bit 6 **LBDIE**: LIN break detection interrupt enable

- Break interrupt mask (break detection using break delimiter).

- 0: Interrupt is inhibited

- 1: An interrupt is generated whenever LBDF=1 in the USART\_ISR register

- Note: If LIN mode is not supported, this bit is reserved and forced by hardware to '0'. Please refer to Section 36.4: USART implementation on page 1085.

#### Bit 11 RTOF: Receiver timeout

This bit is set by hardware when the timeout value, programmed in the RTOR register has lapsed, without any communication. It is cleared by software, writing 1 to the RTOCF bit in the USART\_ICR register.

An interrupt is generated if RTOIE=1 in the USART\_CR1 register.

In Smartcard mode, the timeout corresponds to the CWT or BWT timings.

0: Timeout value not reached

1: Timeout value reached without any data reception

Note: If a time equal to the value programmed in RTOR register separates 2 characters, RTOF is not set. If this time exceeds this value + 2 sample times (2/16 or 2/8, depending on the oversampling method), RTOF flag is set.

The counter counts even if RE = 0 but RTOF is set only when RE = 1. If the timeout has already elapsed when RE is set, then RTOF will be set.

If the USART does not support the Receiver timeout feature, this bit is reserved and forced by hardware to '0'.

#### Bit 10 CTS: CTS flag

This bit is set/reset by hardware. It is an inverted copy of the status of the CTS input pin. 0: CTS line set

1: CTS line reset

- Note: If the hardware flow control feature is not supported, this bit is reserved and forced by hardware to '0'.

- Bit 9 CTSIF: CTS interrupt flag

This bit is set by hardware when the CTS input toggles, if the CTSE bit is set. It is cleared by software, by writing 1 to the CTSCF bit in the USART\_ICR register.

An interrupt is generated if CTSIE=1 in the USART\_CR3 register.

0: No change occurred on the CTS status line

1: A change occurred on the CTS status line

Note: If the hardware flow control feature is not supported, this bit is reserved and forced by hardware to '0'.

Bit 8 LBDF: LIN break detection flag

This bit is set by hardware when the LIN break is detected. It is cleared by software, by writing 1 to the LBDCF in the USART\_ICR.

An interrupt is generated if LBDIE = 1 in the USART\_CR2 register.

- 0: LIN Break not detected

- 1: LIN break detected

- Note: If the USART does not support LIN mode, this bit is reserved and forced by hardware to '0'. Please refer to Section 36.4: USART implementation on page 1085.

### Bit 7 TXE: Transmit data register empty

This bit is set by hardware when the content of the USART\_TDR register has been transferred into the shift register. It is cleared by a write to the USART\_TDR register. The TXE flag can also be cleared by writing 1 to the TXFRQ in the USART\_RQR register, in order to discard the data (only in Smartcard T=0 mode, in case of transmission failure). An interrupt is generated if the TXEIE bit =1 in the USART\_CR1 register.

0: data is not transferred to the shift register

1: data is transferred to the shift register)

Note: This bit is used during single buffer transmission.

## 36.8.10 Receive data register (USART\_RDR)

Address offset: 0x24

Reset value: Undefined

| 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20       | 19   | 18   | 17   | 16   |

|------|------|------|------|------|------|------|------|------|------|------|----------|------|------|------|------|

| Res.     | Res. | Res. | Res. | Res. |

|      |      |      |      |      |      |      |      |      |      |      |          |      |      |      |      |

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4        | 3    | 2    | 1    | 0    |

| Res. |      |      |      |      | RDR[8:0] | ]    |      |      |      |

|      |      |      |      |      |      |      | r    | r    | r    | r    | r        | r    | r    | r    | r    |

Bits 31:9 Reserved, must be kept at reset value.

#### Bits 8:0 RDR[8:0]: Receive data value

Contains the received data character.

The RDR register provides the parallel interface between the input shift register and the internal bus (see *Figure 347*).

When receiving with the parity enabled, the value read in the MSB bit is the received parity bit.

# 36.8.11 Transmit data register (USART\_TDR)

Address offset: 0x28

Reset value: Undefined

| 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20       | 19   | 18   | 17   | 16   |

|------|------|------|------|------|------|------|------|------|------|------|----------|------|------|------|------|

| Res.     | Res. | Res. | Res. | Res. |

|      |      |      |      |      |      |      |      |      |      |      |          |      |      |      |      |

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4        | 3    | 2    | 1    | 0    |

| Res. |      |      |      |      | TDR[8:0] |      |      |      |      |

|      |      |      |      |      |      |      |      |      |      |      |          |      |      |      |      |

Bits 31:9 Reserved, must be kept at reset value.

Bits 8:0 TDR[8:0]: Transmit data value

Contains the data character to be transmitted.

The TDR register provides the parallel interface between the internal bus and the output shift register (see *Figure 347*).

When transmitting with the parity enabled (PCE bit set to 1 in the USART\_CR1 register), the value written in the MSB (bit 7 or bit 8 depending on the data length) has no effect because it is replaced by the parity.

Note: This register must be written only when TXE=1.

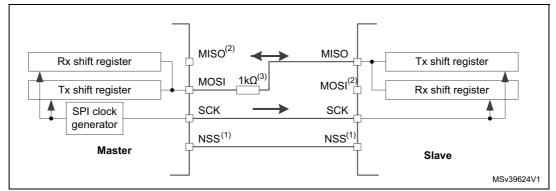

### Half-duplex communication

The SPI can communicate in half-duplex mode by setting the BIDIMODE bit in the SPIx\_CR1 register. In this configuration, one single cross connection line is used to link the shift registers of the master and slave together. During this communication, the data is synchronously shifted between the shift registers on the SCK clock edge in the transfer direction selected reciprocally by both master and slave with the BDIOE bit in their SPIx\_CR1 registers. In this configuration, the master's MISO pin and the slave's MOSI pin are free for other application uses and act as GPIOs.

- 1. The NSS pins can be used to provide a hardware control flow between master and slave. Optionally, the pins can be left unused by the peripheral. Then the flow has to be handled internally for both master and slave. For more details see *Section 38.4.5*: *Slave select (NSS) pin management*.

- 2. In this configuration, the master's MISO pin and the slave's MOSI pin can be used as GPIOs.

- 3. A critical situation can happen when communication direction is changed not synchronously between two nodes working at bidirectionnal mode and new transmitter accesses the common data line while former transmitter still keeps an opposite value on the line (the value depends on SPI configuration and communication data). Both nodes then fight while providing opposite output levels on the common line temporary till next node changes its direction settings correspondingly, too. It is suggested to insert a serial resistance between MISO and MOSI pins at this mode to protect the outputs and limit the current blowing between them at this situation.

### **Simplex communications**

The SPI can communicate in simplex mode by setting the SPI in transmit-only or in receiveonly using the RXONLY bit in the SPIx\_CR2 register. In this configuration, only one line is used for the transfer between the shift registers of the master and slave. The remaining MISO and MOSI pins pair is not used for communication and can be used as standard GPIOs.

- **Transmit-only mode (RXONLY=0):** The configuration settings are the same as for fullduplex. The application has to ignore the information captured on the unused input pin. This pin can be used as a standard GPIO.

- Receive-only mode (RXONLY=1): The application can disable the SPI output function by setting the RXONLY bit. In slave configuration, the MISO output is disabled and the pin can be used as a GPIO. The slave continues to receive data from the MOSI pin while its slave select signal is active (see 38.4.5: Slave select (NSS) pin management). Received data events appear depending on the data buffer configuration. In the master configuration, the MOSI output is disabled and the pin can be used as a GPIO. The clock signal is generated continuously as long as the SPI is enabled. The only way to stop the clock is to clear the RXONLY bit or the SPE bit and wait until the incoming pattern from the MISO pin is finished and fills the data buffer structure, depending on its configuration.

registers (IO\_RW\_EXTENDED, CMD53) to temporarily stall the data transfer while allowing the MMC/SD module to send commands to any function within the SD I/O device. To determine when a card supports the ReadWait protocol, the MMC/SD module must test capability bits in the internal card registers. The timing for ReadWait is based on the interrupt period.

## 41.4.14 Commands and responses

### Application-specific and general commands

The SDMMC card host module system is designed to provide a standard interface for a variety of applications types. In this environment, there is a need for specific customer/application features. To implement these features, two types of generic commands are defined in the standard: application-specific commands (ACMD) and general commands (GEN\_CMD).

When the card receives the APP\_CMD (CMD55) command, the card expects the next command to be an application-specific command. ACMDs have the same structure as regular MultiMediaCard commands and can have the same CMD number. The card recognizes it as ACMD because it appears after APP\_CMD (CMD55). When the command immediately following the APP\_CMD (CMD55) is not a defined application-specific command, the standard command is used. For example, when the card has a definition for SD\_STATUS (ACMD13), and receives CMD13 immediately following APP\_CMD (CMD55), this is interpreted as SD\_STATUS (ACMD13). However, when the card receives CMD7 immediately following APP\_CMD (CMD55) and the card does not have a definition for ACMD7, this is interpreted as the standard (SELECT/DESELECT\_CARD) CMD7.

To use one of the manufacturer-specific ACMDs the SD card Host must perform the following steps:

- Send APP\_CMD (CMD55) The card responds to the MultiMediaCard/SD module, indicating that the APP\_CMD bit is set and an ACMD is now expected.

- 2. Send the required ACMD

The card responds to the MultiMediaCard/SD module, indicating that the APP\_CMD bit is set and that the accepted command is interpreted as an ACMD. When a nonACMD is sent, it is handled by the card as a normal MultiMediaCard command and the APP\_CMD bit in the card status register stays clear.

When an invalid command is sent (neither ACMD nor CMD) it is handled as a standard MultiMediaCard illegal command error.

The bus transaction for a GEN\_CMD is the same as the single-block read or write commands (WRITE\_BLOCK, CMD24 or READ\_SINGLE\_BLOCK, CMD17). In this case, the argument denotes the direction of the data transfer rather than the address, and the data block has vendor-specific format and meaning.

The card must be selected (in transfer state) before sending GEN\_CMD (CMD56). The data block size is defined by SET\_BLOCKLEN (CMD16). The response to GEN\_CMD (CMD56) is in R1b format.

### Scalable width

To optimize and adapt the filters to the application needs, each filter bank can be scaled independently. Depending on the filter scale a filter bank provides:

- One 32-bit filter for the STDID[10:0], EXTID[17:0], IDE and RTR bits.

- Two 16-bit filters for the STDID[10:0], RTR, IDE and EXTID[17:15] bits.

Refer to Figure 448.

Furthermore, the filters can be configured in mask mode or in identifier list mode.

#### Mask mode

In **mask** mode the identifier registers are associated with mask registers specifying which bits of the identifier are handled as "must match" or as "don't care".

#### Identifier list mode

In **identifier list** mode, the mask registers are used as identifier registers. Thus instead of defining an identifier and a mask, two identifiers are specified, doubling the number of single identifiers. All bits of the incoming identifier must match the bits specified in the filter registers.

### Filter bank scale and mode configuration

The filter banks are configured by means of the corresponding CAN\_FMR register. To configure a filter bank it must be deactivated by clearing the FACT bit in the CAN\_FAR register. The filter scale is configured by means of the corresponding FSCx bit in the CAN\_FS1R register, refer to *Figure 448*. The **identifier list** or **identifier mask** mode for the corresponding Mask/Identifier registers is configured by means of the FBMx bits in the CAN\_FMR register.

To filter a group of identifiers, configure the Mask/Identifier registers in mask mode.

To select single identifiers, configure the Mask/Identifier registers in identifier list mode.

Filters not used by the application should be left deactivated.

Each filter within a filter bank is numbered (called the *Filter Number*) from 0 to a maximum dependent on the mode and the scale of each of the filter banks.

Concerning the filter configuration, refer to Figure 448.