Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                 |

|----------------------------|----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                     |

| Speed                      | 80MHz                                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                             |

| Number of I/O              | 38                                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 64K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                           |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                                  |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 48-UFQFN Exposed Pad                                                                   |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l433ccu6                  |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Range 2,  $V_{CORE}$  = 1.0 V so  $V_{DD12}$  should be greater than 1.05 V

- $V_{DD12} \ge 1.08$  V in Range 2 when SYSCLK frequency  $\ge 26$  MHz

- In all other modes, ie LPRun, LPSleep, Stop 1, Stop 2, Standby and Shutdown modes, VDD12 must be disconnected from SMPS output, ie pin must be connected to an high impedance output:

- VDD12 connected to HiZ (voltage is provided by internal regulators)

- Transitions of VDD12 from connected to disconnected is only allowed when SYSCLK frequency ≤ 26 MHz to avoid to big voltage drop on main regulator side.

Note: In case of reset while having the  $V_{DD12} \le 1.25 \text{ V}$ , VDD12 should switch to HiZ in less than regulator switching time from Range 2 to Range 1 (~1 us).

### 5.1.7 Dynamic voltage scaling management

The dynamic voltage scaling is a power management technique which consists in increasing or decreasing the voltage used for the digital peripherals ( $V_{CORE}$ ), according to the application performance and power consumption needs.

Dynamic voltage scaling to increase  $V_{\mbox{CORE}}$  is known as overvolting. It allows to improve the device performance.

Dynamic voltage scaling to decrease  $V_{CORE}$  is known as undervolting. It is performed to save power, particularly in laptop and other mobile devices where the energy comes from a battery and is thus limited.

• Range 1: High-performance range.

The main regulator provides a typical output voltage at 1.2 V. The system clock frequency can be up to 80 MHz. The Flash access time for read access is minimum, write and erase operations are possible.

• Range 2: Low-power range.

The main regulator provides a typical output voltage at 1.0 V. The system clock frequency can be up to 26 MHz. The Flash access time for a read access is increased as compared to Range 1; write and erase operations are possible.

Voltage scaling is selected through the VOS bit in the PWR\_CR1 register.

The sequence to go from Range 1 to Range 2 is:

- 1. Reduce the system frequency to a value lower than 26 MHz

- 2. Adjust number of wait states according new frequency target in Range 2 (LATENCY bits in the FLASH\_ACR).

- 3. Program the VOS bits to "10" in the PWR\_CR1 register.

The sequence to go from Range 2 to Range 1 is:

- 1. Program the VOS bits to "01" in the PWR\_CR1 register.

- 2. Wait until the VOSF flag is cleared in the PWR\_SR2 register.

- 3. Adjust number of wait states according new frequency target in Range 1 (LATENCY bits in the FLASH\_ACR).

- 4. Increase the system frequency.

When supplying VDD12 with an external SMPS, we are defining 3 new states:

• "SMPS range 1": main regulator is in Range 1 and V<sub>CORE</sub> is supplied by external

|                | Table 25. Stop 1 mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stop 1 mode    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                | <ul> <li>WFI (Wait for Interrupt) or WFE (Wait for Event) while:</li> <li>SLEEPDEEP bit is set in Cortex<sup>®</sup>-M4 System Control register</li> <li>No interrupt (for WFI) or event (for WFE) is pending</li> <li>LPMS = "001" in PWR_CR1</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Mode entry     | On Return from ISR while:<br>– SLEEPDEEP bit is set in Cortex <sup>®</sup> -M4 System Control register<br>– SLEEPONEXIT = 1<br>– No interrupt is pending<br>– LPMS = "001" in PWR_CR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                | Note: To enter Stop 1 mode, all EXTI Line pending bits (in Pending<br>register 1 (EXTI_PR1)), and the peripheral flags generating wakeup<br>interrupts must be cleared. Otherwise, the Stop 1 mode entry<br>procedure is ignored and program execution continues.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Mode exit      | <ul> <li>If WFI or Return from ISR was used for entry <ul> <li>Any EXTI Line configured in Interrupt mode (the corresponding EXTI Interrupt vector must be enabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to <i>Table 45: STM32L43xxx/44xxx/45xxx/46xxx vector table</i>.</li> <li>If WFE was used for entry and SEVONPEND = 0: <ul> <li>Any EXTI Line configured in event mode. Refer to <i>Section 13.3.2: Wakeup event management</i>.</li> </ul> </li> <li>If WFE was used for entry and SEVONPEND = 1: <ul> <li>Any EXTI Line configured in Interrupt mode (even if the corresponding EXTI Interrupt vector is disabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to <i>Table 45: STM32L43xxx/44xxx/45xxx/46xxx vector table</i>.</li> </ul> </li> </ul></li></ul> |

| Wakeup latency | Longest wakeup time between: MSI or HSI16 wakeup time and regulator wakeup time from Low-power mode + Flash wakeup time from Stop 1 mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Table 25. Stop 1 mo |

|---------------------|

|---------------------|

# 5.3.8 Stop 2 mode

The Stop 2 mode is based on the Cortex<sup>®</sup>-M4 deepsleep mode combined with peripheral clock gating. In Stop 2 mode, all clocks in the  $V_{CORE}$  domain are stopped, the PLL, the MSI, the HSI16 and the HSE oscillators are disabled. Some peripherals with wakeup capability (I2C3 and LPUART) can switch on the HSI16 to receive a frame, and switch off the HSI16 after receiving the frame if it is not a wakeup frame. In this case the HSI16 clock is propagated only to the peripheral requesting it.

SRAM1, SRAM2 and register contents are preserved.

The BOR is always available in Stop 2 mode. The consumption is increased when thresholds higher than  $V_{BOR0}$  are used.

*Note:* The comparators outputs, the LPUART outputs and the LPTIM1 outputs are forced to low speed (OSPEEDy=00) during the Stop 2 mode.

DocID027295 Rev 3

- Bit 10 RTCAPBSMEN: RTC APB clock enable during Sleep and Stop modes

- Set and cleared by software

- 0: RTC APB clock disabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes 1: RTC APB clock enabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes

- Bit 9 LCDSMEN<sup>(5)</sup>: LCD clocks enable during Sleep and Stop modes

- Set and cleared by software.

- 0: LCD clocks disabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes 1: LCD clocks enabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes

- Bits 8:6 Reserved, must be kept at reset value.

- Bit 5 TIM7SMEN<sup>(6)</sup>: TIM7 timer clocks enable during Sleep and Stop modes Set and cleared by software.

- 0: TIM7 clocks disabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes 1: TIM7 clocks enabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes

- Bit 4 TIM6SMEN: TIM6 timer clocks enable during Sleep and Stop modes

- Set and cleared by software.

- 0: TIM6 clocks disabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes

- 1: TIM6 clocks enabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes

- Bits 3:2 Reserved, must be kept at reset value.

- Bit 1 TIM3SMEN<sup>(4)</sup>: TIM3 timer clocks enable during Sleep and Stop modes

- Set and cleared by software.

- 0: TIM3 clocks disabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes

- 1: TIM3 clocks enabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes

- Bit 0 TIM2SMEN: TIM2 timer clocks enable during Sleep and Stop modes

- Set and cleared by software.

- 0: TIM2 clocks disabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes 1: TIM2 clocks enabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes

- This register only configures the clock gating, not the clock source itself. Most of the peripherals are clocked by a single clock (AHB or APB clock), which is always disabled in Stop mode. In this case setting the bit has no effect in Stop mode.

- 2. Available on STM32L4x2xx and STM32L4x3xx devices only.

- Not available on STM32L432xx and STM32L442xx devices. 3

- Available on STM32L45xxx and STM32L46xxx devices only. 4

- Available on STM32L4x3xx devices only. 5.

- Available on STM32L43xxx and STM32L44xxx devices only.

#### 6.4.25 APB1 peripheral clocks enable in Sleep and Stop modes register 2 (RCC APB1SMENR2)

Address offset: 0x7C

Reset value: 0x0000 0025

Access: no wait state, word, half-word and byte access

#### Bit 4 SSHIFT: Sample shift

By default, the QUADSPI samples data 1/2 of a CLK cycle after the data is driven by the Flash memory. This bit allows the data is to be sampled later in order to account for external signal delays.

0: No shift

1: 1/2 cycle shift

Firmware must assure that SSHIFT = 0 when in DDR mode (when DDRM = 1). This field can be modified only when BUSY = 0.

#### Bit 3 **TCEN**: Timeout counter enable

This bit is valid only when memory-mapped mode (FMODE = 11) is selected. Activating this bit causes the chip select (nCS) to be released (and thus reduces consumption) if there has not been an access after a certain amount of time, where this time is defined by TIMEOUT[15:0] (QUADSPI\_LPTR).

Enable the timeout counter.

By default, the QUADSPI never stops its prefetch operation, keeping the previous read operation active with nCS maintained low, even if no access to the Flash memory occurs for a long time. Since Flash memories tend to consume more when nCS is held low, the application might want to activate the timeout counter (TCEN = 1, bit 3 of QUADSPI\_CR) so that nCS is released after a period of TIMEOUT[15:0] (QUADSPI\_LPTR) cycles have elapsed without an access since when the FIFO becomes full with prefetch data.

0: Timeout counter is disabled, and thus the chip select (nCS) remains active indefinitely after an access in memory-mapped mode.

1: Timeout counter is enabled, and thus the chip select is released in memory-mapped mode after TIMEOUT[15:0] cycles of Flash memory inactivity. This bit can be modified only when BUSY = 0.

#### Bit 2 **DMAEN**: DMA enable

In indirect mode, DMA can be used to input or output data via the QUADSPI\_DR register. DMA transfers are initiated when the FIFO threshold flag, FTF, is set.

0: DMA is disabled for indirect mode

1: DMA is enabled for indirect mode

#### Bit 1 ABORT: Abort request

This bit aborts the on-going command sequence. It is automatically reset once the abort is complete.

This bit stops the current transfer.

- In polling mode or memory-mapped mode, this bit also reset the APM bit or the DM bit.

- 0: No abort requested

- 1: Abort requested

- Bit 0 EN: Enable

Enable the QUADSPI.

0: QUADSPI is disabled

1: QUADSPI is enabled

# 16.4.5 Slave AHB interface

The ADC implements an AHB slave port for control/status register and data access. The features of the AHB interface are listed below:

- Word (32-bit) accesses

- Single cycle response

- Response to all read/write accesses to the registers with zero wait states.

The AHB slave interface does not support split/retry requests, and never generates AHB errors.

# 16.4.6 ADC Deep-power-down mode (DEEPPWD) & ADC Voltage Regulator (ADVREGEN)

By default, the ADC is in Deep-power-down mode where its supply is internally switched off to reduce the leakage currents (the reset state of bit DEEPPWD is 1 in the ADC\_CR register).

To start ADC operations, it is first needed to exit Deep-power-down mode by setting bit DEEPPWD=0.

Then, it is mandatory to enable the ADC internal voltage regulator by setting the bit ADVREGEN=1 into ADC\_CR register. The software must wait for the startup time of the ADC voltage regulator ( $T_{ADCVREG\_STUP}$ ) before launching a calibration or enabling the ADC. This delay must be implemented by software.

For the startup time of the ADC voltage regulator, please refer to device datasheet for  $T_{ADCVREG\ STUP}$  parameter.

After ADC operations are complete, the ADC can be disabled (ADEN=0). It is possible to save power by also disabling the ADC voltage regulator. This is done by writing bit ADVREGEN=0.

Then, to save more power by reducing the leakage currents, it is also possible to re-enter in ADC Deep-power-down mode by setting bit DEEPPWD=1 into ADC\_CR register. This is particularly interesting before entering STOP mode.

*Note:* Writing DEEPPWD=1 automatically disables the ADC voltage regulator and bit ADVREGEN is automatically cleared.

When the internal voltage regulator is disabled (ADVREGEN=0), the internal analog calibration is kept.

In ADC Deep-power-down mode (DEEPPWD=1), the internal analog calibration is lost and it is necessary to either relaunch a calibration or re-apply the calibration factor which was previously saved (refer to *Section 16.4.8: Calibration (ADCAL, ADCALDIF, ADC\_CALFACT)*).

| ADC state      | RDY                | Sampling Ch(N)                   | Converting Ch(N)                       | Sampling Ch(N+1) |  |  |  |  |  |

|----------------|--------------------|----------------------------------|----------------------------------------|------------------|--|--|--|--|--|

| Analog channel |                    | Ch(N)                            | X1111111111111111111111111111111111111 | Ch(N+1)          |  |  |  |  |  |

| Internal S/H   | X                  | Sample AIN(N)                    | Hold AIN(N)                            | Sample AIN(N+1)  |  |  |  |  |  |

|                | Set 🔶              | t <sub>SMPL</sub> <sup>(1)</sup> | t <sub>SAR</sub> <sup>(2)</sup>        | -<br>-<br>-<br>- |  |  |  |  |  |

| ADSTART        | by S/W             |                                  |                                        | <br> <br>        |  |  |  |  |  |

| EOSMP          |                    | Set<br>by H/W                    | Cleared                                |                  |  |  |  |  |  |

| EOC            |                    |                                  | Set<br>by H/W                          | Cleared          |  |  |  |  |  |

| ADC_DR         |                    | Data N                           |                                        |                  |  |  |  |  |  |

|                | Indicative timings |                                  |                                        |                  |  |  |  |  |  |

|                |                    |                                  |                                        | MS30532V1        |  |  |  |  |  |

Figure 47. Analog to digital conversion time

1. T<sub>SMPL</sub> depends on SMP[2:0]

2. T<sub>SAR</sub> depends on RES[2:0]

# 16.4.17 Stopping an ongoing conversion (ADSTP, JADSTP)

The software can decide to stop regular conversions ongoing by setting ADSTP=1 and injected conversions ongoing by setting JADSTP=1.

Stopping conversions will reset the ongoing ADC operation. Then the ADC can be reconfigured (ex: changing the channel selection or the trigger) ready for a new operation.

Note that it is possible to stop injected conversions while regular conversions are still operating and vice-versa. This allows, for instance, re-configuration of the injected conversion sequence and triggers while regular conversions are still operating (and vice-versa).

When the ADSTP bit is set by software, any ongoing regular conversion is aborted with partial result discarded (ADC\_DR register is not updated with the current conversion).

When the JADSTP bit is set by software, any ongoing injected conversion is aborted with partial result discarded (ADC\_JDRy register is not updated with the current conversion). The scan sequence is also aborted and reset (meaning that relaunching the ADC would restart a new sequence).

Once this procedure is complete, bits ADSTP/ADSTART (in case of regular conversion), or JADSTP/JADSTART (in case of injected conversion) are cleared by hardware and the software must poll ADSTART (or JADSTART) until the bit is reset before assuming the ADC is completely stopped.

Note: In auto-injection mode (JAUTO=1), setting ADSTP bit aborts both regular and injected conversions (JADSTP must not be used).

# 16.4.30 Oversampler

The oversampling unit performs data pre-processing to offload the CPU. It is able to handle multiple conversions and average them into a single data with increased data width, up to 16-bit.

It provides a result with the following form, where N and M can be adjusted:

Result =

$$\frac{1}{M} \times \sum_{n=0}^{n=N-1} Conversion(t_n)$$

It allows to perform by hardware the following functions: averaging, data rate reduction, SNR improvement, basic filtering.

The oversampling ratio N is defined using the OVFS[2:0] bits in the ADC\_CFGR2 register, and can range from 2x to 256x. The division coefficient M consists of a right bit shift up to 8 bits, and is defined using the OVSS[3:0] bits in the ADC\_CFGR2 register.

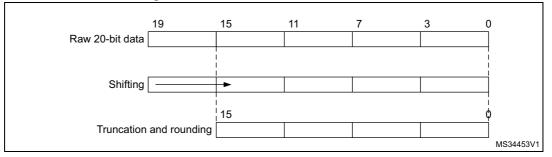

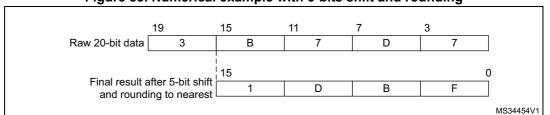

The summation unit can yield a result up to 20 bits (256x 12-bit results), which is first shifted right. It is then truncated to the 16 least significant bits, rounded to the nearest value using the least significant bits left apart by the shifting, before being finally transferred into the ADC\_DR data register.

Note: If the intermediary result after the shifting exceeds 16-bit, the result is truncated as is, without saturation.

Figure 82. 20-bit to 16-bit result truncation

The *Figure 83* gives a numerical example of the processing, from a raw 20-bit accumulated data to the final 16-bit result.

Figure 83. Numerical example with 5-bits shift and rounding

The *Table 65* below gives the data format for the various N and M combinations, for a raw conversion data equal to 0xFFF.

- Bits 31:23 Reserved, must be kept at reset value.

- Bits 22:16 CALFACT\_D[6:0]: Calibration Factors in differential mode

These bits are written by hardware or by software.

Once a differential inputs calibration is complete, they are updated by hardware with the calibration factors.

Software can write these bits with a new calibration factor. If the new calibration factor is different from the current one stored into the analog ADC, it will then be applied once a new differential calibration is launched.

- Note: Software is allowed to write these bits only when ADEN=1, ADSTART=0 and JADSTART=0 (ADC is enabled and no calibration is ongoing and no conversion is ongoing).

- Bits 15:7 Reserved, must be kept at reset value.

Bits 6:0 CALFACT\_S[6:0]: Calibration Factors In single-ended mode

These bits are written by hardware or by software.

Once a single-ended inputs calibration is complete, they are updated by hardware with the calibration factors.

Software can write these bits with a new calibration factor. If the new calibration factor is different from the current one stored into the analog ADC, it will then be applied once a new single-ended calibration is launched.

Note: Software is allowed to write these bits only when ADEN=1, ADSTART=0 and JADSTART=0 (ADC is enabled and no calibration is ongoing and no conversion is ongoing).

# 16.7 ADC common registers

These registers define the control and status registers common to master and slave ADCs:

# 16.7.1 ADC Common status register (ADC\_CSR)

Address offset: 0x00 (this offset address is relative to the master ADC base address + 0x300)

Reset value: 0x0000 0000

This register provides an image of the status bits of the different ADCs. Nevertheless it is read-only and does not allow to clear the different status bits. Instead each status bit must be cleared by writing 0 to it in the corresponding ADC\_SR register.

| 31   | 30   | 29   | 28   | 27   | 26            | 25           | 24           | 23           | 22           | 21           | 20          | 19          | 18          | 17            | 16            |

|------|------|------|------|------|---------------|--------------|--------------|--------------|--------------|--------------|-------------|-------------|-------------|---------------|---------------|

| Res. | Res. | Res. | Res. | Res. | Res.          | Res.         | Res.         | Res.         | Res.         | Res.         | Res.        | Res.        | Res.        | Res.          | Res.          |

|      |      |      |      |      |               |              |              |              |              |              |             |             |             |               |               |

| 15   | 14   | 13   | 12   | 11   | 10            | 9            | 8            | 7            | 6            | 5            | 4           | 3           | 2           | 1             | 0             |

| Res. | Res. | Res. | Res. | Res. | JQOVF_<br>MST | AWD3_<br>MST | AWD2_<br>MST | AWD1_<br>MST | JEOS_<br>MST | JEOC_<br>MST | OVR_<br>MST | EOS_<br>MST | EOC_<br>MST | EOSMP_<br>MST | ADRDY_<br>MST |

|      |      |      |      |      | r             | r            | r            | r            | r            | r            | r           | r           | r           | r             | r             |

Bits 31:11 Reserved, must be kept at reset value.

Bit 10 **JQOVF\_MST:** Injected Context Queue Overflow flag of the master ADC This bit is a copy of the JQOVF bit in the corresponding ADC\_ISR register.

Bit 9 AWD3\_MST: Analog watchdog 3 flag of the master ADC

This bit is a copy of the AWD3 bit in the corresponding ADC\_ISR register.

DocID027295 Rev 3

# 21.4.4 Serial channel transceivers

There are 4 multiplexed serial data channels which can be selected for conversion by each filter or Analog watchdog or Short-circuit detector. Those serial transceivers receive data stream from external  $\Sigma\Delta$  modulator. Data stream can be sent in SPI format or Manchester coded format (see SITP[1:0] bits in DFSDM\_CHyCFGR1 register).

The channel is enabled for operation by setting CHEN=1 in DFSDM\_CHyCFGR1 register.

# Channel inputs selection

Serial inputs (data and clock signals) from DATINy and CKINy pins can be redirected from the following channel pins. This serial input channel redirection is set by CHINSEL bit in DFSDM\_CHyCFGR1 register.

Channel redirection can be used to collect audio data from PDM (pulse density modulation) stereo microphone type. PDM stereo microphone has one data and one clock signal. Data signal provides information for both left and right audio channel (rising clock edge samples for left channel and falling clock edge samples for right channel).

Configuration of serial channels for PDM microphone input:

- PDM microphone signals (data, clock) will be connected to DFSDM input serial channel y (DATINy, CKOUT) pins.

- Channel y will be configured: CHINSEL = 0 (input from given channel pins: DATINy, CKINy).

- Channel (y-1) (modulo 4) will be configured: CHINSEL = 1 (input from the following channel ((y-1)+1) pins: DATINy, CKINy).

- Channel y: SITP[1:0] = 0 (rising edge to strobe data) => left audio channel on channel y.

- Channel (y-1): SITP[1:0] = 1 (falling edge to strobe data) => right audio channel on channel y-1.

- Two DFSDM filters will be assigned to channel y and channel (y-1) (to filter left and right channels from PDM microphone).

- Bit 9 CC3P: Capture/Compare 3 output polarity Refer to CC1P description

- Bit 8 **CC3E**: Capture/Compare 3 output enable Refer to CC1E description

- Bit 7 **CC2NP**: Capture/Compare 2 complementary output polarity Refer to CC1NP description

- Bit 6 **CC2NE**: Capture/Compare 2 complementary output enable Refer to CC1NE description

- Bit 5 **CC2P**: Capture/Compare 2 output polarity Refer to CC1P description

- Bit 4 CC2E: Capture/Compare 2 output enable Refer to CC1E description

- Bit 3 **CC1NP**: Capture/Compare 1 complementary output polarity

CC1 channel configured as output:

0: OC1N active high.

1: OC1N active low.

#### CC1 channel configured as input:

This bit is used in conjunction with CC1P to define the polarity of TI1FP1 and TI2FP1. Refer to CC1P description.

- Note: This bit is not writable as soon as LOCK level 2 or 3 has been programmed (LOCK bits in TIMx\_BDTR register) and CC1S="00" (channel configured as output).

- Note: On channels having a complementary output, this bit is preloaded. If the CCPC bit is set in the TIMx\_CR2 register then the CC1NP active bit takes the new value from the preloaded bit only when a Commutation event is generated.

- Bit 2 CC1NE: Capture/Compare 1 complementary output enable

0: Off - OC1N is not active. OC1N level is then function of MOE, OSSI, OSSR, OIS1, OIS1N and CC1E bits.

1: On - OC1N signal is output on the corresponding output pin depending on MOE, OSSI, OSSR, OIS1, OIS1N and CC1E bits.

Note: On channels having a complementary output, this bit is preloaded. If the CCPC bit is set in the TIMx\_CR2 register then the CC1NE active bit takes the new value from the preloaded bit only when a Commutation event is generated.

in the TIMx\_CR1 register. Moreover, the DIR and CMS bits must not be changed at the same time by the software.

- Writing to the counter while running in center-aligned mode is not recommended as it can lead to unexpected results. In particular:

- The direction is not updated if you write a value in the counter that is greater than the auto-reload value (TIMx\_CNT>TIMx\_ARR). For example, if the counter was counting up, it continues to count up.

- The direction is updated if you write 0 or write the TIMx\_ARR value in the counter but no Update Event UEV is generated.

- The safest way to use center-aligned mode is to generate an update by software (setting the UG bit in the TIMx\_EGR register) just before starting the counter and not to write the counter while it is running.

### 27.3.10 Asymmetric PWM mode

Asymmetric mode allows two center-aligned PWM signals to be generated with a programmable phase shift. While the frequency is determined by the value of the TIMx\_ARR register, the duty cycle and the phase-shift are determined by a pair of TIMx\_CCRx registers. One register controls the PWM during up-counting, the second during down counting, so that PWM is adjusted every half PWM cycle:

- OC1REFC (or OC2REFC) is controlled by TIMx\_CCR1 and TIMx\_CCR2

- OC3REFC (or OC4REFC) is controlled by TIMx\_CCR3 and TIMx\_CCR4

Asymmetric PWM mode can be selected independently on two channels (one OCx output per pair of CCR registers) by writing '1110' (Asymmetric PWM mode 1) or '1111' (Asymmetric PWM mode 2) in the OCxM bits in the TIMx\_CCMRx register.

Note:

The OCxM[3:0] bit field is split into two parts for compatibility reasons, the most significant bit is not contiguous with the 3 least significant ones.

When a given channel is used as asymmetric PWM channel, its secondary channel can also be used. For instance, if an OC1REFC signal is generated on channel 1 (Asymmetric PWM mode 1), it is possible to output either the OC2REF signal on channel 2, or an OC2REFC signal resulting from asymmetric PWM mode 2.

*Figure 245* shows an example of signals that can be generated using Asymmetric PWM mode (channels 1 to 4 are configured in Asymmetric PWM mode 1).

|                            |   |                               |     | <br>      |           |

|----------------------------|---|-------------------------------|-----|-----------|-----------|

| <br>Counter register<br>   |   | 3 4 5                         | 6 7 | 5 4 3 2 1 |           |

| OC1REFC<br>CCR1=0          |   | <br> <br> <br> <br> <br> <br> |     |           | -         |

| CCR2=8<br>CCR3=3<br>CCR4=5 |   |                               |     |           |           |

|                            | 1 | I                             |     | 1         | 1         |

|                            |   |                               |     |           | MS33117V1 |

Figure 245. Generation of 2 phase-shifted PWM signals with 50% duty cycle

#### Output compare mode

- Bits 31:25 Reserved, always read as 0.

- Bit 24 OC4M[3]: Output Compare 2 mode bit 3

- Bits 23:17 Reserved, always read as 0.

- Bit 16 OC3M[3]: Output Compare 1 mode bit 3

- Bit 15 **OC4CE**: Output compare 4 clear enable

- Bits 14:12 **OC4M**: Output compare 4 mode Refer to OC1M description (bits 6:4 in TIMx CCMR1 register)

- Bit 11 OC4PE: Output compare 4 preload enable

- Bit 10 OC4FE: Output compare 4 fast enable

#### Bits 9:8 CC4S: Capture/Compare 4 selection

- This bit-field defines the direction of the channel (input/output) as well as the used input.

- 00: CC4 channel is configured as output

- 01: CC4 channel is configured as input, IC4 is mapped on TI4

- 10: CC4 channel is configured as input, IC4 is mapped on TI3

- 11: CC4 channel is configured as input, IC4 is mapped on TRC. This mode is working only if an internal trigger input is selected through TS bit (TIMx\_SMCR register)

- Note: CC4S bits are writable only when the channel is OFF (CC4E = 0 in TIMx\_CCER).

- Bit 7 OC3CE: Output compare 3 clear enable

- Bits 6:4 OC3M: Output compare 3 mode

Refer to OC1M description (bits 6:4 in TIMx\_CCMR1 register)

- Bit 3 **OC3PE**: Output compare 3 preload enable

- Bit 2 **OC3FE**: Output compare 3 fast enable

- Bits 1:0 CC3S: Capture/Compare 3 selection

This bit-field defines the direction of the channel (input/output) as well as the used input.

- 00: CC3 channel is configured as output

- 01: CC3 channel is configured as input, IC3 is mapped on TI3

- 10: CC3 channel is configured as input, IC3 is mapped on TI4

- 11: CC3 channel is configured as input, IC3 is mapped on TRC. This mode is working only if an internal trigger input is selected through TS bit (TIMx\_SMCR register)

- Note: CC3S bits are writable only when the channel is OFF (CC3E = 0 in TIMx\_CCER).

#### Input capture mode

- Bits 31:16 Reserved, always read as 0.

- Bits 15:12 IC4F: Input capture 4 filter

- Bits 11:10 **IC4PSC**: Input capture 4 prescaler

- Bits 9:8 **CC4S**: Capture/Compare 4 selection

- This bit-field defines the direction of the channel (input/output) as well as the used input.

- 00: CC4 channel is configured as output

- 01: CC4 channel is configured as input, IC4 is mapped on TI4

- 10: CC4 channel is configured as input, IC4 is mapped on TI3

- 11: CC4 channel is configured as input, IC4 is mapped on TRC. This mode is working only if an internal trigger input is selected through TS bit (TIMx\_SMCR register)

Note: CC4S bits are writable only when the channel is OFF (CC4E = 0 in TIMx\_CCER).

DocID027295 Rev 3

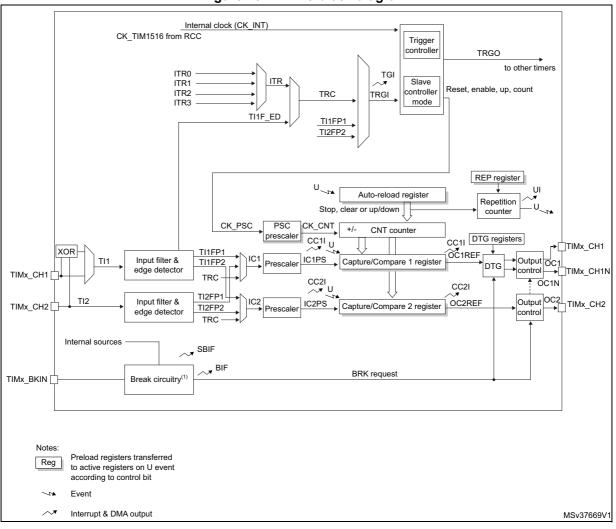

Figure 262. TIM15 block diagram

The internal break event source can be: 1.

A clock failure event generated by CSS. For further information on the CSS, refer to Section 6.2.10: Clock security system

- A PVD output SRAM parity error signal Cortex<sup>®</sup>-M4 LOCKUP (Hardfault) output COMP output

# 30.7.2 LPTIM interrupt clear register (LPTIM\_ICR)

Address offset: 0x04

Reset value: 0x0000 0000

| 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22         | 21   | 20          | 19          | 18            | 17         | 16         |

|------|------|------|------|------|------|------|------|------|------------|------|-------------|-------------|---------------|------------|------------|

| Res.       | Res. | Res.        | Res.        | Res.          | Res.       | Res.       |

|      |      |      |      |      |      |      |      |      |            |      |             |             |               |            |            |

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6          | 5    | 4           | 3           | 2             | 1          | 0          |

| Res. | DOWN<br>CF | UPCF | ARRO<br>KCF | CMPO<br>KCF | EXTTR<br>IGCF | ARRM<br>CF | CMPM<br>CF |

|      |      |      |      |      |      |      |      |      | w          | w    | w           | w           | w             | w          | w          |

- Bits 31:7 Reserved, must be kept at reset value.

- Bit 6 **DOWNCF**: Direction change to down Clear Flag Writing 1 to this bit clear the DOWN flag in the LPT\_ISR register

- Bit 5 **UPCF**: Direction change to UP Clear Flag Writing 1 to this bit clear the UP flag in the LPT\_ISR register

- Bit 4 **ARROKCF**: Autoreload register update OK Clear Flag Writing 1 to this bit clears the ARROK flag in the LPT\_ISR register

- Bit 3 **CMPOKCF**: Compare register update OK Clear Flag Writing 1 to this bit clears the CMPOK flag in the LPT\_ISR register

- Bit 2 **EXTTRIGCF**: External trigger valid edge Clear Flag Writing 1 to this bit clears the EXTTRIG flag in the LPT\_ISR register

- Bit 1 **ARRMCF**: Autoreload match Clear Flag Writing 1 to this bit clears the ARRM flag in the LPT\_ISR register

- Bit 0 **CMPMCF**: compare match Clear Flag Writing 1 to this bit clears the CMP flag in the LPT\_ISR register

except if the TAMPxNOERASE bit is set, or if TAMPxMF is set in the RTC\_TAMPCR register.

#### Tamper detection initialization

Each input can be enabled by setting the corresponding TAMPxE bits to 1 in the RTC\_TAMPCR register.

Each RTC\_TAMPx tamper detection input is associated with a flag TAMPxF in the RTC\_ISR register.

When TAMPxMF is cleared:

The TAMPxF flag is asserted after the tamper event on the pin, with the latency provided below:

- 3 ck\_apre cycles when TAMPFLT differs from 0x0 (Level detection with filtering)

- 3 ck\_apre cycles when TAMPTS=1 (Timestamp on tamper event)

- No latency when TAMPFLT=0x0 (Edge detection) and TAMPTS=0

A new tamper occurring on the same pin during this period and as long as TAMPxF is set cannot be detected.

When TAMPxMF is set:

A new tamper occurring on the same pin cannot be detected during the latency described above and 2.5 ck\_rtc additional cycles.

By setting the TAMPIE bit in the RTC\_TAMPCR register, an interrupt is generated when a tamper detection event occurs (when TAMPxF is set). Setting TAMPIE is not allowed when one or more TAMPxMF is set.

When TAMPIE is cleared, each tamper pin event interrupt can be individually enabled by setting the corresponding TAMPxIE bit in the RTC\_TAMPCR register. Setting TAMPxIE is not allowed when the corresponding TAMPxMF is set.

#### Trigger output generation on tamper event

The tamper event detection can be used as trigger input by the low-power timers.

When TAMPxMF bit in cleared in RTC\_TAMPCR register, the TAMPxF flag must be cleared by software in order to allow a new tamper detection on the same pin.

When TAMPxMF bit is set, the TAMPxF flag is masked, and kept cleared in RTC\_ISR register. This configuration allows to trig automatically the low-power timers in Stop mode, without requiring the system wakeup to perform the TAMPxF clearing. In this case, the backup registers are not cleared.

#### Timestamp on tamper event

With TAMPTS set to '1', any tamper event causes a timestamp to occur. In this case, either the TSF bit or the TSOVF bit are set in RTC\_ISR, in the same manner as if a normal timestamp event occurs. The affected tamper flag register TAMPxF is set at the same time that TSF or TSOVF is set.

#### Edge detection on tamper inputs

If the TAMPFLT bits are "00", the RTC\_TAMPx pins generate tamper detection events when either a rising edge or a falling edge is observed depending on the corresponding

#### **SMBus Slave receiver**

When the I2C is used in SMBus mode, SBC must be programmed to '1' in order to allow the PEC checking at the end of the programmed number of data bytes. In order to allow the ACK control of each byte, the reload mode must be selected (RELOAD=1). Refer to *Slave Byte Control mode on page 1027* for more details.

In order to check the PEC byte, the RELOAD bit must be cleared and the PECBYTE bit must be set. In this case, after NBYTES-1 data have been received, the next received byte is compared with the internal I2C\_PECR register content. A NACK is automatically generated if the comparison does not match, and an ACK is automatically generated if the comparison matches, whatever the ACK bit value. Once the PEC byte is received, it is copied into the I2C\_RXDR register like any other data, and the RXNE flag is set.

In the case of a PEC mismatch, the PECERR flag is set and an interrupt is generated if the ERRIE bit is set in the I2C\_CR1 register.

If no ACK software control is needed, the user can program PECBYTE=1 and, in the same write operation, program NBYTES with the number of bytes to be received in a continuous flow. After NBYTES-1 are received, the next received byte is checked as being the PEC.

**Caution:** The PECBYTE bit has no effect when the RELOAD bit is set.

Bits 3:2 Reserved, must be kept at reset value.

- Bit 1 **TXE:** Transmit buffer empty 0: Tx buffer not empty 1: Tx buffer empty

- Bit 0 RXNE: Receive buffer not empty

- 0: Rx buffer empty

- 1: Rx buffer not empty

# 38.6.4 SPI data register (SPIx\_DR)

Address offset: 0x0C

Reset value: 0x0000

| 15 | 14       | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    | DR[15:0] |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| rw | rw       | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 15:0 DR[15:0]: Data register

Data received or to be transmitted

The data register serves as an interface between the Rx and Tx FIFOs. When the data register is read, RxFIFO is accessed while the write to data register accesses TxFIFO (See *Section 38.4.9: Data transmission and reception procedures*).

Note: Data is always right-aligned. Unused bits are ignored when writing to the register, and read as zero when the register is read. The Rx threshold setting must always correspond with the read access currently used.

# 38.6.5 SPI CRC polynomial register (SPIx\_CRCPR)

Address offset: 0x10

Reset value: 0x0007

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8     | 7        | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|-------|----------|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    | CRCPO | LY[15:0] |    |    |    |    |    | _  |    |

| rw    | rw       | rw | rw | rw | rw | rw | rw | rw |

Bits 15:0 CRCPOLY[15:0]: CRC polynomial register

This register contains the polynomial for the CRC calculation.

The CRC polynomial (0007h) is the reset value of this register. Another polynomial can be configured as required.

Note: The polynomial value should be odd only. No even value is supported.

# 41 SD/SDIO/MMC card host interface (SDMMC)

This section does not apply to STM32L432xx and STM32L442xx devices.

# 41.1 SDMMC main features

The SD/SDIO MMC card host interface (SDMMC) provides an interface between the APB2 peripheral bus and MultiMediaCards (MMCs), SD memory cards and SDIO cards.

The MultiMediaCard system specifications are available through the MultiMediaCard Association website, published by the MMCA technical committee.

SD memory card and SD I/O card system specifications are available through the SD card Association website.

The SDMMC features include the following:

- Full compliance with *MultiMediaCard System Specification Version 4.2*. Card support for three different databus modes: 1-bit (default), 4-bit and 8-bit

- Full compatibility with previous versions of MultiMediaCards (forward compatibility)

- Full compliance with SD Memory Card Specifications Version 2.0

- Full compliance with SD I/O Card Specification Version 2.0: card support for two different databus modes: 1-bit (default) and 4-bit

- Data transfer up to 50 MHz for the 8 bit mode

- Data and command output enable signals to control external bidirectional drivers.

- Note: 1 The SDMMC does not have an SPI-compatible communication mode.

- 2 The SD memory card protocol is a superset of the MultiMediaCard protocol as defined in the MultiMediaCard system specification V2.11. Several commands required for SD memory devices are not supported by either SD I/O-only cards or the I/O portion of combo cards. Some of these commands have no use in SD I/O devices, such as erase commands, and thus are not supported in the SDIO protocol. In addition, several commands are different between SD memory cards and SD I/O card sand thus are not supported in the SDIO protocol. For details refer to SD I/O card Specification Version 1.0.

The MultiMediaCard/SD bus connects cards to the controller.

The current version of the SDMMC supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

# 41.2 SDMMC bus topology

Communication over the bus is based on command and data transfers.

The basic transaction on the MultiMediaCard/SD/SD I/O bus is the command/response transaction. These types of bus transaction transfer their information directly within the command or response structure. In addition, some operations have a data token.

Data transfers to/from SD/SDIO memory cards are done in data blocks. Data transfers to/from MMC are done data blocks or streams.

| -        | 5                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Flag     | Description                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| TXFIFOF  | Set to high when all 32 transmit FIFO words contain valid data.                                                                                                                               |  |  |  |  |  |  |  |  |

| TXFIFOE  | Set to high when the transmit FIFO does not contain valid data.                                                                                                                               |  |  |  |  |  |  |  |  |

| TXFIFOHE | Set to high when 8 or more transmit FIFO words are empty. This flag can be used as a DMA request.                                                                                             |  |  |  |  |  |  |  |  |

| TXDAVL   | Set to high when the transmit FIFO contains valid data. This flag is the inverse of the TXFIFOE flag.                                                                                         |  |  |  |  |  |  |  |  |

|          | Set to high when an underrun error occurs. This flag is cleared by writing to the SDMMC Clear register.                                                                                       |  |  |  |  |  |  |  |  |

| TXUNDERR | Note: In case of TXUNDERR, and DMA is used to fill SDMMC FIFO, user software should disable DMA stream, and then write DMAEN bit in SDMMC_DCTRL with '0' (to disable DMA request generation). |  |  |  |  |  |  |  |  |

#### Table 204. Transmit FIFO status flags

Receive FIFO

When the data path subunit receives a word of data, it drives the data on the write databus. The write pointer is incremented after the write operation completes. On the read side, the contents of the FIFO word pointed to by the current value of the read pointer is driven onto the read databus. If the receive FIFO is disabled, all status flags are deasserted, and the read and write pointers are reset. The data path subunit asserts RXACT when it receives data. *Table 205* lists the receive FIFO status flags. The receive FIFO is accessible via 32 sequential addresses.

#### Table 205. Receive FIFO status flags

| Flag     | Description                                                                                                                                                                                        |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXFIFOF  | Set to high when all 32 receive FIFO words contain valid data                                                                                                                                      |

| RXFIFOE  | Set to high when the receive FIFO does not contain valid data.                                                                                                                                     |

| RXFIFOHF | Set to high when 8 or more receive FIFO words contain valid data. This flag can be used as a DMA request.                                                                                          |

| RXDAVL   | Set to high when the receive FIFO is not empty. This flag is the inverse of the RXFIFOE flag.                                                                                                      |

|          | Set to high when an overrun error occurs. This flag is cleared by writing to the SDMMC Clear register.                                                                                             |

| RXOVERR  | Note: In case of RXOVERR, and DMA is used to read SDMMC FIFO, user<br>software should disable DMA stream, and then write DMAEN bit in<br>SDMMC_DCTRL with '0' (to disable DMA request generation). |

- Bit 31 **DBG\_LPTIM1\_STOP:** LPTIM1 counter stopped when core is halted

- 0: The counter clock of LPTIM1 is fed even if the core is halted

- 1: The counter clock of LPTIM1 is stopped when the core is halted

- Bits 30:26 Reserved, must be kept at reset value.

- Bit 25 **DBG\_CAN\_STOP:** bxCAN stopped when core is halted

- 0: Same behavior as in normal mode

- 1: The bxCAN receive registers are frozen

- Bit 24 Reserved, must be kept at reset value.

- Bit 23 DBG\_I2C3\_STOP: I2C3 SMBUS timeout counter stopped when core is halted

- 0: Same behavior as in normal mode

1: The I2C3 SMBus timeout is frozen

- Bit 22 **DBG\_I2C2\_STOP:** I2C2 SMBUS timeout counter stopped when core is halted 0: Same behavior as in normal mode 1: The I2C2 SMBus timeout is frozen

- Bit 21 **DBG\_I2C1\_STOP:** I2C1 SMBUS timeout counter stopped when core is halted 0: Same behavior as in normal mode

- 1: The I2C1 SMBus timeout is frozen

- Bits 20:13 Reserved, must be kept at reset value.

- Bit 12 **DBG\_IWDG\_STOP:** Independent watchdog counter stopped when core is halted 0: The independent watchdog counter clock continues even if the core is halted 1: The independent watchdog counter clock is stopped when the core is halted

- Bit 11 **DBG\_WWDG\_STOP:** Window watchdog counter stopped when core is halted 0: The window watchdog counter clock continues even if the core is halted 1: The window watchdog counter clock is stopped when the core is halted

- Bit 10 **DBG\_RTC\_STOP:** RTC counter stopped when core is halted

- 0: The clock of the RTC counter is fed even if the core is halted

- 1: The clock of the RTC counter is stopped when the core is halted

- Bits 9:6 Reserved, must be kept at reset value.

- Bit 5 **DBG\_TIM7\_STOP**: TIM7 counter stopped when core is halted 0: The counter clock of TIM7 is fed even if the core is halted 1: The counter clock of TIM7 is stopped when the core is halted

- Bit 4 **DBG\_TIM6\_STOP**: TIM6 counter stopped when core is halted 0: The counter clock of TIM6 is fed even if the core is halted 1: The counter clock of TIM6 is stopped when the core is halted

- Bits 3:1 Reserved, must be kept at reset value.

- Bit 0 **DBG\_TIM2\_STOP:** TIM2 counter stopped when core is halted 0: The counter clock of TIM2 is fed even if the core is halted 1: The counter clock of TIM2 is stopped when the core is halted

### 44.16.5 Debug MCU APB1 freeze register 2 (DBGMCU\_APB1FZR2)

Address: 0xE004 200C Power on reset (POR): 0x0000 0000 System reset: not affected

DocID027295 Rev 3