Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                 |

| Core Processor             | ARM® Cortex®-M4                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                     |

| Speed                      | 80MHz                                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                             |

| Number of I/O              | 52                                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 64K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                  |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 64-UFBGA                                                                               |

| Supplier Device Package    | 64-UFBGA (5x5)                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l433rbi6                  |

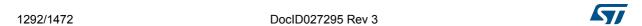

Figure 4. Changing the Read protection (RDP) level

Table 12. Access status versus protection level and execution modes

| Area         | Protection level | User exec | cution (BootFr     | romFlash) | Debug/ BootFromRam/<br>BootFromLoader <sup>(1)</sup> |                    |                   |  |  |  |  |

|--------------|------------------|-----------|--------------------|-----------|------------------------------------------------------|--------------------|-------------------|--|--|--|--|

|              | ievei            | Read      | Write              | Erase     | Read                                                 | Write              | Erase             |  |  |  |  |

| Flash main   | 1                | Yes       | Yes                | Yes       | No                                                   | No                 | No <sup>(3)</sup> |  |  |  |  |

| memory       | 2                | Yes       | Yes                | Yes       | N/A                                                  | N/A                | N/A               |  |  |  |  |

| System       | 1                | Yes       | No                 | No        | Yes                                                  | No                 | No                |  |  |  |  |

| memory (2)   | 2                | Yes       | No                 | No        | N/A                                                  | N/A                | N/A               |  |  |  |  |

| Ontion byton | 1                | Yes       | Yes <sup>(3)</sup> | Yes       | Yes                                                  | Yes <sup>(3)</sup> | Yes               |  |  |  |  |

| Option bytes | 2                | Yes       | No                 | No        | N/A                                                  | N/A                | N/A               |  |  |  |  |

| OTP          | 1                | Yes       | Yes <sup>(4)</sup> | N/A       | No                                                   | No                 | N/A               |  |  |  |  |

| OIF          | 2                | Yes       | Yes <sup>(4)</sup> | N/A       | N/A                                                  | N/A                | N/A               |  |  |  |  |

| Backup       | 1                | Yes       | Yes                | N/A       | No                                                   | No                 | No <sup>(5)</sup> |  |  |  |  |

| registers    | 2                | Yes       | Yes                | N/A       | N/A                                                  | N/A                | N/A               |  |  |  |  |

### 8.3.6 **GPIO** locking mechanism

It is possible to freeze the GPIO control registers by applying a specific write sequence to the GPIOx\_LCKR register. The frozen registers are GPIOx\_MODER, GPIOx\_OTYPER, GPIOx\_OSPEEDR, GPIOx\_PUPDR, GPIOx\_AFRL and GPIOx\_AFRH.

To write the GPIOx\_LCKR register, a specific write / read sequence has to be applied. When the right LOCK sequence is applied to bit 16 in this register, the value of LCKR[15:0] is used to lock the configuration of the I/Os (during the write sequence the LCKR[15:0] value must be the same). When the LOCK sequence has been applied to a port bit, the value of the port bit can no longer be modified until the next MCU reset or peripheral reset. Each GPIOx\_LCKR bit freezes the corresponding bit in the control registers (GPIOx\_MODER, GPIOx\_OTYPER, GPIOx\_OSPEEDR, GPIOx\_PUPDR, GPIOx\_AFRL and GPIOx\_AFRH.

The LOCK sequence (refer to Section 8.4.8: GPIO port configuration lock register (GPIOx\_LCKR) (x = A..E and H)) can only be performed using a word (32-bit long) access to the GPIOx\_LCKR register due to the fact that GPIOx\_LCKR bit 16 has to be set at the same time as the [15:0] bits.

For more details refer to LCKR register description in Section 8.4.8: GPIO port configuration lock register (GPIOx\_LCKR) (x = A..E and H).

# 8.3.7 I/O alternate function input/output

Two registers are provided to select one of the alternate function inputs/outputs available for each I/O. With these registers, the user can connect an alternate function to some other pin as required by the application.

This means that a number of possible peripheral functions are multiplexed on each GPIO using the GPIOx\_AFRL and GPIOx\_AFRH alternate function registers. The application can thus select any one of the possible functions for each I/O. The AF selection signal being common to the alternate function input and alternate function output, a single channel is selected for the alternate function input/output of a given I/O.

To know which functions are multiplexed on each GPIO pin, refer to the device datasheet.

No alternate function is mapped on PH3.

# 8.3.8 External interrupt/wakeup lines

All ports have external interrupt capability. To use external interrupt lines, the port must be configured in input mode. Section 13: Extended interrupts and events controller (EXTI) and to Section 13.3.2: Wakeup event management.

### 8.3.9 Input configuration

When the I/O port is programmed as input:

- The output buffer is disabled

- The Schmitt trigger input is activated

- The pull-up and pull-down resistors are activated depending on the value in the GPIOx\_PUPDR register

- The data present on the I/O pin are sampled into the input data register every AHB clock cycle

- A read access to the input data register provides the I/O state

Table 36. GPIO register map and reset values (continued)

| Offset | Register                       | 72   | 0    | ရ    | 28   | 7:   | 9    | 5    | 4    | 33   | 2    | Σ.   | 0:   | 6    | 8    | 7    | 9    | 2     | 14    | 13    | 2     | _     | 10    | 6            | 8    | 7    | 9    | 2    | 4    | က    | 7    | 7    | 0    |

|--------|--------------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-------|-------|-------|-------|-------|-------|--------------|------|------|------|------|------|------|------|------|------|

|        | 3                              | (r)  | (r)  | 7    | ~    | N    | N    | N    | ~    | ~    | ~    | 7    | ~    | _    | _    | 1    | 1    | _     | _     | _     | 1     | _     | 1     |              |      |      |      |      | Ĭ    |      |      |      |      |

| 0x14   | GPIOx_ODR<br>(where x = AE,H)  | Res. | OD15  | OD14  | OD13  | OD12  | OD11  | OD 10 | 6 <b>Q</b> O | OD8  | OD7  | OD6  | OD5  | OD4  | OD3  | OD2  | OD1  | OD0  |

|        | Reset value                    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | 0     | 0     | 0     | 0     | 0     | 0     | 0            | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0x18   | GPIOx_BSRR<br>(where x = AE,H) | BR15 | BR14 | BR13 | BR12 | BR11 | BR10 | BR9  | BR8  | BR7  | BR6  | BR5  | BR4  | BR3  | BR2  | BR1  | BR0  | BS15  | BS14  | BS13  | BS12  | BS11  | BS10  | BS9          | BS8  | BS7  | BS6  | BS5  | BS4  | BS3  | BS2  | BS1  | BS0  |

|        | Reset value                    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0     | 0            | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0x1C   | GPIOx_LCKR<br>(where x = AE,H) | Res. | LCKK | LCK15 | LCK14 | LCK13 | LCK12 | LCK11 | LCK10 | LCK9         | LCK8 | LCK7 | LCK6 | LCK5 | LCK4 | LCK3 | LCK2 | LCK1 | LCK0 |

|        | Reset value                    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | 0    | 0     | 0     | 0     | 0     | 0     | 0     | 0            | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0x20   | GPIOx_AFRL<br>(where x = AE,H) | AF   | SE   | L7[3 | 3:0] | AF   | SEI  | L6[3 | 3:0] | AF   | SE   | L5[3 | 3:0] | AF   | SE   | L4[3 | 3:0] | AF    | SE    | L3[3  | 3:0]  | AF    | SE    | L2[3         | 3:0] | AF   | SEI  | L1[3 | 3:0] | AF   | SEI  | _0[3 | :0]  |

|        | Reset value                    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0     | 0            | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0x24   | GPIOx_AFRH<br>(where x = AE,H) | AF   | SEL  | _15[ | 3:0] | AF:  | SEL  | .14[ | 3:0] | AF   | SEL  | .13[ | 3:0] | AF:  | SEL  | .12[ | 3:0] | AF:   | SEL   | .11[  | 3:0]  | AF    | SEL   | .10[         | 3:0] | AF   | SEI  | L9[3 | 3:0] | AF   | SEI  | _8[3 | :0]  |

|        | Reset value                    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0     | 0            | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0x28   | GPIOx_BRR<br>(where x = AE,H)  | Res. | BR15  | BR14  | BR13  | BR12  | BR11  | BR10  | BR9          | BR8  | BR7  | BR6  | BR5  | BR4  | BR3  | BR2  | BR1  | BR0  |

|        | Reset value                    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | 0     | 0     | 0     | 0     | 0     | 0     | 0            | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

Refer to Section 2.2.2 on page 64 for the register boundary addresses.

Note: Ti

The regular trigger selection cannot be changed on-the-fly.

The injected trigger selection can be anticipated and changed on-the-fly. Refer to Section 16.4.21: Queue of context for injected conversions on page 390

*Table 58* and *Table 59* give all the possible external triggers of the three ADCs for regular and injected conversion.

Table 58. ADC1 - External triggers for regular channels)

| Name  | Source                   | Туре                                | EXTSEL[3:0] |

|-------|--------------------------|-------------------------------------|-------------|

| EXT0  | TIM1_CH1                 | Internal signal from on-chip timers | 0000        |

| EXT1  | TIM1_CH2                 | Internal signal from on-chip timers | 0001        |

| EXT2  | TIM1_CH3                 | Internal signal from on-chip timers | 0010        |

| EXT3  | TIM2_CH2                 | Internal signal from on-chip timers | 0011        |

| EXT4  | TIM3_TRGO <sup>(1)</sup> | Internal signal from on-chip timers | 0100        |

| EXT5  | -                        | -                                   | 0101        |

| EXT6  | EXTI line 11             | External pin                        | 0110        |

| EXT9  | TIM1_TRGO                | Internal signal from on-chip timers | 1001        |

| EXT10 | TIM1_TRGO2               | Internal signal from on-chip timers | 1010        |

| EXT11 | TIM2_TRGO                | Internal signal from on-chip timers | 1011        |

| EXT13 | TIM6_TRGO                | Internal signal from on-chip timers | 1101        |

| EXT14 | TIM15_TRGO               | Internal signal from on-chip timers | 1110        |

<sup>1.</sup> Available only on STM32L451xx/452xx/462xx.

Table 59. ADC1 - External trigger for injected channels

| Name   | Source                  | Туре                                | JEXTSEL[30] |

|--------|-------------------------|-------------------------------------|-------------|

| JEXT0  | TIM1_TRGO               | Internal signal from on-chip timers | 0000        |

| JEXT1  | TIM1_CH4                | Internal signal from on-chip timers | 0001        |

| JEXT2  | TIM2_TRGO               | Internal signal from on-chip timers | 0010        |

| JEXT3  | TIM2_CH1                | Internal signal from on-chip timers | 0011        |

| JEXT4  | TIM3_CH4 <sup>(1)</sup> | Internal signal from on-chip timers | 0100        |

| JEXT5  | -                       | -                                   | 0101        |

| JEXT6  | EXTI line 15            | External pin                        | 0110        |

| JEXT8  | TIM1_TRGO2              | Internal signal from on-chip timers | 1000        |

| JEXT14 | TIM6_TRGO               | Internal signal from on-chip timers | 1110        |

| JEXT15 | TIM15_TRGO              | Internal signal from on-chip timers | 1111        |

<sup>1.</sup> Available only on STM32L451xx/452xx/462xx.

- ...

- DISCEN=0, channels to be converted = 1, 2, 3, 6, 7, 8, 9, 10,11

- 1st trigger: the complete sequence is converted: channel 1, then 2, 3, 6, 7, 8, 9, 10 and 11. Each conversion generates an EOC event and the last one also generates an EOS event.

- all the next trigger events will relaunch the complete sequence.

Note:

When a regular group is converted in discontinuous mode, no rollover occurs (the last subgroup of the sequence can have less than n conversions).

When all subgroups are converted, the next trigger starts the conversion of the first subgroup. In the example above, the 4th trigger reconverts the channels 1, 2 and 3 in the 1st subgroup.

It is not possible to have both discontinuous mode and continuous mode enabled. In this case (if DISCEN=1, CONT=1), the ADC behaves as if continuous mode was disabled.

### Injected group mode

This mode is enabled by setting the JDISCEN bit in the ADC\_CFGR register. It converts the sequence selected in the ADC\_JSQR register, channel by channel, after an external injected trigger event. This is equivalent to discontinuous mode for regular channels where 'n' is fixed to 1.

When an external trigger occurs, it starts the next channel conversions selected in the ADC\_JSQR registers until all the conversions in the sequence are done. The total sequence length is defined by the JL[1:0] bits in the ADC\_JSQR register.

#### Example:

- JDISCEN=1, channels to be converted = 1, 2, 3

- 1st trigger: channel 1 converted (a JEOC event is generated)

- 2nd trigger: channel 2 converted (a JEOC event is generated)

- 3rd trigger: channel 3 converted and a JEOC event + a JEOS event are generated

- ...

Note:

When all injected channels have been converted, the next trigger starts the conversion of the first injected channel. In the example above, the 4th trigger reconverts the 1st injected channel 1.

It is not possible to use both auto-injected mode and discontinuous mode simultaneously: the bits DISCEN and JDISCEN must be kept cleared by software when JAUTO is set.

### 16.4.21 Queue of context for injected conversions

A queue of context is implemented to anticipate up to 2 contexts for the next injected sequence of conversions. JQDIS bit of ADC\_CFGR register must be reset to enable this feature. Only hardware-triggered conversions are possible when the context queue is enabled.

This context consists of:

- Configuration of the injected triggers (bits JEXTEN[1:0] and JEXTSEL[3:0] in ADC\_JSQR register)

- Definition of the injected sequence (bits JSQx[4:0] and JL[1:0] in ADC\_JSQR register)

57

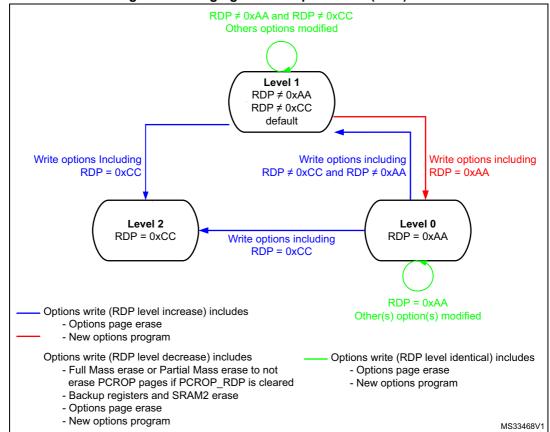

consequence, the converted digital value is one third of the  $V_{BAT}$  voltage. To prevent any unwanted consumption on the battery, it is recommended to enable the bridge divider only when needed, for ADC conversion.

Refer to the electrical characteristics of the device datasheet for the sampling time value to be applied when converting the  $V_{BAT}/3$  voltage.

The figure below shows the block diagram of the  $V_{BAT}$  sensing feature. The DAC2\_int signal and  $V_{BAT}$  sensing input share the same input.

Figure 90. V<sub>BAT</sub> channel block diagram

1. The CH18\_SEL bit must be set to enable the conversion of internal channels ADC1\_IN18 ( $V_{BAT}/3$ ).

# 16.4.33 Monitoring the internal voltage reference

It is possible to monitor the internal voltage reference ( $V_{REFINT}$ ) to have a reference point for evaluating the ADC  $V_{REF+}$  voltage level.

The internal voltage reference is internally connected to the input channel 0 of the ADC1 (ADC1 IN0).

Refer to the electrical characteristics section of the STM32L43xxx/44xxx/45xxx/46xxx datasheet for the sampling time value to be applied when converting the internal voltage reference voltage.

*Figure 91* shows the block diagram of the V<sub>REFINT</sub> sensing feature.

477

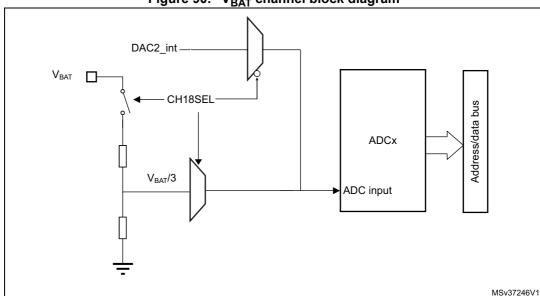

The detection of a clock absence in Manchester coding (after a first successful synchronization) is based on changes comparison of coded serial data input signal with output clock generation (CKOUT signal). There must be a voltage level change on DATINy pin during 2 periods of CKOUT signal (which is controlled by CKOUTDIV bits in DFSDM\_CH0CFGR1 register). This condition also defines the minimum data rate to be able to correctly recover the Manchester coded data and clock signals.

The maximum data rate of Manchester coded data must be less than the CKOUT signal.

So to correctly receive Manchester coded data, the CKOUTDIV divider must be set according the formula:

$$((CKOUTDIV + 1) \times T_{SYSCLK}) < T_{Manchester clock} < (2 \times CKOUTDIV \times T_{SYSCLK})$$

A clock absence flag is set (CKABF[y] = 1) and an interrupt can be invoked (if CKABIE=1) in case of an input clock recovery error (see CKABF[3:0] in DFSDM\_FLT0ISR register and CKABEN in DFSDM\_CHyCFGR1). After a clock absence flag clearing (by CLRCKABF in DFSDM\_FLT0ICR register), the clock absence flag is refreshed.

Figure 113. Clock absence timing diagram for Manchester coding

- enabled by JOVRIE bit in DFSDM FLTxCR2 register

- indicated in JOVRF bit in DFSDM\_FLTxISR register

- cleared by writing '1' into CLRJOVRF bit in DFSDM FLTxICR register

- Data overrun interrupt for regular conversions:

- occurred when regular converted data were not read from DFSDM\_FLTxRDATAR register (by CPU or DMA) and were overwritten by a new regular conversion

- enabled by ROVRIE bit in DFSDM FLTxCR2 register

- indicated in ROVRF bit in DFSDM\_FLTxISR register

- cleared by writing '1' into CLRROVRF bit in DFSDM\_FLTxICR register

- Analog watchdog interrupt:

- occurred when converted data (output data or data from analog watchdog filter according to AWFSEL bit setting in DFSDM\_FLTxCR1 register) crosses over/under high/low thresholds in DFSDM\_FLTxAWHTR / DFSDM\_FLTxAWLTR registers

- enabled by AWDIE bit in DFSDM\_FLTxCR2 register (on selected channels AWDCH[3:0])

- indicated in AWDF bit in DFSDM FLTxISR register

- separate indication of high or low analog watchdog threshold error by AWHTF[3:0] and AWLTF[3:0] fields in DFSDM\_FLTxAWSR register

- cleared by writing '1' into corresponding CLRAWHTF[3:0] or CLRAWLTF[3:0] bits in DFSDM FLTxAWCFR register

- Short-circuit detector interrupt:

- occurred when the number of stable data crosses over thresholds in DFSDM\_CHyAWSCDR register

- enabled by SCDIE bit in DFSDM\_FLTxCR2 register (on channel selected by SCDEN bit in DFSDM\_CHyCFGR1 register)

- indicated in SCDF[3:0] bits in DFSDM\_FLTxISR register (which also reports the channel on which the short-circuit detector event occurred)

- cleared by writing '1' into the corresponding CLRSCDF[3:0] bit in DFSDM FLTxICR register

- Channel clock absence interrupt:

- occurred when there is clock absence on CKINy pin (see Clock absence detection in Section 21.4.4: Serial channel transceivers)

- enabled by CKABIE bit in DFSDM\_FLTxCR2 register (on channels selected by CKABEN bit in DFSDM\_CHyCFGR1 register)

- indicated in CKABF[y] bit in DFSDM\_FLTxISR register

- cleared by writing '1' into CLRCKABF[y] bit in DFSDM\_FLTxICR register

### Table 97. DFSDM interrupt requests

| Interrupt event            | Event flag | Event/Interrupt clearing method | Interrupt enable control bit |

|----------------------------|------------|---------------------------------|------------------------------|

| End of injected conversion | JEOCF      | reading DFSDM_FLTxJDATAR        | JEOCIE                       |

| End of regular conversion  | REOCF      | reading DFSDM_FLTxRDATAR        | REOCIE                       |

| Injected data overrun      | JOVRF      | writing CLRJOVRF = 1            | JOVRIE                       |

#### Bits 6:4 OC1M: Output Compare 1 mode

These bits define the behavior of the output reference signal OC1REF from which OC1 and OC1N are derived. OC1REF is active high whereas OC1 and OC1N active level depends on CC1P and CC1NP bits.

0000: Frozen - The comparison between the output compare register TIMx\_CCR1 and the counter TIMx\_CNT has no effect on the outputs.(this mode is used to generate a timing base).

0001: Set channel 1 to active level on match. OC1REF signal is forced high when the counter TIMx\_CNT matches the capture/compare register 1 (TIMx\_CCR1).

0010: Set channel 1 to inactive level on match. OC1REF signal is forced low when the counter TIMx\_CNT matches the capture/compare register 1 (TIMx\_CCR1).

0011: Toggle - OC1REF toggles when TIMx\_CNT=TIMx\_CCR1.

0100: Force inactive level - OC1REF is forced low.

0101: Force active level - OC1REF is forced high.

0110: PWM mode 1 - In upcounting, channel 1 is active as long as TIMx\_CNT<TIMx\_CCR1 else inactive. In downcounting, channel 1 is inactive (OC1REF='0') as long as

TIMx\_CNT>TIMx\_CCR1 else active (OC1REF='1').

0111: PWM mode 2 - In upcounting, channel 1 is inactive as long as

TIMx\_CNT<TIMx\_CCR1 else active. In downcounting, channel 1 is active as long as TIMx\_CNT>TIMx\_CCR1 else inactive.

1000: Retrigerrable OPM mode 1 - In up-counting mode, the channel is active until a trigger event is detected (on TRGI signal). Then, a comparison is performed as in PWM mode 1 and the channels becomes active again at the next update. In down-counting mode, the channel is inactive until a trigger event is detected (on TRGI signal). Then, a comparison is performed as in PWM mode 1 and the channels becomes inactive again at the next update. 1001: Retrigerrable OPM mode 2 - In up-counting mode, the channel is inactive until a trigger event is detected (on TRGI signal). Then, a comparison is performed as in PWM mode 2 and the channels becomes inactive again at the next update. In down-counting mode, the channel is active until a trigger event is detected (on TRGI signal). Then, a comparison is performed as in PWM mode 1 and the channels becomes active again at the next update.

1010: Reserved.

1011: Reserved.

1100: Combined PWM mode 1 - OC1REF has the same behavior as in PWM mode 1. OC1REFC is the logical OR between OC1REF and OC2REF.

1101: Combined PWM mode 2 - OC1REF has the same behavior as in PWM mode 2. OC1REFC is the logical AND between OC1REF and OC2REF.

1110: Asymmetric PWM mode 1 - OC1REF has the same behavior as in PWM mode 1. OC1REFC outputs OC1REF when the counter is counting up, OC2REF when it is counting down.

1111: Asymmetric PWM mode 2 - OC1REF has the same behavior as in PWM mode 2. OC1REFC outputs OC1REF when the counter is counting up, OC2REF when it is counting down.

Note: These bits can not be modified as long as LOCK level 3 has been programmed (LOCK bits in TIMx\_BDTR register) and CC1S='00' (the channel is configured in output).

Note: In PWM mode, the OCREF level changes only when the result of the comparison changes or when the output compare mode switches from "frozen" mode to "PWM" mode.

Note: On channels having a complementary output, this bit field is preloaded. If the CCPC bit is set in the TIMx\_CR2 register then the OC1M active bits take the new value from the preloaded bits only when a COM event is generated.

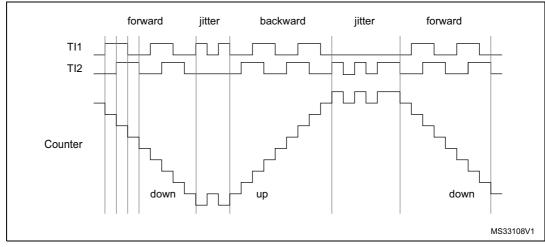

Figure 251. Example of encoder interface mode with TI1FP1 polarity inverted

The timer, when configured in Encoder Interface mode provides information on the sensor's current position. You can obtain dynamic information (speed, acceleration, deceleration) by measuring the period between two encoder events using a second timer configured in capture mode. The output of the encoder which indicates the mechanical zero can be used for this purpose. Depending on the time between two events, the counter can also be read at regular times. You can do this by latching the counter value into a third input capture register if available (then the capture signal must be periodic and can be generated by another timer). when available, it is also possible to read its value through a DMA request generated by a Real-Time clock.

## 27.3.16 UIF bit remapping

The IUFREMAP bit in the TIMx\_CR1 register forces a continuous copy of the update interrupt flag (UIF) into bit 31 of the timer counter register's bit 31 (TIMxCNT[31]). This allows to atomically read both the counter value and a potential roll-over condition signaled by the UIFCPY flag. It eases the calculation of angular speed by avoiding race conditions caused, for instance, by a processing shared between a background task (counter reading) and an interrupt (update interrupt).

There is no latency between the UIF and UIFCPY flag assertions.

In 32-bit timer implementations, when the IUFREMAP bit is set, bit 31 of the counter is overwritten by the UIFCPY flag upon read access (the counter's most significant bit is only accessible in write mode).

### 27.3.17 Timer input XOR function

The TI1S bit in the TIM1xx\_CR2 register, allows the input filter of channel 1 to be connected to the output of a XOR gate, combining the three input pins TIMx CH1 to TIMx CH3.

The XOR output can be used with all the timer input functions such as trigger or input capture.

An example of this feature used to interface Hall sensors is given in *Section 26.3.25*: *Interfacing with Hall sensors on page 719*.

#### Bits 15:13 TRIGSEL: Trigger selector

The TRIGSEL bits select the trigger source that will serve as a trigger event for the LPTIM among the below 8 available sources:

```

000: ext_trig0

001: ext_trig1

010: ext_trig2

011: ext_trig3

100: ext_trig4

101: ext_trig5

110: ext_trig6

111: ext_trig7

```

Bit 12 Reserved, must be kept at reset value.

#### Bits 11:9 PRESC: Clock prescaler

The PRESC bits configure the prescaler division factor. It can be one among the following division factors:

000: /1

001: /2

010: /4

011: /8

100: /16

101: /32

110: /64

111: /128

Bit 8 Reserved, must be kept at reset value.

#### Bits 7:6 TRGFLT: Configurable digital filter for trigger

The TRGFLT value sets the number of consecutive equal samples that should be detected when a level change occurs on an internal trigger before it is considered as a valid level transition. An internal clock source must be present to use this feature

- 00: any trigger active level change is considered as a valid trigger

- 01: trigger active level change must be stable for at least 2 clock periods before it is considered as valid trigger.

- 10: trigger active level change must be stable for at least 4 clock periods before it is considered as valid trigger.

- 11: trigger active level change must be stable for at least 8 clock periods before it is considered as valid trigger.

- Bit 5 Reserved, must be kept at reset value.

Real-time clock (RTC) RM0394

### 34.6.18 RTC alarm B sub second register (RTC\_ALRMBSSR)

This register can be written only when ALRBE is reset in RTC\_CR register, or in initialization mode.

This register is write protected. The write access procedure is described in *Section : RTC register write protection*.

Address offset: 0x48

Backup domain reset value: 0x0000 0000

System reset: not affected

| 31   | 30   | 29   | 28   | 27 | 26   | 25      | 24 | 23       | 22   | 21   | 20   | 19   | 18   | 17   | 16   |

|------|------|------|------|----|------|---------|----|----------|------|------|------|------|------|------|------|

| Res. | Res. | Res. | Res. |    | MASK | SS[3:0] |    | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

|      |      |      |      | rw | rw   | rw      | rw |          |      |      |      |      |      |      |      |

| 15   | 14   | 13   | 12   | 11 | 10   | 9       | 8  | 7        | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| Res. |      |      |      |    |      |         |    | SS[14:0] |      |      |      |      |      |      |      |

|      | rw   | rw   | rw   | rw | rw   | rw      | rw | rw       | rw   | rw   | rw   | rw   | w    | rw   | rw   |

Bits 31:28 Reserved, must be kept at reset value.

Bits 27:24 MASKSS[3:0]: Mask the most-significant bits starting at this bit

0x0: No comparison on sub seconds for Alarm B. The alarm is set when the seconds unit is incremented (assuming that the rest of the fields match).

0x1: SS[14:1] are don't care in Alarm B comparison. Only SS[0] is compared.

0x2: SS[14:2] are don't care in Alarm B comparison. Only SS[1:0] are compared.

0x3: SS[14:3] are don't care in Alarm B comparison. Only SS[2:0] are compared.

•••

0xC: SS[14:12] are don't care in Alarm B comparison. SS[11:0] are compared.

0xD: SS[14:13] are don't care in Alarm B comparison. SS[12:0] are compared.

0xE: SS[14] is don't care in Alarm B comparison. SS[13:0] are compared.

0xF: All 15 SS bits are compared and must match to activate alarm.

The overflow bits of the synchronous counter (bits 15) is never compared. This bit can be different from 0 only after a shift operation.

Bits 23:15 Reserved, must be kept at reset value.

Bits 14:0 SS[14:0]: Sub seconds value

This value is compared with the contents of the synchronous prescaler counter to determine if Alarm B is to be activated. Only bits 0 up to MASKSS-1 are compared.

with a standard (up to 100 kHz), Fast-mode (up to 400 kHz) or Fast-mode Plus (up to 1 MHz)  $I^2C$  bus.

This interface can also be connected to a SMBus with the data pin (SDA) and clock pin (SCL).

If SMBus feature is supported: the additional optional SMBus Alert pin (SMBA) is also available.

The I2C detects its own SCL high level after a  $t_{SYNC2}$  delay depending on the SCL rising edge, SCL input noise filters (analog + digital) and SCL synchronization to I2CxCLK clock. The I2C ties SCL to low level once the SCLH counter is reached reaches the value programmed in the SCLH[7:0] bits in the I2C\_TIMINGR register.

Consequently the master clock period is:

$t_{SCL} = t_{SYNC1} + t_{SYNC2} + \{[(SCLH+1) + (SCLL+1)] \times (PRESC+1) \times t_{I2CCLK}\}$

The duration of t<sub>SYNC1</sub> depends on these parameters:

- SCL falling slope

- When enabled, input delay induced by the analog filter.

- When enabled, input delay induced by the digital filter: DNF x t<sub>l2CCLK</sub>

- Delay due to SCL synchronization with I2CCLK clock (2 to 3 I2CCLK periods)

The duration of t<sub>SYNC2</sub> depends on these parameters:

- SCL rising slope

- When enabled, input delay induced by the analog filter.

- When enabled, input delay induced by the digital filter: DNF x t<sub>I2CCLK</sub>

- Delay due to SCL synchronization with I2CCLK clock (2 to 3 I2CCLK periods)

• If the master addresses a 10-bit address slave, transmits data to this slave and then reads data from the same slave, a master transmission flow must be done first. Then a repeated start is set with the 10 bit slave address configured with HEAD10R=1. In this case the master sends this sequence: ReStart + Slave address 10-bit header Read.

11110XX Slave address Slave address R/W A/A DATA Α DATA 1st 7 bits 2nd byte 11110XX Slave address R/W DATA DATA 1st 7 bits Read MS19823V1

Figure 332. 10-bit address read access with HEAD10R=1

#### Master transmitter

In the case of a write transfer, the TXIS flag is set after each byte transmission, after the 9th SCL pulse when an ACK is received.

A TXIS event generates an interrupt if the TXIE bit is set in the I2C\_CR1 register. The flag is cleared when the I2C\_TXDR register is written with the next data byte to be transmitted.

The number of TXIS events during the transfer corresponds to the value programmed in NBYTES[7:0]. If the total number of data bytes to be sent is greater than 255, reload mode must be selected by setting the RELOAD bit in the I2C\_CR2 register. In this case, when NBYTES data have been transferred, the TCR flag is set and the SCL line is stretched low until NBYTES[7:0] is written to a non-zero value.

The TXIS flag is not set when a NACK is received.

- When RELOAD=0 and NBYTES data have been transferred:

- In automatic end mode (AUTOEND=1), a STOP is automatically sent.

- In software end mode (AUTOEND=0), the TC flag is set and the SCL line is stretched low in order to perform software actions:

A RESTART condition can be requested by setting the START bit in the I2C\_CR2 register with the proper slave address configuration, and number of bytes to be transferred. Setting the START bit clears the TC flag and the START condition is sent on the bus.

A STOP condition can be requested by setting the STOP bit in the I2C\_CR2 register. Setting the STOP bit clears the TC flag and the STOP condition is sent on the bus.

If a NACK is received: the TXIS flag is not set, and a STOP condition is automatically sent after the NACK reception. the NACKF flag is set in the I2C\_ISR register, and an interrupt is generated if the NACKIE bit is set.

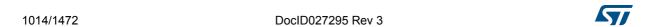

The USART exits from mute mode when an address character is received which matches the programmed address. Then the RWU bit is cleared and subsequent bytes are received normally. The RXNE bit is set for the address character since the RWU bit has been cleared.

An example of mute mode behavior using address mark detection is given in *Figure 355*.

Figure 355. Mute mode using address mark detection

### 36.5.8 Modbus communication using USART

The USART offers basic support for the implementation of Modbus/RTU and Modbus/ASCII protocols. Modbus/RTU is a half duplex, block transfer protocol. The control part of the protocol (address recognition, block integrity control and command interpretation) must be implemented in software.

The USART offers basic support for the end of the block detection, without software overhead or other resources.

#### Modbus/RTU

In this mode, the end of one block is recognized by a "silence" (idle line) for more than 2 character times. This function is implemented through the programmable timeout function.

The timeout function and interrupt must be activated, through the RTOEN bit in the USART\_CR2 register and the RTOIE in the USART\_CR1 register. The value corresponding to a timeout of 2 character times (for example 22 x bit duration) must be programmed in the RTO register. when the receive line is idle for this duration, after the last stop bit is received, an interrupt is generated, informing the software that the current block reception is completed.

### Modbus/ASCII

In this mode, the end of a block is recognized by a specific (CR/LF) character sequence. The USART manages this mechanism using the character match function.

By programming the LF ASCII code in the ADD[7:0] field and by activating the character match interrupt (CMIE=1), the software is informed when a LF has been received and can check the CR/LF in the DMA buffer.

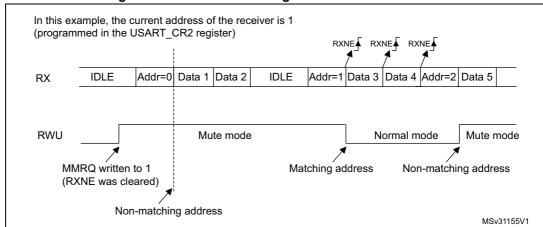

Figure 362. ISO 7816-3 asynchronous protocol

When connected to a smartcard, the TX output of the USART drives a bidirectional line that is also driven by the smartcard. The TX pin must be configured as open drain.

Smartcard mode implements a single wire half duplex communication protocol.

- Transmission of data from the transmit shift register is guaranteed to be delayed by a minimum of 1/2 baud clock. In normal operation a full transmit shift register starts shifting on the next baud clock edge. In Smartcard mode this transmission is further delayed by a guaranteed 1/2 baud clock.

- In transmission, if the smartcard detects a parity error, it signals this condition to the USART by driving the line low (NACK). This NACK signal (pulling transmit line low for 1 baud clock) causes a framing error on the transmitter side (configured with 1.5 stop bits). The USART can handle automatic re-sending of data according to the protocol. The number of retries is programmed in the SCARCNT bit field. If the USART continues receiving the NACK after the programmed number of retries, it stops transmitting and signals the error as a framing error. The TXE bit can be set using the TXFRQ bit in the USART RQR register.

- Smartcard auto-retry in transmission: a delay of 2.5 baud periods is inserted between

the NACK detection by the USART and the start bit of the repeated character. The TC

bit is set immediately at the end of reception of the last repeated character (no guardtime). If the software wants to repeat it again, it must insure the minimum 2 baud

periods required by the standard.

- If a parity error is detected during reception of a frame programmed with a 1.5 stop bits period, the transmit line is pulled low for a baud clock period after the completion of the receive frame. This is to indicate to the smartcard that the data transmitted to the USART has not been correctly received. A parity error is NACKed by the receiver if the NACK control bit is set, otherwise a NACK is not transmitted (to be used in T=1 mode). If the received character is erroneous, the RXNE/receive DMA request is not activated. According to the protocol specification, the smartcard must resend the same character. If the received character is still erroneous after the maximum number of retries specified in the SCARCNT bit field, the USART stops transmitting the NACK and signals the error as a parity error.

- Smartcard auto-retry in reception: the BUSY flag remains set if the USART NACKs the card but the card doesn't repeat the character.

Note: In order to provide correctly the CK clock to the Smartcard, the steps below must be respected:

- -UE = 0

- SCEN = 1

- GTPR configuration

- CLKEN= 1

- -UE = 1

#### Bit 10 CPOL: Clock polarity

This bit allows the user to select the polarity of the clock output on the CK pin in synchronous mode. It works in conjunction with the CPHA bit to produce the desired clock/data relationship

- 0: Steady low value on CK pin outside transmission window

- 1: Steady high value on CK pin outside transmission window

This bit can only be written when the USART is disabled (UE=0).

Note: If synchronous mode is not supported, this bit is reserved and forced by hardware to '0'. Please refer to Section 36.4: USART implementation on page 1085.

#### Bit 9 CPHA: Clock phase

This bit is used to select the phase of the clock output on the CK pin in synchronous mode. It works in conjunction with the CPOL bit to produce the desired clock/data relationship (see *Figure 359* and *Figure 360*)

- 0: The first clock transition is the first data capture edge

- 1: The second clock transition is the first data capture edge

This bit can only be written when the USART is disabled (UE=0).

Note: If synchronous mode is not supported, this bit is reserved and forced by hardware to '0'. Please refer to Section 36.4: USART implementation on page 1085.

#### Bit 8 LBCL: Last bit clock pulse

This bit is used to select whether the clock pulse associated with the last data bit transmitted (MSB) has to be output on the CK pin in synchronous mode.

- 0: The clock pulse of the last data bit is not output to the CK pin

- 1: The clock pulse of the last data bit is output to the CK pin

**Caution:** The last bit is the 7th or 8th or 9th data bit transmitted depending on the 7 or 8 or 9 bit format selected by the M bits in the USART\_CR1 register.

This bit can only be written when the USART is disabled (UE=0).

Note: If synchronous mode is not supported, this bit is reserved and forced by hardware to '0'.

Please refer to Section 36.4: USART implementation on page 1085.

- Bit 7 Reserved, must be kept at reset value.

- Bit 6 LBDIE: LIN break detection interrupt enable

Break interrupt mask (break detection using break delimiter).

- 0: Interrupt is inhibited

- 1: An interrupt is generated whenever LBDF=1 in the USART\_ISR register

Note: If LIN mode is not supported, this bit is reserved and forced by hardware to '0'. Please refer to Section 36.4: USART implementation on page 1085.

### **Anticipated frame synchronization detection (AFSDET)**

The AFSDET flag is used only in slave mode. It is never asserted in master mode. It indicates that a frame synchronization (FS) has been detected earlier than expected since the frame length, the frame polarity, the frame offset are defined and known.

Anticipated frame detection sets the AFSDET flag in the SAI\_xSR register.

This detection has no effect on the current audio frame which is not sensitive to the anticipated FS. This means that "parasitic" events on signal FS are flagged without any perturbation of the current audio frame.

An interrupt is generated if the AFSDETIE bit is set in the SAI\_xIM register. To clear the AFSDET flag, CAFSDET bit must be set in the SAI\_xCLRFR register.

To resynchronize with the master after an anticipated frame detection error, four steps are required:

- 1. Disable the SAI block by resetting SAIXEN bit in SAI\_xCR1 register. To make sure the SAI is disabled, read back the SAIXEN bit and check it is set to 0.

- Flush the FIFO via FFLUS bit in SAI xCR2 register.

- 3. Enable again the SAI peripheral (SAIXEN bit set to 1).

- The SAI block will wait for the assertion on FS to restart the synchronization with master.

Note:

The SAIXEN flag is not asserted in AC'97 mode since the SAI audio block acts as a link controller and generates the FS signal even when declared as slave. It has no meaning in SPDIF mode since the FS signal is not used.

### Late frame synchronization detection

The LFSDET flag in the SAI\_xSR register can be set only when the SAI audio block operates as a slave. The frame length, the frame polarity and the frame offset configuration are known in register SAI\_xFRCR.

If the external master does not send the FS signal at the expecting time thus generating the signal too late, the LFSDET flag is set and an interrupt is generated if LFSDETIE bit is set in the SAI\_xIM register.

The LFSDET flag is cleared when CLFSDET bit is set in the SAI xCLRFR register.

The late frame synchronization detection flag is set when the corresponding error is detected. The SAI needs to be resynchronized with the master (see sequence described in *Section : Anticipated frame synchronization detection (AFSDET)*).

In a noisy environment, glitches on the SCK clock may be wrongly detected by the audio block state machine and shift the SAI data at a wrong frame position. This event can be detected by the SAI and reported as a late frame synchronization detection error.

There is no corruption if the external master is not managing the audio data frame transfer in continuous mode, which should not be the case in most applications. In this case, the LFSDET flag will be set.

Note:

The LFSDET flag is not asserted in AC'97 mode since the SAI audio block acts as a link controller and generates the FS signal even when declared as slave. It has no meaning in SPDIF mode since the signal FS is not used by the protocol.

57

# 40.6.7 SWPMI Transmit data register (SWPMI\_TDR)

Address offset: 0x1C

Reset value: 0x0000 0000

| 31 | 30       | 29 | 28 | 27 | 26 | 25 | 24 | 23      | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----------|----|----|----|----|----|----|---------|----|----|----|----|----|----|----|

|    |          |    |    |    |    |    | TD | [31:16] |    |    |    |    |    |    |    |

| w  | W        | W  | W  | W  | W  | W  | W  | W       | W  | W  | W  | W  | W  | W  | w  |

| 15 | 14       | 13 | 12 | 11 | 10 | 9  | 8  | 7       | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    | TD[15:0] |    |    |    |    |    |    |         |    |    |    |    |    |    |    |

| w  | w        | W  | W  | W  | W  | w  | w  | w       | w  | w  | w  | w  | w  | w  | w  |

Bits 31:0 TD[31:0]: Transmit data

Contains the data to be transmitted.

Writing to this register triggers the SOF transmission or the next payload data transmission, and clears the TXE flag.

# 40.6.8 SWPMI Receive data register (SWPMI\_RDR)

Address offset: 0x20

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23      | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|----|---------|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    | RD | [31:16] |    |    |    |    |    |    |    |

| r  | r  | r  | r  | r  | r  | r  | r  | r       | r  | r  | r  | r  | r  | r  | r  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7       | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    |    |    |    |    |    |    | RD | [15:0]  |    |    |    |    |    |    |    |

| r  | r  | r  | r  | r  | r  | r  | r  | r       | r  | r  | r  | r  | r  | r  | r  |

Bits 31:0 RD[31:0]: received data

Contains the received data

Reading this register is clearing the RXNE flag.

# 40.6.9 SWPMI Option register (SWPMI\_OR)

Address offset: 0x24

Reset value: 0x0000 0000

| 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20   | 19   | 18   | 17            | 16           |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|---------------|--------------|

| Res.          | Res.         |

|      |      |      |      |      |      |      |      |      |      |      |      |      |      |               |              |

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1             | 0            |

|      |      |      |      |      |      |      |      |      |      |      |      |      |      | SWP_<br>CLASS | SWP_<br>TBYP |

|      |      |      |      |      |      |      |      |      |      |      |      |      |      | rw            | rw           |