Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                 |

|----------------------------|----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                     |

| Speed                      | 80MHz                                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                             |

| Number of I/O              | 52                                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 64K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                  |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 64-LQFP                                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l433rct6tr                |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.3 Firewall functional description

# 4.3.1 Firewall AMBA bus snoop

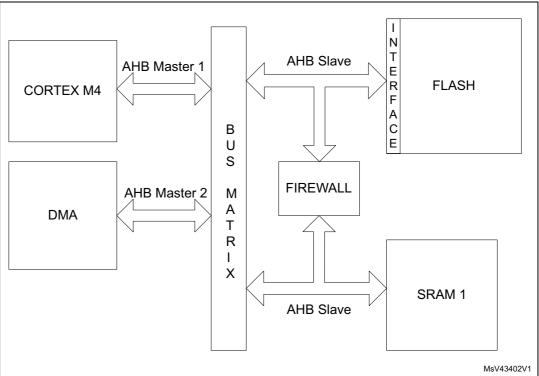

The Firewall peripheral is snooping the AMBA buses on which the memories (volatile and non-volatile) are connected. A global architecture view is illustrated in *Figure 5*.

# 4.3.2 Functional requirements

There are several requirements to guaranty the highest security level by the application code/data which needs to be protected by the Firewall and to avoid unwanted Firewall alarm (reset generation).

### **Debug consideration**

In debug mode, if the Firewall is opened, the accesses by the debugger to the protected segments are not blocked. For this reason, the Read out level 2 protection must be active in conjunction with the Firewall implementation.

If the debug is needed, it is possible to proceed in the following way:

- A dummy code having the same API as the protected code may be developed during the development phase of the final user code. This dummy code may send back coherent answers (in terms of function and potentially timing if needed), as the protected code should do in production phase.

- In the development phase, the protected code can be given to the customer-end under NDA agreement and its software can be developed in level 0 protection. The customer-

# 4.4.7 Configuration register (FW\_CR)

Address offset: 0x20

Reset value: 0x0000 0000

| 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Res. |

|      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| Res. | VDE  | VDS  | FPA  |

|      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

#### Bits 31:3 Reserved, must be kept at the reset value.

#### Bit 2 VDE: Volatile data execution

0: Volatile data segment cannot be executed if VDS = 0

1: Volatile data segment is declared executable whatever VDS bit value

When VDS = 1, this bit has no meaning. The Volatile data segment can be executed whatever the VDE bit value.

If VDS = 1, the code can be executed whatever the Firewall state (opened or closed) If VDS = 0, the code can only be executed if the Firewall is opened or applying the "call gate" entry sequence if the Firewall is closed.

Refer to Segment access depending on the Firewall state.

#### Bit 1 VDS: Volatile data shared

0: Volatile data segment is not shared and cannot be hit by a non protected executable code when the Firewall is closed. If it is accessed in such a condition, a system reset will be generated by the Firewall.

1: Volatile data segment is shared with non protected application code. It can be accessed whatever the Firewall state (opened or closed).

Refer to Segment access depending on the Firewall state.

Bit 0 **FPA**: Firewall prearm

0: any code executed outside the protected segment when the Firewall is opened will generate a system reset.

1: any code executed outside the protected segment will close the Firewall. Refer to *Closing the Firewall*.

This register is protected in the same way as the Non-volatile data segment (refer to *Section 4.3.5: Firewall initialization*).

|        |                    | Destination |      |      |      |       |       |        |        |      |        |      |      |       |       |       |

|--------|--------------------|-------------|------|------|------|-------|-------|--------|--------|------|--------|------|------|-------|-------|-------|

|        | -<br>MCO           |             | TIM2 | TIM6 | TIM7 | TIM15 | TIM16 | LPTIM1 | LPTIM2 | ADC1 | OPAMP1 | DAC1 | DAC2 | COMP1 | COMP2 | IRTIM |

|        | MCO                | -           | -    | -    | -    | -     | 5     | -      | -      | -    | -      | -    | -    | -     | -     | -     |

|        | EXTI               | -           | -    | -    | -    | -     | -     | -      | -      | 2    | -      | 4    | 4    | -     | -     | -     |

| Ice    | RTC                | -           | -    | -    | -    | -     | 5     | 6      | 6      | -    | -      | -    | -    | -     | -     | -     |

| Source | COMP1              | 10          | 10   | -    | -    | 10    | 10    | 6      | 6      | -    | -      | -    | -    | -     | -     | -     |

|        | COMP2              | 10          | 10   | -    | -    | 10    | 10    | 6      | 6      | -    | -      | -    | -    | -     | -     | -     |

|        | SYST ERR           | 11          | -    | -    | -    | 11    | 11    | -      | -      | -    | -      | -    | -    | -     | -     | -     |

|        | USB <sup>(3)</sup> | -           | 8    | -    | -    | -     | -     | -      | -      | -    | -      | -    | -    | -     | -     | -     |

#### Table 38. STM32L43xxx/44xxx/45xxx/46xxx peripherals interconnect matrix<sup>(1) (2)</sup> (continued)

1. Numbers in table are links to corresponding detailed sub-section in Section 10.3: Interconnection details.

2. The "-" symbol in grayed cells means no interconnect.

3. Not available for STM32L431xx devices.

# **10.3** Interconnection details

# 10.3.1 From timer (TIM1/TIM2/TIM15/TIM16) to timer (TIM1/TIM2/TIM15/TIM16)

#### Purpose

Some of the TIMx timers are linked together internally for timer synchronization or chaining.

When one timer is configured in Master Mode, it can reset, start, stop or clock the counter of another timer configured in Slave Mode.

A description of the feature is provided in: Section 27.3.19: Timer synchronization.

The modes of synchronization are detailed in:

- Section 26.3.26: Timer synchronization for advanced-control timers (TIM1)

- Section 27.3.18: Timers and external trigger synchronization for general-purpose timers (TIM2)

- Section 28.4.17: External trigger synchronization (TIM15 only) for general-purpose timer (TIM15)

### **Triggering signals**

The output (from Master) is on signal TIMx\_TRGO (and TIMx\_TRGO2 for TIM1) following a configurable timer event.

The input (to slave) is on signals TIMx\_ITR0/ITR1/ITR2/ITR3

The input and output signals for TIM1 are shown in *Figure 153: Advanced-control timer block diagram*.

Inside the regular sequence, after each conversion is complete:

- The converted data are stored into the 16-bit ADC\_DR register

- The EOC (end of regular conversion) flag is set

- An interrupt is generated if the EOCIE bit is set

Inside the injected sequence, after each conversion is complete:

- The converted data are stored into one of the four 16-bit ADC\_JDRy registers

- The JEOC (end of injected conversion) flag is set

- An interrupt is generated if the JEOCIE bit is set

After the regular sequence is complete:

- The EOS (end of regular sequence) flag is set

- An interrupt is generated if the EOSIE bit is set

After the injected sequence is complete:

- The JEOS (end of injected sequence) flag is set

- An interrupt is generated if the JEOSIE bit is set

Then the ADC stops until a new external regular or injected trigger occurs or until bit ADSTART or JADSTART is set again.

Note: To convert a single channel, program a sequence with a length of 1.

# 16.4.14 Continuous conversion mode (CONT=1)

This mode applies to regular channels only.

In continuous conversion mode, when a software or hardware regular trigger event occurs, the ADC performs once all the regular conversions of the channels and then automatically re-starts and continuously converts each conversions of the sequence. This mode is started with the CONT bit at 1 either by external trigger or by setting the ADSTART bit in the ADC\_CR register.

Inside the regular sequence, after each conversion is complete:

- The converted data are stored into the 16-bit ADC\_DR register

- The EOC (end of conversion) flag is set

• An interrupt is generated if the EOCIE bit is set

After the sequence of conversions is complete:

- The EOS (end of sequence) flag is set

- An interrupt is generated if the EOSIE bit is set

Then, a new sequence restarts immediately and the ADC continuously repeats the conversion sequence.

Note: To convert a single channel, program a sequence with a length of 1.

It is not possible to have both discontinuous mode and continuous mode enabled: it is forbidden to set both DISCEN=1 and CONT=1.

Injected channels cannot be converted continuously. The only exception is when an injected channel is configured to be converted automatically after regular channels in continuous mode (using JAUTO bit), refer to Auto-injection mode section).

### 16.6.4 ADC configuration register (ADC\_CFGR)

Address offset: 0x0C

Reset value: 0x8000 0000

| 31    | 30         | 29   | 28         | 27   | 26     | 25    | 24          | 23         | 22          | 21    | 20          | 19    | 18           | 17         | 16         |

|-------|------------|------|------------|------|--------|-------|-------------|------------|-------------|-------|-------------|-------|--------------|------------|------------|

| JQDIS |            | AV   | VD1CH[4    | :0]  |        | JAUTO | JAWD1<br>EN | AWD1<br>EN | AWD1S<br>GL | JQM   | JDISC<br>EN | DI    | SCNUM[2      | ::0]       | DISC<br>EN |

| rw    | rw         | rw   | rw         | rw   | rw     | rw    | rw          | rw         | rw          | rw    | rw          | rw    | rw           | rw         | rw         |

| 15    | 14         | 13   | 12         | 11   | 10     | 9     | 8           | 7          | 6           | 5     | 4           | 3     | 2            | 1          | 0          |

| Res.  | AUT<br>DLY | CONT | OVR<br>MOD | EXTE | N[1:0] |       | EXTS        | EL[3:0]    |             | ALIGN | RES         | [1:0] | DFSD<br>MCFG | DMA<br>CFG | DMA<br>EN  |

|       | rw         | rw   | rw         | rw   | rw     | rw    | rw          | rw         | rw          | rw    | rw          | rw    | rw           | rw         | rw         |

#### Bit 31 JQDIS: Injected Queue disable

These bits are set and cleared by software to disable the Injected Queue mechanism :

- 0: Injected Queue enabled

- 1: Injected Queue disabled

- Note: Software is allowed to write this bit only when ADSTART=0 and JADSTART=0 (which ensures that no regular nor injected conversion is ongoing).

- A set or reset of JQDIS bit causes the injected queue to be flushed and the JSQR register is cleared.

#### Bits 30:26 AWD1CH[4:0]: Analog watchdog 1 channel selection

These bits are set and cleared by software. They select the input channel to be guarded by the analog watchdog.

00000: ADC analog input channel-0 monitored by AWD1 (available on ADC1 only)

00001: ADC analog input channel-1 monitored by AWD1

.....

10010: ADC analog input channel-18 monitored by AWD1

- others: reserved, must not be used

- Note: The channel selected by AWD1CH must be also selected into the SQRi or JSQRi registers. Software is allowed to write these bits only when ADSTART=0 and JADSTART=0 (which ensures that no conversion is ongoing).

- Bit 25 JAUTO: Automatic injected group conversion

This bit is set and cleared by software to enable/disable automatic injected group conversion after regular group conversion.

- 0: Automatic injected group conversion disabled

- 1: Automatic injected group conversion enabled

- Note: Software is allowed to write this bit only when ADSTART=0 and JADSTART=0 (which ensures that no regular nor injected conversion is ongoing).

- Bit 24 JAWD1EN: Analog watchdog 1 enable on injected channels

- This bit is set and cleared by software

- 0: Analog watchdog 1 disabled on injected channels

- 1: Analog watchdog 1 enabled on injected channels

- Note: Software is allowed to write this bit only when JADSTART=0 (which ensures that no injected conversion is ongoing).

- Bit 8 **AWD2\_MST:** Analog watchdog 2 flag of the master ADC This bit is a copy of the AWD2 bit in the corresponding ADC\_ISR register.

- Bit 7 **AWD1\_MST:** Analog watchdog 1 flag of the master ADC This bit is a copy of the AWD1 bit in the corresponding ADC\_ISR register.

- Bit 6 **JEOS\_MST:** End of injected sequence flag of the master ADC This bit is a copy of the JEOS bit in the corresponding ADC\_ISR register.

- Bit 5 **JEOC\_MST:** End of injected conversion flag of the master ADC This bit is a copy of the JEOC bit in the corresponding ADC\_ISR register.

- Bit 4 **OVR\_MST:** Overrun flag of the master ADC This bit is a copy of the OVR bit in the corresponding ADC\_ISR register.

- Bit 3 **EOS\_MST:** End of regular sequence flag of the master ADC This bit is a copy of the EOS bit in the corresponding ADC\_ISR register.

- Bit 2 **EOC\_MST:** End of regular conversion of the master ADC This bit is a copy of the EOC bit in the corresponding ADC\_ISR register.

- Bit 1 **EOSMP\_MST:** End of Sampling phase flag of the master ADC This bit is a copy of the EOSMP bit in the corresponding ADC\_ISR register.

- Bit 0 **ADRDY\_MST:** Master ADC ready This bit is a copy of the ADRDY bit in the corresponding ADC\_ISR register.

### 16.7.2 ADC common control register (ADC\_CCR)

Address offset: 0x08 (this offset address is relative to the master ADC base address + 0x300)

Reset value: 0x0000 0000

| 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24          | 23          | 22         | 21    | 20   | 19      | 18   | 17   | 16       |

|------|------|------|------|------|------|------|-------------|-------------|------------|-------|------|---------|------|------|----------|

| Res. | CH18<br>SEL | CH17<br>SEL | VREF<br>EN |       | PRES | SC[3:0] |      | СКМС | DDE[1:0] |

|      |      |      |      |      |      |      | rw          |             |            | rw rw |      | rw      | rw   | rw   | rw       |

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8           | 7           | 6          | 5     | 4    | 3       | 2    | 1    | 0        |

| Res.        | Res.        | Res.       | Res.  | Res. | Res.    | Res. | Res. | Res.     |

|      |      |      |      |      |      |      |             |             |            |       |      |         |      |      |          |

Bits 31:25 Reserved, must be kept at reset value.

#### Bit 24 CH18SEL: CH18 selection

This bit is set and cleared by software to control the channel 18 of ADC1

0: V<sub>BAT</sub> channel disabled, DAC2\_int selected.

1: V<sub>BAT</sub> channel enabled

#### Bit 23 CH17SEL: CH17 selection

This bit is set and cleared by software to control the channel 17 of ADC1

0: Temperature sensor channel disabled, DAC1\_int selected

1: Temperature sensor channel enabled

AWHTF[3:0], AWLTF[3:0] of DFSDM\_FLTxAWSR register). Each channel request is executed in 8 DFSDM clock cycles. So, the bandwidth from each channel is limited to 8 DFSDM clock cycles (if AWDCH[3:0] = 0x0F). Because the maximum input channel sampling clock frequency is the DFSDM clock frequency divided by 4, the configuration AWFOSR = 0 (analog watchdog filter is bypassed) cannot be used for analog watchdog feature at this input clock speed. Therefore user must properly configure the number of watched channels and analog watchdog filter parameters with respect to input sampling clock speed and DFSDM frequency.

Analog watchdog filter data for given channel y is available for reading by firmware on field WDATA[15:0] in DFSDM\_CHyWDATR register. That analog watchdog filter data is converted continuously (if CHEN=1 in DFSDM\_CHyCFGR1 register) with the data rate given by the analog watchdog filter setting and the channel input clock frequency.

The analog watchdog filter conversion works like a regular Fast Continuous Conversion without the intergator. The number of serial samples needed for one result from analog watchdog filter output (at channel input clock frequency  $f_{CKIN}$ ):

first conversion:

for Sinc<sup>x</sup> filters (x=1..5): number of samples =  $[F_{OSR} * F_{ORD} + F_{ORD} + 1]$ for FastSinc filter: number of samples =  $[F_{OSR} * 4 + 2 + 1]$

next conversions:

for Sinc<sup>x</sup> and FastSinc filters: number of samples = [FOSR \* IOSR]

where:

$F_{OSR}$  ...... filter oversampling ratio:  $F_{OSR}$  = AWFOSR[4:0]+1 (see DFSDM\_CHyAWSCDR register)

F<sub>ORD</sub> ...... the filter order: F<sub>ORD</sub> = AWFORD[1:0] (see DFSDM\_CHyAWSCDR register)

In case of output data register monitoring (AWFSEL=0), the comparison is done after a right bit shift and an offset correction of final data (see OFFSET[23:0] and DTRBS[4:0] fields in DFSDM\_CHyCFGR2 register). A comparison is performed after each injected or regular end of conversion for the channels selected by AWDCH[3:0] field (in DFSDM\_FLTxCR2 register).

The status of an analog watchdog event is signalized in DFSDM\_FLTxAWSR register where a given event is latched. AWHTF[y]=1 flag signalizes crossing AWHT[23:0] value on channel y. AWLTF[y]=1 flag signalizes crossing AWLT[23:0] value on channel y. Latched events in DFSDM\_FLTxAWSR register are cleared by writing '1' into the corresponding clearing bit CLRAWHTF[y] or CLRAWLTF[y] in DFSDM\_FLTxAWCFR register.

The global status of an analog watchdog is signalized by the AWDF flag bit in DFSDM\_FLTxISR register (it is used for the fast detection of an interrupt source). AWDF=1 signalizes that at least one watchdog occurred (AWHTF[y]=1 or AWLTF[y]=1 for at least one channel). AWDF bit is cleared when all AWHTF[3:0] and AWLTF[3:0] are cleared.

An analog watchdog event can be assigned to break output signal. There are four break outputs to be assigned to a high or low threshold crossing event (dfsdm\_break[3:0]). The break signal assignment to a given analog watchdog event is done by BKAWH[3:0] and BKAWL[3:0] fields in DFSDM\_FLTxAWHTR and DFSDM\_FLTxAWLTR register.

#### RM0394

### Summary of COM and SEG functions versus duty and remap

All the possible ways of multiplexing the COM and SEG functions are described in *Table 101. Figure 127* gives examples showing the signal connections to the external pins.

| Configu | ration bits | SEG x COM | Quitaut ain                    | Function   |

|---------|-------------|-----------|--------------------------------|------------|

| DUTY    | MUX_SEG     | SEG X COM | Output pin                     | Function   |

|         |             |           | SEG[43:40]/SEG[31:28]/COM[7:4] | COM[7:4]   |

|         | 0/1         | 40x8      | COM[3:0]                       | COM[3:0]   |

| 1/8     |             |           | SEG[39:0]                      | SEG[39:0]  |

| 170     |             |           | SEG[43:40]/SEG[31:28]/COM[7:4] | COM[7:4]   |

|         | 0/1         | 28x8      | COM[3:0]                       | COM[3:0]   |

|         |             |           | SEG[27:0]                      | SEG[27:0]  |

|         |             |           | COM[3:0]                       | COM[3:0]   |

|         | 0           | 44x4      | SEG[43:40]/SEG[31:28]/COM[7:4] | SEG[43:40] |

|         |             |           | SEG[39:0]                      | SEG[39:0]  |

|         |             |           | COM[3:0]                       | COM[3:0]   |

|         |             |           | SEG[43:40]/SEG[31:28]/COM[7:4] | SEG[31:28] |

|         | 1           | 40x4      | SEG[39:32]                     | SEG[39:32] |

| 1/4     |             |           | SEG[31:28]                     | not used   |

| 1/4     |             |           | SEG[27:0]                      | SEG[27:0]  |

|         |             |           | COM[3:0]                       | COM[3:0]   |

|         | 0           | 28x4      | SEG[43:40]/SEG[31:28]/COM[7:4] | not used   |

|         |             |           | SEG[27:0]                      | SEG[27:0]  |

|         |             |           | COM[3:0]                       | COM[3:0]   |

|         | 1           | 32x4      | SEG[43:40]/SEG[31:28]/COM[7:4] | SEG[31:28] |

|         |             |           | SEG[27:0]                      | SEG[27:0]  |

The nonce value and 32-bit counter are accessible through the AES\_IVRx register and organized like below in *Figure 144*:

|          |          | i i i i i i i i i i i i i i i i i i i |                 |           |

|----------|----------|---------------------------------------|-----------------|-----------|

| AES_IVR3 | AES_IVR2 | AES_IVR1                              | AES_IVR0        |           |

|          | Nonce I  |                                       | 32- bit counter |           |

|          |          |                                       |                 | MS18943V1 |

Figure 144. 32-bit counter + nonce organization

In counter mode, the counter is incremented from the initialized value for each block to be processed in order to guarantee a unique sequence which is not repeated for a long time. It is a 32-bit counter, meaning that the nonce message is kept to the initialized value stored when the AES was disabled. Only the 32-bit LSB of the 128-bit initialization vector register represents the counter. In contrast to CBC mode (which uses the AES\_IVRx registers only once when processing the first data block), in counter mode, the AES\_IVRx registers are used for processing each data block.

In counter mode, key derivation + decryption mode is not applicable.

The AES\_IVRx register has be written only when the AES is disabled (bit EN = 0) to guarantee good AES behavior.

Reading it while AES is enabled returns the value 0x00000000.

Reading it while the AES is disabled returns the latest counter value (useful for managing suspend mode).

In CTR mode, key derivation + decryption serves no purpose. Consequently it is forbidden to set MODE[1:0] = 11 in the AES\_CR register and any attempt to set this configuration is forced to MODE[1:0] = 10 (which corresponds to CTR mode decryption). This uses the encryption block of the AES processor to decipher the message as shown in *Figure 143*.

# Suspend mode in CTR mode

Like for the CBC mode, it is possible to interrupt a message, sending a higher priority message and resume the message which was interrupted. Refer to the *Figure 141* and *Section 25.5.2* for more details about the suspend mode capability.

# 25.6 Galois counter mode (GCM)

GCM allows to encrypt and authenticate the plaintext, generating the corresponding ciphertext and the TAG (also known as message authentication code or message integrity check). It is based on AES in counter mode for confidentiality and it uses a multiplier over a fixed finite field for generating the TAG. It requires an initialization vector at the beginning. The message to process can be split in 2 different portions:

- The first that is authenticated only (the header of the message),

- The second that is authenticated and encrypted (the payload).

The header part must precede the payload and the two portions cannot be mixed. GCM standard requires to pass at the end of the message a particular 128-bit block composed by

Note:

forced to CTR decryption mode if the software writes MODE[1:0] = 11 and CHMOD[2:0] = 010.

- 3. Select key length 128-bit or 256-bit via KEYSIZE bits configuration in AES\_CR register.

- 4. Write the AES\_KEYRx register with the encryption key. Write the AES\_IVRx register if the CBC mode is selected.

- 5. Enable the AES by setting the EN bit in the AES\_CR register.

- 6. Write the AES\_DINR register 4 times to input the cipher text (MSB first) as shown in *Figure 150: Mode 4: key derivation and decryption with 128-bit key length.*

- 7. Wait until the CCF flag is set in the AES\_SR register.

- 8. Read the AES\_DOUTR register 4 times to get the plain text (MSB first) as shown in *Figure 150: Mode 4: key derivation and decryption with 128-bit key length.*

- 9. Repeat steps 6, 7, 8 to process all the blocks with the same encryption key.

The AES\_KEYRx registers contain the encryption key during all phases of the processing, No derivation key is stored in these registers. The derivation key starting from the encryption key is stored internally in the AES without storing a copy in the AES\_KEYRx registers.

Figure 150. Mode 4: key derivation and decryption with 128-bit key length

# 25.10 AES DMA interface

The AES accelerator provides an interface to connect to the DMA controller.

The DMA must be configured to transfer words.

The AES can be associated with two distinct DMA request channels:

- A DMA request channel for the inputs: When the DMAINEN bit is set in the AES\_CR register, the AES initiates a DMA request (AES\_IN) during the INPUT phase each time it requires a word to be written to the AES\_DINR register. The DMA channel must be configured in memory-to-peripheral mode with 32-bit data size.

- A DMA request channel for the outputs: When the DMAOUTEN bit is enabled, the AES initiates a DMA request (AES\_OUT) during the OUTPUT phase each time it requires a word to be read from the AES\_DOUTR register. The DMA channel must be configured in peripheral-to-memory mode with a data size equal to 32-bit.

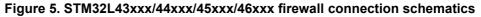

Four DMA requests are asserted for each phase, these are described in *Figure 151* and *Figure 152*.

DMA requests are generated until the AES is disabled. So, after the data output phase at the end of processing a 128-bit data block, the AES switches automatically to a new data input phase for the next data block if any.

Note:

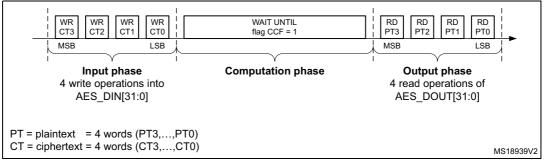

Figure 195. Dead-time waveforms with delay greater than the positive pulse

The dead-time delay is the same for each of the channels and is programmable with the DTG bits in the TIMx\_BDTR register. Refer to *Section 26.4.18: TIM1 break and dead-time register (TIMx\_BDTR)* for delay calculation.

#### Re-directing OCxREF to OCx or OCxN

In output mode (forced, output compare or PWM), OCxREF can be re-directed to the OCx output or to OCxN output by configuring the CCxE and CCxNE bits in the TIMx\_CCER register.

This allows you to send a specific waveform (such as PWM or static active level) on one output while the complementary remains at its inactive level. Other alternative possibilities are to have both outputs at inactive level or both outputs active and complementary with dead-time.

Note: When only OCxN is enabled (CCxE=0, CCxNE=1), it is not complemented and becomes active as soon as OCxREF is high. For example, if CCxNP=0 then OCxN=OCxRef. On the other hand, when both OCx and OCxN are enabled (CCxE=CCxNE=1) OCx becomes active when OCxREF is high whereas OCxN is complemented and becomes active when OCxREF is low.

### 26.3.16 Using the break function

The purpose of the break function is to protect power switches driven by PWM signals generated with the TIM1 timer. The two break inputs are usually connected to fault outputs of power stages and 3-phase inverters. When activated, the break circuitry shuts down the PWM outputs and forces them to a predefined safe state. A number of internal MCU events can also be selected to trigger an output shut-down.

The break features two channels. A break channel which gathers both system-level fault (clock failure, parity error,...) and application fault (from input pins and built-in comparator), and can force the outputs to a predefined level (either active or inactive) after a deadtime duration. A break2 channel which only includes application faults and is able to force the outputs to an inactive state.

# 27.3 TIM2/TIM3 functional description

## 27.3.1 Time-base unit

The main block of the programmable timer is a 16-bit/32-bit counter with its related autoreload register. The counter can count up, down or both up and down but also down or both up and down. The counter clock can be divided by a prescaler.

The counter, the auto-reload register and the prescaler register can be written or read by software. This is true even when the counter is running.

The time-base unit includes:

- Counter Register (TIMx\_CNT)

- Prescaler Register (TIMx\_PSC):

- Auto-Reload Register (TIMx\_ARR)

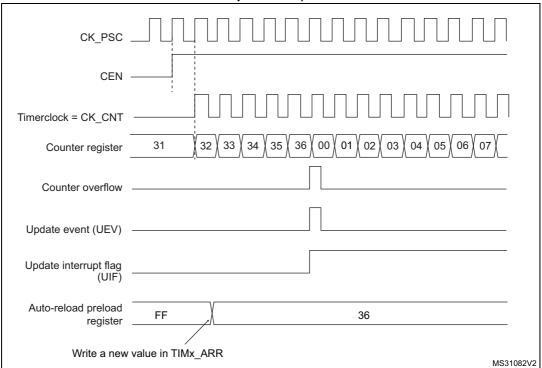

The auto-reload register is preloaded. Writing to or reading from the auto-reload register accesses the preload register. The content of the preload register are transferred into the shadow register permanently or at each update event (UEV), depending on the auto-reload preload enable bit (ARPE) in TIMx\_CR1 register. The update event is sent when the counter reaches the overflow (or underflow when downcounting) and if the UDIS bit equals 0 in the TIMx\_CR1 register. The generation of the update event is described in detail for each configuration.

The counter is clocked by the prescaler output CK\_CNT, which is enabled only when the counter enable bit (CEN) in TIMx\_CR1 register is set (refer also to the slave mode controller description to get more details on counter enabling).

Note that the actual counter enable signal CNT\_EN is set 1 clock cycle after CEN.

#### Prescaler description

The prescaler can divide the counter clock frequency by any factor between 1 and 65536. It is based on a 16-bit counter controlled through a 16-bit/32-bit register (in the TIMx\_PSC register). It can be changed on the fly as this control register is buffered. The new prescaler ratio is taken into account at the next update event.

*Figure 214* and *Figure 215* give some examples of the counter behavior when the prescaler ratio is changed on the fly:

| Figure 21                      | 9. Counter timing diagram, internal clock divided by N |   |

|--------------------------------|--------------------------------------------------------|---|

| CK_PSC                         |                                                        |   |

| Timerclock = CK_CNT            |                                                        |   |

| Counter register               | IF 20 00                                               |   |

| Counter overflow               |                                                        |   |

| Update event (UEV)             |                                                        |   |

| Update interrupt flag<br>(UIF) |                                                        |   |

|                                | MS31081V2                                              | 2 |

Figure 219. Counter timing diagram, internal clock divided by N

Figure 220. Counter timing diagram, Update event when ARPE=0 (TIMx\_ARR not preloaded)

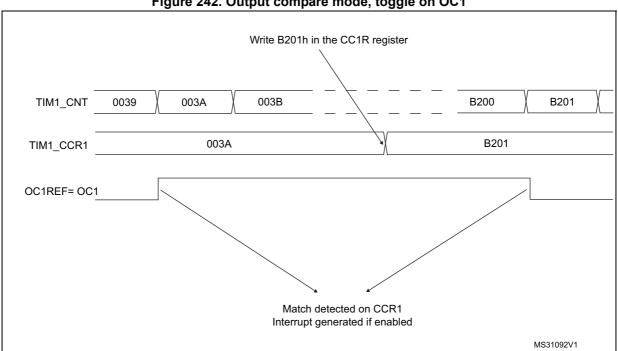

#### Figure 242. Output compare mode, toggle on OC1

#### 27.3.9 **PWM mode**

Pulse width modulation mode allows you to generate a signal with a frequency determined by the value of the TIMx ARR register and a duty cycle determined by the value of the TIMx CCRx register.

The PWM mode can be selected independently on each channel (one PWM per OCx output) by writing 110 (PWM mode 1) or '111 (PWM mode 2) in the OCxM bits in the TIMx CCMRx register. You must enable the corresponding preload register by setting the OCxPE bit in the TIMx CCMRx register, and eventually the auto-reload preload register (in upcounting or center-aligned modes) by setting the ARPE bit in the TIMx CR1 register.

As the preload registers are transferred to the shadow registers only when an update event occurs, before starting the counter, you have to initialize all the registers by setting the UG bit in the TIMx EGR register.

OCx polarity is software programmable using the CCxP bit in the TIMx CCER register. It can be programmed as active high or active low. OCx output is enabled by the CCxE bit in the TIMx CCER register. Refer to the TIMx CCERx register description for more details.

In PWM mode (1 or 2), TIMx CNT and TIMx CCRx are always compared to determine whether TIMx\_CCRx ≤ TIMx\_CNT or TIMx\_CNT ≤ TIMx\_CCRx (depending on the direction of the counter). However, to comply with the OCREF CLR functionality (OCREF can be cleared by an external event through the ETR signal until the next PWM period), the OCREF signal is asserted only:

- When the result of the comparison or

- When the output compare mode (OCxM bits in TIMx CCMRx register) switches from the "frozen" configuration (no comparison, OCxM='000) to one of the PWM modes (OCxM='110 or '111).

This forces the PWM by software while the timer is running.

DocID027295 Rev 3

RM0394

### 28.6.14 TIM16 DMA control register (TIMx\_DCR)

#### Address offset: 0x48

#### Reset value: 0x0000

| 15   | 14   | 13   | 12 | 11 | 10       | 9  | 8  | 7    | 6    | 5    | 4  | 3  | 2        | 1  | 0  |

|------|------|------|----|----|----------|----|----|------|------|------|----|----|----------|----|----|

| Res. | Res. | Res. |    |    | DBL[4:0] |    |    | Res. | Res. | Res. |    |    | DBA[4:0] |    |    |

|      |      |      | rw | rw | rw       | rw | rw |      |      |      | rw | rw | rw       | rw | rw |

Bits 15:13 Reserved, must be kept at reset value.

#### Bits 12:8 DBL[4:0]: DMA burst length

This 5-bit field defines the length of DMA transfers (the timer recognizes a burst transfer when a read or a write access is done to the TIMx\_DMAR address), i.e. the number of transfers. Transfers can be in half-words or in bytes (see example below).

00000: 1 transfer, 00001: 2 transfers,

00010: 3 transfers,

10001: 18 transfers.

Bits 7:5 Reserved, must be kept at reset value.

#### Bits 4:0 DBA[4:0]: DMA base address

This 5-bit field defines the base-address for DMA transfers (when read/write access are done through the TIMx\_DMAR address). DBA is defined as an offset starting from the address of the TIMx\_CR1 register.

Example: 00000: TIMx\_CR1, 00001: TIMx\_CR2, 00010: TIMx\_SMCR,

**Example:** Let us consider the following transfer: DBL = 7 transfers and DBA = TIMx\_CR1. In this case the transfer is done to/from 7 registers starting from the TIMx\_CR1 address.

#### 28.6.15 TIM16 DMA address for full transfer (TIMx\_DMAR)

Address offset: 0x4C

Reset value: 0x0000

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7       | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|------|---------|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    | DMAE | 8[15:0] |    |    |    |    |    |    |    |

| rw   | rw      | rw | rw | rw | rw | rw | rw | rw |

Bits 15:0 DMAB[15:0]: DMA register for burst accesses

A read or write operation to the DMAR register accesses the register located at the address (TIMx\_CR1 address) + (DBA + DMA index) x 4 where TIMx\_CR1 address is the address of the control register 1, DBA is the DMA base address configured in TIMx\_DCP register. DMA index is automatically controlled by the

address configured in TIMx\_DCR register, DMA index is automatically controlled by the DMA transfer, and ranges from 0 to DBL (DBL configured in TIMx\_DCR).

Note:

#### **Overrun error**

An overrun error occurs when a character is received when RXNE has not been reset. Data can not be transferred from the shift register to the RDR register until the RXNE bit is cleared.

The RXNE flag is set after every byte received. An overrun error occurs if RXNE flag is set when the next data is received or the previous DMA request has not been serviced. When an overrun error occurs:

- The ORE bit is set.

- The RDR content will not be lost. The previous data is available when a read to USART\_RDR is performed.

- The shift register will be overwritten. After that point, any data received during overrun is lost.

- An interrupt is generated if either the RXNEIE bit is set or EIE bit is set.

- The ORE bit is reset by setting the ORECF bit in the ICR register.

The ORE bit, when set, indicates that at least 1 data has been lost. There are two possibilities:

- if RXNE=1, then the last valid data is stored in the receive register RDR and can be read,

- if RXNE=0, then it means that the last valid data has already been read and thus there is nothing to be read in the RDR. This case can occur when the last valid data is read in the RDR at the same time as the new (and lost) data is received.

#### Selecting the clock source and the proper oversampling method

The choice of the clock source is done through the Clock Control system (see Section Reset and clock control (RCC))). The clock source must be chosen before enabling the USART (by setting the UE bit).

The choice of the clock source must be done according to two criteria:

- Possible use of the USART in low-power mode

- Communication speed.

The clock source frequency is  $f_{CK}$ .

When the dual clock domain with the wakeup from Stop mode is supported, the clock source can be one of the following sources: PCLK (default), LSE, HSI16 or SYSCLK. Otherwise, the USART clock source is PCLK.

Choosing LSE or HSI16 as clock source may allow the USART to receive data while the MCU is in low-power mode. Depending on the received data and wakeup mode selection, the USART wakes up the MCU, when needed, in order to transfer the received data by software reading the USART\_RDR register or by DMA.

For the other clock sources, the system must be active in order to allow USART communication.

The communication speed range (specially the maximum communication speed) is also determined by the clock source.

The receiver implements different user-configurable oversampling techniques for data recovery by discriminating between valid incoming data and noise. This allows a trade-off between the maximum communication speed and noise/clock inaccuracy immunity.

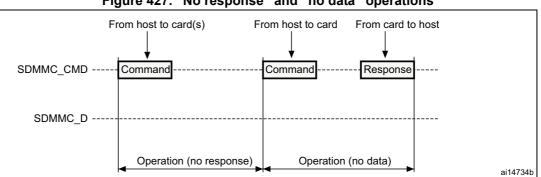

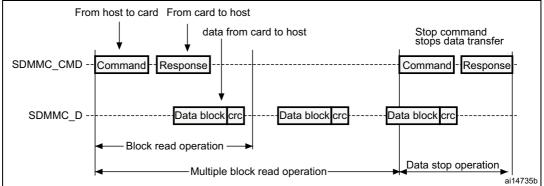

Figure 427. "No response" and "no data" operations

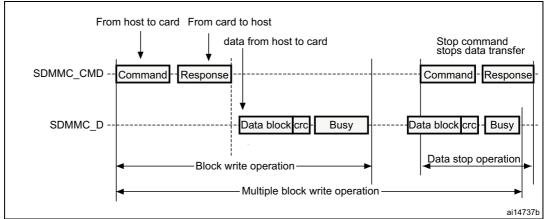

Figure 429. (Multiple) block write operation

The SDMMC will not send any data as long as the Busy signal is asserted (SDMMC\_D0 Note: pulled low).

### RM0394

# 41.8.16 SDMMC register map

The following table summarizes the SDMMC registers.

| Offset | Register                                                                                                                                                                                                                                        | 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   | 15    | 14      | 13      | 12     | 11          | 10     | 6        | 8       | 2    | 9    | 2    | 4      | 3     | 7      | -       | 0    |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-------|---------|---------|--------|-------------|--------|----------|---------|------|------|------|--------|-------|--------|---------|------|

| 0x00   | SDMMC_<br>POWER                                                                                                                                                                                                                                 | Res.  | Res.    | Res.    | Res.   | Res.        | Res.   | Res.     | Res.    | Res. | Res. | Res. | Res.   | Res.  | Res.   | PWRCTRL |      |

|        | Reset value                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |       |         |         |        |             |        |          |         |      |      |      |        |       |        | 0       | 0    |

| 0x04   | SDMMC_<br>CLKCR                                                                                                                                                                                                                                 | Res.  | HWFC_EN | NEGEDGE | MIDRUS |             | BYPASS | PWRSAV   | CLKEN   |      |      |      | CLKDIV |       |        |         |      |

|        | Reset value                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |       | 0       | 0       | 0      | 0           | 0      | 0        | 0       | 0    | 0    | 0    | 0      | 0     | 0      | 0       | 0    |

| 0x08   | SDMMC_ARG                                                                                                                                                                                                                                       |      | _    |      |      | _    | _    |      |      |      |      |      |      |      | _    | (    | CME  | )AR   | G       |         |        |             |        |          |         | _    |      |      |        |       |        |         |      |

| 0,000  | Reset value                                                                                                                                                                                                                                     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0       | 0       | 0      | 0           | 0      | 0        | 0       | 0    | 0    | 0    | 0      | 0     | 0      | 0       | 0    |

| 0x0C   | SDMMC_CMD                                                                                                                                                                                                                                       | Res.  | Res.    | Res.    | Res.   | SDIOSuspend | CPSMEN | WAITPEND | WAITINT |      |      |      |        |       |        |         |      |

|        | Reset value                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |       |         |         |        | 0           | 0      | 0        | 0       | 0    | 0    | 0    | 0      | 0     | 0      | 0       | 0    |

| 0x10   | SDMMC_<br>RESPCMD                                                                                                                                                                                                                               | Res.  | Res.    | Res.    | Res.   | Res.        | Res.   | Res.     | Res.    | Res. | Res. |      | R      | ESF   | СМ     | D       |      |

|        | Reset value                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |       |         |         |        |             |        |          |         |      |      | 0    | 0      | 0     | 0      | 0       | 0    |

| 0x14   | Reset value 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 <th< td=""></th<> |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |       |         |         |        |             |        |          |         |      |      |      |        |       |        |         |      |

|        | Reset value                                                                                                                                                                                                                                     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0       | 0       | 0      | 0           | 0      | 0        | 0       | 0    | 0    | 0    | 0      | 0     | 0      | 0       | 0    |

| 0x18   | SDMMC_<br>RESP2                                                                                                                                                                                                                                 |      |      |      |      |      |      |      |      | -    |      |      |      | -    |      | CAI  | RDS  | TAT   | US      | 2       |        |             | -      | -        |         |      |      | -    |        |       |        |         |      |

|        | Reset value                                                                                                                                                                                                                                     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0       | 0       | 0      | 0           | 0      | 0        | 0       | 0    | 0    | 0    | 0      | 0     | 0      | 0       | 0    |

| 0x1C   | SDMMC_<br>RESP3                                                                                                                                                                                                                                 |      | 1    | 1    | 1    | 1    | 1    |      |      |      |      |      |      | 1    |      |      |      | TAT   |         |         |        |             |        | 1        |         | 1    |      | 1    |        |       |        |         |      |

|        | Reset value                                                                                                                                                                                                                                     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0       | 0       | 0      | 0           | 0      | 0        | 0       | 0    | 0    | 0    | 0      | 0     | 0      | 0       | 0    |

| 0x20   | SDMMC_<br>RESP4                                                                                                                                                                                                                                 |      | i    |      |      | i    | 1    |      |      |      |      |      |      | 1    |      |      | RDS  | TAT   | US      |         |        |             |        | 1        |         | i    | 1    | 1    |        |       |        | -       |      |

|        | Reset value                                                                                                                                                                                                                                     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0       | 0       | 0      | 0           | 0      | 0        | 0       | 0    | 0    | 0    | 0      | 0     | 0      | 0       | 0    |

| 0x24   | SDMMC_<br>DTIMER                                                                                                                                                                                                                                |      | 1    | 1    | T    | 1    | 1    |      |      |      |      |      |      |      | 1    |      |      | AT IN |         |         |        |             |        |          |         | 1    |      |      |        |       |        |         |      |

|        | Reset value                                                                                                                                                                                                                                     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0       | 0       | 0      | 0           | 0      | 0        | 0       | 0    | 0    | 0    | 0      | 0     | 0      | 0       | 0    |

| 0x28   | SDMMC_<br>DLEN                                                                                                                                                                                                                                  | Res. |      |      |      |      |      |      |      |      |      |       |         | ATA     |        |             |        |          |         |      |      |      |        |       |        |         |      |

|        | Reset value                                                                                                                                                                                                                                     |      |      |      |      |      |      |      | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0       | 0       | 0      | 0           | 0      | 0        | 0       | 0    | 0    | 0    | 0      | 0     | 0      | 0       | 0    |

| 0x2C   | SDMMC_<br>DCTRL                                                                                                                                                                                                                                 | Res.  | Res.    | Res.    | Res.   | SDIOEN      | RWMOD  | RWSTOP   | RWSTART |      |      |      |        | DMAEN | DTMODE | DTDIR   | DIEN |

|        | Reset value                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |       |         |         |        | 0           | 0      | 0        | 0       | 0    | 0    | 0    | 0      | 0     | 0      | 0       | 0    |

| 0x30   | SDMMC_<br>DCOUNT                                                                                                                                                                                                                                | Res. |      |      |      |      |      |      |      |      |      |       | D       | ATA     |        |             |        |          |         |      |      |      |        |       |        |         |      |

|        | Reset value                                                                                                                                                                                                                                     |      |      |      |      |      |      |      | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0       | 0       | 0      | 0           | 0      | 0        | 0       | 0    | 0    | 0    | 0      | 0     | 0      | 0       | 0    |

Table 229. SDMMC register map

## 44.6.1 MCU device ID code

The STM32L43xxx/44xxx/45xxx/46xxx MCUs integrate an MCU ID code. This ID identifies the ST MCU part-number and the die revision. It is part of the DBG\_MCU component and is mapped on the external PPB bus (see Section 44.16 on page 1449). This code is accessible using the JTAG debug port (4 to 5 pins) or the SW debug port (two pins) or by the user software. It is even accessible while the MCU is under system reset.

Only the DEV\_ID(11:0) should be used for identification by the debugger/programmer tools.

### DBGMCU\_IDCODE

Address: 0xE004 2000

Only 32-bits access supported. Read-only

| 31     | 30   | 29   | 28   | 27     | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|--------|------|------|------|--------|----|----|----|----|----|----|----|----|----|----|----|

| REV_ID |      |      |      |        |    |    |    |    |    |    |    |    |    |    |    |

| r      | r    | r    | r    | r      | r  | r  | r  | r  | r  | r  | r  | r  | r  | r  | r  |

| 15     | 14   | 13   | 12   | 11     | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| Res.   | Res. | Res. | Res. | DEV_ID |    |    |    |    |    |    |    |    |    |    |    |

|        |      |      |      | r      | r  | r  | r  | r  | r  | r  | r  | r  | r  | r  | r  |

Bits 31:16 **REV\_ID[15:0]** Revision identifier

This field indicates the revision of the device. 0x1000: Rev A 0x1001: Rev Z Others: Reserved

Bits 15:12 Reserved, must be kept at reset value.

#### Bits 11:0 DEV\_ID[11:0]: Device identifier

- The device ID is:

- 0x435 for STM32L43xxx and STM32L44xxx devices

- 0x462 for STM32L45xxx and STM32L46xxx devices

# 44.6.2 Boundary scan TAP

### JTAG ID code

The TAP of the STM32L43xxx/44xxx/45xxx/46xxx BSC (boundary scan) integrates a JTAG ID code equal to 0x06435041.

# 44.6.3 Cortex<sup>®</sup>-M4 TAP

The TAP of the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 integrates a JTAG ID code. This ID code is the ARM<sup>®</sup> default one and has not been modified. This code is only accessible by the JTAG Debug Port.

This code is **0x4BA00477** (corresponds to Cortex<sup>®</sup>-M4 r0p1, see Section 44.2: Reference ARM® documentation).

# 45.3 Package data register

Base address: 0x1FFF 7500

Address offset: 0x00

Read only = 0xXXXX where X is factory-programmed

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4        | 3 | 2 | 1 | 0 |

|------|------|------|------|------|------|------|------|------|------|------|----------|---|---|---|---|

| Res. | PKG[4:0] |   |   |   |   |

|      |      |      |      |      |      |      |      |      |      |      | r        | r | r | r | r |

Bits 15:5 Reserved, must be kept at reset value

Bits 4:0 **PKG[4:0]**: Package type

00000: LQFP64 00001: WLCSP64 00010: LQFP100 01010: UFQFPN48 01011: LQFP48 01100: WLCSP49 01101: UFBGA64 01110: UFBGA100 Others: reserved