Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                 |

| Core Processor             | ARM® Cortex®-M4                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                     |

| Speed                      | 80MHz                                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                             |

| Number of I/O              | 52                                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 64K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                  |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 64-UFBGA, WLCSP                                                                        |

| Supplier Device Package    | 64-WLCSP (3.14x3.13)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l433rcy3tr                |

Table 14. Flash interface - register map and reset values (continued)

| Offset | Register         | 31   | 30   | 29   | 28   | 27   | 56   | 25   | 24   | 23 | 22 | 21  | 20  | 19 | 18   | 17 | 16 | 15   | 14   | 13   | 12   | 11   | 10   | 6    | 8    | 7 | 9 | 2   | 4    | 3   | 2    | -  | 0 |

|--------|------------------|------|------|------|------|------|------|------|------|----|----|-----|-----|----|------|----|----|------|------|------|------|------|------|------|------|---|---|-----|------|-----|------|----|---|

| 0x30   | FLASH_<br>WRP1BR | Res. |    | V  | /RP | 1B_ | EN | D[7: | 0] |    | Res. |   | W | RP1 | IB_S | STR | T[7: | 0] |   |

|        | Reset value      |      |      |      |      |      |      |      |      | Х  | Х  | Х   | Х   | Х  | Х    | Х  | Х  |      |      |      |      |      |      |      |      | Х | Х | Х   | Х    | Х   | Х    | Х  | Х |

Refer to Section 2.2.2 on page 64 for the register boundary addresses.

Table 24. Stop 0 mode

| Stop 0 mode    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | WFI (Wait for Interrupt) or WFE (Wait for Event) while:  - SLEEPDEEP bit is set in Cortex®-M4 System Control register  - No interrupt (for WFI) or event (for WFE) is pending  - LPMS = "000" in PWR_CR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Mode entry     | On Return from ISR while:  — SLEEPDEEP bit is set in Cortex®-M4 System Control register  — SLEEPONEXIT = 1  — No interrupt is pending  — LPMS = "000" in PWR_CR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                | Note: To enter Stop 0 mode, all EXTI Line pending bits (in Pending register 1 (EXTI_PR1)), and the peripheral flags generating wakeup interrupts must be cleared. Otherwise, the Stop 0 mode entry procedure is ignored and program execution continues.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Mode exit      | If WFI or Return from ISR was used for entry  Any EXTI Line configured in Interrupt mode (the corresponding EXTI Interrupt vector must be enabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to Table 45: STM32L43xxx/44xxx/45xxx/46xxx vector table.  If WFE was used for entry and SEVONPEND = 0: Any EXTI Line configured in event mode. Refer to Section 13.3.2: Wakeup event management.  If WFE was used for entry and SEVONPEND = 1: Any EXTI Line configured in Interrupt mode (even if the corresponding EXTI Interrupt vector is disabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to Table 45: STM32L43xxx/44xxx/45xxx/46xxx vector table. Wakeup event: refer to Section 13.3.2: Wakeup event management |

| Wakeup latency | Longest wakeup time between: MSI or HSI16 wakeup time and Flash wakeup time from Stop 0 mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# 5.3.7 Stop 1 mode

The Stop 1 mode is the same as Stop 0 mode except that the main regulator is OFF, and only the low-power regulator is ON. Stop 1 mode can be entered from Run mode and from Low-power run mode.

Refer to *Table 25: Stop 1 mode* for details on how to enter and exit Stop 1 mode.

Power control (PWR) RM0394

Table 25. Stop 1 mode

| Stop 1 mode    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | WFI (Wait for Interrupt) or WFE (Wait for Event) while:  - SLEEPDEEP bit is set in Cortex®-M4 System Control register  - No interrupt (for WFI) or event (for WFE) is pending  - LPMS = "001" in PWR_CR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Mode entry     | On Return from ISR while:  - SLEEPDEEP bit is set in Cortex®-M4 System Control register  - SLEEPONEXIT = 1  - No interrupt is pending  - LPMS = "001" in PWR_CR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                | Note: To enter Stop 1 mode, all EXTI Line pending bits (in Pending register 1 (EXTI_PR1)), and the peripheral flags generating wakeup interrupts must be cleared. Otherwise, the Stop 1 mode entry procedure is ignored and program execution continues.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Mode exit      | If WFI or Return from ISR was used for entry  Any EXTI Line configured in Interrupt mode (the corresponding EXTI Interrupt vector must be enabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to Table 45: STM32L43xxx/44xxx/45xxx/46xxx vector table.  If WFE was used for entry and SEVONPEND = 0:  Any EXTI Line configured in event mode. Refer to Section 13.3.2:  Wakeup event management.  If WFE was used for entry and SEVONPEND = 1:  Any EXTI Line configured in Interrupt mode (even if the corresponding EXTI Interrupt vector is disabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to Table 45: STM32L43xxx/44xxx/45xxx/46xxx vector table. |

| Wakeup latency | Wakeup event: refer to Section 13.3.2: Wakeup event management  Longest wakeup time between: MSI or HSI16 wakeup time and regulator wakeup time from Low-power mode + Flash wakeup time from Stop 1 mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# 5.3.8 Stop 2 mode

The Stop 2 mode is based on the Cortex $^{\$}$ -M4 deepsleep mode combined with peripheral clock gating. In Stop 2 mode, all clocks in the V<sub>CORE</sub> domain are stopped, the PLL, the MSI, the HSI16 and the HSE oscillators are disabled. Some peripherals with wakeup capability (I2C3 and LPUART) can switch on the HSI16 to receive a frame, and switch off the HSI16 after receiving the frame if it is not a wakeup frame. In this case the HSI16 clock is propagated only to the peripheral requesting it.

SRAM1, SRAM2 and register contents are preserved.

The BOR is always available in Stop 2 mode. The consumption is increased when thresholds higher than  $V_{BOR0}$  are used.

Note: The comparators outputs, the LPUART outputs and the LPTIM1 outputs are forced to low speed (OSPEEDy=00) during the Stop 2 mode.

| RES<br>(bits) | T <sub>SAR</sub><br>(ADC clock cycles) | T <sub>SAR</sub> (ns) at<br>F <sub>ADC</sub> =80 MHz | T <sub>CONV</sub> (ADC clock cycles)<br>(with Sampling Time=<br>2.5 ADC clock cycles) | T <sub>CONV</sub> (ns) at<br>F <sub>ADC</sub> =80 MHz |

|---------------|----------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------|

| 12            | 12.5 ADC clock cycles                  | 156.25 ns                                            | 15 ADC clock cycles                                                                   | 187.5 ns                                              |

| 10            | 10.5 ADC clock cycles                  | 131.25 ns                                            | 13 ADC clock cycles                                                                   | 162.5 ns                                              |

| 8             | 8.5 ADC clock cycles                   | 106.25 ns                                            | 11 ADC clock cycles                                                                   | 137.5 ns                                              |

| 6             | 6.5 ADC clock cycles                   | 81.25 ns                                             | 9 ADC clock cycles                                                                    | 112.5 ns                                              |

Table 60. T<sub>SAR</sub> timings depending on resolution

# 16.4.23 End of conversion, end of sampling phase (EOC, JEOC, EOSMP)

The ADC notifies the application for each end of regular conversion (EOC) event and each injected conversion (JEOC) event.

The ADC sets the EOC flag as soon as a new regular conversion data is available in the ADC\_DR register. An interrupt can be generated if bit EOCIE is set. EOC flag is cleared by the software either by writing 1 to it or by reading ADC\_DR.

The ADC sets the JEOC flag as soon as a new injected conversion data is available in one of the ADC\_JDRy register. An interrupt can be generated if bit JEOCIE is set. JEOC flag is cleared by the software either by writing 1 to it or by reading the corresponding ADC\_JDRy register.

The ADC also notifies the end of Sampling phase by setting the status bit EOSMP (for regular conversions only). EOSMP flag is cleared by software by writing 1 to it. An interrupt can be generated if bit EOSMPIE is set.

# 16.4.24 End of conversion sequence (EOS, JEOS)

The ADC notifies the application for each end of regular sequence (EOS) and for each end of injected sequence (JEOS) event.

The ADC sets the EOS flag as soon as the last data of the regular conversion sequence is available in the ADC\_DR register. An interrupt can be generated if bit EOSIE is set. EOS flag is cleared by the software either by writing 1 to it.

The ADC sets the JEOS flag as soon as the last data of the injected conversion sequence is complete. An interrupt can be generated if bit JEOSIE is set. JEOS flag is cleared by the software either by writing 1 to it.

## Simultaneous trigger with different triangle generation

To configure the DAC in this conversion mode, the following sequence is required:

- Set the two DAC channel trigger enable bits TEN1 and TEN2

- Configure the same trigger source for both DAC channels by setting the same value in the TSEL1[2:0] and TSEL2[2:0] bits

- Configure the two DAC channel WAVEx[1:0] bits as "1x" and set different maximum amplitude values in the MAMP1[3:0] and MAMP2[3:0] bits

- Load the dual DAC channel data into the desired DHR register (DAC\_DHR12RD, DAC\_DHR12LD or DAC\_DHR8RD)

When a trigger arrives, the DAC channel1 triangle counter, with a triangle amplitude configured by MAMP1[3:0], is added to the DHR1 register and the sum is transferred into DAC\_DOR1 (three APB clock cycles later). Then the DAC channel1 triangle counter is updated.

At the same time, the DAC channel2 triangle counter, with a triangle amplitude configured by MAMP2[3:0], is added to the DHR2 register and the sum is transferred into DAC\_DOR2 (three APB1 clock cycles later). Then the DAC channel2 triangle counter is updated.

- enabled by JOVRIE bit in DFSDM\_FLTxCR2 register

- indicated in JOVRF bit in DFSDM\_FLTxISR register

- cleared by writing '1' into CLRJOVRF bit in DFSDM FLTxICR register

- Data overrun interrupt for regular conversions:

- occurred when regular converted data were not read from DFSDM\_FLTxRDATAR register (by CPU or DMA) and were overwritten by a new regular conversion

- enabled by ROVRIE bit in DFSDM FLTxCR2 register

- indicated in ROVRF bit in DFSDM\_FLTxISR register

- cleared by writing '1' into CLRROVRF bit in DFSDM\_FLTxICR register

- Analog watchdog interrupt:

- occurred when converted data (output data or data from analog watchdog filter according to AWFSEL bit setting in DFSDM\_FLTxCR1 register) crosses over/under high/low thresholds in DFSDM\_FLTxAWHTR / DFSDM\_FLTxAWLTR registers

- enabled by AWDIE bit in DFSDM\_FLTxCR2 register (on selected channels AWDCH[3:0])

- indicated in AWDF bit in DFSDM FLTxISR register

- separate indication of high or low analog watchdog threshold error by AWHTF[3:0] and AWLTF[3:0] fields in DFSDM\_FLTxAWSR register

- cleared by writing '1' into corresponding CLRAWHTF[3:0] or CLRAWLTF[3:0] bits in DFSDM FLTxAWCFR register

- Short-circuit detector interrupt:

- occurred when the number of stable data crosses over thresholds in DFSDM\_CHyAWSCDR register

- enabled by SCDIE bit in DFSDM\_FLTxCR2 register (on channel selected by SCDEN bit in DFSDM\_CHyCFGR1 register)

- indicated in SCDF[3:0] bits in DFSDM\_FLTxISR register (which also reports the channel on which the short-circuit detector event occurred)

- cleared by writing '1' into the corresponding CLRSCDF[3:0] bit in DFSDM FLTxICR register

- Channel clock absence interrupt:

- occurred when there is clock absence on CKINy pin (see Clock absence detection in Section 21.4.4: Serial channel transceivers)

- enabled by CKABIE bit in DFSDM\_FLTxCR2 register (on channels selected by CKABEN bit in DFSDM\_CHyCFGR1 register)

- indicated in CKABF[y] bit in DFSDM\_FLTxISR register

- cleared by writing '1' into CLRCKABF[y] bit in DFSDM\_FLTxICR register

### Table 97. DFSDM interrupt requests

| Interrupt event            | Event flag | Event/Interrupt clearing method | Interrupt enable control bit |

|----------------------------|------------|---------------------------------|------------------------------|

| End of injected conversion | JEOCF      | reading DFSDM_FLTxJDATAR        | JEOCIE                       |

| End of regular conversion  | REOCF      | reading DFSDM_FLTxRDATAR        | REOCIE                       |

| Injected data overrun      | JOVRF      | writing CLRJOVRF = 1            | JOVRIE                       |

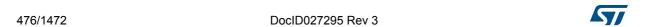

COM[n] n[0 to 7] is active during phase n in the odd frame, so the COM pin is driven to  $V_{ICD}$ .

During phase n of the even frame the COM pin is driven to  $V_{SS}$ .

In the case of 1/3 or 1/4) bias:

COM[n] is inactive during phases other than n so the COM pin is driven to 1/3 (1/4)

V<sub>I CD</sub> during odd frames and to 2/3 (3/4) V<sub>I CD</sub> during even frames

In the case of 1/2 bias:

If COM[n] is inactive during phases other than n, the COM pin is always driven (odd and even frame) to 1/2 V<sub>I CD</sub>.

When static duty is selected, the segment lines are not multiplexed, which means that each segment output corresponds to one pixel. In this way only up to 44 pixels can be driven. COM[0] is always active while COM[7:1] are not used and are driven to  $V_{SS}$ .

When the LCDEN bit in the LCD\_CR register is reset, all common lines are pulled down to  $V_{SS}$  and the ENS flag in the LCD\_SR register becomes 0. Static duty means that COM[0] is always active and only two voltage levels are used for the segment and common lines:  $V_{LCD}$  and  $V_{SS}$ . A pixel is active if the corresponding SEG line has a voltage opposite to that of the COM, and inactive when the voltages are equal. In this way the LCD has maximum contrast (see *Figure 119*, *Figure 120*). In the *Figure 119* pixel 0 is active while pixel 1 is inactive.

Figure 119. Static duty case 1

In each frame there is only one phase, this is why  $f_{frame}$  is equal to  $f_{LCD}$ . If 1/4 duty is selected there are four phases in a frame in which COM[0] is active during phase 0, COM[1] is active during phase 1, COM[2] is active during phase 2, and COM[3] is active during phase 3.

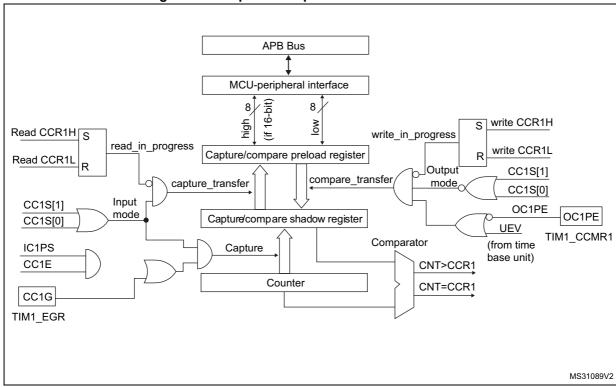

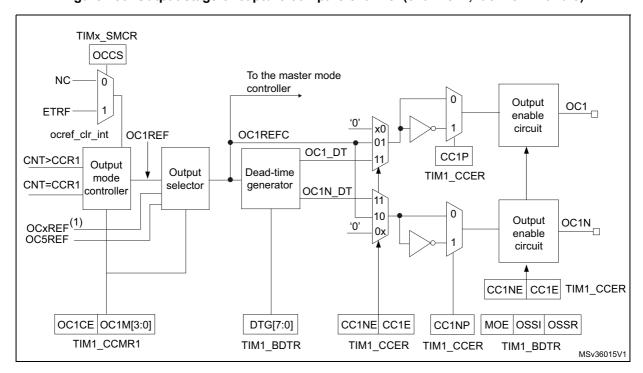

Figure 182. Capture/compare channel 1 main circuit

Figure 183. Output stage of capture/compare channel (channel 1, idem ch. 2 and 3)

1. OCxREF, where x is the rank of the complementary channel

57/

# 28.4.12 Complementary outputs and dead-time insertion

The TIM15/TIM16 general-purpose timers can output one complementary signal and manage the switching-off and switching-on of the outputs.

This time is generally known as dead-time and you have to adjust it depending on the devices you have connected to the outputs and their characteristics (intrinsic delays of level-shifters, delays due to power switches...)

You can select the polarity of the outputs (main output OCx or complementary OCxN) independently for each output. This is done by writing to the CCxP and CCxNP bits in the TIMx\_CCER register.

The complementary signals OCx and OCxN are activated by a combination of several control bits: the CCxE and CCxNE bits in the TIMx\_CCER register and the MOE, OISx, OISxN, OSSI and OSSR bits in the TIMx\_BDTR and TIMx\_CR2 registers. Refer to Table 129: Output control bits for complementary OCx and OCxN channels with break feature (TIM15) on page 885 for more details. In particular, the dead-time is activated when switching to the idle state (MOE falling down to 0).

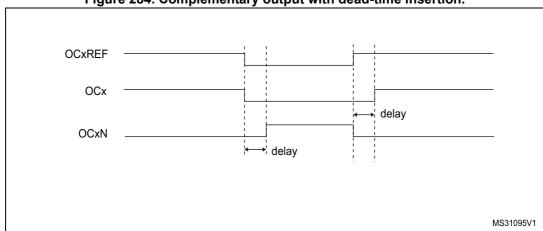

Dead-time insertion is enabled by setting both CCxE and CCxNE bits, and the MOE bit if the break circuit is present. There is one 10-bit dead-time generator for each channel. From a reference waveform OCxREF, it generates 2 outputs OCx and OCxN. If OCx and OCxN are active high:

- The OCx output signal is the same as the reference signal except for the rising edge, which is delayed relative to the reference rising edge.

- The OCxN output signal is the opposite of the reference signal except for the rising edge, which is delayed relative to the reference falling edge.

If the delay is greater than the width of the active output (OCx or OCxN) then the corresponding pulse is not generated.

The following figures show the relationships between the output signals of the dead-time generator and the reference signal OCxREF. (we suppose CCxP=0, CCxNP=0, MOE=1, CCxE=1 and CCxNE=1 in these examples)

Figure 284. Complementary output with dead-time insertion.

Real-time clock (RTC) RM0394

SUBFS[14:0] value to the synchronous prescaler counter SS[15:0]: this will delay the clock. If at the same time the ADD1S bit is set, this results in adding one second and at the same time subtracting a fraction of second, so this will advance the clock.

Caution:

Before initiating a shift operation, the user must check that SS[15] = 0 in order to ensure that no overflow will occur.

As soon as a shift operation is initiated by a write to the RTC\_SHIFTR register, the SHPF flag is set by hardware to indicate that a shift operation is pending. This bit is cleared by hardware as soon as the shift operation has completed.

Caution:

This synchronization feature is not compatible with the reference clock detection feature: firmware must not write to RTC\_SHIFTR when REFCKON=1.

### 34.3.11 RTC reference clock detection

The update of the RTC calendar can be synchronized to a reference clock, RTC\_REFIN, which is usually the mains frequency (50 or 60 Hz). The precision of the RTC\_REFIN reference clock should be higher than the 32.768 kHz LSE clock. When the RTC\_REFIN detection is enabled (REFCKON bit of RTC\_CR set to 1), the calendar is still clocked by the LSE, and RTC\_REFIN is used to compensate for the imprecision of the calendar update frequency (1 Hz).

Each 1 Hz clock edge is compared to the nearest RTC\_REFIN clock edge (if one is found within a given time window). In most cases, the two clock edges are properly aligned. When the 1 Hz clock becomes misaligned due to the imprecision of the LSE clock, the RTC shifts the 1 Hz clock a bit so that future 1 Hz clock edges are aligned. Thanks to this mechanism, the calendar becomes as precise as the reference clock.

The RTC detects if the reference clock source is present by using the 256 Hz clock (ck\_apre) generated from the 32.768 kHz quartz. The detection is performed during a time window around each of the calendar updates (every 1 s). The window equals 7 ck\_apre periods when detecting the first reference clock edge. A smaller window of 3 ck\_apre periods is used for subsequent calendar updates.

Each time the reference clock is detected in the window, the asynchronous prescaler which outputs the ck\_apre clock is forced to reload. This has no effect when the reference clock and the 1 Hz clock are aligned because the prescaler is being reloaded at the same moment. When the clocks are not aligned, the reload shifts future 1 Hz clock edges a little for them to be aligned with the reference clock.

If the reference clock halts (no reference clock edge occurred during the 3 ck\_apre window), the calendar is updated continuously based solely on the LSE clock. The RTC then waits for the reference clock using a large 7 ck\_apre period detection window centered on the ck spre edge.

When the RTC\_REFIN detection is enabled, PREDIV\_A and PREDIV\_S must be set to their default values:

- PREDIV A = 0x007F

- PREVID S = 0x00FF

Note: RTC\_REFIN clock detection is not available in Standby mode.

47/

# 34.6.4 RTC initialization and status register (RTC\_ISR)

This register is write protected (except for RTC\_ISR[13:8] bits). The write access procedure is described in *RTC register write protection on page 974*.

Address offset: 0x0C

Backup domain reset value: 0x0000 0007

System reset: not affected except INIT, INITF, and RSF bits which are cleared to '0'

| 31     | 30     | 29     | 28    | 27    | 26    | 25    | 24    | 23   | 22    | 21    | 20    | 19   | 18    | 17         | 16      |

|--------|--------|--------|-------|-------|-------|-------|-------|------|-------|-------|-------|------|-------|------------|---------|

| Res.   | Res.   | Res.   | Res.  | Res.  | Res.  | Res.  | Res.  | Res. | Res.  | Res.  | Res.  | Res. | Res.  | ITSF       | RECALPF |

|        |        |        |       |       |       |       |       |      |       |       |       |      |       | rc_w0      | r       |

| 15     | 14     | 13     | 12    | 11    | 10    | 9     | 8     | 7    | 6     | 5     | 4     | 3    | 2     | 1          | 0       |

| TAMP3F | TAMP2F | TAMP1F | TSOVF | TSF   | WUTF  | ALRBF | ALRAF | INIT | INITF | RSF   | INITS | SHPF | WUTWF | ALRB<br>WF | ALRAWF  |

| rc_w0  | rc_w0  | rc_w0  | rc_w0 | rc_w0 | rc_w0 | rc_w0 | rc_w0 | rw   | r     | rc_w0 | r     | ŗ    | r     | ŗ          | r       |

#### Bits 31:18 Reserved, must be kept at reset value

#### Bit 17 ITSF: Internal tTime-stamp flag

This flag is set by hardware when a time-stamp on the internal event occurs.

This flag is cleared by software by writing 0, and must be cleared together with TSF bit by writing 0 in both bits.

#### Bit 16 RECALPF: Recalibration pending Flag

The RECALPF status flag is automatically set to '1' when software writes to the RTC\_CALR register, indicating that the RTC\_CALR register is blocked. When the new calibration settings are taken into account, this bit returns to '0'. Refer to *Re-calibration on-the-fly*.

### Bit 15 TAMP3F: RTC\_TAMP3 detection flag

This flag is set by hardware when a tamper detection event is detected on the RTC\_TAMP3 input.

It is cleared by software writing 0

#### Bit 14 TAMP2F: RTC\_TAMP2 detection flag

This flag is set by hardware when a tamper detection event is detected on the RTC\_TAMP2 input

It is cleared by software writing 0

### Bit 13 TAMP1F: RTC\_TAMP1 detection flag

This flag is set by hardware when a tamper detection event is detected on the RTC\_TAMP1 input.

It is cleared by software writing 0

### Bit 12 TSOVF: Time-stamp overflow flag

This flag is set by hardware when a time-stamp event occurs while TSF is already set.

This flag is cleared by software by writing 0. It is recommended to check and then clear TSOVF only after clearing the TSF bit. Otherwise, an overflow might not be noticed if a time-stamp event occurs immediately before the TSF bit is cleared.

### Bit 11 TSF: Time-stamp flag

This flag is set by hardware when a time-stamp event occurs.

This flag is cleared by software by writing 0. If ITSF flag is set, TSF must be cleared together with ITSF by writing 0 in both bits.

#### SMBus Slave receiver

When the I2C is used in SMBus mode, SBC must be programmed to '1' in order to allow the PEC checking at the end of the programmed number of data bytes. In order to allow the ACK control of each byte, the reload mode must be selected (RELOAD=1). Refer to *Slave Byte Control mode on page 1027* for more details.

In order to check the PEC byte, the RELOAD bit must be cleared and the PECBYTE bit must be set. In this case, after NBYTES-1 data have been received, the next received byte is compared with the internal I2C\_PECR register content. A NACK is automatically generated if the comparison does not match, and an ACK is automatically generated if the comparison matches, whatever the ACK bit value. Once the PEC byte is received, it is copied into the I2C\_RXDR register like any other data, and the RXNE flag is set.

In the case of a PEC mismatch, the PECERR flag is set and an interrupt is generated if the ERRIE bit is set in the I2C\_CR1 register.

If no ACK software control is needed, the user can program PECBYTE=1 and, in the same write operation, program NBYTES with the number of bytes to be received in a continuous flow. After NBYTES-1 are received, the next received byte is checked as being the PEC.

**Caution:** The PECBYTE bit has no effect when the RELOAD bit is set.

- In transmission, the USART inserts the Guard Time (as programmed in the Guard Time register) between two successive characters. As the Guard Time is measured after the stop bit of the previous character, the GT[7:0] register must be programmed to the desired CGT (Character Guard Time, as defined by the 7816-3 specification) minus 12 (the duration of one character).

- The assertion of the TC flag can be delayed by programming the Guard Time register. In normal operation, TC is asserted when the transmit shift register is empty and no further transmit requests are outstanding. In Smartcard mode an empty transmit shift register triggers the Guard Time counter to count up to the programmed value in the Guard Time register. TC is forced low during this time. When the Guard Time counter reaches the programmed value TC is asserted high.

- The TCBGT flag can be used to detect the end of data transfer without waiting for guard time completion. This flag is set just after the end of frame transmission and if no NACK has been received from the card.

- The de-assertion of TC flag is unaffected by Smartcard mode.

- If a framing error is detected on the transmitter end (due to a NACK from the receiver), the NACK is not detected as a start bit by the receive block of the transmitter. According to the ISO protocol, the duration of the received NACK can be 1 or 2 baud clock periods.

- On the receiver side, if a parity error is detected and a NACK is transmitted the receiver does not detect the NACK as a start bit.

A break character is not significant in Smartcard mode. A 0x00 data with a framing error is Note: treated as data and not as a break.

> No Idle frame is transmitted when toggling the TE bit. The Idle frame (as defined for the other configurations) is not defined by the ISO protocol.

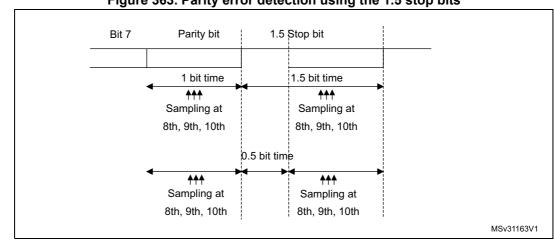

> Figure 363 details how the NACK signal is sampled by the USART. In this example the USART is transmitting data and is configured with 1.5 stop bits. The receiver part of the USART is enabled in order to check the integrity of the data and the NACK signal.

Figure 363. Parity error detection using the 1.5 stop bits

The USART can provide a clock to the smartcard through the CK output. In Smartcard mode, CK is not associated to the communication but is simply derived from the internal peripheral input clock through a 5-bit prescaler. The division ratio is configured in the prescaler register USART GTPR. CK frequency can be programmed from f<sub>Ck</sub>/2 to f<sub>Ck</sub>/62, where f<sub>CK</sub> is the peripheral input clock.

DocID027295 Rev 3

1114/1415

#### Bit 17 CMF: Character match flag

This bit is set by hardware, when the character defined by ADD[7:0] is received. It is cleared by software, writing 1 to the CMCF in the USART\_ICR register.

An interrupt is generated if CMIE=1in the USART CR1 register.

0: No Character match detected

1: Character Match detected

#### Bit 16 BUSY: Busy flag

This bit is set and reset by hardware. It is active when a communication is ongoing on the RX line (successful start bit detected). It is reset at the end of the reception (successful or not).

0: USART is idle (no reception)

1: Reception on going

#### Bit 15 ABRF: Auto baud rate flag

This bit is set by hardware when the automatic baud rate has been set (RXNE will also be set, generating an interrupt if RXNEIE = 1) or when the auto baud rate operation was completed without success (ABRE=1) (ABRE, RXNE and FE are also set in this case) It is cleared by software, in order to request a new auto baud rate detection, by writing 1 to the ABRRQ in the USART RQR register.

Note: If the USART does not support the auto baud rate feature, this bit is reserved and forced by hardware to '0'.

#### Bit 14 ABRE: Auto baud rate error

This bit is set by hardware if the baud rate measurement failed (baud rate out of range or character comparison failed)

It is cleared by software, by writing 1 to the ABRRQ bit in the USART CR3 register.

Note: If the USART does not support the auto baud rate feature, this bit is reserved and forced by hardware to '0'.

Bit 13 Reserved, must be kept at reset value.

### Bit 12 EOBF: End of block flag

This bit is set by hardware when a complete block has been received (for example T=1 Smartcard mode). The detection is done when the number of received bytes (from the start of the block, including the prologue) is equal or greater than BLEN + 4.

An interrupt is generated if the EOBIE=1 in the USART CR2 register.

It is cleared by software, writing 1 to the EOBCF in the USART\_ICR register.

0: End of Block not reached

1: End of Block (number of characters) reached

Note: If Smartcard mode is not supported, this bit is reserved and forced by hardware to '0'.

Please refer to Section 36.4: USART implementation on page 1085.

#### Character transmission procedure

- Program the M bits in LPUART\_CR1 to define the word length.

- Select the desired baud rate using the LPUART\_BRR register.

- 3. Program the number of stop bits in LPUART\_CR2.

- 4. Enable the LPUART by writing the UE bit in LPUART\_CR1 register to 1.

- 5. Select DMA enable (DMAT) in LPUART\_CR3 if multibuffer Communication is to take place. Configure the DMA register as explained in multibuffer communication.

- 6. Set the TE bit in LPUART\_CR1 to send an idle frame as first transmission.

- 7. Write the data to send in the LPUART\_TDR register (this clears the TXE bit). Repeat this for each data to be transmitted in case of single buffer.

- 8. After writing the last data into the LPUART\_TDR register, wait until TC=1. This indicates that the transmission of the last frame is complete. This is required for instance when the LPUART is disabled or enters the Halt mode to avoid corrupting the last transmission.

### Single byte communication

Clearing the TXE bit is always performed by a write to the transmit data register.

The TXE bit is set by hardware and it indicates:

- The data has been moved from the LPUART\_TDR register to the shift register and the data transmission has started.

- The LPUART\_TDR register is empty.

- The next data can be written in the LPUART\_TDR register without overwriting the previous data.

This flag generates an interrupt if the TXEIE bit is set.

When a transmission is taking place, a write instruction to the LPUART\_TDR register stores the data in the TDR register; next, the data is copied in the shift register at the end of the currently ongoing transmission.

When no transmission is taking place, a write instruction to the LPUART\_TDR register places the data in the shift register, the data transmission starts, and the TXE bit is set.

If a frame is transmitted (after the stop bit) and the TXE bit is set, the TC bit goes high. An interrupt is generated if the TCIE bit is set in the LPUART\_CR1 register.

After writing the last data in the LPUART\_TDR register, it is mandatory to wait for TC=1 before disabling the LPUART or causing the microcontroller to enter the low-power mode (see *Figure 350: TC/TXE behavior when transmitting*).

## Framing error

A framing error is detected when the stop bit is not recognized on reception at the expected time, following either a de-synchronization or excessive noise.

When the framing error is detected:

- The FE bit is set by hardware.

- The invalid data is transferred from the Shift register to the LPUART\_RDR register.

- No interrupt is generated in case of single byte communication. However this bit rises

at the same time as the RXNE bit which itself generates an interrupt. In case of

multibuffer communication an interrupt will be issued if the EIE bit is set in the

LPUART\_CR3 register.

The FE bit is reset by writing 1 to the FECF in the LPUART\_ICR register.

## Configurable stop bits during reception

The number of stop bits to be received can be configured through the control bits of Control Register 2 - it can be either 1 or 2 in normal mode.

- 1 stop bit: Sampling for 1 stop Bit is done on the 8th, 9th and 10th samples.

- **2 stop bits**: Sampling for the 2 stop bits is done in the middle of the second stop bit. The RXNE and FE flags are set just after this sample i.e. during the second stop bit. The first stop bit is not checked for framing error.

# 37.4.4 LPUART baud rate generation

The baud rate for the receiver and transmitter (Rx and Tx) are both set to the same value as programmed in the LPUART BRR register.

The baud rate for the receiver and transmitter (Rx and Tx) are both set to the same value as programmed in the LPUART BRR register.

$$Tx/Rx \text{ baud } = \frac{256 \times f_{CK}}{LPUARTDIV}$$

LPUARTDIV is coded on the LPUART\_BRR register.

Note:

The baud counters are updated to the new value in the baud registers after a write operation to LPUART\_BRR. Hence the baud rate register value should not be changed during communication.

It is forbidden to write values less than 0x300 in the LPUART\_BRR register.

fck must be in the range [3 x baud rate, 4096 x baud rate].

The maximum baud rate that can be reached when the LPUART clock source is the LSE, is 9600 baud. Higher baud rates can be reached when the LPUART is clocked by clock sources different than the LSE clock. For example, if the LPUART clock source is the system clock (maximum is 80 MHz), the maximum baud rate that can be reached is 26 Mbaud.

5//

In order to work with n reception buffers in RAM, the DMA channel or stream must be configured in following mode (refer to DMA section):

- memory to memory mode disabled,

- memory increment mode enabled,

- · memory size set to 32-bit,

- peripheral size set to 32-bit,

- peripheral increment mode disabled.

- circular mode enabled,

- data transfer direction set to read from peripheral,

- the number of words to be transferred must be set to 8 x n (8 words per buffer),

- the source address is the SWPMI\_TDR register,

- the destination address is the buffer1 address in RAM

#### Then the user must:

- Set RXDMA in the SWPMI\_CR register

- 2. Set RXBFIE in the SWPMI\_IER register

- 3. Enable stream or channel in the DMA module.

In the SWPMI interrupt routine, the user must check RXBFF in the SWPMI\_ISR register. If it is set, the user must set CRXBFF bit in the SWPMI\_ICR register to clear RXBFF flag and the user can read the first frame payload received in the first buffer (at the RAM address set in DMA2 CMAR1).

The number of data bytes in the payload is available in bits [23:16] of the last 8th word.

In the next SWPMI interrupt routine occurrence, the user will read the second frame received in the second buffer (address set in DMA2\_CMAR1 + 8), and so on (refer to Figure 425: SWPMI Multi software buffer mode reception).

In case the application software cannot ensure to handle the SMPMI interrupt before the next frame reception, each buffer status is available in the most significant byte of the 8th buffer word:

- The CRC error flag (equivalent to RXBERF flag in the SWPMI\_ISR register) is available in bit 24 of the 8th word. Refer to Section 40.3.9: Error management for an CRC error description.

- The receive overrun flag (equivalent to RXOVRF flag in the SWPMI\_ISR register) is available in bit 25 of the 8th word. Refer to Section 40.3.9: Error management for an overrun error description.

- The receive buffer full flag (equivalent to RXBFF flag in the SWPMI\_ISR register) is available in bit 26 of the 8th word.

In case of a CRC error, both RXBFF and RXBERF flags are set, thus bit 24 and bit 26 are set.

In case of an overrun, an overrun flag is set, thus bit 25 is set. The receive buffer full flag is set only in case of an overrun during the last word reception; then, both bit 25 and bit 26 are set for the current and the next frame reception.

The software can also read the DMA counter (number of data to transfer) in the DMA registers in order to retrieve the frame which has already been received and transferred into the RAM memory through DMA. For example, if the software works with 4 reception buffers,

Table 216. Block-oriented write protection commands

| CMD<br>index | Туре   | Argument                                | Response format | Abbreviation    | Description                                                                                                                                                                                         |

|--------------|--------|-----------------------------------------|-----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD28        | ac     | [31:0] data<br>address                  | R1b             | SET_WRITE_PROT  | If the card has write protection features, this command sets the write protection bit of the addressed group. The properties of write protection are coded in the card-specific data (WP_GRP_SIZE). |

| CMD29        | ac     | [31:0] data<br>address                  | R1b             | CLR_WRITE_PROT  | If the card provides write protection features, this command clears the write protection bit of the addressed group.                                                                                |

| CMD30        | adtc   | [31:0] write<br>protect data<br>address | R1              | SEND_WRITE_PROT | If the card provides write protection features, this command asks the card to send the status of the write protection bits.                                                                         |

| CMD31        | Reserv | ed                                      |                 | •               |                                                                                                                                                                                                     |

# Table 217. Erase commands

| CMD<br>index       | Туре | Argument                                      | Response format | Abbreviation               | Description                                                                                  |  |  |  |  |

|--------------------|------|-----------------------------------------------|-----------------|----------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|

| CMD32<br><br>CMD34 |      | ved. These command                            |                 | ot be used in order to mai | ntain backward compatibility with older                                                      |  |  |  |  |

| CMD35              | ac   | [31:0] data address                           | R1              | ERASE_GROUP_START          | Sets the address of the first erase group within a range to be selected for erase.           |  |  |  |  |

| CMD36              | ac   | [31:0] data address                           | R1              | ERASE_GROUP_END            | Sets the address of the last erase group within a continuous range to be selected for erase. |  |  |  |  |

| CMD37              |      | ved. This command in<br>ns of the MultiMediaC |                 | e used in order to maintai | in backward compatibility with older                                                         |  |  |  |  |

| CMD38              | ac   | [31:0] stuff bits                             | R1              | ERASE                      | Erases all previously selected write blocks.                                                 |  |  |  |  |

# Table 218. I/O mode commands

| CMD<br>index | Туре | Argument                                                                                           | Response format | Abbreviation | Description                                                                                                                                                                                                                                                                                                                             |

|--------------|------|----------------------------------------------------------------------------------------------------|-----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD39        | ac   | [31:16] RCA<br>[15:15] register<br>write flag<br>[14:8] register<br>address<br>[7:0] register data | R4              | FAST_IO      | Used to write and read 8-bit (register) data fields. The command addresses a card and a register and provides the data for writing if the write flag is set. The R4 response contains data read from the addressed register. This command accesses application-dependent registers that are not defined in the MultiMediaCard standard. |

# 41.8.16 SDMMC register map

The following table summarizes the SDMMC registers.

Table 229. SDMMC register map

| Offset | Dominton          |      |      |      | ~    |      | <b>~</b> |      | _    | _    |      |      |      |      | ~    |      | <b>~</b> |      | _       | <u>.</u> |        |                 |        |          |         |          |             |                        |        |          |                                                                                                                 |         | ٦          |

|--------|-------------------|------|------|------|------|------|----------|------|------|------|------|------|------|------|------|------|----------|------|---------|----------|--------|-----------------|--------|----------|---------|----------|-------------|------------------------|--------|----------|-----------------------------------------------------------------------------------------------------------------|---------|------------|

| Oliset | Register          | 31   | 30   | 56   | 28   | 2    | 56       | 2    | 7    | 2    | 2    | 21   | 7    | 19   | 18   | 17   | 16       | 15   | 14      | 13       | 12     | 11              | 10     | 6        | 8       | 7        | 9           | 2                      | 4      | 3        | 7                                                                                                               | 7       | 2          |

| 0x00   | SDMMC_<br>POWER   | Res. | Res. | Res. | Res. | Res. | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res.     | Res. | Res.    | Res.     | Res.   | Res.            | Res.   | Res.     | Res.    | Res.     | Res.        | Res.                   | Res.   | Res.     | Res.                                                                                                            | PWRCTRL |            |

|        | Reset value       |      |      |      |      |      |          |      |      |      |      |      |      |      |      |      |          |      |         |          |        |                 |        |          |         |          |             |                        |        |          |                                                                                                                 | 0 (     | )          |

| 0x04   | SDMMC_<br>CLKCR   | Res. | Res. | Res. | Res. | Res. | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res.     | Res. | HWFC_EN | NEGEDGE  | SHBUIM |                 | BYPASS | PWRSAV   | CLKEN   |          |             |                        | אוטאוט |          |                                                                                                                 |         |            |

|        | Reset value       |      |      |      |      |      |          |      |      |      |      |      |      |      |      |      |          |      | 0       | 0        | 0      | 0               | 0      | 0        | 0       | 0        | 0           | 0                      | 0      | 0        | 0                                                                                                               | 0 (     | )          |

| 0x08   | SDMMC_ARG         |      |      |      |      |      |          |      |      |      |      |      |      |      |      | _    | CME      |      |         |          |        |                 |        |          |         |          |             |                        |        |          |                                                                                                                 |         |            |

|        | Reset value       | 0    | 0    | 0    | 0    | 0    | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0        | 0    | 0       | 0        | 0      | 0               | 0      | 0        | 0       | 0        | 0           | 0                      | 0      | 0        | 0                                                                                                               | 0 (     | 0          |

| 0x0C   | SDMMC_CMD         | Res. | Res. | Res. | Res. | Res. | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res.     | Res. | Res.    | Res.     | Res.   | SDIOSuspend     | CPSMEN | WAITPEND | WAITINT | ON TOPIC |             |                        |        | CMOINDEX | ָבְיבְּיבְיבִּיבְיבִּיבְיבִּיבְיבִּיבְיבִּיבְיבִּיבְיבִּיבִּיבִיבְיבִּיבְיבִּיבִיבְיבִּיבְיבִּיבְיבִּיבְיבִיבְי |         |            |

|        | Reset value       |      |      |      |      |      |          |      |      |      |      |      |      |      |      |      |          |      |         |          |        | 0               | 0      | 0        | 0       | 0        | 0           | 0                      | 0      | 0        | 0                                                                                                               | 0 (     | )          |

| 0x10   | SDMMC_<br>RESPCMD | Res. | Res. | Res. | Res. | Res. | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res.     | Res. | Res.    | Res.     | Res.   | Res.            | Res.   | Res.     | Res.    | Res.     | Res.        |                        | R      | ESF      | PCM                                                                                                             | ıD      |            |

|        | Reset value       |      |      |      |      |      |          |      |      |      |      |      |      |      |      |      |          |      |         |          |        |                 |        |          |         |          |             | 0                      | 0      | 0        | 0                                                                                                               | 0 (     | )          |

| 0x14   | SDMMC_<br>RESP1   |      |      |      |      |      |          |      |      |      |      |      |      |      |      | CAI  | RDS      | TAT  | rus     | 1        |        |                 |        |          |         |          |             |                        |        |          |                                                                                                                 |         |            |

|        | Reset value       | 0    | 0    | 0    | 0    | 0    | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0        | 0    | 0       | 0        | 0      | 0               | 0      | 0        | 0       | 0        | 0           | 0                      | 0      | 0        | 0                                                                                                               | 0 (     | )          |

| 0x18   | SDMMC_<br>RESP2   |      |      |      |      |      |          |      |      |      |      |      |      |      |      | CAI  | RDS      | TAT  | rus     | 2        |        |                 |        |          |         |          |             |                        |        |          |                                                                                                                 |         |            |

|        | Reset value       | 0    | 0    | 0    | 0    | 0    | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0        | 0    | 0       | 0        | 0      | 0               | 0      | 0        | 0       | 0        | 0           | 0                      | 0      | 0        | 0                                                                                                               | 0 (     | )          |

| 0x1C   | SDMMC_<br>RESP3   |      |      |      |      |      |          |      |      |      |      |      |      |      |      | CAI  | RDS      | TAT  | rus     | 3        |        |                 |        |          |         |          |             |                        |        |          |                                                                                                                 |         |            |

|        | Reset value       | 0    | 0    | 0    | 0    | 0    | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0        | 0    | 0       | 0        | 0      | 0               | 0      | 0        | 0       | 0        | 0           | 0                      | 0      | 0        | 0                                                                                                               | 0 (     | )          |

| 0x20   | SDMMC_<br>RESP4   |      | -    | •    | •    | •    | -        | -    | -    | -    | -    | •    | •    | •    | •    | CAI  | RDS      | TAT  | rus     | 4        |        |                 |        | •        | •       | -        |             | -                      |        | -        |                                                                                                                 |         |            |

|        | Reset value       | 0    | 0    | 0    | 0    | 0    | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0        | 0    | 0       | 0        | 0      | 0               | 0      | 0        | 0       | 0        | 0           | 0                      | 0      | 0        | 0                                                                                                               | 0 (     | )          |

| 0x24   | SDMMC_<br>DTIMER  |      |      |      |      |      |          |      |      |      |      |      |      |      |      |      | DATA     | ATIN | ΛE      |          |        |                 |        |          |         |          |             |                        |        |          |                                                                                                                 |         |            |

|        | Reset value       | 0    | 0    | 0    | 0    | 0    | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0        | 0    | 0       | 0        | 0      | 0               | 0      | 0        | 0       | 0        | 0           | 0                      | 0      | 0        | 0                                                                                                               | 0 (     | )          |

| 0x28   | SDMMC_<br>DLEN    | Res. | Res. | Res. | Res. | Res. | Res.     | Res. |      |      |      |      |      |      |      |      |          |      | D       | ATA      | LEN    | IGT             | Н      |          |         |          |             |                        |        |          |                                                                                                                 |         |            |

|        | Reset value       |      |      |      |      |      |          |      | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0        | 0    | 0       | 0        | 0      | 0               | 0      | 0        | 0       | 0        | 0           | 0                      | 0      | 0        | 0                                                                                                               | 0 (     | 0          |

| 0x2C   | SDMMC_<br>DCTRL   | Res. | Res. | Res. | Res. | Res. | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res.     | Res. | Res.    | Res.     | Res.   | SDIOEN          | RWMOD  | RWSTOP   | RWSTART |          | DRI OCKSIZE | ZECONOIZE<br>TECONOIZE |        | DMAEN    | DTMODE                                                                                                          | DTDIR   | ָהַ<br>הַי |

|        | Reset value       |      |      |      |      |      |          |      |      |      |      |      |      |      |      |      |          |      |         |          |        | 0               | 0      | 0        | 0       | 0        | 0           | 0                      | 0      | 0        | 0                                                                                                               | 0 (     | 0          |

| 0x30   | SDMMC_<br>DCOUNT  | Res. | Res. | Res. | Res. | Res. | Res.     | Res. |      |      |      |      |      |      |      |      |          |      |         | )ATA     | ACO    | UN <sup>-</sup> | Т      |          |         |          |             |                        |        |          |                                                                                                                 | •       |            |

|        | Reset value       |      |      |      |      |      |          |      | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0        | 0    | 0       | 0        | 0      | 0               | 0      | 0        | 0       | 0        | 0           | 0                      | 0      | 0        | 0                                                                                                               | 0 (     | )          |

#### Bit 4 SLAKI: Sleep acknowledge interrupt

When SLKIE=1, this bit is set by hardware to signal that the bxCAN has entered Sleep Mode. When set, this bit generates a status change interrupt if the SLKIE bit in the CAN\_IER register is set.

This bit is cleared by software or by hardware, when SLAK is cleared.

Note: When SLKIE=0, no polling on SLAKI is possible. In this case the SLAK bit can be polled

### Bit 3 WKUI: Wakeup interrupt

This bit is set by hardware to signal that a SOF bit has been detected while the CAN hardware was in Sleep mode. Setting this bit generates a status change interrupt if the WKUIE bit in the CAN\_IER register is set.

This bit is cleared by software.

#### Bit 2 **ERRI**: Error interrupt

This bit is set by hardware when a bit of the CAN\_ESR has been set on error detection and the corresponding interrupt in the CAN\_IER is enabled. Setting this bit generates a status change interrupt if the ERRIE bit in the CAN\_IER register is set.

This bit is cleared by software.

#### Bit 1 SLAK: Sleep acknowledge

This bit is set by hardware and indicates to the software that the CAN hardware is now in Sleep mode. This bit acknowledges the Sleep mode request from the software (set SLEEP bit in CAN MCR register).

This bit is cleared by hardware when the CAN hardware has left Sleep mode (to be synchronized on the CAN bus). To be synchronized the hardware has to monitor a sequence of 11 consecutive recessive bits on the CAN RX signal.

Note: The process of leaving Sleep mode is triggered when the SLEEP bit in the CAN\_MCR register is cleared. Refer to the AWUM bit of the CAN\_MCR register description for detailed information for clearing SLEEP bit

#### Bit 0 INAK: Initialization acknowledge

This bit is set by hardware and indicates to the software that the CAN hardware is now in initialization mode. This bit acknowledges the initialization request from the software (set INRQ bit in CAN MCR register).

This bit is cleared by hardware when the CAN hardware has left the initialization mode (to be synchronized on the CAN bus). To be synchronized the hardware has to monitor a sequence of 11 consecutive recessive bits on the CAN RX signal.

### CAN transmit status register (CAN\_TSR)

Address offset: 0x08 Reset value: 0x1C00 0000

| 31    | 30   | 29   | 28   | 27    | 26    | 25    | 24     | 23    | 22   | 21   | 20   | 19    | 18    | 17    | 16    |

|-------|------|------|------|-------|-------|-------|--------|-------|------|------|------|-------|-------|-------|-------|

| LOW2  | LOW1 | LOW0 | TME2 | TME1  | TME0  | COD   | E[1:0] | ABRQ2 | Res. | Res. | Res. | TERR2 | ALST2 | TXOK2 | RQCP2 |

| r     | r    | r    | r    | r     | ŗ     | r     | r r    |       |      |      |      | rc_w1 | rc_w1 | rc_w1 | rc_w1 |

| 15    | 14   | 13   | 12   | 11    | 10    | 9     | 8      | 7     | 6    | 5    | 4    | 3     | 2     | 1     | 0     |

| ABRQ1 | Res. | Res. | Res. | TERR1 | ALST1 | TXOK1 | RQCP1  | ABRQ0 | Res. | Res. | Res. | TERR0 | ALST0 | TXOK0 | RQCP0 |

|       |      |      |      |       |       |       |        |       |      |      |      |       |       |       |       |