Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                 |

| Core Processor             | ARM® Cortex®-M4                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                     |

| Speed                      | 80MHz                                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                             |

| Number of I/O              | 83                                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 64K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                  |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 100-LQFP                                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l433vct6                  |

# 8.4.10 GPIO alternate function high register (GPIOx\_AFRH) (x = A..E and H)

Address offset: 0x24

Reset value: 0x0000 0000

| 31 | 30    | 29       | 28 | 27 | 26    | 25      | 24 | 23 | 22    | 21       | 20 | 19 | 18    | 17       | 16 |

|----|-------|----------|----|----|-------|---------|----|----|-------|----------|----|----|-------|----------|----|

|    | AFSEL | 15[3:0]  |    |    | AFSEL | 14[3:0] |    |    | AFSEL | .13[3:0] |    |    | AFSEL | .12[3:0] |    |

| rw | rw    | rw       | rw | rw | rw    | rw      | rw | rw | rw    | rw       | rw | rw | rw    | rw       | rw |

| 15 | 14    | 13       | 12 | 11 | 10    | 9       | 8  | 7  | 6     | 5        | 4  | 3  | 2     | 1        | 0  |

|    | AFSEL | .11[3:0] |    |    | AFSEL | 10[3:0] |    |    | AFSE  | L9[3:0]  |    |    | AFSE  | L8[3:0]  |    |

| rw | rw    | rw       | rw | rw | rw    | rw      | rw | rw | rw    | rw       | rw | rw | rw    | rw       | rw |

Bits 31:0 **AFSELy[3:0]:** Alternate function selection for port x pin y (y = 8..15)

These bits are written by software to configure alternate function I/Os

AFSELy selection:

| 0000: AF0 | 1000: AF8  |

|-----------|------------|

| 0001: AF1 | 1001: AF9  |

| 0010: AF2 | 1010: AF10 |

| 0011: AF3 | 1011: AF11 |

| 0100: AF4 | 1100: AF12 |

| 0101: AF5 | 1101: AF13 |

| 0110: AF6 | 1110: AF14 |

| 0111: AF7 | 1111: AF15 |

### 8.4.11 GPIO port bit reset register (GPIOx\_BRR) (x =A..E and H)

Address offset: 0x28 Reset value: 0x0000 0000

| 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Res. |

|      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| BR15 | BR14 | BR13 | BR12 | BR11 | BR10 | BR9  | BR8  | BR7  | BR6  | BR5  | BR4  | BR3  | BR2  | BR1  | BR0  |

Bits 31:16 Reserved

Bits 15:0 **BRy:** Port x Reset bit y (y= 0..15)

These bits are write-only. A read to these bits returns the value 0x0000

0: No action on the corresponding ODx bit

1: Reset the corresponding ODx bit

# 11.5.9 DMA register map

The following table gives the DMA register map and the reset values.

Table 44. DMA register map and reset values

| Offset | Register               | 31       | 30   | 29   | 28   | 27     | 26     | 25     | 24    | 23     | 22     | 21     | 20    | 19     | 18     | 17     | 16     | 15     | 14      | 13       | 12    | 11          | 10     | 6            | æ            | 7      | 9      | 2      | 4        | က        | 2      | 1      | 0      |

|--------|------------------------|----------|------|------|------|--------|--------|--------|-------|--------|--------|--------|-------|--------|--------|--------|--------|--------|---------|----------|-------|-------------|--------|--------------|--------------|--------|--------|--------|----------|----------|--------|--------|--------|

| 0x00   | DMA_ISR                | Res.     | Res. | Res. | Res. | TEIF7  | HTIF7  | TCIF7  | GIF7  | TEIF6  | HTIF6  | TCIF6  | GIF6  | TEIF5  | HTIF5  | TCIF5  | GIF5   | TEIF4  | HTIF4   | TCIF4    | GIF4  | TEIF3       | HTIF3  | TCIF3        | GIF3         | TEIF2  | HTIF2  | TCIF2  | GIF2     | TEIF1    | HTIF1  | TCIF1  | GIF1   |

|        | Reset value            |          |      |      |      | 0      | 0      | 0      | 0     | 0      | 0      | 0      | 0     | 0      | 0      | 0      | 0      | 0      | 0       | 0        | 0     | 0           | 0      | 0            | 0            | 0      | 0      | 0      | 0        | 0        | 0      | 0      | 0      |

| 0x04   | DMA_IFCR               | Res.     | Res. | Res. | Res. | CTEIF7 | CHTIF7 | CTCIF7 | CGIF7 | CTEIF6 | CHTIF6 | CTCIF6 | CGIF6 | CTEIF5 | CHTIF5 | CTCIF5 | CGIF5  | CTEIF4 | CHTIF4  | CTCIF4   | CGIF4 | CTEIF3      | CHTIF3 | CTCIF3       | CGIF3        | CTEIF2 | CHTIF2 | CTCIF2 | CGIF2    | CTEIF1   | CHTIF1 | CTCIF1 | CGIF1  |

|        | Reset value            |          |      |      |      | 0      | 0      | 0      | 0     | 0      | 0      | 0      | 0     | 0      | 0      | 0      | 0      | 0      | 0       | 0        | 0     | 0           | 0      | 0            | 0            | 0      | 0      | 0      | 0        | 0        | 0      | 0      | 0      |

| 0x08   | DMA_CCR1               | Res.     | Res. | Res. | Res. | Res.   | Res.   | Res.   | Res.  | Res.   | Res.   | Res.   | Res.  | Res.   | Res.   | Res.   | Res.   | Res.   | MEM2MEM | P<br>[1: |       | MSI7F [1:0] | [0:1]  | DS17E [1·01  |              | MINC   | PINC   | CIRC   | DIR      | TEIE     | HTIE   | TCIE   | EN     |

|        | Reset value            |          |      |      |      |        |        |        |       |        |        |        |       |        |        |        |        |        | 0       | 0        | 0     | 0           | 0      | 0            | 0            | 0      | 0      | 0      | 0        | 0        | 0      | 0      | 0      |

| 0x0C   | DMA_CNDTR1             | Res.     | Res. | Res. | Res. | Res.   | Res.   | Res.   | Res.  | Res.   | Res.   | Res.   | Res.  | Res.   | Res.   | Res.   | Res.   |        | ۱ ۵     | _        | 0     | 0           | _      |              | IDT          |        |        | ١.     | <u> </u> | <u> </u> | 10     | _      | 0      |

|        | Reset value            |          |      |      |      |        |        |        |       |        |        |        |       |        |        |        | 21 00  | 0      | 0       | 0        | 0     | 0           | 0      | 0            | 0            | 0      | 0      | 0      | 0        | 0        | 0      | 0      | U      |

| 0x10   | DMA_CPAR1  Reset value | 0        | 0    | 0    | 0    | 0      | 0      | 0      | 0     | 0      | 0      | 0      | 0     | 0      | 0      | 0      | PA[3   | 0      | 0       | 0        | 0     | 0           | 0      | 0            | 0            | 0      | 0      | 0      | 0        | 0        | 0      | 0      | 0      |

|        | DMA_CMAR1              | U        | U    | U    | U    | U      | U      | U      | U     | U      | U      | U      | U     | U      | U      |        | MA[    |        |         | U        | U     | U           | U      | U            | U            | U      | U      | U      | U        | U        | U      | U      | U      |

| 0x14   | Reset value            | 0        | 0    | 0    | 0    | 0      | 0      | 0      | 0     | 0      | 0      | 0      | 0     | 0      | 0      | 0      | 0      | 0      | 0       | 0        | 0     | 0           | 0      | 0            | 0            | 0      | 0      | 0      | 0        | 0        | 0      | 0      | 0      |

| 0.40   |                        | s's      | s'   | o'   | s'   | o'     | o'     | o'     | si si | si si  | s'     | si si  | o'    | o'     | có.    | S.     | S.     | si si  | s'      | S.       | S.    | S.          | S)     | o'           | o'           | o'     | o'     | o'     | s'       | o'       | ó      | S.     | o)     |

| 0x18   | Reserved               | Re       | Re   | Re   | Re   | Re     | Re     | Re     | Re    | Re     | Re     | Re     | Re    | Re     | Re     | Re     | Re     | Re     | Re      | Re       | Re    | Re          | Re     | Re           | Re           | Re     | Re     | Re     | Re       | Re       | Re     | Re     | 20     |

| 0x1C   | DMA_CCR2               | Res.     | Res. | Res. | Res. | Res.   | Res.   | Res.   | Res.  | Res.   | Res.   | Res.   | Res.  | Res.   | Res.   | Res.   | Res.   | Res.   | MEM2MEM | P<br>[1: |       | MSI7F [1-0] |        | DC17E [11.0] | r 312E [1.0] | MINC   | PINC   | CIRC   | DIR      | TEIE     | HTIE   | TCIE   | N<br>N |

|        | Reset value            |          |      |      |      |        |        |        |       |        |        |        |       |        |        |        |        |        | 0       | 0        | 0     | 0           | 0      | 0            | 0            | 0      | 0      | 0      | 0        | 0        | 0      | 0      | 0      |

| 0x20   | DMA_CNDTR2             | Res.     | Res. | Res. | Res. | Res.   | Res.   | Res.   | Res.  | Res.   | Res.   | Res.   | Res.  | Res.   | Res.   | Res.   | Res.   |        |         |          |       |             |        |              | IDT          |        | _      |        |          |          |        |        |        |

|        | Reset value            |          |      |      |      |        |        |        |       |        |        |        |       |        |        |        |        | 0      | 0       | 0        | 0     | 0           | 0      | 0            | 0            | 0      | 0      | 0      | 0        | 0        | 0      | 0      | 0      |

| 0x24   | DMA_CPAR2              |          | _    |      | _    |        |        |        |       |        |        |        |       |        |        |        | PA[3   |        | _       |          |       |             |        |              |              |        |        |        |          |          | _      |        |        |

|        | Reset value            | 0        | 0    | 0    | 0    | 0      | 0      | 0      | 0     | 0      | 0      | 0      | 0     | 0      | 0      | 0      | 0      | 0      | 0       | 0        | 0     | 0           | 0      | 0            | 0            | 0      | 0      | 0      | 0        | 0        | 0      | 0      | 0      |

| 0x28   | DMA_CMAR2              | 0        | 0    | 0    | 0    | 0      | 0      | _      | 0     | 0      | 0      | 0      | 0     | 0      | 0      | 0      | 0<br>0 | 31:0   | 0       | 0        | 0     | 0           | 0      | 0            | 0            | 0      | 0      | 0      | 0        | 0        | 0      | 0      | 0      |

|        | Reset value            | 0        |      | 0    | 0    | 0      | 0      | 0      | 0     | 0      | U C    | 0      | 0     | 0      | 0      | 0      |        | 0      | U       | 0        | 3.    |             |        | 0            | 0            | 0      | 0      |        | U C      | 0        |        |        | U.     |

| 0x2C   | Reserved               | Res      | Res  | Res  | Res  | Res    | Res    | Res    | Res   | Res    | Res    | Res    | Res   | Res    | Res    | Res    | Res    | Res    | Res     | Res      | Res   | Res         | Res    | Res          | Res          | Res    | Res    | Res    | Res      | Res      | Res    | Res    | Res    |

| 0x30   | DMA_CCR3               | Res.     | Res. | Res. | Res. | Res.   | Res.   | Res.   | Res.  | Res.   | Res.   | Res.   | Res.  | Res.   | Res.   | Res.   | Res.   | Res.   | MEM2MEM | P<br>[1: |       | MSI7F [1:0] |        | DC17E [1-0]  | r 312E [1.0] | MINC   | PINC   | CIRC   | DIR      | TEIE     | HTIE   | TCIE   | EN     |

|        | Reset value            |          |      |      |      |        |        |        |       |        |        |        |       |        |        |        |        |        | 0       | 0        | 0     | 0           | 0      | 0            | 0            | 0      | 0      | 0      | 0        | 0        | 0      | 0      | 0      |

| 0x34   | DMA_CNDTR3             | Res.     | Res. | Res. | Res. | Res.   | Res.   | Res.   | Res.  | Res.   | Res.   | Res.   | Res.  | Res.   | Res.   | Res.   | Res.   |        |         |          |       |             |        | Ν            | IDT          |        |        |        |          |          |        |        |        |

|        | Reset value            |          |      |      |      |        |        |        |       |        |        |        |       |        |        |        |        | 0      | 0       | 0        | 0     | 0           | 0      | 0            | 0            | 0      | 0      | 0      | 0        | 0        | 0      | 0      | 0      |

| 0x38   | DMA_CPAR3              |          | 1    |      |      |        |        |        |       |        |        |        |       |        |        |        | PA[3   |        |         |          |       | -           |        |              |              |        |        |        |          |          | _      |        |        |

|        | Reset value            | 0        | 0    | 0    | 0    | 0      | 0      | 0      | 0     | 0      | 0      | 0      | 0     | 0      | 0      | 0      | 0      | 0      | 0       | 0        | 0     | 0           | 0      | 0            | 0            | 0      | 0      | 0      | 0        | 0        | 0      | 0      | 0      |

| 0x3C   | DMA_CMAR3              | <u> </u> | 1.   | ء ا  | 1 -  | 1 -    | ء ا    | 1 -    | ء ا   | ٦      | ٦      | ء ا    | ء ا   | ء ا    | ١.     |        | JAN    |        |         | -        |       |             |        | ء ا          | ١.           | ۱.     | ۱.     | 1.     | ٦        | ۱.       | T-     | · ·    |        |

|        | Reset value            | 0        | 0    | 0    | 0    | 0      | 0      | 0      | 0     | 0      | 0      | 0      | 0     | 0      | 0      | 0      | 0      | 0      | 0       | 0        | 0     | 0           | 0      | 0            | 0            | 0      | 0      | 0      | 0        | 0        | 0      | 0      | 0      |

#### 13.3.3 Peripherals asynchronous Interrupts

Some peripherals are able to generate events when the system is in run mode and also when the system is in Stop mode, allowing to wake up the system from Stop mode.

To accomplish this, the peripheral generates both a synchronized (to the system clock, e.g. APB clock) and an asynchronous version of the event. This asynchronous event is connected to an EXTI direct line.

Note: Few peripherals with wakeup from Stop capability are connected to an EXTI configurable line. In this case, the EXTI configuration is necessary to allow the wakeup from Stop mode.

#### 13.3.4 Hardware interrupt selection

To configure a line as an interrupt source, use the following procedure:

- Configure the corresponding mask bit in the EXTI\_IMR register.

- Configure the Trigger Selection bits of the Interrupt line (EXTI\_RTSR and EXTI\_FTSR).

- Configure the enable and mask bits that control the NVIC IRQ channel mapped to the EXTI so that an interrupt coming from one of the EXTI lines can be correctly acknowledged.

Note: The direct lines do not require any EXTI configuration.

#### 13.3.5 Hardware event selection

To configure a line as an event source, use the following procedure:

- Configure the corresponding mask bit in the EXTL EMR register.

- 2. Configure the Trigger Selection bits of the Event line (EXTL RTSR and EXTL FTSR).

#### 13.3.6 Software interrupt/event selection

Any of the configurable lines can be configured as a software interrupt/event line. The procedure to generate a software interrupt is as follows:

- Configure the corresponding mask bit (EXTI\_IMR, EXTI\_EMR).

- Set the required bit of the software interrupt register (EXTI SWIER).

#### 13.4 **EXTI** interrupt/event line mapping

In the STM32L43xxx/44xxx/45xxx/46xxx, 38 interrupt/event lines are available. The GPIOs are connected to 16 configurable interrupt/event lines (see Figure 29).

### 15.5 QUADSPI registers

### 15.5.1 QUADSPI control register (QUADSPI\_CR)

Address offset: 0x0000

Reset value: 0x0000 0000

| 31   | 30   | 29   | 28   | 27     | 26  | 25   | 24 | 23   | 22   | 21   | 20     | 19   | 18    | 17    | 16   |

|------|------|------|------|--------|-----|------|----|------|------|------|--------|------|-------|-------|------|

|      |      |      | PRES | SCALER |     |      |    | PMM  | APMS | Res. | TOIE   | SMIE | FTIE  | TCIE  | TEIE |

| rw   | rw   | rw   | rw   | rw     | rw  | rw   | rw | rw   | rw   |      | rw     | rw   | rw    | rw    | rw   |

| 15   | 14   | 13   | 12   | 11     | 10  | 9    | 8  | 7    | 6    | 5    | 4      | 3    | 2     | 1     | 0    |

| Res. | Res. | Res. | Res. |        | FTI | HRES |    | FSEL | DFM  | Res. | SSHIFT | TCEN | DMAEN | ABORT | EN   |

|      |      |      |      | rw     | rw  | rw   | rw | rw   | rw   |      | rw     | rw   | rw    | rw    | w1s  |

#### Bits 31: 24 PRESCALER[7:0]: Clock prescaler

This field defines the scaler factor for generating CLK based on the AHB clock (value+1).

0: F<sub>CLK</sub> = F<sub>AHB</sub>, AHB clock used directly as QUADSPI CLK (prescaler bypassed)

1:  $F_{CLK} = F_{AHB}/2$

2:  $F_{CLK} = F_{AHB}/3$

..

255:  $F_{CLK} = F_{AHB}/256$

For odd clock division factors, CLK's duty cycle is not 50%. The clock signal remains low one cycle longer than it stays high.

This field can be modified only when BUSY = 0.

### Bit 23 PMM: Polling match mode

This bit indicates which method should be used for determining a "match" during automatic polling mode.

0: AND match mode. SMF is set if all the unmasked bits received from the Flash memory match the corresponding bits in the match register.

1: OR match mode. SMF is set if any one of the unmasked bits received from the Flash memory matches its corresponding bit in the match register.

This bit can be modified only when BUSY = 0.

#### Bit 22 APMS: Automatic poll mode stop

This bit determines if automatic polling is stopped after a match.

0: Automatic polling mode is stopped only by abort or by disabling the QUADSPI.

1: Automatic polling mode stops as soon as there is a match.

This bit can be modified only when BUSY = 0.

#### Bit 21 Reserved, must be kept at reset value.

#### Bit 20 TOIE: TimeOut interrupt enable

This bit enables the TimeOut interrupt.

0: Interrupt disable

1: Interrupt enabled

#### Bit 19 SMIE: Status match interrupt enable

This bit enables the status match interrupt.

0: Interrupt disable

1: Interrupt enabled

# 15.5.14 QUADSPI register map

Table 52. QUADSPI register map and reset values

|        |                         |      |          |      |      |            |          |            |      |      |      |      | ĺ    |      |      | Ė           |              |             |      |             |      |             |            |            |      |      |      |          |        |          |       |       |          |

|--------|-------------------------|------|----------|------|------|------------|----------|------------|------|------|------|------|------|------|------|-------------|--------------|-------------|------|-------------|------|-------------|------------|------------|------|------|------|----------|--------|----------|-------|-------|----------|

| Offset | Register                | 31   | 30       | 29   | 28   | 27         | 26       | 25         | 24   | 23   | 22   | 21   | 20   | 19   | 18   | 17          | 16           | 15          | 14   | 13          | 12   | 11          | 10         | 6          | œ    | 7    | 9    | 2        | 4      | က        | 7     | 1     | 0        |

| 0x0000 | QUADSPI_CR              |      | Р        | RES  | SCA  | LEI        | २[7:     | 0]         |      | PMM  | APMS | Res. | TOIE | SMIE | FTIE | TCIE        | TEIE         | Res.        | Res. | Res.        | Res. | F           | TH=<br>[3] | RES<br>:0] | S    | FSEL | DFM  | Res.     | SSHIFT | TCEN     | DMAEN | ABORT | EN       |

|        | Reset value             | 0    | 0        | 0    | 0    | 0          | 0        | 0          | 0    | 0    | 0    |      | 0    | 0    | 0    | 0           | 0            |             |      |             |      | 0           | 0          | 0          | 0    | 0    | 0    |          | 0      | 0        | 0     | 0     | 0        |

| 0x0004 | QUADSPI_DCR             | Res. | Res.     | Res. | Res. | Res.       | Res.     | Res.       | Res. | Res. | Res. | Res. |      | FSI  | ZE[  | 4:0]        |              | Res.        | Res. | Res.        | Res. | Res.        | C          | SH         | Т    | Res. | Res. | Res.     | Res.   | Res.     | Res.  | Res.  | CKMODE   |

|        | Reset value             |      |          |      |      |            |          |            |      |      |      |      | 0    | 0    | 0    | 0           | 0            |             |      |             |      |             | 0          | 0          | 0    |      |      |          |        |          |       |       | 0        |

| 0x0008 | QUADSPI_SR              | Res. | Res.     | Res. | Res. | Res.       | Res.     | Res.       | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res.        | Res.         | Res.        | Res. |             | FL   | EVI         | EL[5       | :0]        |      | Res. | Res. | BUSY     | TOF    | SMF      | FTF   | TCF   | TEF      |

|        | Reset value             |      |          |      |      |            |          |            |      |      |      |      |      |      |      |             |              |             |      | 0           | 0    | 0           | 0          | 0          | 0    |      |      | 0        | 0      | 0        | 0     | 0     | 0        |

| 0x000C | QUADSPI_FCR             | Res. | Res.     | Res. | Res. | Res.       | Res.     | Res.       | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res.        | Res.         | Res.        | Res. | Res.        | Res. | Res.        | Res.       | Res.       | Res. | Res. | Res. | Res.     | CTOF   | CSMF     | Res.  | CTCF  | CTEF     |

|        | Reset value             |      |          |      |      |            |          |            |      |      |      |      |      |      |      |             |              |             |      |             |      |             |            |            |      |      |      |          | 0      | 0        |       | 0     | 0        |

| 0x0010 | QUADSPI_DLR             |      |          |      |      |            |          |            |      |      |      |      |      |      |      |             | DL[3         | 31:0        | ]    |             |      |             |            |            |      |      |      |          |        |          |       |       |          |

| 0,0010 | Reset value             | 0    | 0        | 0    | 0    | 0          | 0        | 0          | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0           | 0            | 0           | 0    | 0           | 0    | 0           | 0          | 0          | 0    | 0    | 0    | 0        | 0      | 0        | 0     | 0     | 0        |

| 0x0014 | QUADSPI_CCR             | DDRM | DHHC     | Res. | SIOO | EMODEI1-01 | - MOCE   | DMODE[1-0] |      | Res. |      | DC   | YC[  | 4:0] |      | ABSI7E11-01 | ABSIZE[ 1.0] | ABMODEI1:01 |      | ADSIZE[1:0] |      | ADMODEI1-01 | ליין ליין  | IMODEI1-01 |      |      | IN   | STF      | RUC    | TIC      | )N[7  | :0]   |          |

|        | Reset value             | 0    | 0        |      | 0    | 0          | 0        | 0          | 0    |      | 0    | 0    | 0    | 0    | 0    | 0           | 0            | 0           | 0    | 0           | 0    | 0           | 0          | 0          | 0    | 0    | 0    | 0        | 0      | 0        | 0     | 0     | 0        |

| 0x0018 | QUADSPI_AR              |      |          |      |      |            |          |            |      |      |      |      |      |      | /    | ٩DD         | RE           | SS[         | 31:0 | )]          |      |             |            |            |      |      |      |          |        |          |       |       |          |

|        | Reset value             | 0    | 0        | 0    | 0    | 0          | 0        | 0          | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0           | 0            | 0           | 0    | 0           | 0    | 0           | 0          | 0          | 0    | 0    | 0    | 0        | 0      | 0        | 0     | 0     | 0        |

| 0x001C | QUADSPI_ABR             | _    | <u> </u> |      |      |            | <u> </u> | _          | _    | ١.   |      |      | _    |      |      |             | RN           |             | _    | _           | •    |             |            | _          | _    |      |      | <u> </u> |        | <u> </u> | _     |       |          |

|        | Reset value             | 0    | 0        | 0    | 0    | 0          | 0        | 0          | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0           | 0            | 0           | 0    | 0           | 0    | 0           | 0          | 0          | 0    | 0    | 0    | 0        | 0      | 0        | 0     | 0     | 0        |

| 0x0020 | QUADSPI_DR  Reset value | 0    | 0        | 0    | 0    | 0          | 0        | 0          | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0           | ATA<br>0     | 0           | 0    | 0           | 0    | 0           | 0          | 0          | 0    | 0    | 0    | 0        | 0      | 0        | 0     | 0     | 0        |

| 0x0024 | QUADSPI_<br>PSMKR       |      | L        | L    | L    | Ľ          | L        | L          | U    | U    | U    | Ľ    | L    | Ľ    |      |             | ASK          |             |      | L           | U    | U           | L          |            | L    | L    | L    | L        | L      | U        | L     | L     | $\dashv$ |

|        | Reset value             | 0    | 0        | 0    | 0    | 0          | 0        | 0          | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0           | 0            | 0           | 0    | 0           | 0    | 0           | 0          | 0          | 0    | 0    | 0    | 0        | 0      | 0        | 0     | 0     | 0        |

| 0x0028 | QUADSPI_<br>PSMAR       |      | •        |      | •    |            | •        |            |      | •    |      |      |      |      |      | MA          | ATC          | H[3′        | 1:0] |             |      |             |            |            |      | •    | •    | •        | •      | •        |       | •     |          |

|        | Reset value             | 0    | 0        | 0    | 0    | 0          | 0        | 0          | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0           | 0            | 0           | 0    | 0           | 0    | 0           | 0          | 0          | 0    | 0    | 0    | 0        | 0      | 0        | 0     | 0     | 0        |

| 0x002C | QUADSPI_PIR             | Res. | Res.     | Res. | Res. | Res.       | Res.     | Res.       | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res.        | Res.         |             |      |             |      |             |            |            | ERV  |      |      |          |        |          |       |       |          |

|        | Reset value             |      |          |      |      |            |          |            |      |      |      |      |      |      |      |             |              | 0           | 0    | 0           | 0    | 0           | 0          | 0          | 0    | 0    | 0    | 0        | 0      | 0        | 0     | 0     | 0        |

| 0x0030 | QUADSPI_<br>LPTR        | Res. | Res.     | Res. | Res. | Res.       | Res.     | Res.       | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res.        | Res.         |             |      |             |      |             |            |            | EOl  | JT[1 |      | -        |        |          |       |       |          |

|        | Reset value             |      |          |      |      |            |          |            |      |      |      |      |      |      |      |             |              | 0           | 0    | 0           | 0    | 0           | 0          | 0          | 0    | 0    | 0    | 0        | 0      | 0        | 0     | 0     | 0        |

Refer to Section 2.2.2 for the register boundary addresses.

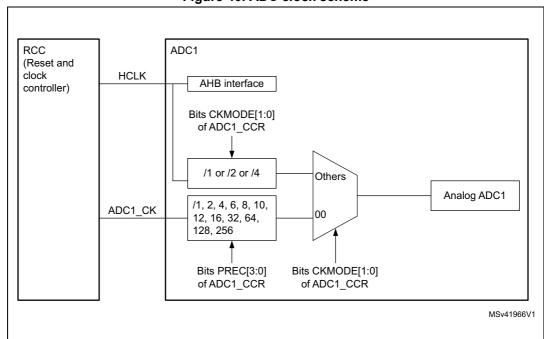

- The ADC clock can be a specific clock source. It can be derived from the following clock sources:

- The system clock

- PLLSAI1

- PLLSAI2

Refer to RCC Section for more information on how to generate ADC dedicated clock. To select this scheme, bits CKMODE[1:0] of the ADC\_CCR register must be reset.

2. The ADC clock can be derived from the AHB clock of the ADC bus interface, divided by a programmable factor (1, 2 or 4). In this mode, a programmable divider factor can be selected (/1, 2 or 4 according to bits CKMODE[1:0]).

To select this scheme, bits CKMODE[1:0] of the ADC\_CCR register must be different from "00".

Note: For option 2), a prescaling factor of 1 (CKMODE[1:0]=01) can be used only if the AHB prescaler is set to 1 (HPRE[3:0] = 0xxx in RCC\_CFGR register).

Option 1) has the advantage of reaching the maximum ADC clock frequency whatever the AHB clock scheme selected. The ADC clock can eventually be divided by the following ratio: 1, 2, 4, 6, 8, 12, 16, 32, 64, 128, 256; using the prescaler configured with bits PRESC[3:0] in the ADC\_CCR register.

Option 2) has the advantage of bypassing the clock domain resynchronizations. This can be useful when the ADC is triggered by a timer and if the application requires that the ADC is precisely triggered without any uncertainty (otherwise, an uncertainty of the trigger instant is added by the resynchronizations between the two clock domains).

Figure 40. ADC clock scheme

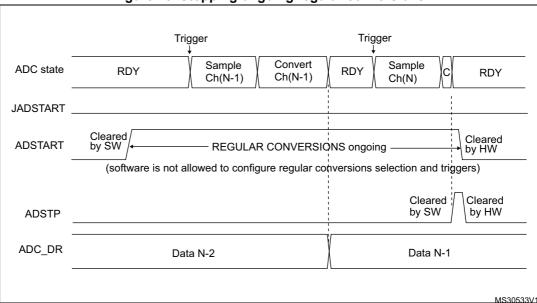

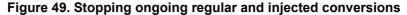

Figure 48. Stopping ongoing regular conversions

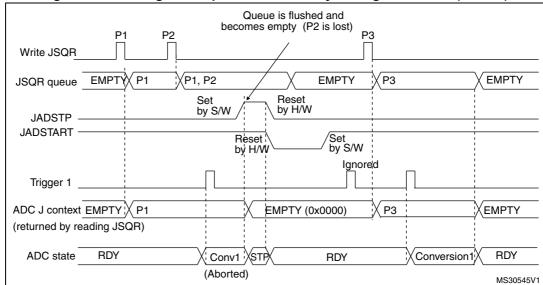

Figure 60. Flushing JSQR queue of context by setting JADSTP=1 (JQM=1)

- Parameters:

- P1: sequence of 1 conversion, hardware trigger 1

- P2: sequence of 1 conversion, hardware trigger 1 P3: sequence of 1 conversion, hardware trigger 1

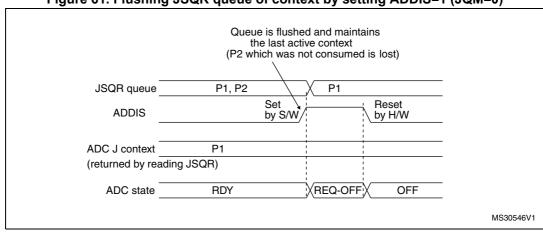

Figure 61. Flushing JSQR queue of context by setting ADDIS=1 (JQM=0)

- Parameters:

P1: sequence of 1 conversion, hardware trigger 1

P2: sequence of 1 conversion, hardware trigger 1

P3: sequence of 1 conversion, hardware trigger 1

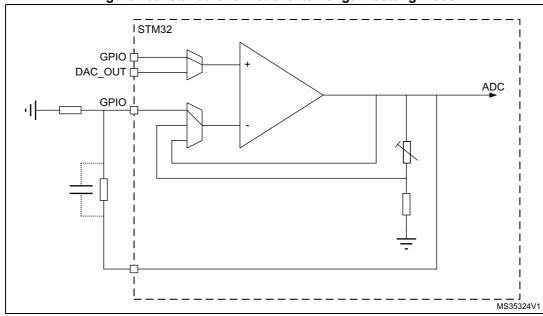

### Standalone mode (external gain setting mode)

The procedure to use the OPAMP in standalone mode is presented hereafter.

Starting from the default value of OPAMP\_CSR, and the default state of GPIOx\_MODER, configure bit OPA\_RANGE according the  $V_{DDA}$  voltage. As soon as the OPAEN bit is set, the two input pins and the output pin are connected to the operational amplifier.

This default configuration uses the factory trimming values and operates in normal mode (highest performance). The behavior of the OPAMP can be changed as follows:

- OPALPM can be set to "operational amplifier low-power" mode in order to save power.

- USERTRIM can be set to modify the trimming values for the input offset.

Figure 105. Standalone mode: external gain setting mode

#### Follower configuration mode

The procedure to use the OPAMP in follower mode is presented hereafter.

- configure OPAMODE bits as "internal follower"

- configure VP SEL bits as "GPIO connected to VINP".

- As soon as the OPAEN bit is set, the signal on pin OPAMP\_VINP is copied to pin OPAMP\_VOUT.

Note: The pin corresponding to OPAMP\_VINM is free for another usage.

The signal on the operational amplifier output is also seen as an ADC input. As a consequence, the OPAMP configured in follower mode can be used to perform impedance adaptation on input signals before feeding them to the ADC input, assuming the input signal frequency is compatible with the operational amplifier gain bandwidth specification.

Note:

Table 98. DFSDM register map and reset values (continued)

|                |                     |      |      |      |      |      |      |      |      | Ŭ           |          |      |      |      |      |      |      | - V          |      |             |      |      |      |      |         | Ĺ    |        |       |                 |               | $\neg$ |           |                                        |

|----------------|---------------------|------|------|------|------|------|------|------|------|-------------|----------|------|------|------|------|------|------|--------------|------|-------------|------|------|------|------|---------|------|--------|-------|-----------------|---------------|--------|-----------|----------------------------------------|

| Offset         | Register            | 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23          | 22       | 21   | 20   | 19   | 18   | 17   | 16   | 15           | 4    | 13          | 12   | 11   | 10   | 6    | 8       | 7    | 9      | 2     | 4               | 3             | 7      | 1         | 0                                      |

| 0x24           | DFSDM_<br>CH1CFGR2  |      |      |      |      |      |      |      |      |             |          | OF   | FSE  | T[2  | 3:0] |      |      |              |      |             |      |      |      |      |         |      | DTF    | RBS   | [4:0]           |               | Res.   | Res.      | Res.                                   |

|                | reset value         | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0           | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0            | 0    | 0           | 0    | 0    | 0    | 0    | 0       | 0    | 0      | 0     | 0               | 0             |        |           |                                        |

| 0x28           | DFSDM_<br>CH1AWSCDR | Res. | AWEORDI1-01 |          | Res. | Д    | WF   | OSI  | R[4: | 0]   | BK           | sc   | :D[3:       | 0]   | Res. | Res. | Res. | Res.    |      |        | S     | CD <sup>-</sup> | Γ[7:0         | )]     |           |                                        |

|                | reset value         |      |      |      |      |      |      |      |      | 0           | 0        |      | 0    | 0    | 0    | 0    | 0    | 0            | 0    | 0           | 0    |      |      |      |         | 0    | 0      | 0     | 0               | 0             | 0      | 0         | 0                                      |

| 0x2C           | DFSDM_<br>CH1WDATR  | Res.        | Res.     | Res. | Res. | Res. | Res. | Res. | Res. |              |      |             |      |      |      | WI   | DAT     | A[1  | 5:0]   |       |                 |               |        |           |                                        |

|                | reset value         |      |      |      |      |      |      |      |      |             |          |      |      |      |      |      | 0    | 0            | 0    | 0           | 0    | 0    | 0    | 0    | 0       | 0    | 0      | 0     | 0               | 0             | 0      | 0         | 0                                      |

| 0x30           | DFSDM_<br>CH1DATINR |      |      |      |      |      |      | INI  | DAT  | 1[15        | 5:0]     |      |      |      |      |      |      |              |      |             |      |      |      | INI  | DAT     | 0[1  | 5:0]   |       |                 |               |        |           |                                        |

|                | reset value         | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0           | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0            | 0    | 0           | 0    | 0    | 0    | 0    | 0       | 0    | 0      | 0     | 0               | 0             | 0      | 0         | 0                                      |

| 0x34 -<br>0x3C | Reserved            | Res.        | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | Res.         | Res. | Res.        | Res. | Res. | Res. | Res. | Res.    | Res. | Res.   | Res.  | Res.            | Res.          | Res.   | Res.      | Res.                                   |

| 0x40           | DFSDM_<br>CH2CFGR1  | Res.        | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | DATPACK[1:0] | •    | DATMPX[1:0] |      | Res. | Res. | Res. | CHINSEL | CHEN | CKABEN | SCDEN | Res.            | SPICKSEL[1:0] |        | SITP[1-0] | · · · · · · · · · · · · · · · · · · ·  |

|                | reset value         |      |      |      |      |      |      |      |      |             |          |      |      |      |      |      |      | 0            | 0    | 0           | 0    |      |      |      | 0       | 0    | 0      | 0     |                 | 0             | 0      | 0         | 0                                      |

| 0x44           | DFSDM_<br>CH2CFGR2  |      |      |      |      |      |      |      | l    |             |          | OF   | FSE  | T[2  | 3:0] |      |      |              |      |             |      |      |      | l    |         |      | DTF    | RBS   | [4:0]           |               | Res.   | Res.      | Res.                                   |

|                | reset value         | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0           | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0            | 0    | 0           | 0    | 0    | 0    | 0    | 0       | 0    | 0      | 0     | 0               | 0             |        |           |                                        |

| 0x48           | DFSDM_<br>CH2AWSCDR | Res. | AWEORDI1-01 | 5:-15:-5 | Res. | Α    | WF   | OSI  | R[4: | 0]   | ВК           | sc   | :D[3:       | 0]   | Res. | Res. | Res. | Res.    |      | •      | S     | CD.             | Γ[7:0         | )]     |           |                                        |

|                | reset value         |      |      |      |      |      |      |      |      | 0           | 0        |      | 0    | 0    | 0    | 0    | 0    | 0            | 0    | 0           | 0    |      |      |      |         | 0    | 0      | 0     | 0               | 0             | 0      | 0         | 0                                      |

| 0x4C           | DFSDM_<br>CH2WDATR  | Res.        | Res.     | Res. | Res. | Res. | Res. | Res. | Res. |              |      |             |      |      |      | WI   | DAT     | A[1  | 5:0]   |       |                 |               |        |           |                                        |

|                | reset value         |      |      |      |      |      |      |      |      |             |          |      |      |      |      |      |      | 0            | 0    | 0           | 0    | 0    | 0    | 0    | 0       | 0    | 0      | 0     | 0               | 0             | 0      | 0         | 0                                      |

| 0x50           | DFSDM_<br>CH2DATINR |      |      |      |      |      |      | INI  | DAT  | 1[15        | 5:0]     |      |      |      |      |      |      |              |      |             |      |      |      | INI  | DAT     | 0[1  | 5:0]   |       |                 |               |        |           |                                        |

|                | reset value         | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0           | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0            | 0    | 0           | 0    | 0    | 0    | 0    | 0       | 0    | 0      | 0     | 0               | 0             | 0      | 0         | 0                                      |

| 0x54 -<br>0x5C | Reserved            | Res.        | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | Res.         | Res. | Res.        | Res. | Res. | Res. | Res. | Res.    | Res. | Res.   | Res.  | Res.            | Res.          | Res.   | Res.      | Res.                                   |

| 0x60           | DFSDM_<br>CH3CFGR1  | Res.        | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | DATPACK[1:0] | •    | DATMPX11:01 |      | Res. | Res. | Res. | CHINSEL | CHEN | CKABEN | SCDEN | Res.            | SPICKSEL[1:0] |        | SITPI1-01 | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; |

|                | reset value         |      |      |      |      |      |      |      |      |             |          |      |      |      |      |      |      | 0            | 0    | 0           | 0    |      |      |      | 0       | 0    | 0      | 0     |                 | 0             | 0      | 0         | 0                                      |

| 0x64           | DFSDM_<br>CH3CFGR2  |      |      |      |      |      |      |      |      |             |          | OF   | FSE  | T[2  | 3:0] |      |      |              |      |             |      |      |      |      |         |      | DTF    | RBS   | [4:0]           | l             | Res.   | Res.      | Res.                                   |

|                | reset value         | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0           | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0            | 0    | 0           | 0    | 0    | 0    | 0    | 0       | 0    | 0      | 0     | 0               | 0             |        |           |                                        |

#### **Downcounting mode**

In downcounting mode, the counter counts from the auto-reload value (content of the TIMx\_ARR register) down to 0, then restarts from the auto-reload value and generates a counter underflow event.

If the repetition counter is used, the update event (UEV) is generated after downcounting is repeated for the number of times programmed in the repetition counter register (TIMx\_RCR) + 1. Else the update event is generated at each counter underflow.

Setting the UG bit in the TIMx\_EGR register (by software or by using the slave mode controller) also generates an update event.

The UEV update event can be disabled by software by setting the UDIS bit in TIMx\_CR1 register. This is to avoid updating the shadow registers while writing new values in the preload registers. Then no update event occurs until UDIS bit has been written to 0. However, the counter restarts from the current auto-reload value, whereas the counter of the prescaler restarts from 0 (but the prescale rate doesn't change).

In addition, if the URS bit (update request selection) in TIMx\_CR1 register is set, setting the UG bit generates an update event UEV but without setting the UIF flag (thus no interrupt or DMA request is sent). This is to avoid generating both update and capture interrupts when clearing the counter on the capture event.

When an update event occurs, all the registers are updated and the update flag (UIF bit in TIMx SR register) is set (depending on the URS bit):

- The repetition counter is reloaded with the content of TIMx\_RCR register.

- The buffer of the prescaler is reloaded with the preload value (content of the TIMx\_PSC register).

- The auto-reload active register is updated with the preload value (content of the TIMx\_ARR register). Note that the auto-reload is updated before the counter is reloaded, so that the next period is the expected one.

The following figures show some examples of the counter behavior for different clock frequencies when TIMx\_ARR=0x36.

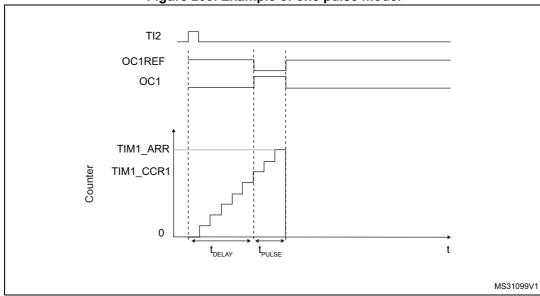

### 26.3.20 One-pulse mode

One-pulse mode (OPM) is a particular case of the previous modes. It allows the counter to be started in response to a stimulus and to generate a pulse with a programmable length after a programmable delay.

Starting the counter can be controlled through the slave mode controller. Generating the waveform can be done in output compare mode or PWM mode. You select One-pulse mode by setting the OPM bit in the TIMx\_CR1 register. This makes the counter stop automatically at the next update event UEV.

A pulse can be correctly generated only if the compare value is different from the counter initial value. Before starting (when the timer is waiting for the trigger), the configuration must be:

- In upcounting: CNT < CCRx ≤ ARR (in particular, 0 < CCRx)</li>

- In downcounting: CNT > CCRx

Figure 203. Example of one pulse mode.

For example you may want to generate a positive pulse on OC1 with a length of t<sub>PULSE</sub> and after a delay of t<sub>DELAY</sub> as soon as a positive edge is detected on the TI2 input pin.

Let's use TI2FP2 as trigger 1:

- Map TI2FP2 to TI2 by writing CC2S='01' in the TIMx\_CCMR1 register.

- TI2FP2 must detect a rising edge, write CC2P='0' and CC2NP='0' in the TIMx\_CCER register.

- Configure TI2FP2 as trigger for the slave mode controller (TRGI) by writing TS=110 in the TIMx\_SMCR register.

- TI2FP2 is used to start the counter by writing SMS to '110' in the TIMx\_SMCR register (trigger mode).

Real-time clock (RTC) RM0394

Note:

When the RTC\_CALIB or RTC\_ALARM output is selected, the RTC\_OUT pin is automatically configured as output.

When COSEL bit is cleared, the RTC\_CALIB output is the output of the 6th stage of the asynchronous prescaler.

When COSEL bit is set, the RTC\_CALIB output is the output of the 8th stage of the synchronous prescaler.

### 34.3.16 Alarm output

The OSEL[1:0] control bits in the RTC\_CR register are used to activate the alarm output RTC\_ALARM, and to select the function which is output. These functions reflect the contents of the corresponding flags in the RTC\_ISR register.

The polarity of the output is determined by the POL control bit in RTC\_CR so that the opposite of the selected flag bit is output when POL is set to 1.

#### **Alarm output**

The RTC\_ALARM pin can be configured in output open drain or output push-pull using the control bit RTC\_ALARM\_TYPE in the RTC\_OR register.

Note:

Once the RTC\_ALARM output is enabled, it has priority over RTC\_CALIB (COE bit is don't care and must be kept cleared).

When the RTC\_CALIB or RTC\_ALARM output is selected, the RTC\_OUT pin is automatically configured as output.

### 34.4 RTC low-power modes

Table 145. Effect of low-power modes on RTC

| Mode            | Description                                                                                                                                                                 |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sleep           | No effect RTC interrupts cause the device to exit the Sleep mode.                                                                                                           |

| Low-power run   | No effect.                                                                                                                                                                  |

| Low-power sleep | No effect. RTC interrupts cause the device to exit the Low-power sleep mode.                                                                                                |

| Stop 0          |                                                                                                                                                                             |

| Stop 1          | Peripheral registers content is kept.                                                                                                                                       |

| Stop 2          |                                                                                                                                                                             |

| Standby         | The RTC remains active when the RTC clock source is LSE or LSI. RTC alarm, RTC tamper event, RTC timestamp event, and RTC Wakeup cause the device to exit the Standby mode. |

| Shutdown        | The RTC remains active when the RTC clock source is LSE. RTC alarm, RTC tamper event, RTC timestamp event, and RTC Wakeup cause the device to exit the Shutdown mode.       |

### 36.4 USART implementation

The STM32L43xxx/44xxx/45xxx/46xxx devices embed up to 4 USARTs and 1 LPUART. The *Table 164* describes the features supported by each peripheral (see also *Table 1: Product specific features*).

USART modes/features(1) **USART1 USART2 USART3** UART4 LPUART1 Hardware flow control for modem Х Х Χ Х Х Х Χ Х Х Х Continuous communication using DMA Х Х Χ Х Χ Multiprocessor communication Χ Χ Χ Synchronous mode -Х Х Χ Smartcard mode Single-wire Half-duplex communication Х Χ Χ Χ Х IrDA SIR ENDEC block Х Χ Χ Χ LIN mode Χ Χ Χ Χ Χ Х Dual clock domain and wakeup from Stop mode Х Х Х Receiver timeout interrupt Χ Χ Χ Χ Χ Х Χ Modbus communication Х Auto baud rate detection X (4 modes) **Driver Enable** Х Χ Χ Χ LPUART/USART/UART data length 7. 8 and 9 bits

Table 164. STM32L43xxx/44xxx/45xxx/46xxx USART/LPUART features

## 36.5 USART functional description

Any USART bidirectional communication requires a minimum of two pins: Receive data In (RX) and Transmit data Out (TX):

• **RX**: Receive data Input.

This is the serial data input. Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

• **TX:** Transmit data Output.

When the transmitter is disabled, the output pin returns to its I/O port configuration. When the transmitter is enabled and nothing is to be transmitted, the TX pin is at high level. In Single-wire and Smartcard modes, this I/O is used to transmit and receive the data.

<sup>1.</sup> X = supported.

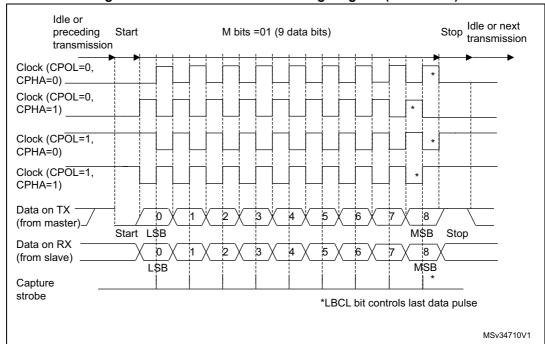

Figure 360. USART data clock timing diagram (M bits = 01)

Note:

The function of CK is different in Smartcard mode. Refer to Section 36.5.13: USART Smartcard mode for more details.

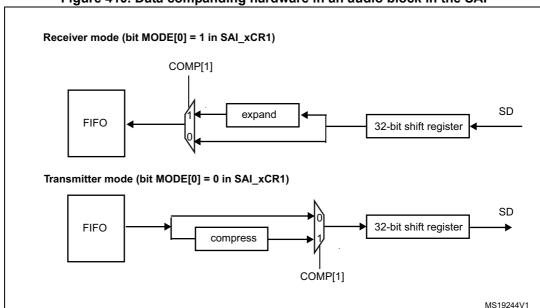

input line (expansion) as illustrated in *Figure 410*. The two companding modes supported are the  $\mu$ -Law and the A-Law log which are a part of the CCITT G.711 recommendation.

The companding standard used in the United States and Japan is the  $\mu$ -Law. It supports 14 bits of dynamic range (COMP[1:0] = 10 in the SAI\_xCR2 register).

The European companding standard is A-Law and supports 13 bits of dynamic range (COMP[1:0] = 11 in the SAI\_xCR2 register).

Both  $\mu$ -Law or A-Law companding standard can be computed based on 1's complement or 2's complement representation depending on the CPL bit setting in the SAI\_xCR2 register.

In  $\mu$ -Law and A-Law standards, data are coded as 8 bits with MSB alignment. Companded data are always 8-bit wide. For this reason, DS[2:0] bits in the SAI\_xCR1 register will be forced to 010 when the SAI audio block is enabled (bit SAIXEN = 1 in the SAI\_xCR1 register) and when one of these two companding modes selected through the COMP[1:0] bits.

If no companding processing is required, COMP[1:0] bits should be kept clear.

Figure 410. Data companding hardware in an audio block in the SAI

1. Not applicable when AC'97 or SPDIF are selected.

Expansion and compression mode are automatically selected through the SAI xCR2:

- If the SAI audio block is configured to be a transmitter, and if the COMP[1] bit is set in the SAI\_xCR2 register, the compression mode will be applied.

- If the SAI audio block is declared as a receiver, the expansion algorithm will be applied.

### Output data line management on an inactive slot

In transmitter mode, it is possible to choose the behavior of the SD line output when an inactive slot is sent on the data line (via TRIS bit).

- Either the SAI forces 0 on the SD output line when an inactive slot is transmitted, or

- The line is released in HI-z state at the end of the last bit of data transferred, to release the line for other transmitters connected to this node.

The behavior is to stop SDMMC\_CK and freeze SDMMC state machines. The data transfer is stalled while the FIFO is unable to transmit or receive data. Only state machines clocked by SDMMCCLK are frozen, the APB2 interface is still alive. The FIFO can thus be filled or emptied even if flow control is activated.

To enable HW flow control, the SDMMC\_CLKCR[14] register bit must be set to 1. After reset Flow Control is disabled.

### 41.8 SDMMC registers

The device communicates to the system via 32-bit-wide control registers accessible via APB2.

### 41.8.1 SDMMC power control register (SDMMC POWER)

Address offset: 0x00

Reset value: 0x0000 0000

| 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Res. |

|      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| Res. | D    | D    | D    | D    |      |      |      |      |      |      |      |      | _    |      |      |

| Res. | PWR  | CTRL |

Bits 31:2 Reserved, must be kept at reset value.

[1:0] **PWRCTRL:** Power supply control bits.

These bits are used to define the current functional state of the card clock:

00: Power-off: the clock to card is stopped.

01: Reserved

10: Reserved power-up

11: Power-on: the card is clocked.

Note: At least seven PCLK2 clock periods are needed between two write accesses to this register.

Note: After a data write, data cannot be written to this register for three SDMMCCLK clock periods plus two PCLK2 clock periods.

### 41.8.2 SDMMC clock control register (SDMMC\_CLKCR)

Address offset: 0x04

Reset value: 0x0000 0000

The SDMMC CLKCR register controls the SDMMC CK output clock.

This mode is very useful for segmented transmission.

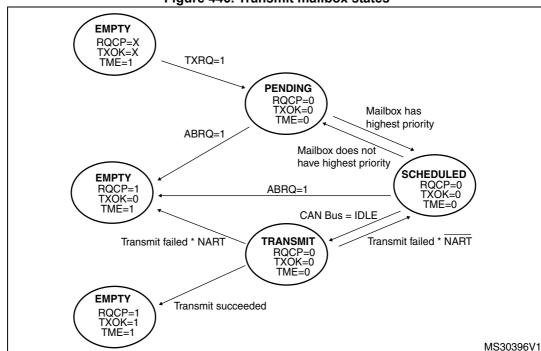

#### **Abort**

A transmission request can be aborted by the user setting the ABRQ bit in the CAN\_TSR register. In **pending** or **scheduled** state, the mailbox is aborted immediately. An abort request while the mailbox is in **transmit** state can have two results. If the mailbox is transmitted successfully the mailbox becomes **empty** with the TXOK bit set in the CAN\_TSR register. If the transmission fails, the mailbox becomes **scheduled**, the transmission is aborted and becomes **empty** with TXOK cleared. In all cases the mailbox will become **empty** again at least at the end of the current transmission.

#### Non automatic retransmission mode

This mode has been implemented in order to fulfill the requirement of the Time Triggered Communication option of the CAN standard. To configure the hardware in this mode the NART bit in the CAN MCR register must be set.

In this mode, each transmission is started only once. If the first attempt fails, due to an arbitration loss or an error, the hardware will not automatically restart the message transmission.

At the end of the first transmission attempt, the hardware considers the request as completed and sets the RQCP bit in the CAN\_TSR register. The result of the transmission is indicated in the CAN\_TSR register by the TXOK, ALST and TERR bits.

Figure 446. Transmit mailbox states

### 42.7.2 Time triggered communication mode

In this mode, the internal counter of the CAN hardware is activated and used to generate the Time Stamp value stored in the CAN\_RDTxR/CAN\_TDTxR registers, respectively (for Rx

Table 243. USB register map and reset values (continued)

| Offset | Register    | 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   | 15   | 14   | 13   | 12   | 11   | 10   | 6    | 8    | 7             | 9    | 2     | 4     | ဗ       | 2    | 1     | 0     |

|--------|-------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|---------------|------|-------|-------|---------|------|-------|-------|

| 0x50   | USB_BTABLE  | Res. |      |      |      |      | В    | TAE  | BLE  | [15: | 3]            |      |       |       |         | Res. | Res.  | Res.  |

|        | Reset value |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0             | 0    | 0     | 0     | 0       |      |       |       |

| 0x54   | USB_LPMCSR  | Res. | Е             | BESI | L[3:0 | 0]    | REMWAKE | Res. | _     | LPMEN |

|        | Reset value |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | 0             | 0    | 0     | 0     | 0       |      | 0     | 0     |

| 0x58   | USB_BCDR    | Res. | DPPU | Res. | <b>PS2DET</b> | SDET | PDET  | рсрет | SDEN    | PDEN | DCDEN | BCDEN |

|        | Reset value |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | 0    |      |      |      |      |      |      |      | 0             | 0    | 0     | 0     | 0       | 0    | 0     | 0     |

Refer to Section 2.2.2 on page 64 for the register boundary addresses.

# 44.18 DBG register map

The following table summarizes the Debug registers

Table 260. DBG register map and reset values

| Addr.       | Register                   | 31              | 30   | 29   | 28   | 27   | 26   | 25           | 24   | 23            | 22            | 21            | 20   | 19   | 18   | 17             | 16             | 15   | 14   | 13   | 12            | 11            | 10           | 6    | 8    | 7               | 9    | S.              | 4             | က    | 2           | 1        | 0             |

|-------------|----------------------------|-----------------|------|------|------|------|------|--------------|------|---------------|---------------|---------------|------|------|------|----------------|----------------|------|------|------|---------------|---------------|--------------|------|------|-----------------|------|-----------------|---------------|------|-------------|----------|---------------|

| 0xE0042000  | DBGMCU_<br>IDCODE          |                 |      |      |      |      |      | I            | RE\  | /_IC          | )             |               |      |      |      |                |                | Res. | Res. | Res. | Res.          |               |              |      |      |                 | DE\  | /_[[            | )             |      |             |          |               |

|             | Reset value <sup>(1)</sup> | Х               | Х    | Х    | Х    | Х    | Х    | Х            | Х    | Х             | Х             | Χ             | Х    | Х    | Х    | Х              | Х              |      |      |      |               | Х             | Х            | Х    | Х    | Х               | Х    | Х               | Х             | Х    | Х           | Х        | Х             |

| 0xE0042004  | DBGMCU_CR                  | Res.            | Res. | Res. | Res. | Res. | Res. | Res.         | Res. | Res.          | Res.          | Res.          | Res. | Res. | Res. | Res.           | Res.           | Res. | Res. | Res. | Res.          | Res.          | Res.         | Res. | Res. | TPACE MODEL1:01 |      | TRACE_IOEN      | Res.          | Res. | DBG_STANDBY | DBG_STOP | DBG_SLEEP     |

|             | Reset value                |                 |      |      |      |      |      |              |      |               |               |               |      |      |      |                |                |      |      |      |               |               |              |      |      | 0               | 0    | 0               |               |      | 0           | 0        | 0             |

| 0xE004 2008 | DBGMCU_<br>APB1FZR1        | DBG_LPTIM1_STOP | Res. | Res. | Res. | Res. | Res. | DBG_CAN_STOP | Res. | DBG_I2C3_STOP | DBG_I2C2_STOP | DBG_I2C1_STOP | Res. | Res. | Res. | Res.           | Res.           | Res. | Res. | Res. | DBG_IWDG_STOP | DBG_WWDG_STOP | DBG_RTC_STOP | Res. | Res. | Res.            | Res. | DBG_TIM7_STOP   | DBG_TIM6_STOP | Res. | Res.        | Res.     | DBG_TIM2_STOP |

|             | Reset value                | 0               |      |      |      |      |      | 0            |      | 0             | 0             | 0             |      |      |      |                |                |      |      |      | 0             | 0             | 0            |      |      |                 |      | 0               | 0             |      |             |          | 0             |

| 0xE004 200C | DBGMCU_<br>APB1FZR2        | Res.            | Res. | Res. | Res. | Res. | Res. | Res.         | Res. | Res.          | Res.          | Res.          | Res. | Res. | Res. | Res.           | Res.           | Res. | Res. | Res. | Res.          | Res.          |              | Res. | Res. | Res.            | Res. | DBG_LPTIM2_STOP | Res.          | Res. | Res.        | Res.     | Res.          |

|             | Reset value                |                 |      |      |      |      |      |              |      |               |               |               |      |      |      |                |                |      |      |      |               |               |              |      |      |                 |      | 0               |               |      |             |          |               |

| 0xE004 2010 | DBGMCU_<br>APB2FZR         | Res.            | Res. | Res. | Res. | Res. | Res. | Res.         | Res. | Res.          | Res.          | Res.          | Res. | Res. | Res. | DBG_TIM16_STOP | DBG_TIM15_STOP | Res. | Res. | Res. | Res.          | DBG_TIM1_STOP | Res.         | Res. | Res. | Res.            | Res. | Res.            | Res.          | Res. | Res.        | Res.     | Res.          |

|             | Reset value                |                 |      |      |      |      |      |              |      |               |               |               |      |      |      | 0              | 0              |      |      |      |               | 0             |              |      |      |                 |      |                 |               |      |             |          |               |

<sup>1.</sup> The reset value is product dependent. For more information, refer to Section 44.6.1: MCU device ID code.