Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | FR81S                                                                          |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, CSIO, EBI/EMI, LINbus, UART/USART                                      |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                        |

| Number of I/O              | 156                                                                            |

| Program Memory Size        | 1.0625MB (1.0625M x 8)                                                         |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 64K x 8                                                                        |

| RAM Size                   | 872K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                    |

| Data Converters            | A/D 32x8/10b                                                                   |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 208-LQFP                                                                       |

| Supplier Device Package    | 208-LQFP (28x28)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb91f594bpmc-gsk5e1 |

- Multi-function serial communication (built-in transmission/reception FIFO memory):

- □ 2 channels for MB91F591/2/4/6/7/9

- □ 6 channels for MB91F59A/B

- < UART (Asynchronous serial interface) >

- Full-duplex double buffering system, 16-byte transmission FIFO memory, 16-byte reception FIFO memory

- · Parity or no parity is selectable.

- · Built-in dedicated baud rate generator

- An external clock can be used as the transfer clock

- · Parity, frame, and overrun error detect functions provided

- DMA transfer support

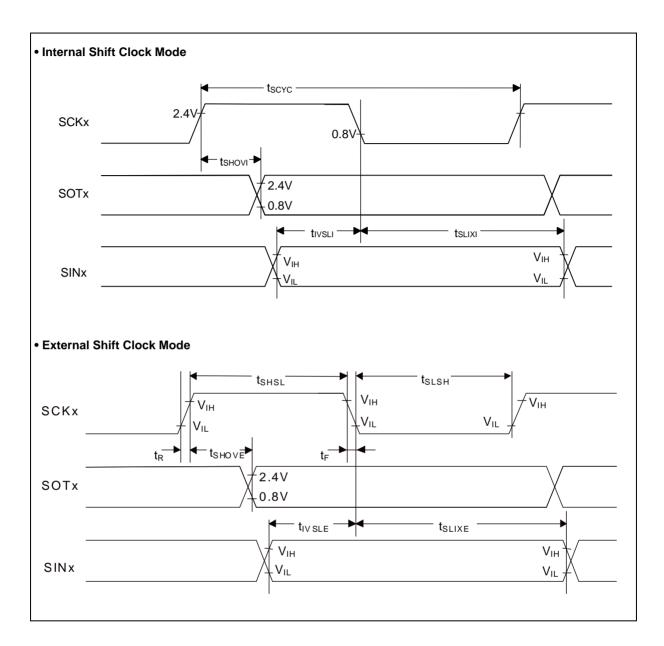

- <CSIO (Synchronous serial interface) >

- Full-duplex double buffering system, 16-byte transmission FIFO memory, 16-byte reception FIFO memory

- SPI supported; master and slave systems supported; 5 to 9-bit data length can be set.

- · Built-in dedicated baud rate generator (Master operation)

- An external clock can be entered. (Slave operation)

- Overrun error detect function is provided

- DMA transfer support

- <LIN-UART (Asynchronous Serial Interface for LIN) >

- Full-duplex double buffering system, 16-byte transmission FIFO memory, 16-byte reception FIFO memory

- · LIN protocol Revision 2.1 supported

- Master and slave systems supported

- Framing error and overrun error detection

- LIN synch break generation and detection; LIN synch delimiter generation

- · Built-in dedicated baud rate generator

- An external clock can be adjusted by the reload counter

- DMA transfer support

#### $< I^2C >$

- ch.0 and ch.1 only supported

- Full-duplex double buffering system, 16-byte transmission FIFO memory, 16-byte reception FIFO memory

- Standard mode (Max. 100kbps) / high-speed mode (Max. 400kbps) supported

- DMA transfer supported (for transmission only)

- ■CAN Controller (C-CAN): 3 channels

- ☐ Transfer speed: Up to 1Mbps

- □ 64-transmission/reception message buffering : 1 channel, 32-transmission/reception message buffering : 2 channels

- ■Up/down counter: 16-bit x 3 channels for MB91F59A/B

- ■PPG: 16-bit x 24 channels

- ■Reload timer:

- □ 16-bit x 4 channels for MB91F591/2/4/6/7/9

- □ 16-bit × 8 channels for MB91F59A/B

### ■Free-run timer:

- □ 32-bit × 2 channels (Can select each channel for input capture, output compare) for MB91F591/2/4/6/7/9

- □ 32-bit x 2 channels (LSYN (LIN synch field detection) for exclusive input capture) for MB91F591/2/4/6/7/9

- □ 32-bit x 8 channels (Can select ch.0, 1, 2, and 3 for input capture, output compare) for MB91F59A/B

### ■Input capture:

- □ 32-bit × 6 channels (linked to the free-run timer) for MB91F591/2/4/6/7/9

- $\square$  32-bit x 2 channels (linked to the free-run timer) LSYN (LIN synch field detected) Exclusive for MB91F591/2/4/6/7/9

- □ 32-bit x 12 channels (linked to the free-run timer) LSYN (LIN synch field detected) for MB91F59A/B

- ■Output compare: 32-bit x 4 channels (linked to the free-run timer)

- ■Sound generator: 5 channels

- □ Frequency and amplitude sequencers provided

- Stepping motor controller: 6 channels

- □ 8/10-bit PWM

- ☐ High current output supported (4 lines × 6 channels)

- ☐ Can refer back electromotive force using pin-shared A/D converter

- ■Real-time clock (RTC) (for day, hours, minutes, seconds)

- ☐ Main/sub oscillation frequency can be selected for the operation clock (dual product only)

- Calibration: The hardware watchdog for CR oscillation drive and real-time clock (RTC) for sub clock drive (dual product only)

- ☐ The CR oscillation frequency can be trimmed

- ☐ The main clock to sub clock (dual product only) ratio can be corrected by setting the real-time clock prescaler

- ■Clock Supervisor

- □ Monitoring abnormality (damage of crystal etc.) of sub oscillation (32kHz) (two system clock kinds) of the outside and main oscillation (4 MHz)

- □ When abnormality is detected, it switches to the CR clock.

- ■Base timer : 2 channels

- □ 16-bit timer

- $\hfill \square$  Any of four PWM/PPG/PWC/reload timer functions can be selected and used

- ☐ As for the functions of PWC and reload timer, 2 channels of cascade mode can be used as 32-bit timer.

- **■**CRC generation

- ■Watchdog timer

- □ Hardware watchdog

- □ Software watchdog

- **■**NMI

- ■Interrupt controller

- ■Interrupt request batch read

- □ Multiple interrupts from peripherals can be read by a series of registers.

| Item                                                            | Product      | MB91F592B<br>/BS                      | MB91F592BH<br>/BHS     | MB91F594B<br>/BS      | MB91F594BH<br>/BHS     |  |  |  |  |

|-----------------------------------------------------------------|--------------|---------------------------------------|------------------------|-----------------------|------------------------|--|--|--|--|

| CPU core                                                        |              | FR81S                                 |                        |                       |                        |  |  |  |  |

| Technology                                                      |              | 90nm                                  |                        |                       |                        |  |  |  |  |

| Package                                                         |              | LQFP208                               |                        |                       |                        |  |  |  |  |

| Sub clock                                                       |              | Yes (Non-S series)<br>No (S series)   |                        |                       |                        |  |  |  |  |

| Maximum CPU oper frequency                                      | ating        | 80MHz                                 |                        |                       |                        |  |  |  |  |

| Maximum GDC oper frequency                                      | ating        | 81MHz                                 |                        |                       |                        |  |  |  |  |

| Built-in CR oscillator                                          |              | 100kHz                                |                        |                       |                        |  |  |  |  |

| System clock                                                    |              | On chip PLL                           |                        |                       |                        |  |  |  |  |

| Flash                                                           | Main<br>Work | 576KB<br>64KB                         |                        | 1088KB                |                        |  |  |  |  |

|                                                                 |              |                                       |                        | CAICD                 |                        |  |  |  |  |

| RAM                                                             | Main         | 40KB<br>8KB                           |                        | 64KB                  |                        |  |  |  |  |

| VDAM                                                            | Backup       |                                       |                        |                       |                        |  |  |  |  |

| VRAM                                                            |              | 800KB<br>1ch Hardware                 |                        |                       |                        |  |  |  |  |

| Watchdog timer                                                  |              | 1ch Software                          |                        |                       |                        |  |  |  |  |

| Clock supervisor                                                |              | Initial value<br>"ON"                 | Initial value<br>"OFF" | Initial value<br>"ON" | Initial value<br>"OFF" |  |  |  |  |

| Low-voltage detection (External low-voltage                     |              | Yes                                   |                        |                       |                        |  |  |  |  |

| Low-voltage detection reset<br>(Internal low-voltage detection) |              | Yes                                   |                        |                       |                        |  |  |  |  |

| NMI function                                                    | dotootion    | Yes                                   |                        |                       |                        |  |  |  |  |

| DMA Controller                                                  |              |                                       | 16ch                   |                       |                        |  |  |  |  |

| CAN                                                             |              | 1ch (64msg)<br>2ch (32msg)            |                        |                       |                        |  |  |  |  |

| LIN-UART                                                        |              | 6ch                                   |                        |                       |                        |  |  |  |  |

| Multi-function Serial                                           | Interface    | 2ch                                   |                        |                       |                        |  |  |  |  |

| A/D converter (8bit/1                                           |              | 1unit/32ch                            |                        |                       |                        |  |  |  |  |

| Reload timer(16bit)                                             | obit)        | 4ch                                   |                        |                       |                        |  |  |  |  |

| Base timer(16bit)                                               |              | 2ch                                   |                        |                       |                        |  |  |  |  |

| Free-run timer(32bit)                                           |              | 2ch                                   |                        |                       |                        |  |  |  |  |

| Input capture(32bit)                                            | ,            | 6ch                                   |                        |                       |                        |  |  |  |  |

| Output compare(32b                                              | oit)         | 4ch                                   |                        |                       |                        |  |  |  |  |

| PPG timer(16bit)                                                | ,            | 24ch                                  |                        |                       |                        |  |  |  |  |

| Sound generator                                                 |              | 5ch                                   |                        |                       |                        |  |  |  |  |

| Real-time clock                                                 |              | Yes                                   |                        |                       |                        |  |  |  |  |

| External interrupt                                              |              | 16ch                                  |                        |                       |                        |  |  |  |  |

| CR/SUB compensat                                                | ion function | Yes                                   |                        |                       |                        |  |  |  |  |

| CRC generation                                                  |              | Yes                                   |                        |                       |                        |  |  |  |  |

| Stepping motor control                                          |              | 6ch                                   |                        |                       |                        |  |  |  |  |

| Stop mode (including shut-off)                                  | g power      | Supported                             |                        |                       |                        |  |  |  |  |

| Power supply voltag                                             | e            | MICOM:4.5V to 5.5<br>GDC:3.0V to 3.6V | 5V                     |                       |                        |  |  |  |  |

| Operating temperature                                           |              | -40°C to +105°C                       |                        |                       |                        |  |  |  |  |

| Allowable power [m\                                             |              | 1250                                  |                        |                       |                        |  |  |  |  |

| Others                                                          |              | Flash product                         |                        |                       |                        |  |  |  |  |

| On chip debugger                                                |              | Yes                                   |                        |                       |                        |  |  |  |  |

| Pin No.                                                             | Pin Name | Polarity | I/O Circuit<br>Types*1           | Function <sup>*2</sup>                  |  |

|---------------------------------------------------------------------|----------|----------|----------------------------------|-----------------------------------------|--|

| 126, 136,<br>146, 156                                               | DVCC     | _        | _                                | SMC large current port power supply pin |  |

| 125, 135,<br>145, 155                                               | DVSS     | _        | - SMC large current port GND pin |                                         |  |

| 89, 105,<br>122, 173                                                | VCC5     | _        | _                                | +5.0V power supply pin                  |  |

| 1, 18, 37,<br>53, 71,<br>175, 189                                   | VCC3     | -        | _                                | +3.3V power supply pin                  |  |

| 19, 36,<br>52, 72,<br>82, 88,<br>104, 123,<br>170, 174,<br>188, 208 | VSS      | -        | _                                | GND pin                                 |  |

<sup>\*1:</sup> For the I/O circuit types, see "I/O Circuit Type".

\*2: For switching, see "I/O Port" of Hardware Manual.

| BGA Pin No. | Pin Name | Polarity     | I/O Circuit<br>Types*1 | Function <sup>*2</sup>                                |  |  |  |

|-------------|----------|--------------|------------------------|-------------------------------------------------------|--|--|--|

| 72          | GOUT7    |              | 0                      | Display digital G7 output pin                         |  |  |  |

| 12          | PE7      | ]_           |                        | General-purpose I/O port (3V pin)                     |  |  |  |

| 73          | GOUT4    |              | 0                      | Display digital G4 output pin                         |  |  |  |

| 73          | PE4      |              | 0                      | General-purpose I/O port (3V pin)                     |  |  |  |

| 74          | ROUT7    |              | 0                      | Display digital R7 output pin                         |  |  |  |

| 74          | PD7      |              | 0                      | General-purpose I/O port (3V pin)                     |  |  |  |

| 75          | ROUT4    |              | 0                      | Display digital R4 output pin                         |  |  |  |

| 75          | PD4      |              | 0                      | General-purpose I/O port (3V pin)                     |  |  |  |

| 76          | VSS      | _            | _                      | GND pin                                               |  |  |  |

| 77          | VSS      | _            | _                      | GND pin                                               |  |  |  |

| 78          | VSS      | _            | _                      | GND pin                                               |  |  |  |

| 79          | AVSS3    | _            | _                      | NTSC AD convertor GND pin                             |  |  |  |

| 80          | AVR3     | _            | S                      | "L" side reference voltage for NTSC A/D converter pin |  |  |  |

| 81          | AVSS3    | _            | _                      | NTSC AD convertor GND pin                             |  |  |  |

| 00          | BIN6     |              |                        | Capture B6 input pin (RGB mode)                       |  |  |  |

| 82          | PC6      | 1-           | 0                      | General-purpose I/O port (3V pin)                     |  |  |  |

| 00          | BIN3     |              |                        | Capture B3 input pin (RGB mode)                       |  |  |  |

| 83          | PC3      | 1-           | 0                      | General-purpose I/O port (3V pin)                     |  |  |  |

| 0.4         | GIN6     |              |                        | Capture G6 input pin (RGB mode)                       |  |  |  |

| 84          | PB6      | 1-           | 0                      | General-purpose I/O port (3V pin)                     |  |  |  |

|             | GIN3     |              | 0                      | Capture G3 input pin (RGB mode)                       |  |  |  |

| 85          | VIN7     | 1_           |                        | Capture VIN7 input pin (656 mode)                     |  |  |  |

|             | PB3      |              |                        | General-purpose I/O port (3V pin)                     |  |  |  |

|             | RIN6     |              | 0                      | Capture R6 input pin (RGB mode)                       |  |  |  |

| 86          | VIN4     | 1_           |                        | Capture VIN4 input pin (656 mode)                     |  |  |  |

|             | PA6      |              |                        | General-purpose I/O port (3V pin)                     |  |  |  |

|             | RIN3     |              |                        | Capture R3 input pin (RGB mode)                       |  |  |  |

| 87          | VIN1     | _            | 0                      | Capture VIN1 input pin (656 mode)                     |  |  |  |

|             | PA3      |              |                        | General-purpose I/O port (3V pin)                     |  |  |  |

|             | P122     |              |                        | General-purpose I/O port                              |  |  |  |

|             | SCK5     |              |                        | LIN-UART ch.5 clock I/O pin                           |  |  |  |

| 88          | OCU0     | 1_           | С                      | Output compare ch.0 output pin                        |  |  |  |

|             | PPG7_2   |              |                        | PPG ch.7 output pin (2)                               |  |  |  |

|             | TOT3     | 1            |                        | Reload timer ch.3 output pin                          |  |  |  |

| 89          | VSS      | _            | _                      | GND pin                                               |  |  |  |

| 90          | MD2      | _            | F2                     | Mode pin 2                                            |  |  |  |

|             | FRCK7    |              |                        | Free-run timer 7 clock input pin                      |  |  |  |

|             | P114     | 1            |                        | General-purpose I/O port                              |  |  |  |

|             | ICU5_1   | 1            |                        | Input capture ch.5 input pin (1)                      |  |  |  |

| 91          | SCK3     | 1_           | С                      | LIN-UART ch.3 clock I/O pin                           |  |  |  |

|             | TRG3     | †            |                        | PPG trigger 3 input pin (ch.12 to ch.15)              |  |  |  |

|             | TIN1     | 1            |                        | Reload timer ch.1 event input pin                     |  |  |  |

|             | SGA2     | †            |                        | Sound generator ch.2 SGA output pin                   |  |  |  |

|             | RX2      |              |                        | CAN reception data 2 input pin                        |  |  |  |

|             | P113     | 1            |                        | General-purpose I/O port                              |  |  |  |

| 92          | INT11    | 1_           | С                      | INT11 External interrupt input pin                    |  |  |  |

| <u></u>     | PPG4_2   | 1            |                        | PPG ch.4 output pin (2)                               |  |  |  |

|             | TIN7     | 1            |                        | Reload timer ch.7 event input pin                     |  |  |  |

| 93          | TDI      | <del> </del> | U                      | Test Data In (JTAG Boundary Scan Test)                |  |  |  |

| JU          | וטו      |              | J                      | 1001 Data in (0170 Doundary Ocall 1601)               |  |  |  |

| BGA Pin No. | Pin Name  | Polarity     | I/O Circuit<br>Types*1 | Function*2                                         |  |  |

|-------------|-----------|--------------|------------------------|----------------------------------------------------|--|--|

| 94          | VSS       | _            | _                      | GND pin                                            |  |  |

| 95          | TRST      | _            | V                      | Test Reset (JTAG Boundary Scan Test)               |  |  |

| 00          | AN30      |              | _                      | ADC Analog 30 input pin                            |  |  |

| 96          | P086      | 1-           | E                      | General-purpose I/O port                           |  |  |

|             | ICU3_2    |              |                        | Input capture ch.3 input pin (2)                   |  |  |

| 96          | PPG22     | 1_           | E                      | PPG ch.22 output pin                               |  |  |

|             | PWM2P5    | 1            |                        | SMC ch.5 output pin                                |  |  |

|             | AN27      |              |                        | ADC Analog 27 input pin                            |  |  |

|             | P083      |              |                        | General-purpose I/O port                           |  |  |

|             | ICU0_2    |              | _                      | Input capture ch.0 input pin (2)                   |  |  |

| 97          | PPG19     | -            | E                      | PPG ch.19 output pin                               |  |  |

|             | PWM2M4    |              |                        | SMC ch.4 output pin                                |  |  |

|             | UDCZIN2   | 1            |                        | Up/down counter ch.2 ZIN input pin                 |  |  |

|             | AN24      |              |                        | ADC Analog 24 input pin                            |  |  |

|             | P080      |              |                        | General-purpose I/O port                           |  |  |

|             | SIN6      |              |                        | LIN-UART ch.6 serial data input pin                |  |  |

| 98          | PPG16     | _            | E                      | PPG ch.16 output pin                               |  |  |

|             | PWM1P4    |              |                        | SMC ch.4 output pin                                |  |  |

|             | UDCAIN0_1 |              |                        | Up/down counter ch.0 AIN input pin (1)             |  |  |

|             | AN21      |              |                        | ADC Analog 21 input pin                            |  |  |

|             | P075      |              | E                      | General-purpose I/O port                           |  |  |

|             | ICU8      |              |                        | Input capture ch.8 input pin                       |  |  |

| 99          | SIN7_1    | <del>-</del> |                        | LIN-UART ch.7 serial data input pin                |  |  |

|             | PPG13_1   |              |                        | PPG ch.13 output pin (1)                           |  |  |

|             | PWM1M3    | 1            |                        | SMC ch.3 output pin                                |  |  |

|             | AN18      |              |                        | ADC Analog 18 input pin                            |  |  |

|             | P072      |              |                        | General-purpose I/O port                           |  |  |

| 100         | ICU11     | <u> </u> _   | E                      | Input capture ch.11 input pin                      |  |  |

| 100         | SIN8      |              | _                      | Multi-function serial ch.8 serial data input pin   |  |  |

|             | PWM2P2    |              |                        | SMC ch.2 output pin                                |  |  |

|             | AN15      |              | 1                      | ADC Analog 15 input pin                            |  |  |

|             | P067      |              |                        | General-purpose I/O port                           |  |  |

| 101         | SIN9      | <u> </u>     | E                      | Multi-function serial ch.9 serial data input pin   |  |  |

| 101         | PWM2M1    | -            |                        | SMC ch.1 output pin                                |  |  |

|             | UDCAIN0   |              |                        | Up/down counter ch.0 AIN input pin                 |  |  |

|             | AN12      |              |                        | ADC Analog 12 input pin                            |  |  |

|             | P064      | 1            |                        | General-purpose I/O port                           |  |  |

| 102         | PWM1P1    | -            | E                      | SMC ch.1 output pin                                |  |  |

|             | UDCAIN1   | -            |                        | Up/down counter ch.1 AIN input pin                 |  |  |

|             |           |              |                        | · · ·                                              |  |  |

|             | AN9       | -            |                        | ADC Analog 9 input pin                             |  |  |

| 103         | P061      | -            | E                      | General-purpose I/O port                           |  |  |

|             | SOT10     | -            |                        | Multi-function serial ch.10 serial data output pin |  |  |

| 404         | PWM1M0    |              |                        | SMC ch.0 output pin                                |  |  |

| 104         | VSS       | _            | _                      | GND pin                                            |  |  |

| BGA Pin<br>No. | Pin Name | Polarity | I/O Circuit<br>Types*1 | Function*2             |

|----------------|----------|----------|------------------------|------------------------|

| 251            | VSS      | _        | _                      | GND pin                |

| 252            | VCC3     | _        | _                      | +3.3V power supply pin |

| 253            | VCC3     | _        | _                      | +3.3V power supply pin |

| 254            | VSS      | _        | _                      | GND pin                |

| 255            | VCC3     | _        | _                      | +3.3V power supply pin |

| 256            | VCC3     | _        | _                      | +3.3V power supply pin |

| 257            | GND      | _        | _                      | GND pin                |

| :              | :        | :        | :                      | :                      |

| :              | :        | :        | :                      | :                      |

| :              | :        | :        | :                      | :                      |

| 320            | GND      | _        | _                      | GND pin                |

<sup>\*1:</sup> For the I/O circuit types, see "I/O Circuit Type".

\*2: For switching, see "I/O Port" of Hardware Manual.

## ■Memory map

|                        | MB91F592,<br>MB91F597                 |     |

|------------------------|---------------------------------------|-----|

| 0000 0000 <sub>H</sub> | I/O                                   |     |

| 0000 4000 <sub>H</sub> | Back up RAM (8KB)                     |     |

| 0000 6000 <sub>H</sub> | I/O                                   |     |

| 0001 0000 <sub>H</sub> | RAM (40KB)                            |     |

| 0001 A000 <sub>H</sub> | Reserved                              |     |

| 0003 0000 <sub>H</sub> |                                       | АНВ |

|                        | Access inhibit                        |     |

| 0007 0000 <sub>H</sub> | Flash memory<br>(512+64) KB           |     |

| 0010 0000 <sub>H</sub> | Access inhibit                        |     |

| 0023 0000 <sub>H</sub> | WorkFlash (64KB)                      |     |

| 0024 0000 <sub>H</sub> | Access inhibit                        |     |

| 0040 0000 <sub>H</sub> | GDC control +<br>External area (96MB) | АНВ |

| 0640 0000 <sub>H</sub> |                                       |     |

| 8000 0000 <sub>H</sub> | Access inhibit                        |     |

| FFFF FFFF <sub>H</sub> |                                       |     |

| Adduses             |                                  | Block                                                                |                                  |                                  |                                                             |

|---------------------|----------------------------------|----------------------------------------------------------------------|----------------------------------|----------------------------------|-------------------------------------------------------------|

| Address             | +0                               | +1                                                                   | +2                               | +3                               | Block                                                       |

| 000E60 <sub>н</sub> | EPFR00[R/W]<br>B,H,W<br>00000000 | EPFR01[R/W]<br>B,H,W<br>0000 <sup>*1</sup><br>00000000 <sup>*2</sup> | EPFR02[R/W]<br>B,H,W<br>00000    | EPFR03[R/W]<br>B,H,W<br>00000    |                                                             |

| 000E64 <sub>н</sub> | EPFR04[R/W]<br>B,H,W<br>00000    | EPFR05[R/W]<br>B,H,W<br>00000                                        | EPFR06[R/W]<br>B,H,W<br>00000    | EPFR07[R/W]<br>B,H,W<br>00000    |                                                             |

| 000E68 <sub>Н</sub> | EPFR08[R/W]<br>B,H,W<br>00000    | EPFR09[R/W]<br>B,H,W<br>00000                                        | EPFR10[R/W]<br>B,H,W<br>-0000000 | EPFR11[R/W]<br>B,H,W<br>000000   |                                                             |

| 000E6C <sub>н</sub> | EPFR12[R/W]<br>B,H,W<br>000000   | EPFR13[R/W]<br>B,H,W<br>000000                                       | EPFR14[R/W]<br>B,H,W<br>000000   | EPFR15[R/W]<br>B,H,W<br>-0000000 |                                                             |

| 000Е70н             | EPFR16[R/W]<br>B,H,W<br>00000000 | EPFR17[R/W]<br>B,H,W<br>00000000                                     | EPFR18[R/W]<br>B,H,W<br>10000000 | EPFR19[R/W]<br>B,H,W<br>11111111 |                                                             |

| 000E74 <sub>H</sub> | EPFR20[R/W]<br>B,H,W<br>-1111111 | EPFR21[R/W]<br>B,H,W<br>00000000                                     | EPFR22[R/W]<br>B,H,W<br>00000000 | EPFR23[R/W]<br>B,H,W<br>00000000 |                                                             |

| 000Е78 <sub>н</sub> | EPFR24[R/W]<br>B,H,W<br>000      | EPFR25[R/W]<br>B,H,W<br>000                                          | EPFR26[R/W]<br>B,H,W<br>0000     | EPFR27[R/W]<br>B,H,W<br>00000    | Extended port<br>function register<br>*1:MB91F591/2/4/6/7/9 |

| 000Е7Сн             | EPFR28[R/W]<br>B,H,W<br>00       | EPFR29[R/W]<br>B,H,W<br>00000000                                     | EPFR30[R/W]<br>B,H,W<br>00000000 | EPFR31[R/W]<br>B,H,W<br>00000000 | *2:MB91F59A/B                                               |

| 000E80 <sub>н</sub> | EPFR32[R/W]<br>B,H,W<br>00000000 | EPFR33[R/W]<br>B,H,W<br>00000                                        | EPFR34[R/W]<br>B,H,W<br>00000    | EPFR35[R/W]<br>B,H,W<br>00000    |                                                             |

| 000E84 <sub>н</sub> | EPFR36[R/W]<br>B,H,W<br>00000    | EPFR37[R/W]<br>B,H,W<br>00000000                                     | EPFR38[R/W]<br>B,H,W<br>00000    | EPFR39[R/W]<br>B,H,W<br>00000000 |                                                             |

| 000E88 <sub>н</sub> | EPFR40[R/W]<br>B,H,W<br>000000   | EPFR41[R/W]<br>B,H,W<br>000                                          | EPFR42[R/W]<br>B,H,W<br>00       | EPFR43[R/W]<br>B,H,W<br>00000000 |                                                             |

| 000E8С <sub>н</sub> | EPFR44[R/W]<br>B,H,W<br>00000000 | EPFR45[R/W]<br>B,H,W<br>00000000                                     | EPFR46[R/W]<br>B,H,W<br>000000   | EPFR47[R/W]<br>B,H,W<br>0        |                                                             |

| 000Е90 <sub>н</sub> | EPFR48[R/W]<br>B,H,W<br>00000000 | EPFR49[R/W]<br>B,H,W<br>00000000                                     | EPFR50[R/W]<br>B,H,W<br>00000000 | EPFR51[R/W]<br>B,H,W<br>00000    |                                                             |

| 000Е94 <sub>н</sub> | EPFR52[R/W]<br>B,H,W<br>000      | EPFR53[R/W]<br>B,H,W<br>00000                                        | EPFR54[R/W]<br>B,H,W<br>0000     | EPFR55[R/W]<br>B,H,W<br>01       |                                                             |

| 000Е98н             | EPFR56[R/W]<br>B,H,W<br>000000   | EPFR57[R/W]<br>B,H,W<br>000000                                       | EPFR58[R/W]<br>B,H,W<br>0000     | _                                | Extended port<br>function register<br>MB91F59A/B only       |

| 000Е9Сн             | _                                | _                                                                    | _                                | _                                | Reserved                                                    |

| Address                                          |                                      | Address Offset Val                  | ue / Register Nan                                                 | ne                                   | Block                                      |

|--------------------------------------------------|--------------------------------------|-------------------------------------|-------------------------------------------------------------------|--------------------------------------|--------------------------------------------|

| Audiess                                          | +0                                   | +1                                  | +2                                                                | +3                                   | BIOCK                                      |

| 000FAC <sub>н</sub>                              | CPCLR3 [R/W] W<br>11111111 11111111  | 11111111 11111111                   |                                                                   |                                      |                                            |

| 000FB0 <sub>н</sub>                              | TCDT3 [R/W] W<br>00000000 000000     | 00 00000000 00000                   | 0000                                                              |                                      | Free-run timer 3                           |

| 000FB4 <sub>н</sub>                              | TCCSH3 [R/W]<br>B, H, W<br>000       | TCCSL3 [R/W]<br>B, H, W<br>-1-00000 | _                                                                 |                                      |                                            |

| 000FB8 <sub>н</sub>                              | CPCLR4 [R/W] W                       | 11111111 11111111                   |                                                                   |                                      |                                            |

| 000FBC <sub>н</sub>                              | TCDT4 [R/W] W                        | 00 00000000 00000                   | 0000                                                              |                                      | Free-run timer 4                           |

| 000FC0 <sub>н</sub>                              | TCCSH4 [R/W]<br>B, H, W<br>000       | TCCSL4 [R/W]<br>B, H, W<br>-1-00000 | _                                                                 |                                      | –MB91F59A/B only                           |

| 000FC4 <sub>Н</sub>                              | CPCLR5 [R/W] W<br>11111111 11111111  | 11111111 11111111                   |                                                                   |                                      |                                            |

| 000FC8 <sub>н</sub>                              |                                      | 00 00000000 00000                   | 0000                                                              |                                      | Free-run timer 5  MB91F59A/B only          |

| 000FCC <sub>н</sub>                              | TCCSH5 [R/W]<br>B, H, W<br>000       | TCCSL5 [R/W]<br>B, H, W<br>-1-00000 | _                                                                 |                                      |                                            |

| 000FD0 <sub>Н</sub>                              | IPCP6 [R] W<br>XXXXXXXX XXXX         | XXXXX XXXXXXX                       | XXXXXXX                                                           |                                      |                                            |

| 000FD4 <sub>Н</sub>                              | IPCP7 [R] W XXXXXXX XXXXXXX XXXXXXXX |                                     |                                                                   |                                      | Input capture 6,7                          |

| 000FD8 <sub>Н</sub>                              | ICFS67 [R/W]<br>B, H, W<br>00        | _                                   | LSYNS1 [R/W]<br>B,H,W<br>00 <sup>*1</sup><br>000000* <sup>2</sup> | ICS67 [R/W]<br>B, H, W<br>00000000   | *2:MB91F59A/B                              |

| 000FDC <sub>н</sub>                              | IPCP8 [R] W<br>XXXXXXXX XXXX         | XXXX XXXXXXX                        | XXXXXXX                                                           |                                      |                                            |

| 000FE0 <sub>н</sub>                              | IPCP9 [R] W<br>XXXXXXXX XXXX         | XXXXX XXXXXXX                       | XXXXXXX                                                           |                                      | Input Capture 8,9  MB91F59A/B only         |

| 000FE4 <sub>H</sub>                              | ICFS89 [R/W]<br>B, H, W<br>00        | _                                   | _                                                                 | ICS89 [R/W]<br>B, H, W<br>00000000   | - Wide II Serve Stilly                     |

| 000FE8 <sub>н</sub>                              | IPCP10 [R] W<br>XXXXXXXX XXXX        | XXXXX XXXXXXXX                      | XXXXXXX                                                           |                                      |                                            |

| 000FEC <sub>н</sub>                              |                                      | XXXX XXXXXXX                        | xxxxxxx                                                           |                                      | Input Capture 10,11<br>—MB91F59A/B only    |

| 000FF0 <sub>н</sub>                              | ICFS1011 [R/W]<br>B, H, W<br>00      | _                                   | _                                                                 | ICS1011 [R/W]<br>B, H, W<br>00000000 | ,                                          |

| 000FF4 <sub>н</sub>                              | RCRH2[W]<br>H,W<br>XXXXXXXX          | RCRL2[W]<br>B,H,W<br>XXXXXXXX       | UDCRH2[R]<br>H,W<br>00000000                                      | UDCRL2[R]<br>B,H,W<br>00000000       | Up/down counter 2                          |

| 000FF8 <sub>н</sub>                              | CCR2[R/W] B,H<br>00000000 -000100    |                                     | _                                                                 | CSR2[R/W] B<br>00000000              | MB91F59A/B only                            |

| 000FFC <sub>н</sub>                              | _                                    | _                                   | _                                                                 | _                                    | Reserved                                   |

| 001000 <sub>Н</sub>                              | SACR [R/W]<br>B,H,W<br>0             | PICD [R/W]<br>B,H,W<br>0011         | _                                                                 | _                                    | Synchronous/asynchronous switching control |

| 001004 <sub>H</sub><br>to<br>00103C <sub>H</sub> | _                                    |                                     |                                                                   |                                      | Reserved                                   |

| Address                                          |                                      | Address Offset V                 | alue / Register N               | ame                             | Block             |  |  |

|--------------------------------------------------|--------------------------------------|----------------------------------|---------------------------------|---------------------------------|-------------------|--|--|

| Address                                          | +0                                   | +1                               | +2                              | +3                              | Біоск             |  |  |

| 0010C0 <sub>н</sub>                              | _                                    |                                  |                                 |                                 |                   |  |  |

| 0010С4 <sub>н</sub>                              | SGAR4[R/W] B,H<br>00000000 000000    | •                                | SGFR4[R/W]<br>B,H,W<br>00000000 | SGNR4[R/W]<br>B,H,W<br>00000000 | Sound generator 4 |  |  |

| 0010С8 <sub>н</sub>                              | SGTCR4[R/W]<br>B,H,W<br>00000000     | SGIDR4[R/W]<br>B,H,W<br>00000000 | SGPCR4[R/W]<br>00000000 11111   |                                 |                   |  |  |

| 0010ССн                                          | SGDMAR4[W] B,I                       | H,W<br>000 00000000 000          | 00000                           |                                 |                   |  |  |

| 0010D0 <sub>H</sub><br>to<br>00112C <sub>H</sub> | _                                    | _                                | _                               | _                               | Reserved          |  |  |

| 001130 <sub>н</sub>                              | _                                    | _                                | _                               | CRCCR[R/W]<br>B,H,W<br>-0000000 |                   |  |  |

| 001134 <sub>н</sub>                              | CRCINIT[R/W] B,<br>1111111 1111111 1 |                                  |                                 | ·                               | CRC arithmetic    |  |  |

| 001138 <sub>Н</sub>                              | CRCIN[R/W] B,H,<br>00000000 000000   | W<br>000 00000000 000            | 00000                           |                                 | operation         |  |  |

| 00113С <sub>н</sub>                              | CRCR[R] B,H,W<br>1111111 1111111 1   | 111111 1111111                   |                                 |                                 |                   |  |  |

| 001140 <sub>Н</sub><br>to<br>0013FC <sub>Н</sub> | _                                    |                                  | _                               | _                               | Reserved          |  |  |

| 001400 <sub>H</sub><br>to<br>001FFC <sub>H</sub> | _                                    | _                                | _                               | _                               | Reserved (3KB)    |  |  |

| A -1 -1                                          | <i>-</i>                          | Address Offset Va | Disala                            |                                              |                                    |

|--------------------------------------------------|-----------------------------------|-------------------|-----------------------------------|----------------------------------------------|------------------------------------|

| Address                                          | +0                                | +1                | +2                                | +3                                           | Block                              |

| 002500н                                          | SEEARH[R] B,H,W<br>000000 0000000 |                   | DEEARH[R] B,H,V<br>000000 0000000 |                                              |                                    |

| 002504 <sub>н</sub>                              | EECSRH[R/W]<br>B,H,W<br>0000      | _                 | EFEARH[R/W]B,H<br>000000 0000000  | AHB RAM ECC control register MB91F59A/B only |                                    |

| 002508 <sub>Н</sub>                              | _                                 | EFECRH[R/W]B,H    |                                   |                                              |                                    |

| 00250С <sub>н</sub><br>to<br>002FFС <sub>н</sub> | _                                 | _                 | _                                 | _                                            | Reserved                           |

| 003000н                                          | SEEARA[R] B,H,W                   | I                 | DEEARA[R] B,H,V                   |                                              |                                    |

| 003004 <sub>н</sub>                              | EECSRA<br>[R/W] B,H,W<br>0000     | _                 | EFEARA[R/W] B,F                   |                                              | Backup RAM<br>ECC control register |

| 003008н                                          | _                                 | EFECRA[R/W] B,F   |                                   |                                              |                                    |

| 00300С <sub>н</sub><br>to<br>003FFС <sub>н</sub> | _                                 | _                 | _                                 | _                                            | Reserved                           |

| 004000 <sub>н</sub><br>to<br>005FFC <sub>н</sub> | Backup RAM                        |                   |                                   | Backup RAM area                              |                                    |

| 006000 <sub>H</sub><br>to<br>00EFFC <sub>H</sub> | _                                 | _                 | _                                 | _                                            | Reserved                           |

| 00F000 <sub>H</sub><br>to<br>00FEFC <sub>H</sub> | _                                 | _                 | _                                 | _                                            | Reserved [S]                       |

| 00FF00 <sub>н</sub>                              | DSUCR [R/W] B,H                   | ,W                | _                                 | _                                            | OCDU [S]                           |

| 00FF04 <sub>H</sub><br>to<br>00FF0C <sub>H</sub> | _                                 | _                 | _                                 | _                                            | Reserved [S]                       |

| 00FF10 <sub>н</sub>                              | PCSR [R/W] B,H,V<br>XXXXXXXX XXXX |                   | XXXXXXX                           |                                              | OCDITICI                           |

| 00FF14 <sub>н</sub>                              | PSSR [R/W] B,H,V<br>XXXXXXXX XXXX | V<br>XXXX XXXXXXX | OCDU [S]                          |                                              |                                    |

| 00FF18 <sub>H</sub><br>to<br>00FFF4 <sub>H</sub> | _                                 | _                 | _                                 | _                                            | Reserved [S]                       |

| 00FFF8 <sub>H</sub>                              | EDIR1 [R] B,H,W<br>XXXXXXXX XXXX  | xxxx xxxxxxx      | xxxxxxx                           | <b>,</b>                                     | OCDITIEI                           |

| 00FFFС <sub>н</sub>                              | EDIR0 [R] B,H,W<br>XXXXXXXX XXXX  | xxxx xxxxxxx      | XXXXXXX                           |                                              | OCDU [S]                           |

[S]:It is a system register. The illegal instruction exception (data access error) is generated in these registers in the user mode when reading and writing to it.

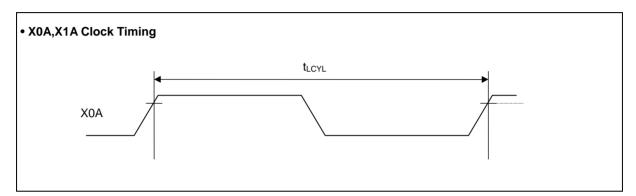

## 11.4.1.1 Sub clock timing (products without s-suffix)

(T<sub>A</sub>: Recommended operating conditions,  $V_{CC}5=5.0V \pm 10\%$ ,  $V_{SS}=DV_{SS}=AV_{SS}=0.0V$ )

| Parameter                           | Symbol            | Pin Name    | Conditions | Value |        |     | Unit | Remarks |

|-------------------------------------|-------------------|-------------|------------|-------|--------|-----|------|---------|

| Farameter                           | Syllibol          | FIII Naille | Conditions | Min   | Тур    | Max | Oiii | Remarks |

| Source oscillation clock frequency  | F <sub>CL</sub>   | X0A, X1A    | _          | _     | 32.768 | _   | kHz  |         |

| Source oscillation clock cycle time | t <sub>LCYL</sub> | X0A, X1A    | _          | -     | 30.52  | _   | μs   |         |

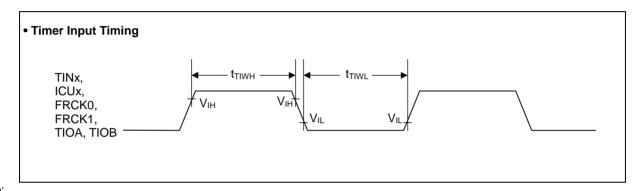

## 11.4.1.6 Timer input timing

(T<sub>A</sub>: Recommended operating conditions,  $V_{CC}5=5.0V \pm 10\%$ ,  $V_{SS}=AV_{SS}=0.0V$ )

| Parameter         | Symbol                                   | Pin Name                                                                                                                             | Conditions | Value             |     | Unit  | Remarks |

|-------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|-----|-------|---------|

| i arameter        | Cyllibol                                 | 1 III I I I III                                                                                                                      | Conditions | Min               | Max | Offic | Remarks |

| Input pulse width | t <sub>TIWH</sub> ,<br>t <sub>TIWL</sub> | TIN0 to TIN3,<br>TIN7 to TIN10,<br>ICU0 to ICU11,<br>FRCK0 to FRCK7,<br>TIOA,TIOB,<br>UDCAIN0 to 2,<br>UDCBIN0 to 2,<br>UDCZIN0 to 2 | -          | 4t <sub>CPP</sub> | _   | ns    |         |

### Note:

The description can be applied to FRCK2 to 7, UDCAIN0 to 2, UDCBIN0 to 2, and UDCZIN0 to 2 as well.

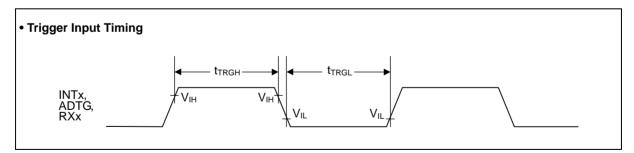

## 11.4.1.7 Trigger input timing

( $T_A$ : Recommended operating conditions,  $V_{CC}5=5.0V \pm 10\%$ ,  $V_{SS}=AV_{SS}=0.0V$ )

| Parameter         | Symbol                                                                   | Pin Name | Conditions | Value             |     | Unit         | Remarks     |

|-------------------|--------------------------------------------------------------------------|----------|------------|-------------------|-----|--------------|-------------|

| raiailletei       |                                                                          |          |            | Min               | Max | Offic        | iveillai va |

| Input pulse width | t <sub>TRGH</sub> , t <sub>TRGL</sub> INT0 to INT15, ADTG, RX0, RX1, RX2 | ,        |            | 5t <sub>CPP</sub> | _   | ns           |             |

|                   |                                                                          | _        | 1          | _                 | μs  | At stop mode |             |

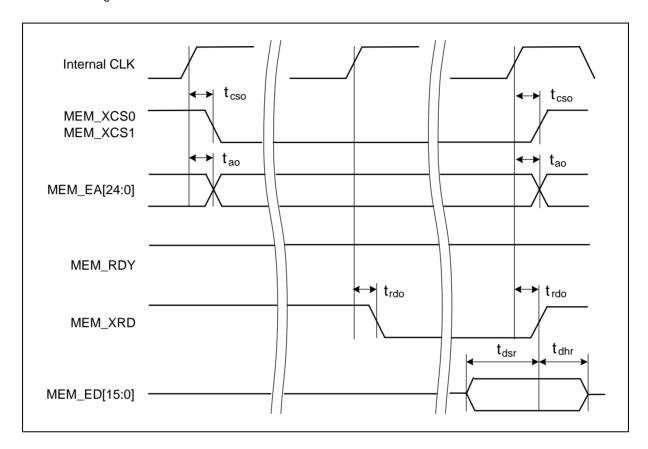

## ■NOR Flash read timing

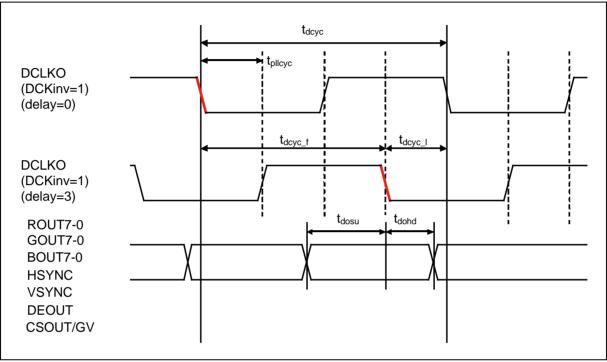

Built-in PLL reverse edge and delay mode (DCM3.DCKinv=1)

Figure 6 shows the setup/hold definition when the external display device receives the signal at the falling edge of DCLKO. (Example: When frequency division ratio = 4)

Figure 6. Built-in PLL Reverse Edge and Delay Mode Setup/Hold Definition

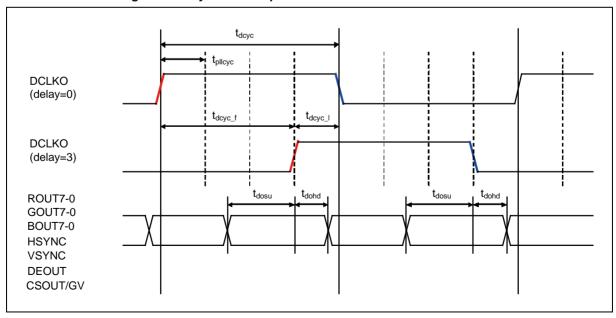

Built-in PLL both edge and delay mode (DCM3.DCKinv=0)

Figure 7 shows the setup/hold definition when the external display device (TFT) receives the signal both at the rising edge and the falling edge of DCLKO. (Example: When frequency division ratio = 4) Although there are two sampling locations in both edge mode; one at the rising edge and the other at the falling edge, the values of setup/hold definition are same.

Figure 7. Built-in PLL Both Edge and Delay Mode Setup/Hold Definition

## Setup/Hold Definition in Delay Mode

The delay mode is a mode realized with DCLKO delay function, and it can provide delay to DCLKO signal output itself. This can be used when both the following conditions are satisfied.

- The internal PLL is used to generate DCLKO (CKS field of DCM register = 0)

- The frequency division ratio to the internal PLL of DCLKO is 2 or more (SC field of DCM register > 0)

The delay value is set as the unit for internal PLL clock by DCKD field of DCM3 register. The meanings of DCKD setting value are shown below.

When the internal PLL frequency division ratio = 2

| irequeries arrielen ratio = 2 |                     |  |  |  |

|-------------------------------|---------------------|--|--|--|

| DCKD                          | Delay               |  |  |  |

| 000000                        | No additional delay |  |  |  |

| 000100                        | +1 PLL clock        |  |  |  |

When the internal PLL frequency division ratio > 2

| arriolori radio / 2 |                     |

|---------------------|---------------------|

| DCKD                | Delay               |

| 000000              | No additional delay |

| 000010              | +2 PLL clock        |

| 000100              | +3 PLL clock        |

| 000110              | +4 PLL clock        |

|                     | :                   |

| 111110              | +17 PLL clock       |

In delay mode, t<sub>dcvc f</sub> and t<sub>dcvc l</sub> are defined by the delay value above (e.g. "2" of "+2 PLL clock") as shown below.

$t_{dcyc_f}$  = Delay value ×  $t_{pllcyc}$

$t_{dcyc\_I} = t_{dcyc} - t_{dcyc\_f}$

# 12. Ordering Information

| Part Number         | Package '                               |  |  |

|---------------------|-----------------------------------------|--|--|

| MB91F591BPMC-GSE1   |                                         |  |  |

| MB91F591BSPMC-GSE1  |                                         |  |  |

| MB91F591BHPMC-GSE1  |                                         |  |  |

| MB91F591BHSPMC-GSE1 |                                         |  |  |

| MB91F592BPMC-GSE1   |                                         |  |  |

| MB91F592BSPMC-GSE1  | 208-pin plastic LQFP (LQR208)           |  |  |

| MB91F592BHPMC-GSE1  |                                         |  |  |

| MB91F592BHSPMC-GSE1 |                                         |  |  |

| MB91F594BPMC-GSE1   |                                         |  |  |

| MB91F594BSPMC-GSE1  |                                         |  |  |

| MB91F594BHPMC-GSE1  |                                         |  |  |

| MB91F594BHSPMC-GSE1 |                                         |  |  |

| MB91F59BCEQ-GSE1    | 208-pin plastic TEQFP                   |  |  |

| MB91F59BCHSEQ-GSE1  | (LET208)                                |  |  |

| MB91F59ACPB-GSE1    |                                         |  |  |

| MB91F59ACSPB-GSE1   |                                         |  |  |

| MB91F59ACHPB-GSE1   |                                         |  |  |

| MB91F59ACHSPB-GSE1  | 320-Ball Grid Array Package<br>(BYA320) |  |  |

| MB91F59BCPB-GSE1    |                                         |  |  |

| MB91F59BCSPB-GSE1   |                                         |  |  |

| MB91F59BCHPB-GSE1   |                                         |  |  |

| MB91F59BCHSPB-GSE1  |                                         |  |  |

$<sup>^{*1}</sup>$ : For details of the package, see "Package Dimensions ".

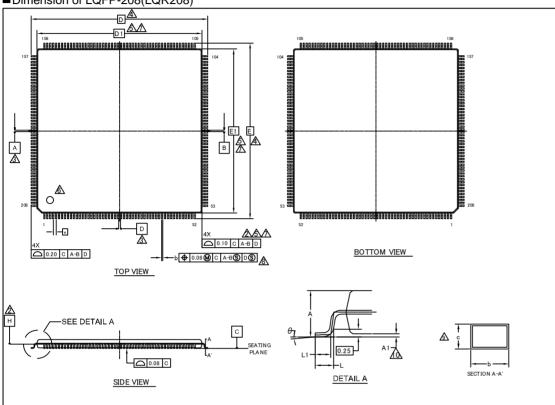

## 13. Package Dimensions

■Dimension of LQFP-208(LQR208)

| SYMBOL  | DIMENSIONS |      |      |  |  |

|---------|------------|------|------|--|--|

| STWIBOL | MIN.       | NOM. | MAX. |  |  |

| Α       | _          | -    | 1.70 |  |  |

| A1      | 0.05       |      | 0.15 |  |  |

| b       | 0.17       | 0.22 | 0.27 |  |  |

| С       | 0.09       | -    | 0.20 |  |  |

| D       | 30.00 BSC  |      |      |  |  |

| D1      | 28.00 BSC  |      |      |  |  |

| е       | 0.50 BSC   |      |      |  |  |

| E       | 30.00 BSC  |      |      |  |  |

| E1      | 28.00 BSC  |      |      |  |  |

| L       | 0.45       | 0.60 | 0.75 |  |  |

| L1      | 0.30       | 0.50 | 0.70 |  |  |

| θ       | 0°         |      | 8°   |  |  |

### **NOTES**

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- △ DATUM PLANE H IS LOCATED AT THE BOTTOM OF THE MOLD PARTING LINE COINCIDENT WITH WHERE THE LEAD EXITS THE BODY.

- $\frac{\triangle}{\triangle}$  DATUMS A-B AND D TO BE DETERMINED AT DATUM PLANE H.

- ⚠ TO BE DETERMINED AT SEATING PLANE C.

- ⚠ DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION.

ALLOWABLE PROTRUSION IS 0.25mm PRE SIDE.

DIMENSIONS D1 AND E1 INCLUDE MOLD MISMATCH AND ARE DETERMINED

AT DATUM PLANE H.

- ⚠DETAILS OF PIN 1 IDENTIFIER ARE OPTIONAL BUT MUST BE LOCATED WITHIN THE ZONE INDICATED.

- AREGARDLESS OF THE RELATIVE SIZE OF THE UPPER AND LOWER BODY SECTIONS. DIMENSIONS D1 AND E1 ARE DETERMINED AT THE LARGEST FEATURE OF THE BODY EXCLUSIVE OF MOLD FLASH AND GATE BURRS. BUT INCLUDING ANY MISMATCH BETWEEN THE UPPER AND LOWER SECTIONS OF THE MOLDER BODY.

- ⚠DIMENSION 6 DOES NOT INCLUDE DAMBER PROTRUSION. THE DAMBAR PROTRUSION (\$) SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 6 MAXIMUM BY MORE THAN 0.08mm. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE LEAD FOOT.

- ↑ THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10mm AND 0.25mm FROM THE LEAD TIP.

- A1 IS DEFINED AS THE DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT OF THE PACKAGE BODY.

002-15151 \*\*

PACKAGE OUTLINE, 208 LEAD LQFP 28.0X28.0X1.7 MM LQR208 REV\*\*

## Sales, Solutions, and Legal Information

### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

### **Products**

ARM® Cortex® Microcontrollers cypress.com/arm

Automotive cypress.com/automotive

Clocks & Buffers cypress.com/clocks

Interface cypress.com/interface

Internet of Things cypress.com/iot

Memory cypress.com/memory

Microcontrollers cypress.com/mcu

PSoC cypress.com/psoc

Power Management ICs cypress.com/pmic

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless Connectivity cypress.com/wireless

# **PSoC®** Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

# **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Videos | Blogs | Training | Components

# **Technical Support**

cypress.com/support

Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

© Cypress Semiconductor Corporation, 2015-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software produce code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system values or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 002-04727 Rev. \*B December 1, 2017 Page 174 of 174