Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                          |

| Number of I/O              | 20                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 11x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs702-e-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-0           | R/W-0                                                      | R/W-0                           | R/W-0                                  | R/W-0                               | R/W-0           | R/W-0           | R/W-0 |

|-----------------|------------------------------------------------------------|---------------------------------|----------------------------------------|-------------------------------------|-----------------|-----------------|-------|

| NSTDIS          | OVAERR                                                     | OVBERR                          | COVAERR                                | COVBERR                             | OVATE           | OVBTE           | COVTE |

| bit 15          |                                                            |                                 |                                        |                                     |                 |                 | bit 8 |

|                 | <b>- - -</b>                                               |                                 | <b>B</b> 444 -                         | <b>-</b>                            | <b>B</b> 444 -  | <b>B</b> 444 -  |       |

| R/W-0           | R/W-0                                                      | U-0                             | R/W-0                                  | R/W-0                               | R/W-0           | R/W-0           | U-0   |

| SFTACERR        | DIV0ERR                                                    | —                               | MATHERR                                | ADDRERR                             | STKERR          | OSCFAIL         | —     |

| bit 7           |                                                            |                                 |                                        |                                     |                 |                 | bit 0 |

| Legend:         |                                                            |                                 |                                        |                                     |                 |                 |       |

| R = Readable    | bit                                                        | W = Writable                    | bit                                    | U = Unimplem                        | ented bit, read | as '0'          |       |

| -n = Value at F |                                                            | '1' = Bit is set                |                                        | '0' = Bit is clea                   |                 | x = Bit is unki | nown  |

|                 |                                                            |                                 |                                        |                                     |                 |                 |       |

| bit 15          | NSTDIS: Inte                                               | errupt Nesting                  | Disable bit                            |                                     |                 |                 |       |

|                 |                                                            | nesting is disa                 |                                        |                                     |                 |                 |       |

|                 |                                                            | nesting is ena                  |                                        |                                     |                 |                 |       |

| bit 14          |                                                            |                                 | Overflow Trap F                        | -                                   |                 |                 |       |

|                 |                                                            |                                 | erflow of Accur<br>y overflow of Accur |                                     |                 |                 |       |

| bit 13          |                                                            |                                 | Overflow Trap F                        |                                     |                 |                 |       |

|                 |                                                            |                                 | erflow of Accur                        | -                                   |                 |                 |       |

|                 |                                                            |                                 | y overflow of A                        |                                     |                 |                 |       |

| bit 12          | COVAERR: Accumulator A Catastrophic Overflow Trap Flag bit |                                 |                                        |                                     |                 |                 |       |

|                 |                                                            | •                               | •                                      | flow of Accumul                     |                 |                 |       |

| bit 11          | -                                                          |                                 |                                        | overflow of Accu<br>Overflow Trap F |                 |                 |       |

|                 |                                                            |                                 | -                                      | flow of Accumul                     | -               |                 |       |

|                 |                                                            |                                 |                                        | overflow of Accu                    |                 |                 |       |

| bit 10          | OVATE: Acc                                                 | umulator A Ov                   | erflow Trap En                         | able bit                            |                 |                 |       |

|                 | 1 = Trap ove<br>0 = Trap is d                              | rflow of Accun<br>isabled       | nulator A                              |                                     |                 |                 |       |

| bit 9           | OVBTE: Acc                                                 | cumulator B O                   | erflow Trap En                         | able bit                            |                 |                 |       |

|                 | 1 = Trap ove<br>0 = Trap is d                              | rflow of Accun<br>isabled       | nulator B                              |                                     |                 |                 |       |

| bit 8           | COVTE: Cat                                                 | astrophic Over                  | flow Trap Enat                         | ole bit                             |                 |                 |       |

|                 | 1 = Trap on 6<br>0 = Trap is d                             | -                               | verflow of Accu                        | mulator A or B is                   | s enabled       |                 |       |

| bit 7           | SFTACERR:                                                  | Shift Accumu                    | lator Error Statu                      | us bit                              |                 |                 |       |

|                 |                                                            | •                               | •                                      | alid accumulator<br>invalid accumul |                 |                 |       |

| bit 6           | DIVOERR: D                                                 | ivide-by-Zero                   | Error Status bit                       |                                     |                 |                 |       |

|                 |                                                            |                                 | used by a divide<br>t caused by a d    | -                                   |                 |                 |       |

| bit 5           |                                                            | nted: Read as                   | -                                      |                                     |                 |                 |       |

| bit 4           | MATHERR:                                                   | Math Error Sta                  | tus bit                                |                                     |                 |                 |       |

|                 |                                                            | or trap has occ                 |                                        |                                     |                 |                 |       |

|                 |                                                            | or trap has not                 | occurred                               |                                     |                 |                 |       |

|                 |                                                            |                                 |                                        |                                     |                 |                 |       |

| bit 3           |                                                            | Address Error<br>error trap has | Trap Status bit                        |                                     |                 |                 |       |

### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

### TABLE 11-10: PORTE REGISTER MAP<sup>(1)</sup>

| IADLE I      | 1-10. F     |             | LOISILI |        |        |        |       |        |        |       |       |       |       |       |       |       |

|--------------|-------------|-------------|---------|--------|--------|--------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| File<br>Name | Bit 15      | Bit 14      | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| TRISE        |             | TRISE<15:0> |         |        |        |        |       |        |        |       |       |       |       |       |       |       |

| PORTE        |             | RE<15:0>    |         |        |        |        |       |        |        |       |       |       |       |       |       |       |

| LATE         | LATE<15:0>  |             |         |        |        |        |       |        |        |       |       |       |       |       |       |       |

| ODCE         |             |             |         |        |        |        |       | ODCE<  | :15:0> |       |       |       |       |       |       |       |

| CNENE        |             |             |         |        |        |        |       | CNIEE< | <15:0> |       |       |       |       |       |       |       |

| CNPUE        |             | CNPUE<15:0> |         |        |        |        |       |        |        |       |       |       |       |       |       |       |

| CNPDE        | CNPDE<15:0> |             |         |        |        |        |       |        |        |       |       |       |       |       |       |       |

| ANSELE       |             | —           | —       | —      | —      | _      | _     | —      | —      |       | _     | _     | _     | _     | _     |       |

**Legend:** — = unimplemented, read as '0'.

Note 1: Refer to Table 11-5 for bit availability on each pin count variant.

| U-0    | R/W-0   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| —      | RP181R6 | RP181R5 | RP181R4 | RP181R3 | RP181R2 | RP181R1 | RP181R0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

|        |         |         |         |         |         |         |         |

| 11-0   | R/W-0   | R/W-0   | R/\/_0  | R/W-0   | R/\\/_0 | R/W-0   | R/\\/_0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | RP180R6 | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 |

| U-0   | R/W-0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 Unimplemented: Read as '0'

bit 14-8 **RP181R<6:0>:** Peripheral Output Function is Assigned to RP181 Output Pin bits (see Table 11-13 for peripheral function numbers)

bit 7 Unimplemented: Read as '0'

bit 6-0 **RP180R<6:0>:** Peripheral Output Function is Assigned to RP180 Output Pin bits (see Table 11-13 for peripheral function numbers)

### **REGISTER 16-17: DTRx: PWMx DEAD-TIME REGISTER (x = 1 to 8)**

| U-0                                                     | U-0   | R/W-0 | R/W-0                              | R/W-0   | R/W-0  | R/W-0 | R/W-0 |

|---------------------------------------------------------|-------|-------|------------------------------------|---------|--------|-------|-------|

| —                                                       | _     |       |                                    | DTRx    | <13:8> |       |       |

| bit 15                                                  |       |       |                                    |         |        |       | bit 8 |

| R/W-0                                                   | R/W-0 | R/W-0 | R/W-0                              | R/W-0   | R/W-0  | R/W-0 | R/W-0 |

|                                                         |       |       | DTF                                | Rx<7:0> |        |       |       |

| bit 7                                                   |       |       |                                    |         |        |       | bit 0 |

| Legend:                                                 |       |       |                                    |         |        |       |       |

| R = Readable bit W = Writable bit                       |       | bit   | U = Unimplemented bit, read as '0' |         |        |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared |       | ared  | x = Bit is unkr                    | nown    |        |       |       |

bit 15-14Unimplemented: Read as '0'bit 13-0DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

### **REGISTER 16-18:** ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER (x = 1 to 8)

|        |       |       |        |         |          | • •   |       |

|--------|-------|-------|--------|---------|----------|-------|-------|

| U-0    | U-0   | R/W-0 | R/W-0  | R/W-0   | R/W-0    | R/W-0 | R/W-0 |

| —      | —     |       |        | ALTDTF  | Rx<13:8> |       |       |

| bit 15 |       |       |        |         |          |       | bit 8 |

|        |       |       |        |         |          |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0   | R/W-0    | R/W-0 | R/W-0 |

|        |       |       | ALTDTI | Rx<7:0> |          |       |       |

| bit 7  |       |       |        |         |          |       | bit 0 |

|        |       |       |        |         |          |       |       |

|        |       |       |        |         |          |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Alternate Dead-Time Value for PWMx Dead-Time Unit bits

|                 | R/W-1             | R/W-0                                | R/W-0                             | R/W-0                 | R/W-0                 | R/W-0           | R/W-0  |

|-----------------|-------------------|--------------------------------------|-----------------------------------|-----------------------|-----------------------|-----------------|--------|

| PENH            | PENL              | POLH                                 | POLL                              | PMOD1 <sup>(1)</sup>  | PMOD0 <sup>(1)</sup>  | OVRENH          | OVRENL |

| bit 15          |                   |                                      |                                   |                       |                       |                 | bit    |

|                 |                   |                                      |                                   |                       |                       |                 |        |

| R/W-0           | R/W-0             | R/W-0                                | R/W-0                             | R/W-0                 | R/W-0                 | R/W-0           | R/W-0  |

| OVRDAT1         | OVRDAT0           | FLTDAT1 <sup>(2)</sup>               | FLTDAT0 <sup>(2)</sup>            | CLDAT1 <sup>(2)</sup> | CLDAT0 <sup>(2)</sup> | SWAP            | OSYNC  |

| bit 7           |                   |                                      |                                   |                       |                       |                 | bit    |

|                 |                   |                                      |                                   |                       |                       |                 |        |

| Legend:         |                   |                                      |                                   |                       |                       |                 |        |

| R = Readable    |                   | W = Writable                         |                                   | •                     | nented bit, read      |                 |        |

| -n = Value at F | POR               | '1' = Bit is set                     |                                   | '0' = Bit is clea     | ared                  | x = Bit is unkr | nown   |

| bit 15          |                   | xH Output Pin                        | Ownorship hit                     |                       |                       |                 |        |

| 511 15          |                   | •                                    | he PWMxH pin                      |                       |                       |                 |        |

|                 |                   | dule controls th                     |                                   |                       |                       |                 |        |

| bit 14          |                   | L Output Pin C                       | -                                 |                       |                       |                 |        |

|                 |                   | •                                    | he PWMxL pin                      |                       |                       |                 |        |

|                 |                   | dule controls th                     |                                   |                       |                       |                 |        |

| bit 13          | POLH: PWM         | xH Output Pin I                      | Polarity bit                      |                       |                       |                 |        |

|                 | 1 = PWMxH p       | oin is active-low                    | /                                 |                       |                       |                 |        |

|                 |                   | oin is active-hig                    |                                   |                       |                       |                 |        |

| bit 12          | POLL: PWMx        | L Output Pin F                       | olarity bit                       |                       |                       |                 |        |

|                 |                   | in is active-low<br>in is active-hig |                                   |                       |                       |                 |        |

| bit 11-10       | PMOD<1:0>:        | PWMx I/O Pin                         | Mode bits <sup>(1)</sup>          |                       |                       |                 |        |

|                 | 11 = PWMx I/      | O pin pair is in                     | the True Indep                    | endent Output         | mode                  |                 |        |

|                 |                   |                                      | the Push-Pull (                   | •                     |                       |                 |        |

|                 |                   |                                      | the Redundant                     |                       |                       |                 |        |

|                 |                   | • •                                  | the Compleme                      |                       | node                  |                 |        |

| bit 9           |                   |                                      | for PWMxH Pin                     |                       |                       |                 |        |

|                 |                   |                                      | i for output on the F             |                       | 1                     |                 |        |

| bit 8           | -                 | -                                    | or PWMxL Pin                      | -                     |                       |                 |        |

| JILO            |                   |                                      | for output on t                   |                       |                       |                 |        |

|                 |                   |                                      | es data for the F                 |                       |                       |                 |        |

| bit 7-6         | •                 | •                                    | /MxH, PWMxL                       |                       | e is Enabled bi       | its             |        |

|                 |                   |                                      | provides data fo                  |                       |                       |                 |        |

|                 |                   |                                      | provides data fo                  |                       |                       |                 |        |

| bit 5-4         |                   | -                                    | MxH and PWM                       | -                     |                       | Enabled bits(2) |        |

|                 |                   |                                      | = 0: Normal Fa                    |                       |                       |                 |        |

|                 |                   |                                      | AT1 provides the                  |                       | PWMxH pin.            |                 |        |

|                 | If Fault is activ | ve, then FLTDA                       | AT0 provides the                  | e state for the       | PWMxL pin.            |                 |        |

|                 |                   |                                      |                                   |                       |                       |                 |        |

|                 | IFLTMOD (FC       |                                      |                                   |                       |                       |                 |        |

|                 | If current limit  | is active, then                      | FLTDAT1 provi<br>AT0 provides the | ides the state f      | for the PWMxH         | l pin.          |        |

### REGISTER 16-20: IOCONX: PWMx I/O CONTROL REGISTER (x = 1 to 8)

2: State represents the active/inactive state of the PWMx depending on the POLH and POLL bits settings.

| bit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                          |

|---------|------------------------|-------------|---------------------------------------------|

|         | PTGWHI(1) or           | 0000        | PWM Special Event Trigger                   |

|         | PTGWLO(1)              | 0001        | PWM master time base synchronization output |

|         |                        | 0010        | PWM1 interrupt                              |

|         |                        | 0011        | PWM2 interrupt                              |

|         |                        | 0100        | PWM3 interrupt                              |

|         |                        | 0101        | PWM4 interrupt                              |

|         |                        | 0110        | PWM5 interrupt                              |

|         |                        | 0111        | OC1 trigger event                           |

|         |                        | 1000        | OC2 trigger event                           |

|         |                        | 1001        | IC1 trigger event                           |

|         |                        | 1010        | CMP1 trigger event                          |

|         |                        | 1011        | CMP2 trigger event                          |

|         |                        | 1100        | CMP3 trigger event                          |

|         |                        | 1101        | CMP4 trigger event                          |

|         |                        | 1110        | ADC conversion done interrupt               |

|         |                        | 1111        | INT2 external interrupt                     |

|         | PTGIRQ(1)              | 0000        | Generate PTG Interrupt 0                    |

|         |                        | 0001        | Generate PTG Interrupt 1                    |

|         |                        | 0010        | Generate PTG Interrupt 2                    |

|         |                        | 0011        | Generate PTG Interrupt 3                    |

|         |                        | 0100        | Reserved                                    |

|         |                        | •           | •                                           |

|         |                        | •           | •                                           |

|         |                        | 1111        | Reserved                                    |

|         | PTGTRIG <sup>(2)</sup> | 00000       | PTGO0                                       |

|         | 1 1 0 1 1 2 0          | 00001       | PTGO1                                       |

|         |                        | •           | •                                           |

|         |                        | •           | •                                           |

|         |                        | •           | •                                           |

|         |                        | 11110       | PTGO30                                      |

|         |                        | 11111       | PTGO31                                      |

### TABLE 17-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 17-2 for the trigger output descriptions.

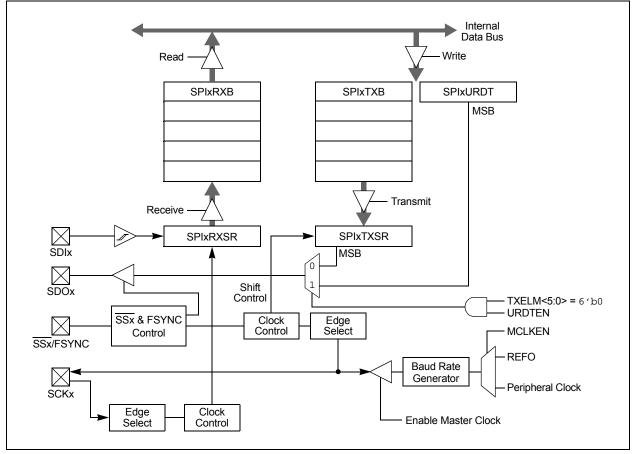

To set up the SPIx module for the Enhanced Buffer Master mode of operation:

- 1. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with MSTEN (SPIxCON1L<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTATL<6>).

- 4. Select Enhanced Buffer mode by setting the ENHBUF bit (SPIxCON1L<0>).

- 5. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

To set up the SPIx module for the Enhanced Buffer Slave mode of operation:

- 1. Clear the SPIxBUFL and SPIxBUFH registers.

- 2. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with the MSTEN bit (SPIxCON1L<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit must be set, thus enabling the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTATL<6>).

- 7. Select Enhanced Buffer mode by setting the ENHBUF bit (SPIxCON1L<0>).

- 8. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

### REGISTER 21-4: CLCxGLSL: CLCx GATE LOGIC INPUT SELECT LOW REGISTER

| R/W-0         | R/W-0                                                                                                                             | R/W-0                                | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|-------------------|------------------|-----------------|-------|--|--|--|--|

| G2D4T         | G2D4N                                                                                                                             | G2D3T                                | G2D3N           | G2D2T             | G2D2N            | G2D1T           | G2D1N |  |  |  |  |

| bit 15        | •                                                                                                                                 |                                      |                 |                   |                  |                 | bit 8 |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                             | R/W-0                                | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

| G1D4T         | G1D4N                                                                                                                             | G1D3T                                | G1D3N           | G1D2T             | G1D2N            | G1D1T           | G1D1N |  |  |  |  |

| bit 7         | GIDHN                                                                                                                             | GIBOI                                | GIDSN           | 01021             | GIDZIN           | 01011           | bit 0 |  |  |  |  |

| Legend:       |                                                                                                                                   |                                      |                 |                   |                  |                 |       |  |  |  |  |

| R = Readable  | e bit                                                                                                                             | W = Writable I                       | oit             | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value at |                                                                                                                                   | '1' = Bit is set                     |                 | '0' = Bit is clea |                  | x = Bit is unkr | nown  |  |  |  |  |

|               |                                                                                                                                   | 2.1.0 001                            |                 | 0 2000 0.00       |                  |                 |       |  |  |  |  |

| bit 15        | G2D4T: Gate                                                                                                                       | 2 Data Source                        | 4 True Enable   | e bit             |                  |                 |       |  |  |  |  |

|               | 1 = Data Source 4 non-inverted signal is enabled for Gate 2                                                                       |                                      |                 |                   |                  |                 |       |  |  |  |  |

|               | 0 = Data Sour                                                                                                                     | rce 4 non-inver                      | ed signal is di | sabled for Gate   | e 2              |                 |       |  |  |  |  |

| bit 14        |                                                                                                                                   | 2 Data Source                        | •               |                   |                  |                 |       |  |  |  |  |

|               |                                                                                                                                   | rce 4 inverted s<br>rce 4 inverted s |                 |                   |                  |                 |       |  |  |  |  |

| bit 13        |                                                                                                                                   | 2 Data Source                        | •               |                   |                  |                 |       |  |  |  |  |

|               | 1 = Data Sour                                                                                                                     | rce 3 non-inver                      | ed signal is er | nabled for Gate   |                  |                 |       |  |  |  |  |

| bit 12        |                                                                                                                                   | 2 Data Source                        | •               |                   |                  |                 |       |  |  |  |  |

| 511 12        | 1 = Data Sour                                                                                                                     | rce 3 inverted s                     | ignal is enable | ed for Gate 2     |                  |                 |       |  |  |  |  |

| bit 11        | <ul> <li>0 = Data Source 3 inverted signal is disabled for Gate 2</li> <li>G2D2T: Gate 2 Data Source 2 True Enable bit</li> </ul> |                                      |                 |                   |                  |                 |       |  |  |  |  |

|               |                                                                                                                                   | rce 2 non-inver<br>rce 2 non-inver   |                 |                   |                  |                 |       |  |  |  |  |

| bit 10        |                                                                                                                                   | 2 Data Source                        | •               |                   |                  |                 |       |  |  |  |  |

|               |                                                                                                                                   | rce 2 inverted s<br>rce 2 inverted s |                 |                   |                  |                 |       |  |  |  |  |

| bit 9         |                                                                                                                                   | 2 Data Source                        | •               |                   |                  |                 |       |  |  |  |  |

|               |                                                                                                                                   | rce 1 non-inver<br>rce 1 non-inver   | •               |                   |                  |                 |       |  |  |  |  |

| bit 8         |                                                                                                                                   | 2 Data Source                        | -               |                   |                  |                 |       |  |  |  |  |

|               |                                                                                                                                   | rce 1 inverted s<br>rce 1 inverted s |                 |                   |                  |                 |       |  |  |  |  |

| bit 7         |                                                                                                                                   | 1 Data Source                        | -               |                   |                  |                 |       |  |  |  |  |

|               |                                                                                                                                   | rce 4 non-inver<br>rce 4 non-inver   |                 |                   |                  |                 |       |  |  |  |  |

| bit 6         |                                                                                                                                   | 1 Data Source                        | -               |                   |                  |                 |       |  |  |  |  |

|               | 1 = Data Sour                                                                                                                     | rce 4 inverted s<br>rce 4 inverted s | ignal is enable | ed for Gate 1     |                  |                 |       |  |  |  |  |

| bit 5         |                                                                                                                                   | 1 Data Source                        | -               |                   |                  |                 |       |  |  |  |  |

|               | 1 = Data Sour                                                                                                                     | rce 3 non-inver<br>rce 3 non-inver   | ed signal is er | nabled for Gate   |                  |                 |       |  |  |  |  |

| bit 4         |                                                                                                                                   | 1 Data Source                        | -               |                   |                  |                 |       |  |  |  |  |

|               | 1 = Data Sour                                                                                                                     | rce 3 inverted s<br>rce 3 inverted s | ignal is enable | ed for Gate 1     |                  |                 |       |  |  |  |  |

### REGISTER 22-17: ADEISTATL: ADC EARLY INTERRUPT STATUS REGISTER LOW

| R/W-0                                                              | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------------------------------------------------------------------|-------|-------|-------|---------|-------|-------|-------|

|                                                                    |       |       | EISTA | T<15:8> |       |       |       |

| bit 15                                                             |       |       |       |         |       |       | bit 8 |

|                                                                    |       |       |       |         |       |       |       |

| R/W-0                                                              | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|                                                                    |       |       | EISTA | AT<7:0> |       |       |       |

| bit 7                                                              |       |       |       |         |       |       | bit 0 |

|                                                                    |       |       |       |         |       |       |       |

| Legend:                                                            |       |       |       |         |       |       |       |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |       |       |       |         |       |       |       |

|                                                                    |       |       |       |         |       |       |       |

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 EISTAT<15:0>: Early Interrupt Status for Corresponding Analog Inputs bits

1 = Early interrupt was generated

0 = Early interrupt was not generated since the last ADCBUFx read

### REGISTER 22-18: ADEISTATH: ADC EARLY INTERRUPT STATUS REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0   | R/W-0 | R/W-0 |

|-------|-----|-------|-------|--------|---------|-------|-------|

| —     | —   |       |       | EISTAT | <21:16> |       |       |

| bit 7 |     |       |       |        |         |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 EISTAT<21:16>: Early Interrupt Status for Corresponding Analog Inputs bits

1 = Early interrupt was generated

0 = Early interrupt was not generated since the last ADCBUFx read

## REGISTER 22-32: ADCMPxENL: ADC DIGITAL COMPARATOR x CHANNEL ENABLE REGISTER LOW (x = 0 or 1)

| bit 15      | R/W/0  | R/W-0 |

|-------------|--------|-------|-------|-------|-------|-------|-------|-------|

| bit 15      |        |       |       |       |       |       |       |       |

|             | bit 15 |       |       |       |       |       |       | bit   |

| CMPEN<15:8> | _      | R/W-0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **CMPEN<15:0>:** Comparator Enable for Corresponding Input Channels bits

0 = Conversion result for corresponding channel is not used by the comparator

## REGISTER 22-33: ADCMPxENH: ADC DIGITAL COMPARATOR x CHANNEL ENABLE REGISTER HIGH (x = 0 or 1)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------|--------------|-------|-------|-------|-------|--|

| —     | —   |       | CMPEN<21:16> |       |       |       |       |  |

| bit 7 |     |       |              |       |       |       | bit 0 |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0

CMPEN<21:16>: Comparator Enable for Corresponding Input Channels bits

1 = Conversion result for corresponding channel is used by the comparator

0 = Conversion result for corresponding channel is not used by the comparator

<sup>1 =</sup> Conversion result for corresponding channel is used by the comparator

### REGISTER 23-10: CxCFG2: CANx BAUD RATE CONFIGURATION REGISTER 2

| U-0             | R/W-x                                                                                                                               | U-0              | U-0            | U-0              | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|------------------|------------------|-----------------|---------|--|--|--|--|

| _               | WAKFIL                                                                                                                              | _                | _              | _                | SEG2PH2          | SEG2PH1         | SEG2PH0 |  |  |  |  |

| bit 15          |                                                                                                                                     |                  |                |                  |                  |                 | bit 8   |  |  |  |  |

|                 |                                                                                                                                     |                  |                |                  |                  |                 |         |  |  |  |  |

| R/W-x           | R/W-x                                                                                                                               | R/W-x            | R/W-x          | R/W-x            | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |

| SEG2PHTS        | SAM                                                                                                                                 | SEG1PH2          | SEG1PH1        | SEG1PH0          | PRSEG2           | PRSEG1          | PRSEG0  |  |  |  |  |

| bit 7           |                                                                                                                                     |                  |                |                  |                  |                 | bit C   |  |  |  |  |

| Legend:         |                                                                                                                                     |                  |                |                  |                  |                 |         |  |  |  |  |

| R = Readable    | bit                                                                                                                                 | W = Writable     | bit            | U = Unimpler     | mented bit, read | l as '0'        |         |  |  |  |  |

| -n = Value at F |                                                                                                                                     | '1' = Bit is set |                | '0' = Bit is cle |                  | x = Bit is unkr | nown    |  |  |  |  |

|                 |                                                                                                                                     |                  |                |                  |                  |                 |         |  |  |  |  |

| bit 15          | Unimplemer                                                                                                                          | ted: Read as '   | )'             |                  |                  |                 |         |  |  |  |  |

| bit 14          |                                                                                                                                     |                  |                |                  |                  |                 |         |  |  |  |  |

|                 | 1 = Uses CAN bus line filter for wake-up<br>0 = CAN bus line filter is not used for wake-up                                         |                  |                |                  |                  |                 |         |  |  |  |  |

|                 |                                                                                                                                     |                  |                | e-up             |                  |                 |         |  |  |  |  |

| bit 13-11       | -                                                                                                                                   | nted: Read as '  |                |                  |                  |                 |         |  |  |  |  |

| oit 10-8        | SEG2PH<2:0>: Phase Segment 2 bits<br>111 = Length is 8 x TQ                                                                         |                  |                |                  |                  |                 |         |  |  |  |  |

|                 |                                                                                                                                     |                  |                |                  |                  |                 |         |  |  |  |  |

|                 | •                                                                                                                                   |                  |                |                  |                  |                 |         |  |  |  |  |

|                 | •                                                                                                                                   | · 4 T-           |                |                  |                  |                 |         |  |  |  |  |

| L:1 7           | 000 = Length                                                                                                                        |                  |                | -4 1- :4         |                  |                 |         |  |  |  |  |

| bit 7           |                                                                                                                                     | Phase Segmer     | it 2 Time Sele |                  |                  |                 |         |  |  |  |  |

|                 | <ol> <li>Freely programmable</li> <li>Maximum of SEG1PHx bits or Information Processing Time (IPT), whichever is greater</li> </ol> |                  |                |                  |                  |                 |         |  |  |  |  |

| bit 6           |                                                                                                                                     | e of the CAN Bu  |                |                  |                  | C               |         |  |  |  |  |

|                 | 1 = Bus line i                                                                                                                      | s sampled three  | e times at the | sample point     |                  |                 |         |  |  |  |  |

|                 |                                                                                                                                     | s sampled once   |                | e point          |                  |                 |         |  |  |  |  |

| bit 5-3         |                                                                                                                                     | D>: Phase Segn   | nent 1 bits    |                  |                  |                 |         |  |  |  |  |

|                 | 111 = Length                                                                                                                        | n is 8 x Tq      |                |                  |                  |                 |         |  |  |  |  |

|                 | •                                                                                                                                   |                  |                |                  |                  |                 |         |  |  |  |  |

|                 | •                                                                                                                                   |                  |                |                  |                  |                 |         |  |  |  |  |

|                 | 000 = Length                                                                                                                        |                  |                |                  |                  |                 |         |  |  |  |  |

| bit 2-0         |                                                                                                                                     | >: Propagation   | Time Segmen    | t bits           |                  |                 |         |  |  |  |  |

|                 | 111 = Length                                                                                                                        | 1 IS 8 X FQ      |                |                  |                  |                 |         |  |  |  |  |

|                 | •                                                                                                                                   |                  |                |                  |                  |                 |         |  |  |  |  |

|                 | •                                                                                                                                   |                  |                |                  |                  |                 |         |  |  |  |  |

|                 | 000 = Length                                                                                                                        |                  |                |                  |                  |                 |         |  |  |  |  |

### 25.2 PGA Resources

Many useful resources are provided on the main product page of the Microchip website for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 25.2.1 KEY RESOURCES

- "Programmable Gain Amplifier (PGA)" (DS70005146) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### REGISTER 25-1: PGAxCON: PGAx CONTROL REGISTER

| R/W-0                             | R/W-0                              | R/W-0            | R/W-0           | R/W-0                                   | R/W-0  | R/W-0    | R/W-0  |  |  |  |  |

|-----------------------------------|------------------------------------|------------------|-----------------|-----------------------------------------|--------|----------|--------|--|--|--|--|

| PGAEN                             | PGAOEN                             | SELPI2           | SELPI1          | SELPI0                                  | SELNI2 | SELNI1   | SELNI0 |  |  |  |  |

| bit 15                            |                                    |                  |                 |                                         |        | <u>.</u> | bit 8  |  |  |  |  |

|                                   |                                    |                  |                 |                                         |        |          |        |  |  |  |  |

| U-0                               | U-0                                | U-0              | U-0             | U-0                                     | R/W-0  | R/W-0    | R/W-0  |  |  |  |  |

| _                                 | _                                  | _                | _               | _                                       | GAIN2  | GAIN1    | GAIN0  |  |  |  |  |

| bit 7                             |                                    | •                |                 |                                         |        |          | bit C  |  |  |  |  |

|                                   |                                    |                  |                 |                                         |        |          |        |  |  |  |  |

| Legend:                           |                                    |                  |                 |                                         |        |          |        |  |  |  |  |

| R = Readable bit W = Writable bit |                                    |                  | bit             | U = Unimplemented bit, read as '0'      |        |          |        |  |  |  |  |

| -n = Value at                     | -n = Value at POR '1' = Bit is set |                  |                 | '0' = Bit is cleared x = Bit is unknown |        |          |        |  |  |  |  |

|                                   |                                    |                  |                 |                                         |        |          |        |  |  |  |  |

| bit 15                            | PGAEN: PGAx Enable bit             |                  |                 |                                         |        |          |        |  |  |  |  |

|                                   | 1 = PGAx module is enabled         |                  |                 |                                         |        |          |        |  |  |  |  |

|                                   | 0 = PGAx mo                        | odule is disable | d (reduces po   | wer consumpt                            | ion)   |          |        |  |  |  |  |

| bit 14                            | PGAOEN: PO                         | GAx Output En    | able bit        |                                         |        |          |        |  |  |  |  |

|                                   | 1 = PGAx out                       | tput is connect  | ed to the DAC   | OUTx pin                                |        |          |        |  |  |  |  |

|                                   | 0 = PGAx out                       | tput is not conr | nected to the I | DACOUTx pin                             |        |          |        |  |  |  |  |

| bit 13-11                         | SELPI<2:0>:                        | PGAx Positive    | e Input Selecti | on bits                                 |        |          |        |  |  |  |  |

|                                   | 111 = Reserv                       | ved              |                 |                                         |        |          |        |  |  |  |  |

|                                   | 110 = Reserv                       | ved              |                 |                                         |        |          |        |  |  |  |  |

|                                   | 101 = Reserved                     |                  |                 |                                         |        |          |        |  |  |  |  |

|                                   | 100 = Reserv                       | 100 = Reserved   |                 |                                         |        |          |        |  |  |  |  |

|                                   | 011 = PGAxF                        | -                |                 |                                         |        |          |        |  |  |  |  |

|                                   | 010 = PGAxF                        | 010 = PGAxP3     |                 |                                         |        |          |        |  |  |  |  |

|                                   |                                    | 22               |                 |                                         |        |          |        |  |  |  |  |

001 = PGAxP2 000 = PGAxP1

## bit 10-8 **SELNI<2:0>:** PGAx Negative Input Selection bits

- 111 = Reserved 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = Ground (Single-Ended mode)

- 010 = PGAxN3

- 001 = PGAxN2

- 000 = Ground (Single-Ended mode)

- bit 7-3 Unimplemented: Read as '0'

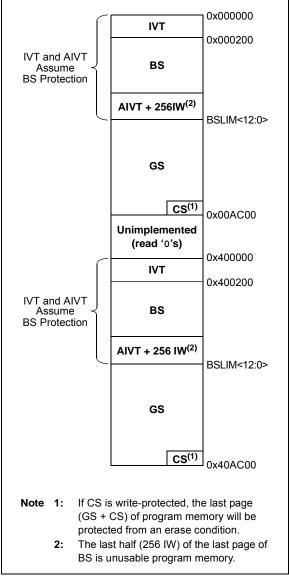

### FIGURE 27-5: SECURITY SEGMENTS EXAMPLE FOR dsPIC33EP128GS70X/80X DEVICES (DUAL PARTITION MODES)

| AC CHARACTERISTICS |           |                                                              |                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |               |       |                                                                            |  |  |

|--------------------|-----------|--------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-------|----------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                |                     | Min.                                                                                                                                                                                                                                                                                | Тур. | Max.          | Units | Conditions                                                                 |  |  |

| TB10               | TtxH      | TxCK High<br>Time                                            | Synchronous<br>mode | Greater of:<br>20 or<br>(TCY + 20)/N                                                                                                                                                                                                                                                | _    | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescale Value<br>(1, 8, 64, 256) |  |  |

| TB11               | TtxL      | TxCK Low<br>Time                                             | Synchronous<br>mode | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                                                                                                                                                |      | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescale Value<br>(1, 8, 64, 256) |  |  |

| TB15               | TtxP      | TxCK<br>Input<br>Period                                      | Synchronous<br>mode | Greater of:<br>40 or<br>(2 Tcy + 40)/N                                                                                                                                                                                                                                              | —    | _             | ns    | N = Prescale Value<br>(1, 8, 64, 256)                                      |  |  |

| TB20               | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                     | 0.75 Tcy + 40                                                                                                                                                                                                                                                                       | _    | 1.75 Tcy + 40 | ns    |                                                                            |  |  |

### TABLE 30-25: TIMER2 AND TIMER4 (TYPE B TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

**Note 1:** These parameters are characterized but not tested in manufacturing.

### TABLE 30-26: TIMER3 AND TIMER5 (TYPE C TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                             |                         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |               |       |                                       |  |  |

|--------------------|-----------|---------------------------------------------|-------------------------|------------------------------------------------------|------|---------------|-------|---------------------------------------|--|--|

| Param<br>No.       | Symbol    | Charact                                     | teristic <sup>(1)</sup> | Min.                                                 | Тур. | Max.          | Units | Conditions                            |  |  |

| TC10               | TtxH      | TxCK High Synchronous<br>Time               |                         | Tcy + 20                                             |      |               | ns    | Must also meet<br>Parameter TC15      |  |  |

| TC11               | TtxL      | TxCK Low Synchronous<br>Time                |                         | Tcy + 20                                             | _    | —             | ns    | Must also meet<br>Parameter TC15      |  |  |

| TC15               | TtxP      | TxCK InputSynchronousPeriodwith Prescaler   |                         | 2 Tcy + 40                                           | _    | —             | ns    | N = Prescale Value<br>(1, 8, 64, 256) |  |  |

| TC20               | TCKEXTMRL | Delay from Ex<br>Clock Edge to<br>Increment |                         | 0.75 Tcy + 40                                        |      | 1.75 Tcy + 40 | ns    |                                       |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

| AC CHARACTERISTICS        |                        |         | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(2)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                     |      |       |                                       |  |  |  |

|---------------------------|------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|---------------------------------------|--|--|--|

| Param<br>No.              | Symbol Characteristics |         | Min.                                                                                                                                                                                                                                                                                    | Тур. <sup>(1)</sup> | Max. | Units | Conditions                            |  |  |  |

| Clock Parameters          |                        |         |                                                                                                                                                                                                                                                                                         |                     |      |       |                                       |  |  |  |

| AD50 TAD ADC Clock Period |                        | 14.28   | _                                                                                                                                                                                                                                                                                       | _                   | ns   |       |                                       |  |  |  |

|                           | Throughput Rate        |         |                                                                                                                                                                                                                                                                                         |                     |      |       |                                       |  |  |  |

| AD51                      | Ftp                    | SH0-SH3 | _                                                                                                                                                                                                                                                                                       | _                   | 3.25 |       | 70 MHz ADC clock, 12 bits, no pending |  |  |  |

|                           |                        | SH4     | _                                                                                                                                                                                                                                                                                       | —                   | 3.25 | Msps  | conversion at time of trigger         |  |  |  |

### TABLE 30-53: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

2: The ADC module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is ensured, but not characterized.

### TABLE 30-54: HIGH-SPEED ANALOG COMPARATOR MODULE SPECIFICATIONS

| AC/DC CHARACTERISTICS |                       |                                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(2)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                                                                                                                             |  |  |

|-----------------------|-----------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.          | Symbol Characteristic |                                                   | Min.                                                                                                                                                                                                                                                                                          | Тур. | Max. | Units | Comments                                                                                                                    |  |  |

| CM10                  | VIOFF                 | Input Offset Voltage                              | -35                                                                                                                                                                                                                                                                                           | ±5   | 35   | mV    |                                                                                                                             |  |  |

| CM11                  | VICM                  | Input Common-Mode<br>Voltage Range <sup>(1)</sup> | 0                                                                                                                                                                                                                                                                                             | —    | AVDD | V     |                                                                                                                             |  |  |