Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                          |

| Number of I/O              | 20                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 11x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

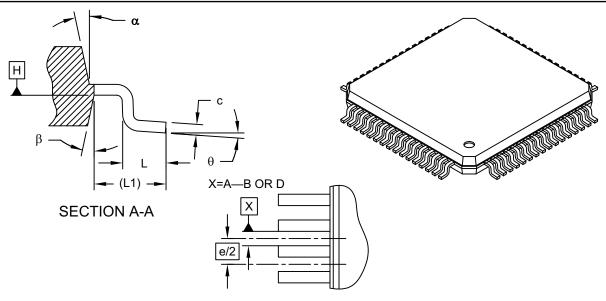

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs702-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

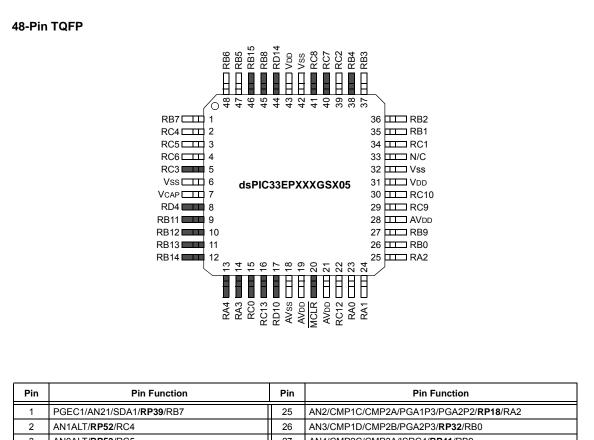

### **Pin Diagrams (Continued)**

| 2  | AN1ALT/RP52/RC4                  | 26 | AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0           |

|----|----------------------------------|----|-------------------------------------------|

| 3  | AN0ALT/RP53/RC5                  | 27 | AN4/CMP2C/CMP3A/ISRC4/RP41/RB9            |

| 4  | AN17/ <b>RP54</b> /RC6           | 28 | AVDD                                      |

| 5  | RP51/RC3                         | 29 | AN11/PGA1N3/ <b>RP57</b> /RC9             |

| 6  | Vss                              | 30 | EXTREF2/AN10/PGA1P4/ <b>RP58</b> /RC10    |

| 7  | VCAP                             | 31 | VDD                                       |

| 8  | RP68/RD4                         | 32 | Vss                                       |

| 9  | TMS/PWM3H/RP43/RB11              | 33 | N/C                                       |

| 10 | TCK/PWM3L/RP44/RB12              | 34 | AN8/CMP4C/PGA2P4/RP49/RC1                 |

| 11 | PWM2H/ <b>RP45</b> /RB13         | 35 | OSCI/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1  |

| 12 | PWM2L/RP46/RB14                  | 36 | OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2 |

| 13 | PWM1H/ <b>RP20</b> /RA4          | 37 | PGED2/DACOUT1/AN18/INT0/RP35/RB3          |

| 14 | PWM1L/ <b>RP19</b> /RA3          | 38 | PGEC2/ADTRG31/ <b>RP36</b> /RB4           |

| 15 | FLT12/ <b>RP48</b> /RC0          | 39 | EXTREF1/AN9/CMP4D/RP50/RC2                |

| 16 | FLT11/ <b>RP61</b> /RC13         | 40 | ASDA1/RP55/RC7                            |

| 17 | CLC4OUT/FLT10/RP74/RD10          | 41 | ASCL1/RP56/RC8                            |

| 18 | AVss                             | 42 | Vss                                       |

| 19 | AVDD                             | 43 | VDD                                       |

| 20 | MCLR                             | 44 | CLC3OUT/RD14                              |

| 21 | AVDD                             | 45 | PGED3/SDA2/FLT31/RP40/RB8                 |

| 22 | AN14/PGA2N3/RP60/RC12            | 46 | PGEC3/SCL2/RP47/RB15                      |

| 23 | AN0/CMP1A/PGA1P1/RP16/RA0        | 47 | TDO/AN19/PGA2N2/ <b>RP37</b> /RB5         |

| 24 | AN1/CMP1B/PGA1P2/PGA2P1/RP17/RA1 | 48 | PGED1/TDI/AN20/SCL1/RP38/RB6              |

Legend: Shaded pins are up to 5 VDC tolerant.

**RPn** represents remappable peripheral functions. See Table 11-12 and Table 11-13 for the complete list of remappable sources.

| Pin Name <sup>(1)</sup>    | Pin<br>Type | Buffer<br>Type | PPS                | Description                                               |

|----------------------------|-------------|----------------|--------------------|-----------------------------------------------------------|

| U2CTS                      | I           | ST             | Yes                | UART2 Clear-to-Send.                                      |

| U2RTS                      | 0           | —              | Yes                | UART2 Ready-to-Send.                                      |

| U2RX                       |             | ST             | Yes                | UART2 receive.                                            |

| U2TX                       | 0           |                | Yes                | UART2 transmit.                                           |

| BCLK2                      | 0           | ST             | Yes                | UART2 IrDA baud clock output.                             |

| SCK1                       | I/O         | ST             | Yes                | Synchronous serial clock input/output for SPI1.           |

| SDI1                       |             | ST             | Yes                | SPI1 data in.                                             |

| SDO1                       | 0           |                | Yes                | SPI1 data out.                                            |

| SS1                        | I/O         | ST             | Yes                | SPI1 slave synchronization or frame pulse I/O.            |

| SCK2                       | I/O         | ST             | Yes                | Synchronous serial clock input/output for SPI2.           |

| SDI2                       | I           | ST             | Yes                | SPI2 data in.                                             |

| SDO2                       | 0           | —              | Yes                | SPI2 data out.                                            |

| SS2                        | I/O         | ST             | Yes                | SPI2 slave synchronization or frame pulse I/O.            |

| SCK3                       | I/O         | ST             | Yes <sup>(3)</sup> | Synchronous serial clock input/output for SPI3.           |

| SDI3                       | 1           | ST             | Yes                | SPI3 data in.                                             |

| SDO3                       | 0           | —              | Yes                | SPI3 data out.                                            |

| SS3                        | I/O         | ST             | Yes                | SPI3 slave synchronization or frame pulse I/O.            |

| SCL1                       | I/O         | ST             | No                 | Synchronous serial clock input/output for I2C1.           |

| SDA1                       | I/O         | ST             | No                 | Synchronous serial data input/output for I2C1.            |

| ASCL1                      | I/O         | ST             | No                 | Alternate synchronous serial clock input/output for I2C1. |

| ASDA1                      | I/O         | ST             | No                 | Alternate synchronous serial data input/output for I2C1.  |

| SCL2                       | I/O         | ST             | No                 | Synchronous serial clock input/output for I2C2.           |

| SDA2                       | I/O         | ST             | No                 | Synchronous serial data input/output for I2C2.            |

| ASCL2                      | I/O         | ST             | No                 | Alternate synchronous serial clock input/output for I2C2. |

| ASDA2                      | I/O         | ST             | No                 | Alternate synchronous serial data input/output for I2C2.  |

| TMS                        | I           | ST             | No                 | JTAG Test mode select pin.                                |

| ТСК                        | I           | ST             | No                 | JTAG test clock input pin.                                |

| TDI                        | 1           | ST             | No                 | JTAG test data input pin.                                 |

| TDO                        | 0           | —              | No                 | JTAG test data output pin.                                |

| FLT1-FLT8                  | 1           | ST             | Yes                | PWM Fault Inputs 1 through 8.                             |

| FLT9-FLT12                 | I           | ST             | No                 | PWM Fault Inputs 9 through 12.                            |

| PWM1L-PWM3L                | 0           | —              | No                 | PWM Low Outputs 1 through 3.                              |

| PWM1H-PWM3H                | 0           | —              | No                 | PWM High Outputs 1 through 3.                             |

| PWM4L-PWM8L <sup>(2)</sup> | 0           | —              | Yes                | PWM Low Outputs 4 through 8.                              |

| PWM4H-PWM8H <sup>(2)</sup> | 0           | —              | Yes                | PWM High Outputs 4 through 8.                             |

| SYNCI1, SYNCI2             | I.          | ST             | Yes                | PWM Synchronization Inputs 1 and 2.                       |

| SYNCO1, SYNCO2             | 0           |                | Yes                | PWM Synchronization Outputs 1 and 2.                      |

| Legend: CMOS = C           |             |                |                    |                                                           |

| ST = Schm                  | itt Trigg   | jer input      | with CN            | IOS levels O = Output I = Input                           |

#### TABLE 1-1. PINOUT I/O DESCRIPTIONS (CONTINUED)

PPS = Peripheral Pin Select TTL = TTL input buffer 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

2: PWM4H/L through PWM8H/L are fixed on dsPIC33EPXXXGS708/808 devices. PWM4H/L through PWM6H/L are fixed on dsPIC33EPXXXGS706/806 devices.

3: The SCK3 pin is fixed on dsPIC33EPXXXGS706/806 and dsPIC33EPXXXGS708/808 devices.

4: PPS is available on dsPIC33EPXXXGS702 devices only.

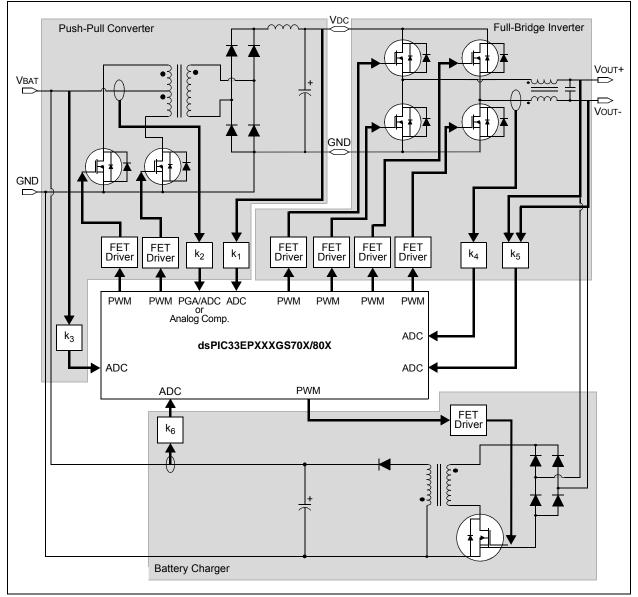

### FIGURE 2-6: OFF-LINE UPS

| Register        | Address       | All Resets                              | Register  | Address | All Resets                              | Register  | Address | All Resets                              |

|-----------------|---------------|-----------------------------------------|-----------|---------|-----------------------------------------|-----------|---------|-----------------------------------------|

| I2C1 and I2C    | I2C1 and I2C2 |                                         | U1STA     | 222     | 000000010010000                         | SPI1BRGH  | 252     | 000000000000000000000000000000000000000 |

| I2C1CONL        | 200           | 0001000000000000                        | U1TXREG   | 224     | 0000000xxxxxxxxx                        | SPI1IMSKL | 254     | 000000000000000000000000000000000000000 |

| I2C1CONH        | 202           | 000000000000000000000000000000000000000 | U1RXREG   | 226     | 000000000000000000000000000000000000000 | SPI1IMSKH | 256     | 000000000000000000000000000000000000000 |

| I2C1STAT        | 204           | 000000000000000000000000000000000000000 | U1BRG     | 228     | 000000000000000000000000000000000000000 | SPI1URDTL | 258     | 000000000000000000000000000000000000000 |

| I2C1ADD         | 206           | 000000000000000000000000000000000000000 | U2MODE    | 230     | 000000000000000000000000000000000000000 | SPI1URDTH | 25A     | 000000000000000000000000000000000000000 |

| I2C1MSK         | 208           | 000000000000000000000000000000000000000 | U2STA     | 232     | 000000010010000                         | SPI2CON1L | 260     | 000000000000000000000000000000000000000 |

| I2C1BRG         | 20A           | 000000000000000000000000000000000000000 | U2TXREG   | 234     | 0000000xxxxxxxxx                        | SPI2CON1H | 262     | 000000000000000000000000000000000000000 |

| I2C1TRN         | 20C           | 0000000011111111                        | U2RXREG   | 236     | 000000000000000000000000000000000000000 | SPI2CON2L | 264     | 000000000000000000000000000000000000000 |

| I2C1RCV         | 20E           | 000000000000000000000000000000000000000 | U2BRG     | 238     | 000000000000000000000000000000000000000 | SPI2CON2H | 266     | 000000000000000000000000000000000000000 |

| I2C2CON1        | 210           | 0001000000000000                        | SPI       |         |                                         | SPI2STATL | 268     | 0000000000101000                        |

| I2C2CON2        | 212           | 000000000000000000000000000000000000000 | SPI1CON1L | 240     | 000000000000000000000000000000000000000 | SPI2STATH | 26A     | 000000000000000000000000000000000000000 |

| I2C2STAT        | 214           | 000000000000000000000000000000000000000 | SPI1CON1H | 242     | 000000000000000000000000000000000000000 | SPI2BUFL  | 26C     | 000000000000000000000000000000000000000 |

| I2C2ADD         | 216           | 000000000000000000000000000000000000000 | SPI1CON2L | 244     | 000000000000000000000000000000000000000 | SPI2BUFH  | 26E     | 000000000000000000000000000000000000000 |

| I2C2MSK         | 218           | 000000000000000000000000000000000000000 | SPI1CON2H | 246     | 000000000000000000000000000000000000000 | SPI3STAT  | 270     | 000xxxxxxxxxxxx                         |

| I2C2BRG         | 21A           | 000000000000000000000000000000000000000 | SPI1STATL | 248     | 000000000101000                         | SPI2BRGH  | 272     | 000000000000000000000000000000000000000 |

| I2C2TRN         | 21C           | 0000000011111111                        | SPI1STATH | 24A     | 000000000000000000000000000000000000000 | SPI2IMSKL | 274     | 000000000000000000000000000000000000000 |

| I2C2RCV         | 21E           | 000000000000000000000000000000000000000 | SPI1BUFL  | 24C     | 000000000000000000000000000000000000000 | SPI2IMSKH | 276     | 000000000000000000000000000000000000000 |

| UART1 and UART2 |               |                                         | SPI1BUFH  | 24E     | 000000000000000000000000000000000000000 | SPI2URDTL | 278     | 000000000000000000000000000000000000000 |

| U1MODE          | 220           | 000000000000000000000000000000000000000 | SPI1BRGL  | 250     | 000xxxxxxxxxxx                          | SPI2URDTH | 27A     | 000000000000000000000000000000000000000 |

TABLE 4-4: SFR BLOCK 200h

Legend: x = unknown or indeterminate value. Address values are in hexadecimal. Reset values are in binary.

### TABLE 4-5: SFR BLOCK 300h

| Register  | Address | All Resets                              | Register  | Address | All Resets         | Register  | Address | All Resets                              |

|-----------|---------|-----------------------------------------|-----------|---------|--------------------|-----------|---------|-----------------------------------------|

| ADC       |         |                                         | ADCMP0ENH | 33A     | 000000000000000000 | ADTRIG4L  | 390     | 000000000000000000000000000000000000000 |

| ADCON1L   | 300     | 000000000000000000                      | ADCMP0LO  | 33C     | 000000000000000000 | ADTRIG4H  | 392     | 000000000000000000000000000000000000000 |

| ADCON1H   | 302     | 000000001100000                         | ADCMP0HI  | 33E     | 000000000000000000 | ADCMP0CON | 3A0     | 000000000000000000000000000000000000000 |

| ADCON2L   | 304     | 000000000000000000                      | ADCMP1ENL | 340     | 000000000000000000 | ADCMP1CON | 3A4     | 000000000000000000000000000000000000000 |

| ADCON2H   | 306     | 000000000000000000                      | ADCMP1ENH | 342     | 000000000000000000 | ADBASE    | 3C0     | 000000000000000000000000000000000000000 |

| ADCON3L   | 308     | 000000000000000000                      | ADCMP1LO  | 344     | 000000000000000000 | ADLVLTRGL | 3D0     | 000000000000000000000000000000000000000 |

| ADCON3H   | 30A     | 000000000000000000000000000000000000000 | ADCMP1HI  | 346     | 000000000000000000 | ADLVLTRGH | 3D2     | 000000000000000000000000000000000000000 |

| ADCON4L   | 30C     | 000000000000000000000000000000000000000 | ADFL0DAT  | 368     | 000000000000000000 | ADCORE0L  | 3D4     | 000000000000000000000000000000000000000 |

| ADCON4H   | 30E     | 000000000000000000000000000000000000000 | ADFL0CON  | 36A     | 000000000000000000 | ADCORE0H  | 3D6     | 0000001100000000                        |

| ADMOD0L   | 310     | 000000000000000000000000000000000000000 | ADFL1DAT  | 36C     | 000000000000000000 | ADCORE1L  | 3D8     | 000000000000000000000000000000000000000 |

| ADMOD0H   | 312     | 000000000000000000000000000000000000000 | ADFL1CON  | 36E     | 000000000000000000 | ADCORE1H  | 3DA     | 0000001100000000                        |

| ADMOD1L   | 314     | 000000000000000000000000000000000000000 | ADTRIG0L  | 380     | 000000000000000000 | ADCORE2L  | 3DC     | 000000000000000000000000000000000000000 |

| ADIEL     | 320     | 000000000000000000000000000000000000000 | ADTRIG0H  | 382     | 000000000000000000 | ADCORE2H  | 3DE     | 0000001100000000                        |

| ADIEH     | 322     | 000000000000000000000000000000000000000 | ADTRIG1L  | 384     | 000000000000000000 | ADCORE3L  | 3E0     | 000000000000000000000000000000000000000 |

| ADCSS1L   | 328     | 000000000000000000000000000000000000000 | ADTRIG1H  | 386     | 000000000000000000 | ADCORE3H  | 3E2     | 0000001100000000                        |

| ADCSS1H   | 32A     | 000000000000000000000000000000000000000 | ADTRIG2L  | 388     | 000000000000000000 | ADEIEL    | 3F0     | 000000000000000000000000000000000000000 |

| ADSTATL   | 330     | 000000000000000000                      | ADTRIG2H  | 38A     | 000000000000000000 | ADEIEH    | 3F2     | 000000000000000000000000000000000000000 |

| ADSTATH   | 332     | 000000000000000000                      | ADTRIG3L  | 38C     | 000000000000000000 | ADEISTATL | 3F8     | 000000000000000000000000000000000000000 |

| ADCMP0ENL | 338     | 000000000000000000                      | ADTRIG3H  | 38E     | 000000000000000000 | ADEISTATH | 3FA     | 000000000000000000000000000000000000000 |

Legend: x = unknown or indeterminate value. Address values are in hexadecimal. Reset values are in binary.

| Register | Address | All Resets         | Register | Address | All Resets                              | Register | Address | All Resets                              |

|----------|---------|--------------------|----------|---------|-----------------------------------------|----------|---------|-----------------------------------------|

| PORTA    |         |                    | ANSELB   | E1E     | 0000001011101111                        | CNPDD    | E3C     | 000000000000000000000000000000000000000 |

| TRISA    | E00     | 000000000011111    | PORTC    |         |                                         | ANSELD   | E3E     | 0110000110100000                        |

| PORTA    | E02     | 000000000000000000 | TRISC    | E20     | 0111011111111111                        | PORTE    |         |                                         |

| LATA     | E04     | 000000000000000000 | PORTC    | E22     | 000000000000000000                      | TRISE    | E40     | 11111111111111111                       |

| ODCA     | E06     | 000000000000000000 | LATC     | E24     | 000000000000000000                      | PORTE    | E42     | 000000000000000000                      |

| CNENA    | E08     | 000000000000000000 | ODCC     | E26     | 000000000000000000                      | LATE     | E44     | 000000000000000000                      |

| CNPUA    | E0A     | 000000000000000000 | CNENC    | E28     | 000000000000000000                      | ODCE     | E46     | 000000000000000000                      |

| CNPDA    | E0C     | 000000000000000000 | CNPUC    | E2A     | 000000000000000000                      | CNENE    | E48     | 000000000000000000                      |

| ANSELA   | E0E     | 000000000000111    | CNPDC    | E2C     | 000000000000000000                      | CNPUE    | E4A     | 000000000000000000                      |

| PORTB    |         |                    | ANSELC   | E2E     | 0001011001110111                        | CNPDE    | E4C     | 000000000000000000000000000000000000000 |

| TRISB    | E10     | 0111101111111111   | PORTD    |         |                                         | ANSELE   | E4E     | 110000010000000                         |

| PORTB    | E12     | 000000000000000000 | TRISD    | E30     | 111111111111111111                      | CPU      |         |                                         |

| LATB     | E14     | 000000000000000000 | PORTD    | E32     | 000000000000000000                      | VISI     | F88     | 000000000000000000                      |

| ODCB     | E16     | 00000000000000000  | LATD     | E34     | 000000000000000000000000000000000000000 | JTAG     |         |                                         |

| CNENB    | E18     | 000000000000000000 | ODCD     | E36     | 000000000000000000                      | JDATAH   | FF0     | 00000000000000000                       |

| CNPUB    | E1A     | 000000000000000000 | CNEND    | E38     | 000000000000000000                      | JDATAL   | FF2     | 000000000000000000                      |

| CNPDB    | E1C     | 000000000000000000 | CNPUD    | E3A     | 00000000000000000                       |          |         |                                         |

### TABLE 4-15: SFR BLOCK E00h-F00h

Legend: x = unknown or indeterminate value. Address values are in hexadecimal. Reset values are in binary.

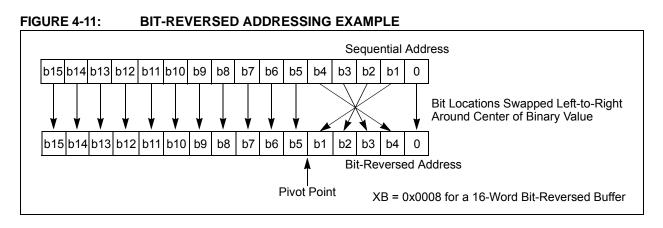

### TABLE 4-18: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      |    |    | Bit-Rev | ersed Ac | ldress  |

|----|----|-------|-----------|---------|----|----|---------|----------|---------|

| A3 | A2 | A1    | A0        | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0  | 0     | 1         | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0  | 1     | 0         | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0  | 1     | 1         | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1  | 0     | 0         | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1  | 0     | 1         | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1  | 1     | 0         | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1  | 1     | 1         | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0  | 0     | 0         | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0  | 0     | 1         | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0  | 1     | 0         | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0  | 1     | 1         | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1  | 0     | 0         | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1  | 0     | 1         | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1  | 1     | 0         | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1  | 1     | 1         | 15      | 1  | 1  | 1       | 1        | 15      |

| U-0             | U-0                                                                             | U-0                                  | U-0         | R-0              | R-0              | R-0             | R-0    |  |  |  |

|-----------------|---------------------------------------------------------------------------------|--------------------------------------|-------------|------------------|------------------|-----------------|--------|--|--|--|

| —               | —                                                                               | —                                    | _           | ILR3             | ILR2             | ILR1            | ILR0   |  |  |  |

| bit 15          |                                                                                 |                                      |             |                  |                  |                 | bit    |  |  |  |

|                 |                                                                                 |                                      |             |                  |                  |                 |        |  |  |  |

| R-0             | R-0                                                                             | R-0                                  | R-0         | R-0              | R-0              | R-0             | R-0    |  |  |  |

| VECNUM7         | VECNUM6                                                                         | VECNUM5                              | VECNUM4     | VECNUM3          | VECNUM2          | VECNUM1         | VECNUM |  |  |  |

| bit 7           |                                                                                 |                                      |             |                  |                  |                 | bit    |  |  |  |

| Legend:         |                                                                                 |                                      |             |                  |                  |                 |        |  |  |  |

| R = Readable    | bit                                                                             | W = Writable                         | bit         | U = Unimpler     | nented bit, read | l as '0'        |        |  |  |  |

| -n = Value at F | POR                                                                             | '1' = Bit is set                     |             | '0' = Bit is cle | ared             | x = Bit is unki | nown   |  |  |  |

|                 |                                                                                 |                                      |             |                  |                  |                 |        |  |  |  |

| bit 15-12       | Unimplemen                                                                      | ted: Read as '                       | 0'          |                  |                  |                 |        |  |  |  |

| bit 11-8        | ILR<3:0>: New CPU Interrupt Priority Level bits                                 |                                      |             |                  |                  |                 |        |  |  |  |

|                 | 1111 = CPU Interrupt Priority Level is 15                                       |                                      |             |                  |                  |                 |        |  |  |  |

|                 | •                                                                               |                                      |             |                  |                  |                 |        |  |  |  |

|                 |                                                                                 |                                      |             |                  |                  |                 |        |  |  |  |

|                 | •<br>0001 = CPU                                                                 | Interrupt Priorit                    | v Lovolis 1 |                  |                  |                 |        |  |  |  |

|                 |                                                                                 | Interrupt Priorit                    |             |                  |                  |                 |        |  |  |  |

| bit 7-0         | VECNUM<7:0>: Vector Number of Pending Interrupt bits                            |                                      |             |                  |                  |                 |        |  |  |  |

|                 | 11111111 = 255, Reserved; do not use                                            |                                      |             |                  |                  |                 |        |  |  |  |

|                 | •                                                                               |                                      |             |                  |                  |                 |        |  |  |  |

|                 | •                                                                               |                                      |             |                  |                  |                 |        |  |  |  |

|                 | •                                                                               |                                      |             |                  |                  |                 |        |  |  |  |

|                 | 00001001 = 9, IC1 - Input Capture 1                                             |                                      |             |                  |                  |                 |        |  |  |  |

|                 | 00001000 = 8, INT0 – External Interrupt 0<br>00000111 = 7, Reserved; do not use |                                      |             |                  |                  |                 |        |  |  |  |

|                 | 00000111 - 7, Reserved, do not use<br>00000110 = 6, Generic soft error trap     |                                      |             |                  |                  |                 |        |  |  |  |

|                 | 00000101 = 5, Reserved; do not use                                              |                                      |             |                  |                  |                 |        |  |  |  |

|                 | 00000100 =                                                                      | 4, Math error tr                     | ар          |                  |                  |                 |        |  |  |  |

|                 |                                                                                 | 3, Stack error t                     |             |                  |                  |                 |        |  |  |  |

|                 |                                                                                 | 2, Generic har                       |             |                  |                  |                 |        |  |  |  |

|                 |                                                                                 | 1, Address erro<br>0, Oscillator fai |             |                  |                  |                 |        |  |  |  |

|                 | - 00000000 –                                                                    | o, Oscillator Id                     | nuap        |                  |                  |                 |        |  |  |  |

### REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme, based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA Channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU Interrupt after Half or Full Block Transfer Complete

- Byte or Word Transfers

- · Fixed Priority Channel Arbitration

- Manual (software) or Automatic (peripheral DMA requests) Transfer Initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM Start addresses after each block transfer complete)

- DMA Request for each Channel can be Selected from any Supported Interrupt Source

- Debug Support Features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA<br>Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|----------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0      | 00000000                             | —                                                       | _                                                      |

| IC1 – Input Capture 1            | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2            | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3            | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4            | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1           | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2           | 00000110                             | —                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3           | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4           | 00011010                             | _                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                    | 00000111                             | —                                                       | —                                                      |

| TMR3 – Timer3                    | 00001000                             | —                                                       | —                                                      |

| TMR4 – Timer4                    | 00011011                             | —                                                       | —                                                      |

| TMR5 – Timer5                    | 00011100                             | —                                                       | —                                                      |

| UART1RX – UART1 Receiver         | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter      | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver         | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter      | 00011111                             | _                                                       | 0x0234 (U2TXREG)                                       |

| CAN1 – RX Data Ready             | 00100010                             | 0x0440 (C1RXD)                                          |                                                        |

| CAN1 – TX Data Request           | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| CAN2 – RX Data Ready             | 00110111                             | 0X0540(C2RXD)                                           | _                                                      |

| CAN2 – TX Data Request           | 01000111                             | _                                                       | 0X0542(C2TXD)                                          |

### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

| U-0                               | R/W-0  | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |

|-----------------------------------|--------|------------------|--------|------------------------------------|--------|--------------------|--------|--|

| —                                 | RP53R6 | RP53R5           | RP53R4 | RP53R3                             | RP53R2 | RP53R1             | RP53R0 |  |

| bit 15                            |        |                  |        |                                    |        |                    | bit 8  |  |

|                                   |        |                  |        |                                    |        |                    |        |  |

| U-0                               | R/W-0  | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |

| —                                 | RP52R6 | RP52R5           | RP52R4 | RP52R3                             | RP52R2 | RP52R1             | RP52R0 |  |

| bit 7                             |        |                  |        |                                    |        |                    | bit 0  |  |

|                                   |        |                  |        |                                    |        |                    |        |  |

| Legend:                           |        |                  |        |                                    |        |                    |        |  |

| R = Readable bit W = Writable bit |        |                  | bit    | U = Unimplemented bit, read as '0' |        |                    |        |  |

| -n = Value at POR                 |        | '1' = Bit is set |        | '0' = Bit is cleared               |        | x = Bit is unknown |        |  |

### REGISTER 11-45: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

| bit 15   | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-8 | <b>RP53R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP53 Output Pin bits (see Table 11-13 for peripheral function numbers) |

| bit 7    | Unimplemented: Read as '0'                                                                                                                |

| bit 6-0  | <b>RP52R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP52 Output Pin bits (see Table 11-13 for peripheral function numbers) |

#### **REGISTER 11-46: RPOR13: PERIPHERAL PIN SELECT OUTPUT REGISTER 13**

| U-0           | R/W-0                                 | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |

|---------------|---------------------------------------|------------------|--------|------------------|------------------|-----------------|--------|--|--|

| —             | RP55R6                                | RP55R5           | RP55R4 | RP55R3           | RP55R2           | RP55R1          | RP55R0 |  |  |

| bit 15        |                                       |                  |        |                  |                  |                 | bit 8  |  |  |

|               |                                       |                  |        |                  |                  |                 |        |  |  |

| U-0           | R/W-0                                 | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |

|               | RP54R6                                | RP54R5           | RP54R4 | RP54R3           | RP54R2           | RP54R1          | RP54R0 |  |  |

| bit 7         |                                       |                  |        |                  |                  |                 | bit 0  |  |  |

|               |                                       |                  |        |                  |                  |                 |        |  |  |

| Legend:       |                                       |                  |        |                  |                  |                 |        |  |  |

| R = Readable  | bit                                   | W = Writable     | bit    | U = Unimpler     | mented bit, read | l as '0'        |        |  |  |

| -n = Value at | POR                                   | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |  |

|               |                                       |                  |        |                  |                  |                 |        |  |  |

| bit 15        | Unimplemen                            | ted: Read as '   | 0'     |                  |                  |                 |        |  |  |

| bit 14-8      | · · · · · · · · · · · · · · · · · · · |                  |        |                  |                  |                 |        |  |  |

|               |                                       |                  |        |                  |                  |                 |        |  |  |

- bit 7 **Unimplemented:** Read as '0'

- RP54R<6:0>: Peripheral Output Function is Assigned to RP54 Output Pin bits bit 6-0 (see Table 11-13 for peripheral function numbers)

### **REGISTER 16-16:** SPHASEx: PWMx SECONDARY PHASE-SHIFT REGISTER (x = 1 to 8)<sup>(1,2)</sup>

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|--|--|

|                                   |       |                  | SPHA  | SEx<15:8>                          |       |                 |       |  |  |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |  |  |

|                                   |       |                  |       |                                    |       |                 |       |  |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |

|                                   |       |                  | SPHA  | SEx<7:0>                           |       |                 |       |  |  |

| bit 7                             |       |                  |       |                                    |       |                 | bit 0 |  |  |

|                                   |       |                  |       |                                    |       |                 |       |  |  |

| Legend:                           |       |                  |       |                                    |       |                 |       |  |  |

| R = Readable bit W = Writable bit |       |                  |       | U = Unimplemented bit, read as '0' |       |                 |       |  |  |

| -n = Value at POR '1              |       | '1' = Bit is set |       | '0' = Bit is clear                 | ed    | x = Bit is unkr | nown  |  |  |

bit 15-0 **SPHASEx<15:0>:** Secondary Phase Offset for PWMxL Output Pin bits (used in Independent PWM mode only)

- **Note 1:** If PWMCONx<9> = 0, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); SPHASEx<15:0> = Not used

- True Independent Output mode (IOCONx<11:10> = 11), PHASEx<15:0> = Phase-shift value for PWMxL only

- **2:** If PWMCONx<9> = 1, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); SPHASEx<15:0> = Not used

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Independent time base period value for PWMxL only

- When the PHASEx/SPHASEx registers provide the local period, the valid range of values is 0x0010-0xFFF8

### **REGISTER 17-6: PTGSDLIM: PTG STEP DELAY LIMIT REGISTER**<sup>(1,2)</sup>

| R/W-0          |       | R/W-0       | R/W-0             |  |  |  |  |  |  |  |

|----------------|-------|-------------|-------------------|--|--|--|--|--|--|--|

|                | R/W-0 | 10.00-0     | 10/00-0           |  |  |  |  |  |  |  |

| PTGSDLIM<15:8> |       |             |                   |  |  |  |  |  |  |  |

|                |       |             | bit 8             |  |  |  |  |  |  |  |

|                |       |             |                   |  |  |  |  |  |  |  |

| R/W-0          | R/W-0 | R/W-0       | R/W-0             |  |  |  |  |  |  |  |

| PTGSDLIM<7:0>  |       |             |                   |  |  |  |  |  |  |  |

|                |       |             | bit 0             |  |  |  |  |  |  |  |

|                |       |             |                   |  |  |  |  |  |  |  |

|                | R/W-0 | R/W-0 R/W-0 | R/W-0 R/W-0 R/W-0 |  |  |  |  |  |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 **PTGSDLIM<15:0>:** PTG Step Delay Limit Register bits Holds a PTG Step delay value, representing the number of additional PTG clocks, between the start of a Step command and the completion of a Step command.

- **Note 1:** A base Step delay of one PTG clock is added to any value written to the PTGSDLIM register (Step Delay = (PTGSDLIM) + 1).

- 2: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

### REGISTER 17-7: PTGC0LIM: PTG COUNTER 0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0                             | R/W-0 | R/W-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|-----------------------------------|-------|-------|-------|--------------|------------------|----------|-------|

|                                   |       |       | PTGC0 | _IM<15:8>    |                  |          |       |

| bit 15                            |       |       |       |              |                  |          | bit 8 |

|                                   |       |       |       |              |                  |          |       |

| R/W-0                             | R/W-0 | R/W-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                                   |       |       | PTGC0 | LIM<7:0>     |                  |          |       |

| bit 7                             |       |       |       |              |                  |          | bit 0 |

|                                   |       |       |       |              |                  |          |       |

| Legend:                           |       |       |       |              |                  |          |       |

| R = Readable bit W = Writable bit |       |       |       | U = Unimpler | mented bit, read | l as '0' |       |

|                                   |       |       |       |              |                  |          |       |

bit 15-0 **PTGC0LIM<15:0>:** PTG Counter 0 Limit Register bits

'1' = Bit is set

May be used to specify the loop count for the PTGJMPC0 Step command or as a limit register for the General Purpose Counter 0.

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

### REGISTER 18-4: SPIx STATL: SPIx STATUS REGISTER LOW (CONTINUED)

- bit 3 SPITBE: SPIx Transmit Buffer Empty Status bit 1 = SPIxTXB is empty 0 = SPIxTXB is not empty Standard Buffer mode: Automatically set in hardware when SPIx transfers data from SPIxTXB to SPIxTXSR. Automatically cleared in hardware when SPIxBUF is written, loading SPIxTXB. Enhanced Buffer mode: Indicates TXELM<5:0> = 000000. bit 2 Unimplemented: Read as '0' bit 1 SPITBF: SPIx Transmit Buffer Full Status bit 1 = SPIxTXB is full 0 = SPIxTXB not full Standard Buffer mode: Automatically set in hardware when SPIxBUF is written, loading SPIxTXB. Automatically cleared in hardware when SPIx transfers data from SPIxTXB to SPIxTXSR. Enhanced Buffer mode: Indicates TXELM<5:0> = 111111. SPIRBF: SPIx Receive Buffer Full Status bit bit 0 1 = SPIxRXB is full 0 = SPIxRXB is not full Standard Buffer mode: Automatically set in hardware when SPIx transfers data from SPIxRXSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB. Enhanced Buffer mode: Indicates RXELM<5:0> = 111111.

- **Note 1:** SPITUR is cleared when SPIEN = 0. When IGNTUR = 1, SPITUR provides dynamic status of the Transmit Underrun condition, but does not stop RX/TX operation and does not need to be cleared by software.

### 22.0 HIGH-SPEED, 12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "12-Bit High-Speed, Multiple SARs A/D Converter (ADC)" (DS70005213) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

dsPIC33EPXXXGS70X/80X devices have a high-speed, 12-bit Analog-to-Digital Converter (ADC) that features a low conversion latency, high resolution and oversampling capabilities to improve performance in AC/DC, DC/DC power converters.

### 22.1 Features Overview

The high-speed, 12-bit multiple SARs Analog-to-Digital Converter (ADC) includes the following features:

- Five ADC Cores: Four Dedicated Cores and One Shared (common) Core

- User-Configurable Resolution of up to 12 Bits for each Core

- Up to 3.25 Msps Conversion Rate per Channel at 12-Bit Resolution

- Low Latency Conversion

- Up to 22 Analog Input Channels, with a Separate 16-Bit Conversion Result Register for each Input

- Conversion Result can be Formatted as Unsigned or Signed Data, on a per Channel Basis, for All Channels

- Single-Ended and Pseudodifferential Conversions are available on All ADC Cores

- Simultaneous Sampling of up to 5 Analog Inputs

- Channel Scan Capability

- Multiple Conversion Trigger Options for each Core, including:

- PWM1 through PWM6 (primary and secondary triggers, and current-limit event trigger)

- PWM Special Event Trigger

- Timer1/Timer2 period match

- Output Compare 1 and event trigger

- External pin trigger event (ADTRG31)

- Software trigger

- Two Integrated Digital Comparators with Dedicated Interrupts:

- Multiple comparison options

- Assignable to specific analog inputs

- Two Oversampling Filters with Dedicated Interrupts:

- Provide increased resolution

- Assignable to a specific analog input

The module consists of five independent SAR ADC cores. Simplified block diagrams of the multiple SARs 12-bit ADC are shown in Figure 22-1, Figure 22-2 and Figure 22-3.

The analog inputs (channels) are connected through multiplexers and switches to the Sample-and-Hold (S&H) circuit of each ADC core. The core uses the channel information (the output format, the Measurement mode and the input number) to process the analog sample. When conversion is complete, the result is stored in the result buffer for the specific analog input, and passed to the digital filter and digital comparator if they were configured to use data from this particular channel.

The ADC module can sample up to five inputs at a time (four inputs from the dedicated SAR cores and one from the shared SAR core). If multiple ADC inputs request conversion on the shared core, the module will convert them in a sequential manner, starting with the lowest order input.

The ADC provides each analog input the ability to specify its own trigger source. This capability allows the ADC to sample and convert analog inputs that are associated with PWM generators operating on independent time bases.

|                 | 22-6: ADCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Mon. ADC C                                                               |                  | GISTER 3 H        | IGH              |                 |         |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------|-------------------|------------------|-----------------|---------|--|

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                    | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |

| CLKSEL1         | CLKSEL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CLKDIV5                                                                  | CLKDIV4          | CLKDIV3           | CLKDIV2          | CLKDIV1         | CLKDIV0 |  |

| bit 15          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                          |                  |                   |                  |                 | bit 8   |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                          |                  |                   |                  |                 |         |  |

| R/W-0           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                      | U-0              | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |

| SHREN           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                        | —                | C3EN              | C2EN             | C1EN            | C0EN    |  |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                          |                  |                   |                  |                 | bit 0   |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                          |                  |                   |                  |                 |         |  |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                          |                  |                   |                  |                 |         |  |

| R = Readable    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | W = Writable                                                             | oit              | •                 | nented bit, read |                 |         |  |

| -n = Value at I | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | '1' = Bit is set                                                         |                  | '0' = Bit is clea | ared             | x = Bit is unkr | IOWN    |  |

| bit 15-14       | 11 = APLL<br>10 = FRC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | >: ADC Module<br>ystem Clock x 2<br>ystem Clock)                         |                  | Selection bits    |                  |                 |         |  |

| bit 13-8        | <ul> <li>CLKDIV&lt;5:0&gt;: ADC Module Clock Source Divider bits</li> <li>The divider forms a TCORESRC clock used by all ADC cores (shared and dedicated) from the TSRC module clock source selected by the CLKSEL&lt;1:0&gt; bits. Then, each ADC core individually divide</li> <li>TCORESRC clock to get a core-specific TADCORE clock using the ADCS&lt;6:0&gt; bits in the ADCOF register or the SHRADCS&lt;6:0&gt; bits in the ADCON2L register.</li> <li>111111 = 64 Source Clock Periods</li> </ul> |                                                                          |                  |                   |                  |                 |         |  |

|                 | 000010 = 3 S<br>000001 = 2 S                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Source Clock Po<br>Source Clock Po<br>Source Clock Po<br>Source Clock Po | eriods<br>eriods |                   |                  |                 |         |  |

| bit 7           | 1 = Shared Al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | red ADC Core I<br>DC core is ena<br>DC core is disa                      | bled             |                   |                  |                 |         |  |

| bit 6-4         | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ted: Read as 'd                                                          | )'               |                   |                  |                 |         |  |

| bit 3           | C3EN: Dedicated ADC Core 3 Enable bits<br>1 = Dedicated ADC Core 3 is enabled<br>0 = Dedicated ADC Core 3 is disabled                                                                                                                                                                                                                                                                                                                                                                                      |                                                                          |                  |                   |                  |                 |         |  |

| bit 2           | C2EN: Dedicated ADC Core 2 Enable bits<br>1 = Dedicated ADC Core 2 is enabled<br>0 = Dedicated ADC Core 2 is disabled                                                                                                                                                                                                                                                                                                                                                                                      |                                                                          |                  |                   |                  |                 |         |  |

| bit 1           | 1 = Dedicated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ated ADC Core<br>I ADC Core 1 is<br>I ADC Core 1 is                      | senabled         |                   |                  |                 |         |  |

| bit 0           | 1 = Dedicated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ated ADC Core<br>I ADC Core 0 is<br>I ADC Core 0 is                      | senabled         |                   |                  |                 |         |  |

#### REGISTER 22-6: ADCON3H: ADC CONTROL REGISTER 3 HIGH

| R/W-0, HS           | U-0                                                                                                                                                                                                                                                                       | U-0                                                                                                    | U-0                                            | R/W-0                                                  | R/W-0            | R/W-0           | R/W-0   |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------|------------------|-----------------|---------|--|--|

| CSHRRDY             |                                                                                                                                                                                                                                                                           | _                                                                                                      | —                                              | CSHRSKIP                                               | CSHRDIFF         | CSHREN          | CSHRRUN |  |  |

| bit 15              |                                                                                                                                                                                                                                                                           |                                                                                                        |                                                | •                                                      |                  |                 | bit 8   |  |  |

|                     |                                                                                                                                                                                                                                                                           |                                                                                                        |                                                |                                                        |                  |                 |         |  |  |

| U-0                 | U-0                                                                                                                                                                                                                                                                       | U-0                                                                                                    | U-0                                            | U-0                                                    | U-0              | U-0             | U-0     |  |  |

| —                   | —                                                                                                                                                                                                                                                                         | —                                                                                                      | —                                              |                                                        | —                |                 | —       |  |  |

| bit 7               |                                                                                                                                                                                                                                                                           |                                                                                                        |                                                |                                                        |                  |                 | bit 0   |  |  |

|                     |                                                                                                                                                                                                                                                                           |                                                                                                        |                                                |                                                        |                  |                 |         |  |  |

| Legend:             |                                                                                                                                                                                                                                                                           | HS = Hardwar                                                                                           | e Settable bit                                 |                                                        |                  |                 |         |  |  |

| R = Readabl         | e bit                                                                                                                                                                                                                                                                     | W = Writable I                                                                                         | bit                                            | U = Unimplem                                           | nented bit, read | as '0'          |         |  |  |

| -n = Value at       | POR                                                                                                                                                                                                                                                                       | '1' = Bit is set                                                                                       |                                                | '0' = Bit is clea                                      | ared             | x = Bit is unkr | nown    |  |  |

| bit 14-12<br>bit 11 | Unimplemen<br>CSHRSKIP:<br>1 = After pov<br>0 = After pov                                                                                                                                                                                                                 | ADC core calibra<br><b>nted:</b> Read as '0<br>Shared ADC Co<br>ver-up, the share<br>ver-up, the share | ore Calibration<br>ed ADC core weed ADC core w | Bypass bit<br>vill not be calibr<br>vill be calibrated | ł                |                 |         |  |  |