#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                          |

| Number of I/O              | 20                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 11x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

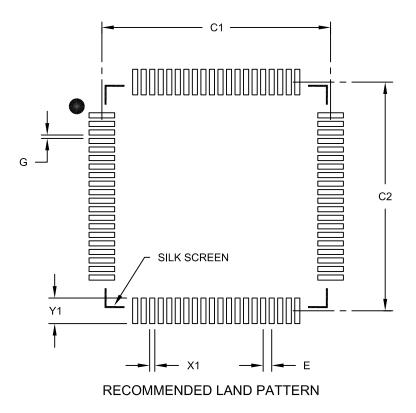

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs702-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Communication Interfaces**

- Two UART modules (15 Mbps):

- Supports LIN/J2602 protocols and IrDA®

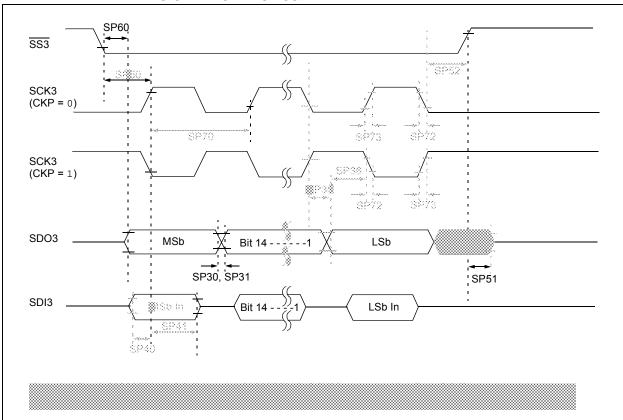

- Three Variable Width SPI modules with Operating modes:

- 3-wire SPI

- 8x16 or 8x8 FIFO mode

- I<sup>2</sup>S mode

- Two I<sup>2</sup>C modules (up to 1 Mbaud) with SMBus Support

- Up to Two CAN modules

- Four-Channel DMA

## Input/Output

- Constant-Current Source (10 µA nominal)

- Sink/Source up to 12 mA/15 mA, respectively; Pin-Specific for Standard VOH/VOL

- 5V Tolerant Pins

- · Selectable, Open-Drain Pull-ups and Pull-Downs

- External Interrupts on all I/O Pins

- Peripheral Pin Select (PPS) to allow Function Remap with Six Virtual I/Os

## **Qualification and Class B Support**

- AEC-Q100 REVG (Grade 1, -40°C to +125°C)

- Class B Safety Library, IEC 60730

- The 6x6x0.55 mm UQFN Package is Designed and Optimized to ease IPC9592B 2nd Level Temperature Cycle Qualification

## **Debugger Development Support**

- In-Circuit and In-Application Programming

- Five Program and Three Complex Data Breakpoints

- IEEE 1149.2 Compatible (JTAG) Boundary Scan

- Trace and Run-Time Watch

## **Digital Peripherals**

- Four Configurable Logic Cells

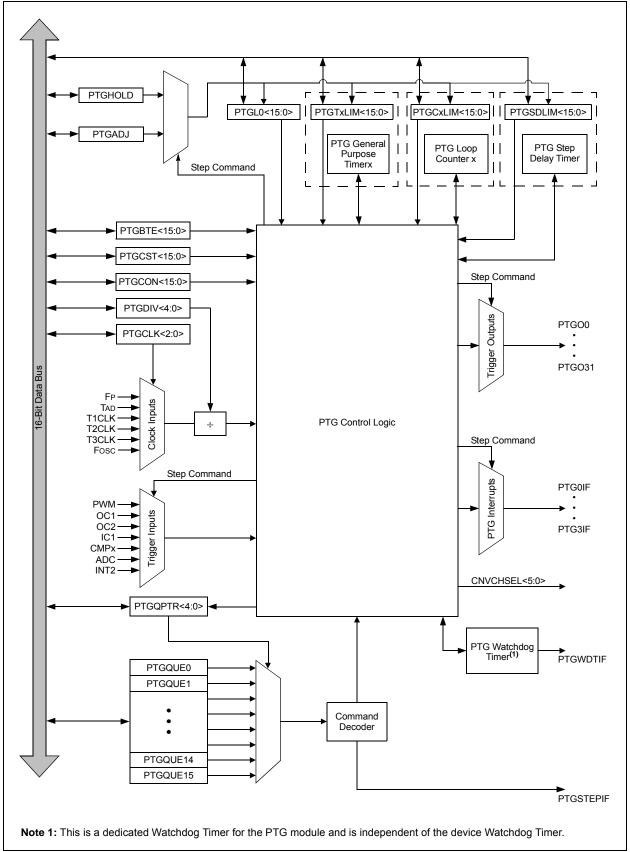

- Peripheral Trigger Generator

|                   |      | rtes                 |             | (GPIO)                |                       | Re            | ma             | ppal | ole F | Perip              | hera                               | als |                 |                  |     |     | 12-<br>A[     | -            |     |     | r                 |            | Source               |                         |

|-------------------|------|----------------------|-------------|-----------------------|-----------------------|---------------|----------------|------|-------|--------------------|------------------------------------|-----|-----------------|------------------|-----|-----|---------------|--------------|-----|-----|-------------------|------------|----------------------|-------------------------|

| Device            | Pins | Program Memory Bytes | RAM (Bytes) | General Purpose I/O ( | Timers <sup>(1)</sup> | Input Capture | Output Compare | UART | IdS   | PWM <sup>(2)</sup> | External Interrupts <sup>(3)</sup> | CAN | Reference Clock | 1 <sup>2</sup> C | CLC | ÐLd | Analog Inputs | S&H Circuits | V9d | AMA | Analog Comparator | DAC Output | Constant-Current Sou | Packages                |

| dsPIC33EP128GS702 | 28   | 128K                 | 8K          | 20                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 11            | 5            | 2   | 0   | 4                 | 1          | 1                    | SOIC,<br>QFN-S,<br>UQFN |

| dsPIC33EP64GS804  | 44   | 64K                  | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 4   | 4                 | 1          | 1                    |                         |

| dsPIC33EP128GS704 | 44   | 128K                 | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 0   | 4                 | 1          | 1                    | QFN,<br>TQFP            |

| dsPIC33EP128GS804 | 44   | 128K                 | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 4   | 4                 | 1          | 1                    | i Qi i                  |

| dsPIC33EP64GS805  | 48   | 64K                  | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 4   | 4                 | 1          | 1                    |                         |

| dsPIC33EP128GS705 | 48   | 128K                 | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 0   | 4                 | 1          | 1                    | TQFP                    |

| dsPIC33EP128GS805 | 48   | 128K                 | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 4   | 4                 | 1          | 1                    |                         |

| dsPIC33EP64GS806  | 64   | 64K                  | 8K          | 51                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 4   | 4                 | 2          | 1                    |                         |

| dsPIC33EP128GS706 | 64   | 128K                 | 8K          | 51                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 0   | 4                 | 2          | 1                    | TQFP                    |

| dsPIC33EP128GS806 | 64   | 128K                 | 8K          | 51                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 4   | 4                 | 2          | 1                    | 1                       |

| dsPIC33EP64GS708  | 80   | 64K                  | 8K          | 67                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 0   | 4                 | 2          | 1                    |                         |

| dsPIC33EP64GS808  | 80   | 64K                  | 8K          | 67                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 4   | 4                 | 2          | 1                    | TQFP                    |

| dsPIC33EP128GS708 | 80   | 128K                 | 8K          | 67                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 0   | 4                 | 2          | 1                    | IQFP                    |

| dsPIC33EP128GS808 | 80   | 128K                 | 8K          | 67                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 4   | 4                 | 2          | 1                    |                         |

Note 1: The external clock for Timer1, Timer2 and Timer3 is remappable.

2: PWM4 through PWM8 are remappable on 28/44/48-pin devices; on 64-pin devices, only PWM7/PWM8 are remappable.

**3:** External interrupts, INT0 and INT4, are not remappable.

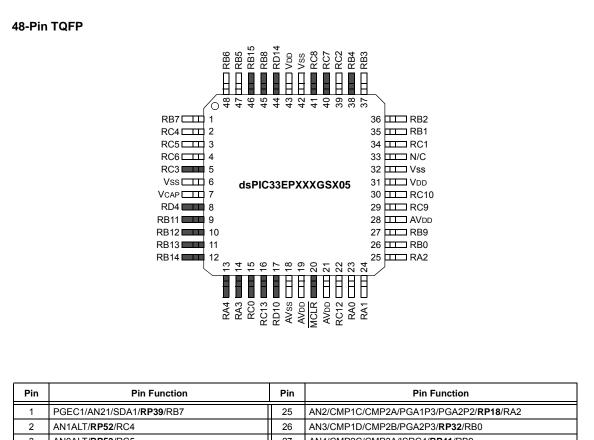

## Pin Diagrams (Continued)

|                                                                                                           | RB6<br>RB5<br>R815                                                                                                                                                                                                                                                                                                                                                                                           | KB8<br>VDD<br>VSS                                                                                                                | RC7<br>RC7<br>RB4<br>RB3                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              | 4 4 %                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                           | RB7 1                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  | 33 RB2                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                           | RC4 2                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  | 32 RB1                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                           | RC5 3                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  | 31 🛛 RC1                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                           | RC6 4                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  | <sup>30</sup> Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                           | RC3                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                  | 29 VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              | IC33EPX                                                                                                                          | <b>XXGSX04</b> 28 RC10                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  | 27 🛛 RC9                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                           | RB11 8                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                           | RB12 9                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  | 25 RB9                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                           | RB13 10                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  | 24 RB0                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                           | RB14 11                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  | <sup>23</sup> RA2                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                           | 4 0 C                                                                                                                                                                                                                                                                                                                                                                                                        | RC13<br>AVss<br>AVbb                                                                                                             | AVDD<br>RC12<br>RA0<br>RA1                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Pin                                                                                                       | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                 | Pin                                                                                                                              | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1                                                                                                         | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7                                                                                                                                                                                                                                                                                                                                                                            | 23                                                                                                                               | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1<br>2                                                                                                    | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4                                                                                                                                                                                                                                                                                                                                                | 23<br>24                                                                                                                         | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2<br>AN3/CMP1D/CMP2B/PGA2P3/ <b>RP32</b> /RB0                                                                                                                                                                                                                                                                                                                                                                      |

| 1                                                                                                         | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5                                                                                                                                                                                                                                                                                                                    | 23<br>24<br>25                                                                                                                   | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1<br>2<br>3                                                                                               | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4                                                                                                                                                                                                                                                                                                                                                | 23<br>24                                                                                                                         | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2<br>AN3/CMP1D/CMP2B/PGA2P3/ <b>RP32</b> /RB0<br>AN4/CMP2C/CMP3A/ISRC4/ <b>RP41</b> /RB9                                                                                                                                                                                                                                                                                                                           |

| 1<br>2<br>3<br>4                                                                                          | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6                                                                                                                                                                                                                                                                                          | 23<br>24<br>25<br>26                                                                                                             | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2<br>AN3/CMP1D/CMP2B/PGA2P3/ <b>RP32</b> /RB0<br>AN4/CMP2C/CMP3A/ISRC4/ <b>RP41</b> /RB9<br>AVDD                                                                                                                                                                                                                                                                                                                   |

| 1<br>2<br>3<br>4<br>5                                                                                     | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3                                                                                                                                                                                                                                                                      | 23<br>24<br>25<br>26<br>27                                                                                                       | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2<br>AN3/CMP1D/CMP2B/PGA2P3/ <b>RP32</b> /RB0<br>AN4/CMP2C/CMP3A/ISRC4/ <b>RP41</b> /RB9<br>AVDD<br>AN11/PGA1N3/ <b>RP57</b> /RC9                                                                                                                                                                                                                                                                                  |

| 1<br>2<br>3<br>4<br>5<br>6                                                                                | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3<br>Vss                                                                                                                                                                                                                                                               | 23<br>24<br>25<br>26<br>27<br>28                                                                                                 | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2<br>AN3/CMP1D/CMP2B/PGA2P3/ <b>RP32</b> /RB0<br>AN4/CMP2C/CMP3A/ISRC4/ <b>RP41</b> /RB9<br>AVDD<br>AN11/PGA1N3/ <b>RP57</b> /RC9<br>EXTREF2/AN10/PGA1P4/ <b>RP58</b> /RC10                                                                                                                                                                                                                                        |

| 1<br>2<br>3<br>4<br>5<br>6<br>7                                                                           | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3<br>Vss<br>VcaP                                                                                                                                                                                                                                                       | 23<br>24<br>25<br>26<br>27<br>28<br>28<br>29                                                                                     | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2<br>AN3/CMP1D/CMP2B/PGA2P3/ <b>RP32</b> /RB0<br>AN4/CMP2C/CMP3A/ISRC4/ <b>RP41</b> /RB9<br>AVDD<br>AN11/PGA1N3/ <b>RP57</b> /RC9<br>EXTREF2/AN10/PGA1P4/ <b>RP58</b> /RC10<br>VDD                                                                                                                                                                                                                                 |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8                                                                      | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3<br>Vss<br>VcAP<br>TMS/PWM3H/ <b>RP43</b> /RB11                                                                                                                                                                                                                       | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30                                                                                     | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2   AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0   AN4/CMP2C/CMP3A/ISRC4/RP41/RB9   AVDD   AN11/PGA1N3/RP57/RC9   EXTREF2/AN10/PGA1P4/RP58/RC10   VDD   VSS                                                                                                                                                                                                                                                                              |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9                                                                 | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3<br>Vss<br>VcAP<br>TMS/PWM3H/ <b>RP43</b> /RB11<br>TCK/PWM3L/ <b>RP44</b> /RB12                                                                                                                                                                                       | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31                                                                               | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2   AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0   AN4/CMP2C/CMP3A/ISRC4/RP41/RB9   AVDD   AN11/PGA1N3/RP57/RC9   EXTREF2/AN10/PGA1P4/RP58/RC10   VDD   VSS   AN8/CMP4C/PGA2P4/RP49/RC1                                                                                                                                                                                                                                                  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12                                               | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3<br>Vss<br>VcAP<br>TMS/PWM3H/ <b>RP43</b> /RB11<br>TCK/PWM3L/ <b>RP44</b> /RB12<br>PWM2H/ <b>RP45</b> /RB13<br>PWM2L/ <b>RP46</b> /RB14<br>PWM1H/ <b>RP20</b> /RA4                                                                                                    | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>33                                                       | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2   AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0   AN4/CMP2C/CMP3A/ISRC4/RP41/RB9   AVDD   AN11/PGA1N3/RP57/RC9   EXTREF2/AN10/PGA1P4/RP58/RC10   VDD   VSS   AN8/CMP4C/PGA2P4/RP49/RC1   OSC2/CLK0/AN7/CMP3D/CMP4A/ISRC2/RP33/RB1   OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2   PGED2/DACOUT1/AN18/INT0/RP35/RB3                                                                                                                        |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13                                         | PGEC1/AN21/SDA1/RP39/RB7   AN1ALT/RP52/RC4   AN0ALT/RP53/RC5   AN17/RP54/RC6   RP51/RC3   Vss   Vcap   TMS/PWM3H/RP43/RB11   TCK/PWM3L/RP44/RB12   PWM2L/RP46/RB13   PWM2L/RP46/RB14   PWM1L/RP19/RA3                                                                                                                                                                                                        | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>34<br>35                                                 | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2   AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0   AN4/CMP2C/CMP3A/ISRC4/RP41/RB9   AVD   AN11/PGA1N3/RP57/RC9   EXTREF2/AN10/PGA1P4/RP58/RC10   VDD   VSS   AN8/CMP4C/PGA2P4/RP49/RC1   OSCI/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1   OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2   PGED2/DACOUT1/AN18/INT0/RP35/RB3   PGEC2/ADTRG31/RP36/RB4                                                                                                |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14                                   | PGEC1/AN21/SDA1/RP39/RB7   AN1ALT/RP52/RC4   AN0ALT/RP53/RC5   AN17/RP54/RC6   RP51/RC3   Vss   Vcap   TMS/PWM3H/RP43/RB11   TCK/PWM3L/RP44/RB12   PWM2H/RP45/RB13   PWM2L/RP46/RB14   PWM1L/RP19/RA3   FLT12/RP48/RC0                                                                                                                                                                                       | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>34<br>35<br>36                                           | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2   AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0   AN4/CMP2C/CMP3A/ISRC4/RP41/RB9   AVD   AN1/PGA1N3/RP57/RC9   EXTREF2/AN10/PGA1P4/RP58/RC10   VDD   VSS   AN8/CMP4C/PGA2P4/RP49/RC1   OSCI/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1   OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2   PGED2/DACOUT1/AN18/INT0/RP35/RB3   PGEC2/ADTRG31/RP36/RB4   EXTREF1/AN9/CMP4D/RP50/RC2                                                                    |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>9<br>10<br>11<br>12<br>13<br>14<br>15                        | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3<br>Vss<br>Vcap<br>TMS/PWM3H/ <b>RP43</b> /RB11<br>TCK/PWM3L/ <b>RP44</b> /RB12<br>PWM2H/ <b>RP45</b> /RB13<br>PWM2L/ <b>RP46</b> /RB14<br>PWM1H/ <b>RP20</b> /RA4<br>PWM1L/ <b>RP19</b> /RA3<br>FLT12/ <b>RP48</b> /RC0<br>FLT11/ <b>RP61</b> /RC13                  | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>33<br>34<br>35<br>36<br>37                               | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2   AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0   AN4/CMP2C/CMP3A/ISRC4/RP41/RB9   AVD   AN1/PGA1N3/RP57/RC9   EXTREF2/AN10/PGA1P4/RP58/RC10   VDD   VSS   AN8/CMP4C/PGA2P4/RP49/RC1   OSCI/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1   OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2   PGED2/DACOUT1/AN18/INT0/RP35/RB3   PGEC2/ADTRG31/RP36/RB4   EXTREF1/AN9/CMP4D/RP50/RC2   ASDA1/RP55/RC7                                                   |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16                  | PGEC1/AN21/SDA1/RP39/RB7   AN1ALT/RP52/RC4   AN0ALT/RP53/RC5   AN17/RP54/RC6   RP51/RC3   Vss   Vcap   TMS/PWM3H/RP43/RB11   TCK/PWM3L/RP44/RB12   PWM2H/RP45/RB13   PWM2L/RP46/RB14   PWM1L/RP19/RA3   FLT12/RP48/RC0   FLT11/RP61/RC13   AVss                                                                                                                                                              | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>33<br>34<br>35<br>36<br>36<br>37<br>38                   | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2   AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0   AN4/CMP2C/CMP3A/ISRC4/RP41/RB9   AVD   AVDD   AN11/PGA1N3/RP57/RC9   EXTREF2/AN10/PGA1P4/RP58/RC10   VDD   VSS   AN8/CMP4C/PGA2P4/RP49/RC1   OSCI/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1   OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2   PGED2/DACOUT1/AN18/INT0/RP35/RB3   PGEC2/ADTRG31/RP36/RB4   EXTREF1/AN9/CMP4D/RP50/RC2   ASDA1/RP55/RC7   ASCL1/RP56/RC8                          |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17            | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3<br>Vss<br>VcAP<br>TMS/PWM3H/ <b>RP43</b> /RB11<br>TCK/PWM3L/ <b>RP44</b> /RB12<br>PWM2H/ <b>RP45</b> /RB13<br>PWM2L/ <b>RP46</b> /RB14<br>PWM1L/ <b>RP46</b> /RB14<br>PWM1L/ <b>RP19</b> /RA3<br>FLT12/ <b>RP48</b> /RC0<br>FLT11/ <b>RP61</b> /RC13<br>AVss<br>AVDD | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>33<br>34<br>35<br>36<br>36<br>37<br>38<br>39             | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2   AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0   AN4/CMP2C/CMP3A/ISRC4/RP41/RB9   AVD   AN1/PGA1N3/RP57/RC9   EXTREF2/AN10/PGA1P4/RP58/RC10   VDD   VSS   AN8/CMP4C/PGA2P4/RP49/RC1   OSC2/CLK0/AN7/CMP3D/CMP4A/ISRC2/RP33/RB1   OSC2/CLK0/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2   PGED2/DACOUT1/AN18/INT0/RP35/RB3   PGEC2/ADTRG31/RP36/RB4   EXTREF1/AN9/CMP4D/RP50/RC2   ASDA1/RP55/RC7   ASCL1/RP56/RC8   Vss                            |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>7<br>8<br>9<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 | PGEC1/AN21/SDA1/RP39/RB7   AN1ALT/RP52/RC4   AN0ALT/RP53/RC5   AN17/RP54/RC6   RP51/RC3   Vss   VCAP   TMS/PWM3H/RP43/RB11   TCK/PWM3L/RP44/RB12   PWM2H/RP45/RB13   PWM2L/RP46/RB14   PWM1L/RP19/RA3   FLT12/RP48/RC0   FLT11/RP61/RC13   AVss   AVod   MCLR                                                                                                                                                | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>33<br>34<br>35<br>36<br>36<br>37<br>38<br>39<br>40       | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2   AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0   AN4/CMP2C/CMP3A/ISRC4/RP41/RB9   AVD   AN1/PGA1N3/RP57/RC9   EXTREF2/AN10/PGA1P4/RP58/RC10   VDD   VSS   AN8/CMP4C/PGA2P4/RP49/RC1   OSC2/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1   OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2   PGED2/DACOUT1/AN18/INT0/RP35/RB3   PGEC2/ADTRG31/RP36/RB4   EXTREF1/AN9/CMP4D/RP50/RC2   ASDA1/RP55/RC7   ASSCL1/RP56/RC8   VbD                           |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19     | PGEC1/AN21/SDA1/RP39/RB7   AN1ALT/RP52/RC4   AN0ALT/RP53/RC5   AN17/RP54/RC6   RP51/RC3   Vss   VCAP   TMS/PWM3H/RP43/RB11   TCK/PWM3L/RP44/RB12   PWM2H/RP45/RB13   PWM2L/RP46/RB14   PWM1L/RP19/RA3   FLT12/RP48/RC0   FLT11/RP61/RC13   AVbd   MCLR   AVdd                                                                                                                                                | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>33<br>34<br>35<br>36<br>36<br>37<br>38<br>39<br>40<br>41 | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2   AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0   AN4/CMP2C/CMP3A/ISRC4/RP41/RB9   AVD   AN1/PGA1N3/RP57/RC9   EXTREF2/AN10/PGA1P4/RP58/RC10   Vbb   VSS   AN8/CMP4C/PGA2P4/RP49/RC1   OSC2/CLK/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1   OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2   PGED2/DACOUT1/AN18/INT0/RP35/RB3   PGEC2/ADTRG31/RP36/RB4   EXTREF1/AN9/CMP4D/RP50/RC2   ASDA1/RP55/RC7   ASSL1/RP56/RC8   VbD   PGED3/SDA2/FLT31/RP40/RB8 |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>7<br>8<br>9<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 | PGEC1/AN21/SDA1/RP39/RB7   AN1ALT/RP52/RC4   AN0ALT/RP53/RC5   AN17/RP54/RC6   RP51/RC3   Vss   VCAP   TMS/PWM3H/RP43/RB11   TCK/PWM3L/RP44/RB12   PWM2H/RP45/RB13   PWM2L/RP46/RB14   PWM1L/RP19/RA3   FLT12/RP48/RC0   FLT11/RP61/RC13   AVss   AVod   MCLR                                                                                                                                                | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>33<br>34<br>35<br>36<br>36<br>37<br>38<br>39<br>40       | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2   AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0   AN4/CMP2C/CMP3A/ISRC4/RP41/RB9   AVD   AN1/PGA1N3/RP57/RC9   EXTREF2/AN10/PGA1P4/RP58/RC10   VDD   VSS   AN8/CMP4C/PGA2P4/RP49/RC1   OSC2/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1   OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2   PGED2/DACOUT1/AN18/INT0/RP35/RB3   PGEC2/ADTRG31/RP36/RB4   EXTREF1/AN9/CMP4D/RP50/RC2   ASDA1/RP55/RC7   ASSCL1/RP56/RC8   VbD                           |

Legend: Shaded pins are up to 5 VDC tolerant. RPn represents remappable peripheral functions. See Table 11-12 and Table 11-13 for the complete list of remappable sources.

## **Pin Diagrams (Continued)**

| 2  | AN1ALT/RP52/RC4                  | 26 | AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0           |

|----|----------------------------------|----|-------------------------------------------|

| 3  | AN0ALT/RP53/RC5                  | 27 | AN4/CMP2C/CMP3A/ISRC4/RP41/RB9            |

| 4  | AN17/ <b>RP54</b> /RC6           | 28 | AVDD                                      |

| 5  | RP51/RC3                         | 29 | AN11/PGA1N3/ <b>RP57</b> /RC9             |

| 6  | Vss                              | 30 | EXTREF2/AN10/PGA1P4/RP58/RC10             |

| 7  | VCAP                             | 31 | VDD                                       |

| 8  | RP68/RD4                         | 32 | Vss                                       |

| 9  | TMS/PWM3H/RP43/RB11              | 33 | N/C                                       |

| 10 | TCK/PWM3L/RP44/RB12              | 34 | AN8/CMP4C/PGA2P4/RP49/RC1                 |

| 11 | PWM2H/ <b>RP45</b> /RB13         | 35 | OSCI/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1  |

| 12 | PWM2L/ <b>RP46</b> /RB14         | 36 | OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2 |

| 13 | PWM1H/ <b>RP20</b> /RA4          | 37 | PGED2/DACOUT1/AN18/INT0/RP35/RB3          |

| 14 | PWM1L/ <b>RP19</b> /RA3          | 38 | PGEC2/ADTRG31/ <b>RP36</b> /RB4           |

| 15 | FLT12/ <b>RP48</b> /RC0          | 39 | EXTREF1/AN9/CMP4D/RP50/RC2                |

| 16 | FLT11/ <b>RP61</b> /RC13         | 40 | ASDA1/RP55/RC7                            |

| 17 | CLC4OUT/FLT10/RP74/RD10          | 41 | ASCL1/RP56/RC8                            |

| 18 | AVss                             | 42 | Vss                                       |

| 19 | AVDD                             | 43 | VDD                                       |

| 20 | MCLR                             | 44 | CLC3OUT/RD14                              |

| 21 | AVDD                             | 45 | PGED3/SDA2/FLT31/RP40/RB8                 |

| 22 | AN14/PGA2N3/RP60/RC12            | 46 | PGEC3/SCL2/RP47/RB15                      |

| 23 | AN0/CMP1A/PGA1P1/RP16/RA0        | 47 | TDO/AN19/PGA2N2/ <b>RP37</b> /RB5         |

| 24 | AN1/CMP1B/PGA1P2/PGA2P1/RP17/RA1 | 48 | PGED1/TDI/AN20/SCL1/RP38/RB6              |

Legend: Shaded pins are up to 5 VDC tolerant.

**RPn** represents remappable peripheral functions. See Table 11-12 and Table 11-13 for the complete list of remappable sources.

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXXGS70X/80X Digital Signal Controller (DSC) devices.

dsPIC33EPXXXGS70X/80X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

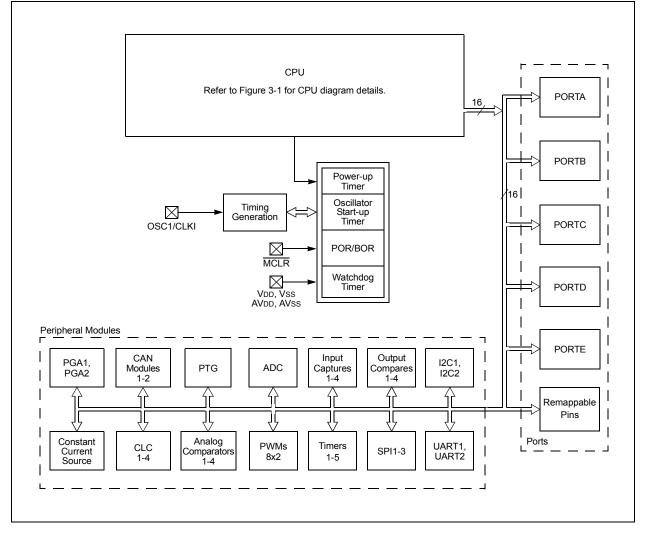

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

### FIGURE 1-1: dsPIC33EPXXXGS70X/80X FAMILY BLOCK DIAGRAM

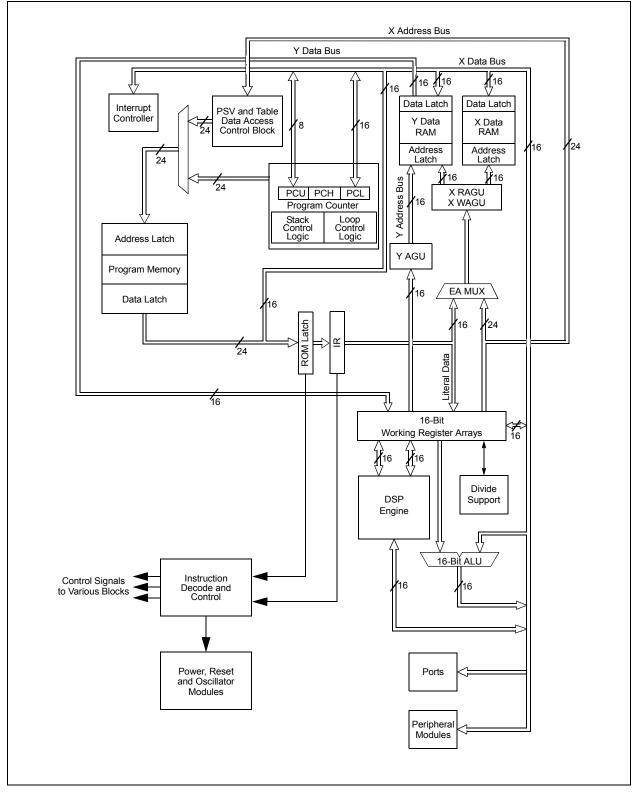

## FIGURE 3-1: dsPIC33EPXXXGS70X/80X FAMILY CPU BLOCK DIAGRAM

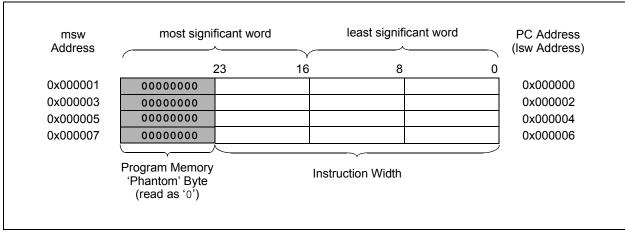

#### 4.2.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-5).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

## 4.2.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGS70X/80X family devices reserve the addresses between 0x000000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-5: PROGRAM MEMORY ORGANIZATION

### 4.3.5 X AND Y DATA SPACES

The dsPIC33EPXXXGS70X/80X core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

#### 4.4 Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 4.4.1 KEY RESOURCES

- "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 15.2 Output Compare Control Registers

## REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

|                                                            | U-0                                                                                      | OCSIDL              | OCTSEL2                                                                                      | OCTSEL1           | OCTSEL0          |                 |        |  |  |  |  |

|------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| R/W-0<br>ENFLTA                                            | U-0                                                                                      |                     |                                                                                              |                   | OCISELU          | _               |        |  |  |  |  |

| ENFLTA                                                     | U-0                                                                                      |                     |                                                                                              |                   |                  |                 | bit    |  |  |  |  |

| ENFLTA                                                     | 00                                                                                       | U-0                 | R/W-0, HSC                                                                                   | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| bit 7                                                      | _                                                                                        |                     | OCFLTA                                                                                       | TRIGMODE          | OCM2             | OCM1            | OCM0   |  |  |  |  |

|                                                            |                                                                                          |                     |                                                                                              |                   |                  |                 | bit    |  |  |  |  |

| Legend:                                                    |                                                                                          | USC - Hardwa        | ara Sattabla/Cla                                                                             | arablo bit        |                  |                 |        |  |  |  |  |

| R = Readab                                                 | lo hit                                                                                   | W = Writable b      | HSC = Hardware Settable/Clearable bit<br>W = Writable bit U = Unimplemented bit, read as '0' |                   |                  |                 |        |  |  |  |  |

| -n = Value a                                               |                                                                                          | '1' = Bit is set    | п                                                                                            | '0' = Bit is clea |                  | x = Bit is unkr |        |  |  |  |  |

|                                                            |                                                                                          |                     |                                                                                              |                   |                  |                 | 101111 |  |  |  |  |

| bit 15-14                                                  | Unimpleme                                                                                | ented: Read as '0   | ,                                                                                            |                   |                  |                 |        |  |  |  |  |

| bit 13                                                     | OCSIDL: 0                                                                                | utput Compare x     | Stop in Idle Mo                                                                              | de Control bit    |                  |                 |        |  |  |  |  |

|                                                            | 1 = Output                                                                               | Compare x halts     | in CPU Idle mo                                                                               | de                |                  |                 |        |  |  |  |  |

| 0 = Output Compare x continues to operate in CPU Idle mode |                                                                                          |                     |                                                                                              |                   |                  |                 |        |  |  |  |  |

| bit 12-10                                                  | OCTSEL<2                                                                                 | :0>: Output Com     | oare x Clock Se                                                                              | lect bits         |                  |                 |        |  |  |  |  |

|                                                            | 111 = Perip                                                                              | heral clock (FP)    |                                                                                              |                   |                  |                 |        |  |  |  |  |

|                                                            | 110 = Rese                                                                               |                     |                                                                                              |                   |                  |                 |        |  |  |  |  |

|                                                            | 101 = Rese                                                                               |                     | was of the OCy                                                                               |                   |                  |                 |        |  |  |  |  |

|                                                            |                                                                                          | K is the clock sou  |                                                                                              |                   | Ironous clock is | supported)      |        |  |  |  |  |

|                                                            | 011 = T5CLK is the clock source of the OCx<br>010 = T4CLK is the clock source of the OCx |                     |                                                                                              |                   |                  |                 |        |  |  |  |  |

|                                                            | 001 = T3CLK is the clock source of the OCx                                               |                     |                                                                                              |                   |                  |                 |        |  |  |  |  |

|                                                            | 000 = T2CL                                                                               | K is the clock sou  | urce of the OCx                                                                              |                   |                  |                 |        |  |  |  |  |

| bit 9-8                                                    | Unimpleme                                                                                | ented: Read as '0   | ,                                                                                            |                   |                  |                 |        |  |  |  |  |

| bit 7                                                      | ENFLTA: Fa                                                                               | ault A Input Enabl  | e bit                                                                                        |                   |                  |                 |        |  |  |  |  |

|                                                            | 1 = Output Compare Fault A input (OCFA) is enabled                                       |                     |                                                                                              |                   |                  |                 |        |  |  |  |  |

|                                                            | 0 = Output                                                                               | Compare Fault A     | input (OCFA) is                                                                              | s disabled        |                  |                 |        |  |  |  |  |

| bit 6-5                                                    | Unimpleme                                                                                | ented: Read as '0   | ,                                                                                            |                   |                  |                 |        |  |  |  |  |

| bit 4                                                      | OCFLTA: P                                                                                | WM Fault A Cond     | lition Status bit                                                                            |                   |                  |                 |        |  |  |  |  |

|                                                            |                                                                                          | ault A condition c  |                                                                                              |                   |                  |                 |        |  |  |  |  |

|                                                            | 0 = No PW                                                                                | M Fault A condition | on on the OCFA                                                                               | pin has occurre   | ed               |                 |        |  |  |  |  |

| bit 3                                                      |                                                                                          | : Trigger Status N  |                                                                                              |                   |                  |                 |        |  |  |  |  |

|                                                            |                                                                                          | TAT (OCxCON2<       | ,                                                                                            | /hen OCxRS = (    | OCxTMR or in s   | oftware         |        |  |  |  |  |

|                                                            | 0 = TRIGS                                                                                | TAT is cleared on   | y by software                                                                                |                   |                  |                 |        |  |  |  |  |

**Note 1:** OCxR and OCxRS are double-buffered in PWM mode only.

## 21.1 Control Registers

The CLCx module is controlled by the following registers:

- CLCxCONL

- CLCxCONH

- CLCxSEL

- CLCxGLSL

- CLCxGLSH

The CLCx Control registers (CLCxCONL and CLCxCONH) are used to enable the module and interrupts, control the output enable bit, select output polarity and select the logic function. The CLCx Control registers also allow the user to control the logic polarity of not only the cell output, but also some intermediate variables. The CLCx Input MUX Select register (CLCxSEL) allows the user to select up to 4 data input sources using the 4 data input selection multiplexers. Each multiplexer has a list of 8 data sources available.

The CLCx Gate Logic Input Select registers (CLCxGLSL and CLCxGLSH) allow the user to select which outputs from each of the selection MUXes are used as inputs to the input gates of the logic cell. Each data source MUX outputs both a true and a negated version of its output. All of these 8 signals are enabled, ORed together by the logic cell input gates.

### REGISTER 21-1: CLCxCONL: CLCx CONTROL REGISTER (LOW)

| D 444 0                |                                                            |                                                                       |                              |                   |                  |          |       |  |  |  |  |

|------------------------|------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------|-------------------|------------------|----------|-------|--|--|--|--|

| R/W-0                  | U-0                                                        | U-0                                                                   | U-0                          | R/W-0             | R/W-0            | U-0      | U-0   |  |  |  |  |

| LCEN                   | —                                                          | —                                                                     | —                            | INTP              | INTN             | —        | —     |  |  |  |  |

| bit 15                 |                                                            |                                                                       |                              |                   |                  |          | bit 8 |  |  |  |  |

|                        |                                                            |                                                                       |                              |                   |                  |          |       |  |  |  |  |

| R-0                    | R-0                                                        | R/W-0                                                                 | U-0                          | U-0               | R/W-0            | R/W-0    | R/W-0 |  |  |  |  |

| LCOE                   | LCOUT                                                      | LCOUT LCPOL — — MODE2 MODE1 MO                                        |                              |                   |                  |          |       |  |  |  |  |

| bit 7                  |                                                            |                                                                       |                              |                   |                  |          | bit 0 |  |  |  |  |

| Logondi                |                                                            |                                                                       |                              |                   |                  |          |       |  |  |  |  |

| Legend:<br>R = Readabl | e hit                                                      | W = Writable t                                                        | nit                          | II – Unimplen     | nented bit, read | 1 ac '0' |       |  |  |  |  |

| -n = Value at          |                                                            | '1' = Bit is set                                                      | JIL                          |                   | x = Bit is unkr  |          |       |  |  |  |  |

|                        | IFUR                                                       | I – DILIS SEL                                                         |                              | '0' = Bit is clea | areu             |          | IOWIT |  |  |  |  |

| bit 15                 | I CEN: CLCx                                                | Enable bit                                                            |                              |                   |                  |          |       |  |  |  |  |