Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                           |

| Number of I/O              | 20                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 11x12b; D/A 1x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-UQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-UQFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs702t-i-2n |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

| Interrupt Source                            | Vector  | IRQ     | IVT Address       | Interrupt Bit Location |                      |                               |  |

|---------------------------------------------|---------|---------|-------------------|------------------------|----------------------|-------------------------------|--|

| interrupt Source                            | #       | #       | IVI Address       | Flag                   | Enable               | Priority                      |  |

| PSES – PWM Secondary Special<br>Event Match | 81      | 73      | 0x0000A6          | IFS4<9><br>PSESIF      | IEC4<9><br>PSESIE    | IPC18<6:4><br>PSESIP<2:0>     |  |

| Reserved                                    | 82-97   | 74-89   | 0x0000A8-0x0000C6 | _                      | _                    | —                             |  |

| SPI3TX – SPI3 Transfer Done                 | 98      | 90      | 0x0000C8          | IFS5<10><br>SPI3TXIF   | IEC5<10><br>SPI3TXIE | IPC22<10:8><br>SPI3TXIP<2:0>  |  |

| SPI3RX – SPI3 Receive Done                  | 99      | 91      | 0x0000CA          | IFS5<10><br>SPI3RXIF   | IEC5<11><br>SPI3RXIE | IPC22<14:12><br>SPI3RXIP<2:0> |  |

| Reserved                                    | 100-101 | 92-93   | 0x0000CC-0x0000CE |                        | _                    | _                             |  |

| PWM1 – PWM1 Interrupt                       | 102     | 94      | 0x0000D0          | IFS5<14><br>PWM1IF     | IEC5<14><br>PWM1IE   | IPC23<10:8><br>PWM1IP<2:0>    |  |

| PWM2 – PWM2 Interrupt                       | 103     | 95      | 0x0000D2          | IFS5<15><br>PWM2IF     | IEC5<15><br>PWM2IE   | IPC23<14:12><br>PWM2IP<2:0>   |  |

| PWM3 – PWM3 Interrupt                       | 104     | 96      | 0x0000D4          | IFS6<0><br>PWM3IF      | IEC6<0><br>PWM3IE    | IPC24<2:0><br>PWM3IP<2:0>     |  |

| PWM4 – PWM4 Interrupt                       | 105     | 97      | 0x0000D6          | IFS6<1><br>PWM4IF      | IEC6<1><br>PWM4IE    | IPC24<6:4><br>PWM4IP<2:0>     |  |

| PWM5 – PWM5 Interrupt                       | 106     | 98      | 0x0000D8          | IFS6<2><br>PWM5IF      | IEC6<2><br>PWM5IE    | IPC24<10:8><br>PWM5IP<2:0>    |  |

| PWM6 – PWM6 Interrupt                       | 107     | 99      | 0x0000DA          | IFS6<3><br>PWM6IF      | IEC6<3><br>PWM6IE    | IPC24<14:12><br>PWM6IP<2:0>   |  |

| PWM7 – PWM7 Interrupt                       | 108     | 100     | 0x0000DC          | IFS6<4><br>PWM7IF      | IEC6<4><br>PWM7IE    | IPC25<2:0><br>PWM7IP<2:0>     |  |

| PWM8 – PWM8 Interrupt                       | 109     | 101     | 0x0000DE          | IFS6<5><br>PWM8IF      | IEC6<5><br>PWM8IE    | IPC25<6:4><br>PWM8IP<2:0>     |  |

| Reserved                                    | 110     | 102     | 0x0000E0          | _                      | _                    | _                             |  |

| AC2 – Analog Comparator 2 Interrupt         | 111     | 103     | 0x0000E2          | IFS6<7><br>AC2IF       | IEC6<7><br>AC2IE     | IPC25<14:12><br>AC2IP<2:0>    |  |

| AC3 – Analog Comparator 3 Interrupt         | 112     | 104     | 0x0000E4          | IFS6<8><br>AC3IF       | IEC6<8><br>AC3IE     | IPC26<2:0><br>AC3IP<2:0>      |  |

| AC4 – Analog Comparator 4 Interrupt         | 113     | 105     | 0x0000E6          | IFS6<9><br>AC4IF       | IEC6<9><br>AC4IE     | IPC26<6:4><br>AC4IP<2:0>      |  |

| Reserved                                    | 114-117 | 106-109 | 0x0000E8-0x0000EE | _                      | —                    |                               |  |

| AN0 Conversion Done                         | 118     | 110     | 0x0000F0          | IFS6<14><br>AN0IF      | IEC6<14><br>AN0IE    | IPC27<10:8><br>AN0IP<2:0>     |  |

| AN1 Conversion Done                         | 119     | 111     | 0x0000F2          | IFS6<15><br>AN1IF      | IEC6<15><br>AN1IE    | IPC27<14:12><br>AN1IP<2:0>    |  |

| AN2 Conversion Done                         | 120     | 112     | 0x0000F4          | IFS7<0><br>AN2IF       | IEC7<0><br>AN2IE     | IPC28<2:0><br>AN2IP<2:0>      |  |

| AN3 Conversion Done                         | 121     | 113     | 0x0000F6          | IFS7<1><br>AN3IF       | IEC7<1><br>AN3IE     | IPC28<6:4><br>AN3IP<2:0>      |  |

| AN4 Conversion Done                         | 122     | 114     | 0x0000F8          | IFS7<2><br>AN4IF       | IEC7<2><br>AN4IE     | IPC28<10:8><br>AN4IP<2:0>     |  |

| AN5 Conversion Done                         | 123     | 115     | 0x0000FA          | IFS7<3><br>AN5IF       | IEC7<3><br>AN5IE     | IPC28<14:12><br>AN5IP<2:0>    |  |

| AN6 Conversion Done                         | 124     | 116     | 0x0000FC          | IFS7<4><br>AN6IF       | IEC7<4><br>AN6IE     | IPC29<2:0><br>AN6IP<2:0>      |  |

| AN7 Conversion Done                         | 125     | 117     | 0x0000FE          | IFS7<5><br>AN7IF       | IEC7<5><br>AN7IE     | IPC29<6:4><br>AN7IP<2:0>      |  |

| Reserved                                    | 126-131 | 118-123 | 0x000100-0x00010A |                        |                      |                               |  |

NOTES:

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **"Oscillator Module"** (DS70005131) in the *"dsPIC33/PIC24 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGS70X/80X family oscillator system provides:

- On-Chip Phase-Locked Loop (PLL) to Boost Internal Operating Frequency on Select Internal and External Oscillator Sources

- On-the-Fly Clock Switching between Various Clock Sources

- Doze mode for System Power Savings

- Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown

- Configuration Bits for Clock Source Selection

- Auxiliary PLL for ADC and PWM

A simplified diagram of the oscillator system is shown in Figure 9-1.

| R/W-0         | R/W-0        | R/W-0                               | R/W-0      | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|---------------|--------------|-------------------------------------|------------|-------------------|------------------|-----------------|--------|

| PWM8MD        | PWM7MD       | PWM6MD                              | PWM5MD     | PWM4MD            | PWM3MD           | PWM2MD          | PWM1MD |

| bit 15        |              |                                     |            |                   |                  |                 | bit 8  |

|               |              |                                     |            |                   |                  |                 |        |

| U-0           | U-0          | U-0                                 | U-0        | U-0               | U-0              | U-0             | R/W-0  |

|               | —            |                                     |            | —                 |                  |                 | SPI3MD |

| bit 7         |              |                                     |            |                   |                  |                 | bit C  |

| Legend:       |              |                                     |            |                   |                  |                 |        |

| R = Readable  | e bit        | W = Writable                        | oit        | U = Unimplem      | nented bit, read | 1 as '0'        |        |

| -n = Value at | POR          | '1' = Bit is set                    |            | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

|               |              |                                     |            |                   |                  |                 |        |

| bit 15        | PWM8MD: P    | WM8 Module D                        | isable bit |                   |                  |                 |        |

|               | -            | odule is disable<br>odule is enable |            |                   |                  |                 |        |

| bit 14        |              | WM7 Module D                        | -          |                   |                  |                 |        |

| DIL 14        |              | odule is disable                    |            |                   |                  |                 |        |

|               |              | odule is enable                     |            |                   |                  |                 |        |

| bit 13        | PWM6MD: P    | WM6 Module D                        | isable bit |                   |                  |                 |        |

|               |              | odule is disable<br>odule is enable |            |                   |                  |                 |        |

| bit 12        | PWM5MD: P    | WM5 Module D                        | isable bit |                   |                  |                 |        |

|               | -            | odule is disable                    |            |                   |                  |                 |        |

| L:1 44        |              | odule is enable                     |            |                   |                  |                 |        |

| bit 11        |              | WM4 Module D<br>odule is disable    |            |                   |                  |                 |        |

|               |              | odule is disable                    |            |                   |                  |                 |        |

| bit 10        | PWM3MD: P    | WM3 Module D                        | isable bit |                   |                  |                 |        |

|               |              | odule is disable                    |            |                   |                  |                 |        |

|               |              | odule is enable                     |            |                   |                  |                 |        |

| bit 9         |              | WM2 Module D                        |            |                   |                  |                 |        |

|               |              | odule is disable<br>odule is enable |            |                   |                  |                 |        |

| bit 8         |              | WM1 Module D                        |            |                   |                  |                 |        |

|               |              | odule is disable                    |            |                   |                  |                 |        |

|               | 0 = PWM1 m   | odule is enable                     | d          |                   |                  |                 |        |

| bit 7-1       | Unimplemen   | ted: Read as 'o                     | )'         |                   |                  |                 |        |

| bit 0         |              | 3 Module Disat                      | ole bit    |                   |                  |                 |        |

|               |              | lule is disabled                    |            |                   |                  |                 |        |

|               | 0 = SP13 mod | lule is enabled                     |            |                   |                  |                 |        |

### REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

### TABLE 11-10: PORTE REGISTER MAP<sup>(1)</sup>

| IADLE I      | 1-10. F |        | LOISILI |        |        |        |       |        |        |       |       |       |       |       |       |       |

|--------------|---------|--------|---------|--------|--------|--------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| File<br>Name | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| TRISE        |         |        |         |        |        |        |       | TRISE< | :15:0> |       |       |       |       |       |       |       |

| PORTE        |         |        |         |        |        |        |       | RE<1   | 5:0>   |       |       |       |       |       |       |       |

| LATE         |         |        |         |        |        |        |       | LATE<  | 15:0>  |       |       |       |       |       |       |       |

| ODCE         |         |        |         |        |        |        |       | ODCE<  | :15:0> |       |       |       |       |       |       |       |

| CNENE        |         |        |         |        |        |        |       | CNIEE< | <15:0> |       |       |       |       |       |       |       |

| CNPUE        |         |        |         |        |        |        |       | CNPUE  | <15:0> |       |       |       |       |       |       |       |

| CNPDE        |         |        |         |        |        |        |       | CNPDE  | <15:0> |       |       |       |       |       |       |       |

| ANSELE       |         | —      | —       | —      | —      | _      | _     | —      | —      |       | _     | _     | _     | _     | _     |       |

**Legend:** — = unimplemented, read as '0'.

Note 1: Refer to Table 11-5 for bit availability on each pin count variant.

| U-0                | R/W-0      | R/W-0                                                        | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|--------------------|------------|--------------------------------------------------------------|---------------|------------------|------------------|-----------------|--------|

| —                  | RP17R6     | RP17R5                                                       | RP17R4        | RP17R3           | RP17R2           | RP17R1          | RP17R0 |

| bit 15             |            |                                                              |               |                  |                  |                 | bit 8  |

|                    |            |                                                              |               |                  |                  |                 |        |

| U-0                | R/W-0      | R/W-0                                                        | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| —                  | RP16R6     | RP16R5                                                       | RP16R4        | RP16R3           | RP16R2           | RP16R1          | RP16R0 |

| bit 7              |            |                                                              |               |                  |                  |                 | bit (  |

| Legend:            |            |                                                              |               |                  |                  |                 |        |

| R = Readable       | e bit      | W = Writable                                                 | bit           | U = Unimpler     | nented bit, read | l as '0'        |        |

| -n = Value at      | POR        | '1' = Bit is set                                             |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15<br>bit 14-8 | RP17R<6:0> | <b>ited:</b> Read as '<br>: Peripheral Ou<br>-13 for periphe | tput Function | •                | RP17 Output F    | Pin bits        |        |

bit 7 Unimplemented: Read as '0'

| bit 6-0 | <b>RP16R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP16 Output Pin bits |

|---------|-----------------------------------------------------------------------------------------|

|         | (see Table 11-13 for peripheral function numbers)                                       |

#### REGISTER 11-34: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0                                                                                                                                                | R/W-0      | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|--------|------------------|------------------|-----------------|--------|--|

| _                                                                                                                                                  | RP19R6     | RP19R5           | RP19R4 | RP19R3           | RP19R2           | RP19R1          | RP19R0 |  |

| bit 15                                                                                                                                             |            |                  |        |                  |                  |                 | bit 8  |  |

|                                                                                                                                                    |            |                  |        |                  |                  |                 |        |  |

| U-0                                                                                                                                                | R/W-0      | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |

| —                                                                                                                                                  | RP18R6     | RP18R5           | RP18R4 | RP18R3           | RP18R2           | RP18R1          | RP18R0 |  |

| bit 7                                                                                                                                              |            |                  |        |                  |                  |                 | bit 0  |  |

|                                                                                                                                                    |            |                  |        |                  |                  |                 |        |  |

| Legend:                                                                                                                                            |            |                  |        |                  |                  |                 |        |  |

| R = Readable                                                                                                                                       | bit        | W = Writable     | bit    | U = Unimpler     | mented bit, read | l as '0'        |        |  |

| -n = Value at I                                                                                                                                    | POR        | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |

|                                                                                                                                                    |            |                  |        |                  |                  |                 |        |  |

| bit 15                                                                                                                                             | Unimplemen | ted: Read as '   | 0'     |                  |                  |                 |        |  |

| bit 14-8 <b>RP19R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP19 Output Pin bits (see Table 11-13 for peripheral function numbers) |            |                  |        |                  |                  |                 |        |  |

bit 7 Unimplemented: Read as '0'

bit 6-0 **RP18R<6:0>:** Peripheral Output Function is Assigned to RP18 Output Pin bits (see Table 11-13 for peripheral function numbers)

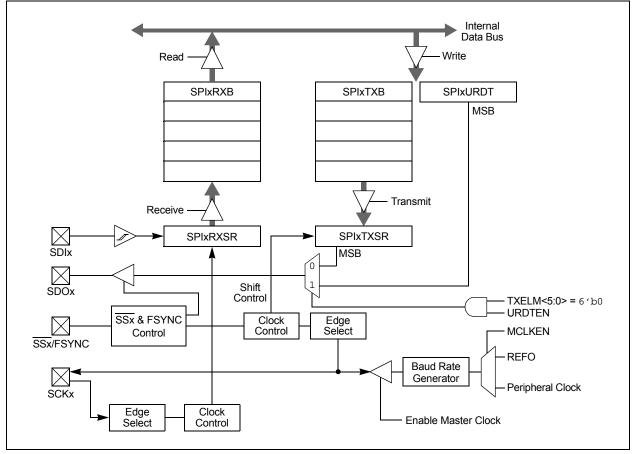

To set up the SPIx module for the Enhanced Buffer Master mode of operation:

- 1. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with MSTEN (SPIxCON1L<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTATL<6>).

- 4. Select Enhanced Buffer mode by setting the ENHBUF bit (SPIxCON1L<0>).

- 5. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

To set up the SPIx module for the Enhanced Buffer Slave mode of operation:

- 1. Clear the SPIxBUFL and SPIxBUFH registers.

- 2. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with the MSTEN bit (SPIxCON1L<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit must be set, thus enabling the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTATL<6>).

- 7. Select Enhanced Buffer mode by setting the ENHBUF bit (SPIxCON1L<0>).

- 8. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

To set up the SPIx module for Audio mode:

- 1. Clear the SPIxBUFL and SPIxBUFH registers.

- 2. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- a) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with AUDEN (SPIxCON1H<15>) = 1.

- 4. Clear the SPIROV bit (SPIxSTATL<6>).

- Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- 6. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

#### REGISTER 18-1: SPIxCON1L: SPIx CONTROL REGISTER 1 LOW

| Legend:<br>R = Readable |       | W = Writable |        |                         | ented bit read          | (0)   |                    |

|-------------------------|-------|--------------|--------|-------------------------|-------------------------|-------|--------------------|

| bit 7                   |       |              |        |                         |                         |       | bit 0              |

| SSEN <sup>(2)</sup>     | CKP   | MSTEN        | DISSDI | DISSCK                  | MCLKEN <sup>(3)</sup>   | SPIFE | ENHBUF             |

| R/W-0                   | R/W-0 | R/W-0        | R/W-0  | R/W-0                   | R/W-0                   | R/W-0 | R/W-0              |

| bit 15                  |       |              |        |                         |                         |       | bit 8              |

| SPIEN                   | _     | SPISIDL      | DISSDO | MODE32 <sup>(1,4)</sup> | MODE16 <sup>(1,4)</sup> | SMP   | CKE <sup>(1)</sup> |

| R/W-0                   | U-0   | R/W-0        | R/W-0  | R/W-0                   | R/W-0                   | R/W-0 | R/W-0              |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 15 SPIEN: SPIx On bit

- 1 = Enables module

- 0 = Turns off and resets module, disables clocks, disables interrupt event generation, allows SFR modifications

#### bit 14 Unimplemented: Read as '0'

- bit 13 SPISIDL: SPIx Stop in Idle Mode bit

- 1 = Halts in CPU Idle mode

- 0 = Continues to operate in CPU Idle mode

#### bit 12 DISSDO: Disable SDOx Output Port bit

1 = SDOx pin is not used by the module; pin is controlled by port function

#### 0 = SDOx pin is controlled by the module

#### bit 11-10 MODE32 and MODE16: Serial Word Length Select bits<sup>(1,4)</sup>

| MODE32 | MODE16 | AUDEN | Communication                                         |  |  |  |  |  |

|--------|--------|-------|-------------------------------------------------------|--|--|--|--|--|

| 1      | x      |       | 32-Bit                                                |  |  |  |  |  |

| 0      | 1      | 0     | 16-Bit                                                |  |  |  |  |  |

| 0      | 0      |       | 8-Bit                                                 |  |  |  |  |  |

| 1      | 1      |       | 24-Bit Data, 32-Bit FIFO, 32-Bit Channel/64-Bit Frame |  |  |  |  |  |

| 1      | 0      | 1     | 32-Bit Data, 32-Bit FIFO, 32-Bit Channel/64-Bit Frame |  |  |  |  |  |

| 0      | 1      | T     | 16-Bit Data, 16-Bit FIFO, 32-Bit Channel/64-Bit Frame |  |  |  |  |  |

| 0      | 0      |       | 16-Bit FIFO, 16-Bit Channel/32-Bit Frame              |  |  |  |  |  |

#### **Note 1:** When AUDEN (SPIxCON1H<15>) = 1, this module functions as if CKE = 0, regardless of its actual value.

- 2: When FRMEN = 1, SSEN is not used.

- 3: MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows FRMSYPW.

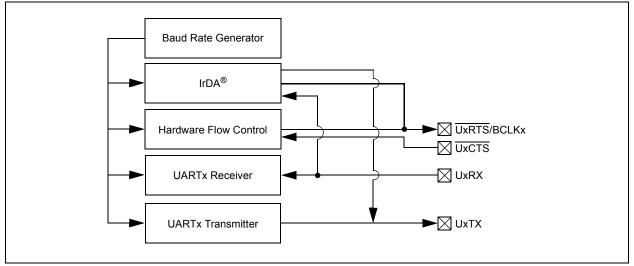

### 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/ 80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGS70X/80X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGS70X/80X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps in 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps in 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

### FIGURE 20-1: UARTX SIMPLIFIED BLOCK DIAGRAM

### 22.2 Analog-to-Digital Converter Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 22.2.1 KEY RESOURCES

- "12-Bit High-Speed, Multiple SARs A/D Converter (ADC)" (DS70005213) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### REGISTER 22-1: ADCON1L: ADC CONTROL REGISTER 1 LOW

| R/W-0               | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------------------|-----|--------|-----|-----|-----|-----|-------|

| ADON <sup>(1)</sup> | —   | ADSIDL | —   | —   | —   | —   | —     |

| bit 15              |     |        |     |     |     |     | bit 8 |

|                     |     |        |     |     |     |     |       |

| U-0                 | r-0 | r-0    | r-0 | r-0 | U-0 | U-0 | U-0   |

| —                   | _   | —      | —   |     |     |     | —     |

| bit 7               |     |        |     |     |     |     | bit 0 |

| Legend:           | r = Reserved bit |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

- bit 15 **ADON:** ADC Enable bit<sup>(1)</sup> 1 = ADC module is enabled

- 0 = ADC module is off

- bit 14 Unimplemented: Read as '0'

- bit 13 ADSIDL: ADC Stop in Idle Mode bit

- 1 = Discontinues module operation when device enters Idle mode

- 0 = Continues module operation in Idle mode

- bit 12-7 Unimplemented: Read as '0'

- bit 6-3 Reserved: Maintain as '0'

- bit 2-0 Unimplemented: Read as '0'

- **Note 1:** Set the ADON bit only after the ADC module has been configured. Changing ADC Configuration bits when ADON = 1 will result in unpredictable behavior.

### 26.3 Current Source Control Register

#### REGISTER 26-1: ISRCCON: CONSTANT-CURRENT SOURCE CONTROL REGISTER

| R/W-0                 | U-0                                             | U-0                             | U-0             | U-0              | R/W-0            | R/W-0                                       | R/W-0    |

|-----------------------|-------------------------------------------------|---------------------------------|-----------------|------------------|------------------|---------------------------------------------|----------|

| ISRCEN                |                                                 | —                               | —               | _                | OUTSEL2          | OUTSEL1                                     | OUTSEL0  |

| bit 15                |                                                 |                                 |                 |                  |                  |                                             | bit 8    |

|                       |                                                 |                                 |                 |                  |                  |                                             |          |

| U-0                   | U-0                                             | R/W-0                           | R/W-0           | R/W-0            | R/W-0            | R/W-0                                       | R/W-0    |

| —                     |                                                 | ISRCCAL5                        | ISRCCAL4        | ISRCCAL3         | ISRCCAL2         | ISRCCAL1                                    | ISRCCAL0 |

| bit 7                 |                                                 |                                 |                 |                  |                  |                                             | bit C    |

| Legend:               |                                                 |                                 |                 |                  |                  |                                             |          |

| R = Readable          | e bit                                           | W = Writable                    | bit             | U = Unimpler     | mented bit, read | d as '0'                                    |          |

| -n = Value at         | POR                                             | '1' = Bit is set                |                 | '0' = Bit is cle | ared             | x = Bit is unkr                             | nown     |

| bit 14-11<br>bit 10-8 | -                                               | ted: Read as '<br>>: Output Con |                 | Select bits      |                  |                                             |          |

|                       | 011 = Input p<br>010 = Input p<br>001 = Input p | ed                              | 5)<br>6)        |                  |                  |                                             |          |

| bit 7-6               | Unimplemen                                      | ted: Read as '                  | 0'              |                  |                  |                                             |          |

| bit 5-0               | ISRCCAL<5:                                      | 0>: Constant-C                  | Current Source  | e Calibration bi | ts               |                                             |          |

|                       | module is ena                                   |                                 | the calibration |                  |                  | 8, into these b<br>7-3) in <b>Section</b> : |          |

| Field | Description                                                                                                                                                                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm*Wm | Multiplicand and Multiplier Working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                                        |

| Wm*Wn | Multiplicand and Multiplier Working register pair for DSP instructions $\in$ {W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                       |

| Wn    | One of 16 Working registers $\in$ {W0W15}                                                                                                                                                                                                                            |

| Wnd   | One of 16 Destination Working registers ∈ {W0W15}                                                                                                                                                                                                                    |

| Wns   | One of 16 Source Working registers ∈ {W0W15}                                                                                                                                                                                                                         |

| WREG  | W0 (Working register used in file register instructions)                                                                                                                                                                                                             |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                                         |

| Wso   | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                                      |

| Wx    | X Data Space Prefetch Address register for DSP instructions<br>∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2,<br>[W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2,<br>[W9 + W12], none}                |

| Wxd   | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |

| Wy    | Y Data Space Prefetch Address register for DSP instructions<br>∈ {[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - = 2,<br>[W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = 2,<br>[W11 + W12], none} |

| Wyd   | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |

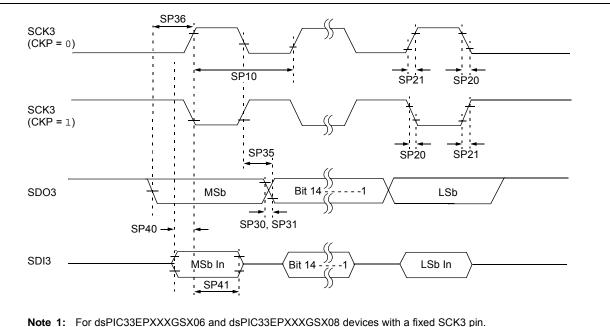

## TABLE 30-36:SPI1, SPI2 AND SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)TIMING REQUIREMENTS<sup>(5)</sup>

| AC CHARACTERISTICS |                       |                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                                |

|--------------------|-----------------------|----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|--------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                  | Тур. <sup>(2)</sup> | Max. | Units | Conditions                     |

| SP70               | FscP                  | Maximum SCKx Input Frequency                 |                                                       |                     | 11   | MHz   | (Note 3)                       |

| SP72               | TscF                  | SCKx Input Fall Time                         |                                                       |                     |      | ns    | See Parameter DO32<br>(Note 4) |

| SP73               | TscR                  | SCKx Input Rise Time                         | —                                                     | _                   | _    | ns    | See Parameter DO31<br>(Note 4  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                   | —                                                     | _                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP31               | TdoR                  | SDOx Data Output Rise Time                   | —                                                     | _                   | _    | ns    | See Parameter DO31 (Note 4)    |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    | —                                                     | 6                   | 20   | ns    |                                |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge | 30                                                    | _                   | _    | ns    |                                |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge   | 30                                                    | _                   | _    | ns    |                                |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge    | 30                                                    | —                   |      | ns    |                                |

| SP50               | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↑ or SCKx ↓<br>Input           | 120                                                   | —                   | _    | ns    |                                |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance       | 10                                                    | —                   | 50   | ns    | (Note 4)                       |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                        | 1.5 Tcy + 40                                          | _                   | _    | ns    | (Note 4)                       |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge     | —                                                     | —                   | 50   | ns    |                                |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

5: Pertaining to SPI3: dsPIC33EPXXXGS702, dsPIC33EPXXXGSX04 and dsPIC33EPXXXGSX05 devices with a remappable SCK3 pin.

2: Refer to Figure 30-1 for load conditions.

## TABLE 30-41:SPI3 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1)TIMING REQUIREMENTS<sup>(5)</sup>

| AC CHARACTERISTICS |                       |                                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                             |

|--------------------|-----------------------|-----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP10               | FscP                  | Maximum SCK3 Frequency                        | _                                                     | _                   | 25   | MHz   | (Note 3)                    |

| SP20               | TscF                  | SCK3 Output Fall Time                         | _                                                     |                     | _    | ns    | See Parameter DO32 (Note 4) |

| SP21               | TscR                  | SCK3 Output Rise Time                         | _                                                     |                     | _    | ns    | See Parameter DO31 (Note 4) |

| SP30               | TdoF                  | SDO3 Data Output Fall Time                    | _                                                     | _                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP31               | TdoR                  | SDO3 Data Output Rise Time                    | —                                                     |                     | _    | ns    | See Parameter DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO3 Data Output Valid after SCK3 Edge        | _                                                     | 6                   | 20   | ns    |                             |

| SP36               | TdoV2sc,<br>TdoV2scL  | SDO3 Data Output Setup to<br>First SCK3 Edge  | 20                                                    | —                   | _    | ns    |                             |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI3 Data<br>Input to SCK3 Edge | 20                                                    | _                   | _    | ns    |                             |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI3 Data Input to SCK3 Edge     | 15                                                    | —                   |      | ns    |                             |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK3 is 100 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPI3 pins.

- 5: For dsPIC33EPXXXGSX06 and dsPIC33EPXXXGSX08 devices with a fixed SCK3 pin.

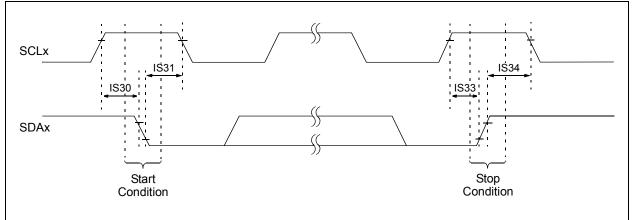

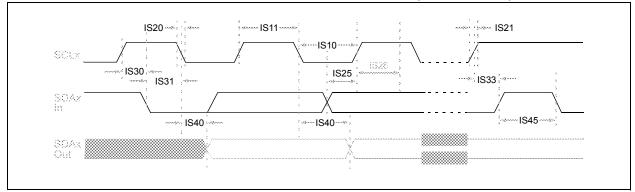

| AC CHARACTERISTICS |                            |                  |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |            |                        |  |

|--------------------|----------------------------|------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|------------------------|--|

| Param<br>No.       | Symbol                     | Characte         | eristic <sup>(4)</sup>    | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                                     | Max. | Units      | Conditions             |  |

| IM10               | M10 TLO:SCL Clock Low Time |                  | 100 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                         |      | μS         |                        |  |

|                    |                            |                  | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         | —    | μS         |                        |  |

|                    |                            |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         | —    | μS         |                        |  |

| IM11               | THI:SCL                    | Clock High Time  | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         | _    | μS         |                        |  |

|                    |                            |                  | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         | _    | μS         |                        |  |

|                    |                            |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         | _    | μS         |                        |  |

| IM20               | TF:SCL                     | SDAx and SCLx    | 100 kHz mode              | _                                                                                                                                                                                                                                                                                       | 300  | ns         | CB is specified to be  |  |

|                    |                            | Fall Time        | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                             | 300  | ns         | from 10 to 400 pF      |  |

|                    |                            |                  | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                                                                                                                       | 100  | ns         |                        |  |

| IM21               | TR:SCL                     | SDAx and SCLx    | 100 kHz mode              | —                                                                                                                                                                                                                                                                                       | 1000 | ns         | CB is specified to be  |  |

|                    |                            | Rise Time        | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                             | 300  | ns         | from 10 to 400 pF      |  |

|                    |                            |                  | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                                                                                                                                       | 300  | ns         | -                      |  |

| IM25               | TSU:DAT                    | Data Input       | 100 kHz mode              | 250                                                                                                                                                                                                                                                                                     |      | ns         |                        |  |

|                    |                            | Setup Time       | 400 kHz mode              | 100                                                                                                                                                                                                                                                                                     |      | ns         | -                      |  |

|                    |                            |                  | 1 MHz mode <sup>(2)</sup> | 40                                                                                                                                                                                                                                                                                      |      | ns         | -                      |  |

| IM26               | THD:DAT                    | Data Input       | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                       |      | μS         |                        |  |

|                    |                            | Hold Time        | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                       | 0.9  | μ <b>S</b> | -                      |  |

|                    |                            |                  | 1 MHz mode <sup>(2)</sup> | 0.2                                                                                                                                                                                                                                                                                     |      | μs         | -                      |  |

| IM30               | TSU:STA                    | Start Condition  | 100 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                         |      | μS         | Only relevant for      |  |

|                    |                            | Setup Time       | 400 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                         |      | μ <b>S</b> | Repeated Start         |  |

|                    |                            |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                         |      | μS         | condition              |  |

| IM31               | THD:STA                    | Start Condition  | 100 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                         |      | μS         | After this period, the |  |

|                    |                            | Hold Time        | 400 kHz mode              | Tcy/2 (BRG +2)                                                                                                                                                                                                                                                                          |      | μ <b>S</b> | first clock pulse is   |  |

|                    |                            |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         |      | μS         | generated              |  |

| IM33               | Tsu:sto                    | Stop Condition   | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         |      | μS         |                        |  |

|                    |                            | Setup Time       | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         |      | μS         |                        |  |

|                    |                            |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                         |      | μS         |                        |  |

| IM34               | THD:STO                    | Stop Condition   | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         |      | μS         |                        |  |

|                    |                            | Hold Time        | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         |      | μS         |                        |  |

|                    |                            |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         |      | μS         | -                      |  |

| IM40               | TAA:SCL                    | Output Valid     | 100 kHz mode              |                                                                                                                                                                                                                                                                                         | 3500 | ns         |                        |  |

|                    |                            | from Clock       | 400 kHz mode              | —                                                                                                                                                                                                                                                                                       | 1000 | ns         |                        |  |

|                    |                            |                  | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                                                                                                                       | 400  | ns         |                        |  |

| IM45               | TBF:SDA                    | A Bus Free Time  | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                     |      | μs         | Time the bus must be   |  |

|                    |                            |                  | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                                     |      | μS         | free before a new      |  |

|                    |                            |                  | 1 MHz mode <sup>(2)</sup> | 0.5                                                                                                                                                                                                                                                                                     |      | ,<br>μs    | transmission can start |  |

| IM50               | Св                         | Bus Capacitive L |                           | _                                                                                                                                                                                                                                                                                       | 400  | pF         |                        |  |

| IM51               | TPGD                       | Pulse Gobbler De | •                         | 65                                                                                                                                                                                                                                                                                      | 390  | ns         | (Note 3)               |  |

### TABLE 30-47: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator.

2: Maximum Pin Capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** Typical value for this parameter is 130 ns.

4: These parameters are characterized but not tested in manufacturing.

#### FIGURE 30-29: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (SLAVE MODE)

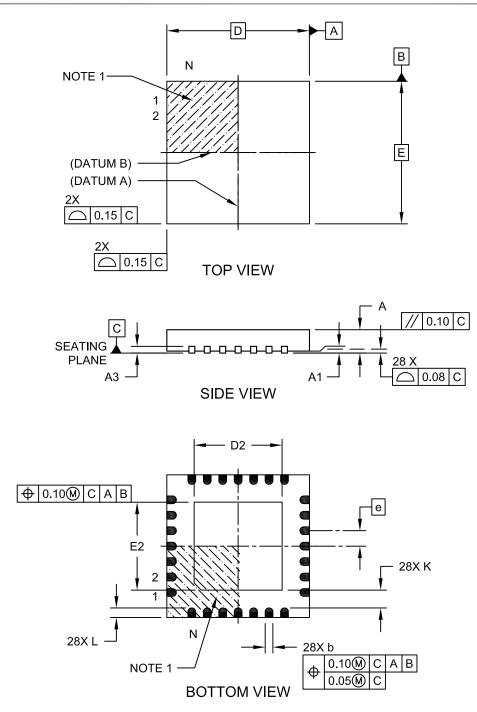

## 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-124C Sheet 1 of 2

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units            |                |          | S    |  |  |

|-------------------------|------------------|----------------|----------|------|--|--|

| Dimension               | Dimension Limits |                |          |      |  |  |

| Number of Pins          | Ν                |                | 44       | -    |  |  |

| Pitch                   | е                |                | 0.65 BSC |      |  |  |

| Overall Height          | А                | 0.80           | 0.90     | 1.00 |  |  |

| Standoff                | A1               | 0.00           | 0.02     | 0.05 |  |  |

| Terminal Thickness      | A3               | 0.20 REF       |          |      |  |  |

| Overall Width           | E                | 8.00 BSC       |          |      |  |  |

| Exposed Pad Width       | E2               | 6.25 6.45 6.6  |          |      |  |  |

| Overall Length          | D                |                | 8.00 BSC |      |  |  |

| Exposed Pad Length      | D2               | 6.25 6.45 6.60 |          |      |  |  |

| Terminal Width          | b                | 0.20           | 0.30     | 0.35 |  |  |

| Terminal Length         | L                | 0.30           | 0.40     | 0.50 |  |  |

| Terminal-to-Exposed-Pad | К                | 0.20           | -        | -    |  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103D Sheet 2 of 2

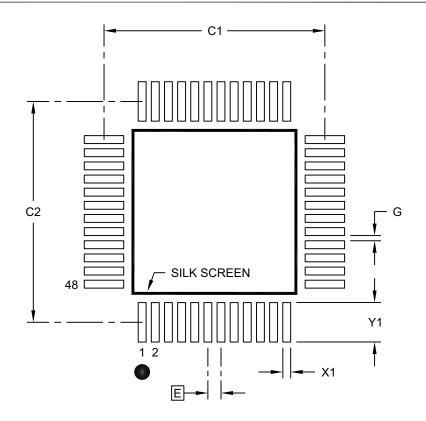

## 48-Lead Thin Quad Flatpack (PT) - 7x7x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                            | Units            |          |      | S    |

|----------------------------|------------------|----------|------|------|

| Dimensio                   | Dimension Limits |          | NOM  | MAX  |

| Contact Pitch              | E                | 0.50 BSC |      |      |

| Contact Pad Spacing        | C1               | 8.40     |      |      |

| Contact Pad Spacing        |                  |          | 8.40 |      |

| Contact Pad Width (X48) X1 |                  |          |      | 0.30 |

| Contact Pad Length (X48)   |                  |          |      | 1.50 |

| Distance Between Pads      | G                | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2300-PT Rev A

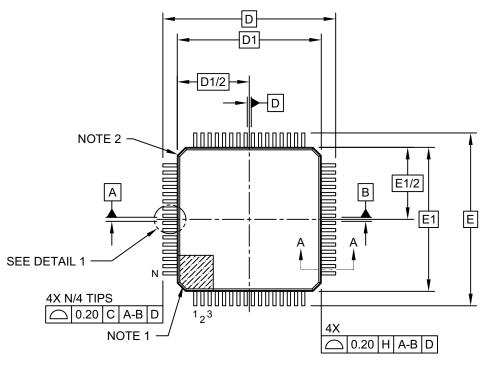

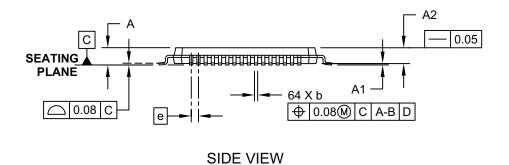

### 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**TOP VIEW**

Microchip Technology Drawing C04-085C Sheet 1 of 2