Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                           |

| Number of I/O              | 20                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 11x12b; D/A 1x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

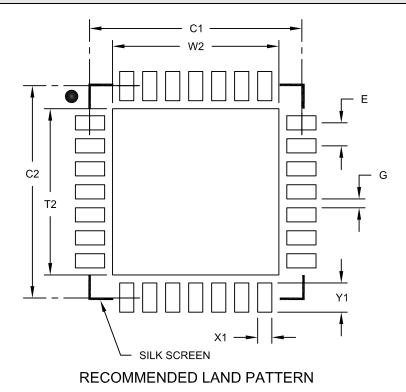

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs702t-i-mm |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                                       |     |

|-------|-----------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Digital Signal Controllers |     |

| 3.0   | CPU                                                                   |     |

| 4.0   | Memory Organization                                                   |     |

| 5.0   | Flash Program Memory                                                  |     |

| 6.0   | Resets                                                                |     |

| 7.0   | Interrupt Controller                                                  |     |

| 8.0   | Direct Memory Access (DMA)                                            |     |

| 9.0   | Oscillator Configuration                                              | 103 |

| 10.0  | Power-Saving Features                                                 | 115 |

| 11.0  | I/O Ports                                                             | 125 |

| 12.0  | Timer1                                                                |     |

| 13.0  | Timer2/3 and Timer4/5                                                 | 173 |

| 14.0  | Input Capture                                                         | 177 |

| 15.0  | Output Compare                                                        | 181 |

| 16.0  | High-Speed PWM                                                        |     |

| 17.0  |                                                                       |     |

| 18.0  |                                                                       |     |

| 19.0  |                                                                       |     |

| 20.0  |                                                                       |     |

| 21.0  |                                                                       |     |

| 22.0  | <b>J</b> - [ <b>J J J J</b>                                           |     |

| 23.0  |                                                                       |     |

| 24.0  | High-Speed Analog Comparator                                          |     |

| 25.0  |                                                                       |     |

| 26.0  | Constant-Current Source                                               |     |

| 27.0  | Special Features                                                      |     |

| 28.0  | Instruction Set Summary                                               |     |

| 29.0  |                                                                       |     |

| 30.0  |                                                                       |     |

|       | DC and AC Device Characteristics Graphs                               |     |

|       | Packaging Information                                                 |     |

| Appe  | endix A: Revision History                                             |     |

| Index | Χ                                                                     |     |

|       | Microchip Web Site                                                    |     |

|       | omer Change Notification Service                                      |     |

|       | omer Support                                                          |     |

| Prod  | uct Identification System                                             |     |

#### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER

| R/W-0      |                                   | R/W-1                           | R/W-1                | R/W-0                                | R/W-0              | R/W-0             | R/W-0              |

|------------|-----------------------------------|---------------------------------|----------------------|--------------------------------------|--------------------|-------------------|--------------------|

| ROI        | DOZE2 <sup>(1)</sup>              | DOZE1 <sup>(1)</sup>            | DOZE0 <sup>(1)</sup> | DOZEN <sup>(2,3)</sup>               | FRCDIV2            | FRCDIV1           | FRCDIV0            |

| bit 15     |                                   |                                 |                      |                                      |                    |                   | bit 8              |

|            |                                   |                                 |                      |                                      |                    |                   |                    |

| R/W-0      |                                   | U-0                             | R/W-0                | R/W-0                                | R/W-0              | R/W-0             | R/W-0              |

| PLLPOS     | T1 PLLPOST0                       |                                 | PLLPRE4              | PLLPRE3                              | PLLPRE2            | PLLPRE1           | PLLPRE0            |

| bit 7      |                                   |                                 |                      |                                      |                    |                   | bit 0              |

| Legend:    |                                   |                                 |                      |                                      |                    |                   |                    |

| R = Read   | able bit                          | W = Writable                    | hit                  | II = I Inimplem                      | nented bit, read   | 1 as 'N'          |                    |

| -n = Value |                                   | '1' = Bit is set                |                      | '0' = Bit is clea                    |                    | x = Bit is unkr   |                    |

|            |                                   |                                 |                      |                                      | arca               |                   | IOWIT              |

| bit 15     | ROI: Recover                      | r on Interrupt bi               | t                    |                                      |                    |                   |                    |

| bit 10     |                                   | •                               |                      | he processor clo                     | ock and the ne     | ripheral clock ra | ntio is set to 1.1 |

|            |                                   | s have no effect                |                      |                                      | boll, and the po   |                   |                    |

| bit 14-12  | DOZE<2:0>:                        | Processor Cloc                  | k Reduction S        | elect bits <sup>(1)</sup>            |                    |                   |                    |

|            | 111 = Fcy div                     |                                 |                      |                                      |                    |                   |                    |

|            | 110 = Fcy div                     |                                 |                      |                                      |                    |                   |                    |

|            | 101 = Fcy div                     |                                 |                      |                                      |                    |                   |                    |

|            | 100 = FCY div                     |                                 |                      |                                      |                    |                   |                    |

|            |                                   | vided by 8 (defa                | ault)                |                                      |                    |                   |                    |

|            | 010 = FCY div<br>001 = FCY div    | •                               |                      |                                      |                    |                   |                    |

|            | 000 = FCY div                     |                                 |                      |                                      |                    |                   |                    |

| bit 11     |                                   | e Mode Enable                   | bit <sup>(2,3)</sup> |                                      |                    |                   |                    |

|            |                                   |                                 |                      | ween the peripl<br>atio is forced to |                    | d the processo    | r clocks           |

| bit 10-8   | FRCDIV<2:0>                       | >: Internal Fast                | RC Oscillator        | Postscaler bits                      |                    |                   |                    |

|            | 111 <b>= FRC di</b>               |                                 |                      |                                      |                    |                   |                    |

|            | 110 <b>= FRC di</b>               |                                 |                      |                                      |                    |                   |                    |

|            | 101 <b>= FRC d</b> i              |                                 |                      |                                      |                    |                   |                    |

|            | 100 <b>= FRC d</b> i              |                                 |                      |                                      |                    |                   |                    |

|            | 011 <b>= FRC di</b>               |                                 |                      |                                      |                    |                   |                    |

|            | 010 = FRC di                      |                                 |                      |                                      |                    |                   |                    |

|            | 001 = FRC di                      | ivided by 2<br>ivided by 1 (def | ault)                |                                      |                    |                   |                    |

| bit 7-6    |                                   |                                 | ,                    | Select bits (also                    | o denoted as 'I    | N2' PLL postso    | aler)              |

|            | 11 = Output d                     |                                 |                      |                                      |                    | 12, 1 LL posise   |                    |

|            | 10 = Reserve                      | •                               |                      |                                      |                    |                   |                    |

|            |                                   | livided by 4 (de                | fault)               |                                      |                    |                   |                    |

|            | 00 = Output d                     | livided by 2                    |                      |                                      |                    |                   |                    |

| bit 5      | Unimplemen                        | ted: Read as 'o                 | )'                   |                                      |                    |                   |                    |

| Note 1:    | The DOZE<2:0><br>DOZE<2:0> are iş | •                               | e written to whe     | en the DOZEN                         | bit is clear. If D | OZEN = 1, any     | v writes to        |

| 2:         | This bit is cleared               | -                               | bit is set and a     | an interrupt occ                     | urs.               |                   |                    |

| 3:         | The DOZEN bit ca                  |                                 |                      | •                                    |                    | y attempt by us   | er software to     |

**3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| REGISTER         | 9-0. KEFU                                                                                                                                                                                                                                                  | CON. REFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LENCE USC                                                                                                                                                                                                             | ILLATOR CO            |                       | ISTER                 |                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| R/W-0            | U-0                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

| ROON             |                                                                                                                                                                                                                                                            | ROSSLP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ROSEL                                                                                                                                                                                                                 | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |

| bit 15           |                                                                                                                                                                                                                                                            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       | •                     | •                     | •                     | bit 8                 |

|                  |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| U-0              | U-0                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                   | U-0                   | U-0                   | U-0                   | U-0                   |

| <br>bit 7        | _                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       | _                     | _                     | _                     | bit (                 |

|                  |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| Legend:          |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| R = Readabl      | le bit                                                                                                                                                                                                                                                     | W = Writable I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | pit                                                                                                                                                                                                                   | U = Unimplem          | nented bit, read      | l as '0'              |                       |

| -n = Value at    | t POR                                                                                                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                       | '0' = Bit is clea     | ared                  | x = Bit is unkn       | iown                  |

| bit 15<br>bit 14 | 1 = Reference<br>0 = Reference                                                                                                                                                                                                                             | ence Oscillator<br>e oscillator outp<br>e oscillator outp<br>ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ut is enabled o<br>ut is disabled                                                                                                                                                                                     |                       | 2)                    |                       |                       |

| bit 13           | -                                                                                                                                                                                                                                                          | ference Oscilla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       | an hit                |                       |                       |                       |

| bit 15           | 1 = Reference                                                                                                                                                                                                                                              | e oscillator outp<br>oscillator outp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ut continues to                                                                                                                                                                                                       | run in Sleep          |                       |                       |                       |

| bit 12           | 1 = Oscillator                                                                                                                                                                                                                                             | rence Oscillato<br>crystal is used<br>ock is used as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | as the referen                                                                                                                                                                                                        | ce clock              |                       |                       |                       |

| bit 11-8         | 1111 = Refer<br>1110 = Refer<br>1101 = Refer<br>100 = Refer<br>1011 = Refer<br>1010 = Refer<br>1001 = Refer<br>000 = Refer<br>0111 = Refer<br>0110 = Refer<br>0101 = Refer<br>0101 = Refer<br>0101 = Refer<br>0101 = Refer<br>0100 = Refer<br>0100 = Refer | Reference Ose<br>ence clock dividence clock | ded by 32,768<br>ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 | bits <sup>(1)</sup>   |                       |                       |                       |

| bit 7-0          | Unimplement                                                                                                                                                                                                                                                | ted: Read as 'o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | )'                                                                                                                                                                                                                    |                       |                       |                       |                       |

|                  |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                       |                       |                       |                       |

#### REGISTER 9-6: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.6 "Peripheral Pin Select (PPS)" for more information.

### 11.6 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features, while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.6.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions.

#### 11.6.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. One example includes  $I^2C$  modules. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/Os and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.6.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### REGISTER 11-15: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| OCFAR7 | OCFAR6 | OCFAR5 | OCFAR4 | OCFAR3 | OCFAR2 | OCFAR1 | OCFAR0 |

| bit 7  |        |        |        | •      |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **OCFAR<7:0>:** Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits See Table 11-11 which contains a list of remappable inputs for the index value.

#### REGISTER 11-16: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FLT2R7 | FLT2R6 | FLT2R5 | FLT2R4 | FLT2R3 | FLT2R2 | FLT2R1 | FLT2R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-0  |

| bit 7  |        |        |        |        |        |        | bit 0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FLT1R7 | FLT1R6 | FLT1R5 | FLT1R4 | FLT1R3 | FLT1R2 | FLT1R1 | FLT1R0 |

| R/W-U  | R/VV-U |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8**FLT2R<7:0>:** Assign PWM Fault 2 (FLT2) to the Corresponding RPn Pin bits<br/>See Table 11-11 which contains a list of remappable inputs for the index value.bit 7-0**FLT1R<7:0>:** Assign PWM Fault 1 (FLT1) to the Corresponding RPn Pin bits<br/>See Table 11-11 which contains a list of remappable inputs for the index value.

© 2016-2017 Microchip Technology Inc.

| U-0               | R/W-0  | R/W-0            | R/W-0  | R/W-0                          | R/W-0  | R/W-0              | R/W-0  |

|-------------------|--------|------------------|--------|--------------------------------|--------|--------------------|--------|

| —                 | RP53R6 | RP53R5           | RP53R4 | RP53R3                         | RP53R2 | RP53R1             | RP53R0 |

| bit 15            |        |                  |        |                                |        |                    | bit 8  |

|                   |        |                  |        |                                |        |                    |        |

| U-0               | R/W-0  | R/W-0            | R/W-0  | R/W-0                          | R/W-0  | R/W-0              | R/W-0  |

| —                 | RP52R6 | RP52R5           | RP52R4 | RP52R3                         | RP52R2 | RP52R1             | RP52R0 |

| bit 7             |        |                  |        |                                |        | bit 0              |        |

|                   |        |                  |        |                                |        |                    |        |

| Legend:           |        |                  |        |                                |        |                    |        |

| R = Readable bit  |        | W = Writable bit |        | U = Unimplemented bit, read as |        | l as '0'           |        |

| -n = Value at POR |        | '1' = Bit is set |        | '0' = Bit is cleared           |        | x = Bit is unknown |        |

#### REGISTER 11-45: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

| bit 15   | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-8 | <b>RP53R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP53 Output Pin bits (see Table 11-13 for peripheral function numbers) |

| bit 7    | Unimplemented: Read as '0'                                                                                                                |

| bit 6-0  | <b>RP52R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP52 Output Pin bits (see Table 11-13 for peripheral function numbers) |

#### **REGISTER 11-46: RPOR13: PERIPHERAL PIN SELECT OUTPUT REGISTER 13**

| U-0           | R/W-0                      | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |

|---------------|----------------------------|------------------|--------|------------------------------------|--------|--------------------|--------|

| —             | RP55R6                     | RP55R5           | RP55R4 | RP55R3                             | RP55R2 | RP55R1             | RP55R0 |

| bit 15        |                            |                  |        |                                    |        |                    | bit 8  |

|               |                            |                  |        |                                    |        |                    |        |

| U-0           | R/W-0                      | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |

|               | RP54R6                     | RP54R5           | RP54R4 | RP54R3                             | RP54R2 | RP54R1             | RP54R0 |

| bit 7         |                            |                  |        |                                    |        |                    | bit 0  |

|               |                            |                  |        |                                    |        |                    |        |

| Legend:       |                            |                  |        |                                    |        |                    |        |

| R = Readable  | bit                        | W = Writable     | bit    | U = Unimplemented bit, read as '0' |        |                    |        |

| -n = Value at | POR                        | '1' = Bit is set |        | '0' = Bit is cleared               |        | x = Bit is unknown |        |

|               |                            |                  |        |                                    |        |                    |        |

| bit 15        | Unimplemented: Read as '0' |                  |        |                                    |        |                    |        |

| bit 14-8      | -                          |                  |        |                                    |        |                    |        |

|               |                            |                  |        |                                    |        |                    |        |

- bit 7 **Unimplemented:** Read as '0'

- RP54R<6:0>: Peripheral Output Function is Assigned to RP54 Output Pin bits bit 6-0 (see Table 11-13 for peripheral function numbers)

#### REGISTER 11-53: RPOR20: PERIPHERAL PIN SELECT OUTPUT REGISTER 20

| U-0                   | R/W-0  | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |

|-----------------------|--------|------------------|--------|------------------------------------|--------|--------------------|--------|

| 00                    | -      |                  |        | -                                  |        | _                  | -      |

| —                     | RP70R6 | RP70R5           | RP70R4 | RP70R3                             | RP70R2 | RP70R1             | RP70R0 |

| bit 15                |        |                  |        |                                    |        |                    | bit 8  |

|                       |        |                  |        |                                    |        |                    |        |

| U-0                   | R/W-0  | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |

| _                     | RP69R6 | RP69R5           | RP69R4 | RP69R3                             | RP69R2 | RP69R1             | RP69R0 |

| bit 7                 |        |                  |        |                                    |        |                    | bit 0  |

|                       |        |                  |        |                                    |        |                    |        |

| Legend:               |        |                  |        |                                    |        |                    |        |

| R = Readable b        | pit    | W = Writable     | bit    | U = Unimplemented bit, read as '0' |        |                    |        |

| -n = Value at POR '1' |        | '1' = Bit is set |        | '0' = Bit is cleared               |        | x = Bit is unknown |        |

| bit 10   |                                                                                                                                           |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-8 | <b>RP70R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP70 Output Pin bits (see Table 11-13 for peripheral function numbers) |

| bit 7    | Unimplemented: Read as '0'                                                                                                                |

| bit 6-0  | <b>RP69R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP69 Output Pin bits (see Table 11-13 for peripheral function numbers) |

#### REGISTER 11-54: RPOR21: PERIPHERAL PIN SELECT OUTPUT REGISTER 21

| U-0    | R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| —      | RP72R6 | RP72R5 | RP72R4 | RP72R3 | RP72R2 | RP72R1 | RP72R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| U-0    | R/W-0  |

| _      | RP71R6 | RP71R5 | RP71R4 | RP71R3 | RP71R2 | RP71R1 | RP71R0 |

| bit 7  |        |        |        | •      |        |        | bit 0  |

|        |        |        |        |        |        |        |        |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15 Unimplemented: Read as '0'

| bit 14-8 | RP72R<6:0>: Peripheral Output Function is Assigned to RP72 Output Pin bits |  |  |  |  |  |  |

|----------|----------------------------------------------------------------------------|--|--|--|--|--|--|

|          | (see Table 11-13 for peripheral function numbers)                          |  |  |  |  |  |  |

|          |                                                                            |  |  |  |  |  |  |

- bit 7 Unimplemented: Read as '0'

- bit 6-0 **RP71R<6:0>:** Peripheral Output Function is Assigned to RP71 Output Pin bits (see Table 11-13 for peripheral function numbers)

NOTES:

### REGISTER 19-3: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 4 | P: Stop bit                                                                                                                                                                                                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> <li>Hardware is set or clear when a Start, Repeated Start or Stop is detected.</li> </ul>                                           |

| bit 3 | S: Start bit                                                                                                                                                                                                                                       |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> <li>Hardware is set or clear when a Start, Repeated Start or Stop is detected.</li> </ul>                     |

| bit 2 | <b>R_W:</b> Read/Write Information bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                          |

|       | <ul> <li>1 = Read – Indicates data transfer is output from the slave</li> <li>0 = Write – Indicates data transfer is input to the slave</li> <li>Hardware is set or clear after reception of an I<sup>2</sup>C device address byte.</li> </ul>     |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                                                |

|       | <ul> <li>1 = Receive is complete, I2CxRCV is full</li> <li>0 = Receive is not complete, I2CxRCV is empty</li> <li>Hardware is set when I2CxRCV is written with a received byte. Hardware is clear when software reads</li> <li>I2CxRCV.</li> </ul> |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                               |

|       | <ul> <li>1 = Transmit is in progress, I2CxTRN is full</li> <li>0 = Transmit is complete, I2CxTRN is empty</li> <li>Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of a data transmission.</li> </ul>             |

#### REGISTER 22-4: ADCON2H: ADC CONTROL REGISTER 2 HIGH

| R-0, HSC      | R-0, HSC | r-0 | r-0 | r-0 | r-0 | R/W-0    | R/W-0    |

|---------------|----------|-----|-----|-----|-----|----------|----------|

| REFRDY        | REFERR   | —   | —   | —   | —   | SHRSAMC9 | SHRSAMC8 |

| bit 15 bit 15 |          |     |     |     |     |          | bit 8    |

| R/W-0     | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|-----------|----------|----------|----------|----------|----------|----------|----------|

| SHRSAMC7  | SHRSAMC6 | SHRSAMC5 | SHRSAMC4 | SHRSAMC3 | SHRSAMC2 | SHRSAMC1 | SHRSAMC0 |

| bit 7 bit |          |          |          |          |          |          | bit 0    |

| Legend: r = Reserved bit |                  | U = Unimplemented bit, read as '0'      |  |  |  |

|--------------------------|------------------|-----------------------------------------|--|--|--|

| R = Readable bit         | W = Writable bit | HSC = Hardware Settable/Clearable bit   |  |  |  |

| -n = Value at POR        | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |  |  |

| bit 15    | <b>REFRDY:</b> Band Gap and Reference Voltage Ready Flag bit<br>1 = Band gap is ready<br>0 = Band gap is not ready                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14    | <b>REFERR:</b> Band Gap or Reference Voltage Error Flag bit<br>1 = Band gap was removed after the ADC module was enabled (ADON = 1)<br>0 = No band gap error was detected                                        |

| bit 13-10 | Reserved: Maintain as '0'                                                                                                                                                                                        |

| bit 9-0   | <pre>SHRSAMC&lt;9:0&gt;: Shared ADC Core Sample Time Selection bits These bits specify the number of shared ADC Core Clock Periods (TADCORE) for the shared ADC core sample time. 111111111 = 1025 TADCORE</pre> |

REGISTER 23-2: CxCTRL2: CANx CONTROL REGISTER 2

| U-0           | U-0                                                                                       | U-0              | U-0             | U-0                                | U-0        | U-0                | U-0   |  |  |

|---------------|-------------------------------------------------------------------------------------------|------------------|-----------------|------------------------------------|------------|--------------------|-------|--|--|

| —             | —                                                                                         | —                | —               | —                                  | —          | —                  | —     |  |  |

| bit 15        |                                                                                           |                  |                 |                                    |            | •                  | bit 8 |  |  |

|               |                                                                                           |                  |                 |                                    |            |                    |       |  |  |

| U-0           | U-0                                                                                       | U-0              | R-0             | R-0                                | R-0        | R-0                | R-0   |  |  |

|               | —                                                                                         | —                |                 |                                    | DNCNT<4:0> |                    |       |  |  |

| bit 7 bit     |                                                                                           |                  |                 |                                    |            | bit 0              |       |  |  |

|               |                                                                                           |                  |                 |                                    |            |                    |       |  |  |

| Legend:       |                                                                                           |                  |                 |                                    |            |                    |       |  |  |

| R = Readable  | e bit                                                                                     | W = Writable     | bit             | U = Unimplemented bit, read as '0' |            |                    |       |  |  |

| -n = Value at | POR                                                                                       | '1' = Bit is set |                 | '0' = Bit is cleared               |            | x = Bit is unknown |       |  |  |

|               |                                                                                           |                  |                 |                                    |            |                    |       |  |  |

| bit 15-5      | Unimplemen                                                                                | ted: Read as '   | כ'              |                                    |            |                    |       |  |  |

| bit 4-0       | DNCNT<4:0>                                                                                | : DeviceNet™     | Filter Bit Num  | ber bits                           |            |                    |       |  |  |

|               | 10010-11111                                                                               | = Invalid sele   | ction           |                                    |            |                    |       |  |  |

|               | 10001 <b>= Corr</b>                                                                       | pare up to Dat   | a Byte 3, bit 6 | with EID<17>                       | •          |                    |       |  |  |

|               | •                                                                                         |                  |                 |                                    |            |                    |       |  |  |

|               | •                                                                                         |                  |                 |                                    |            |                    |       |  |  |

|               | -00001 = Corr                                                                             | nare un to Dat   | a Byte 1 bit 7  | with FID<0>                        |            |                    |       |  |  |

|               | 00001 = Compare up to Data Byte 1, bit 7 with EID<0><br>00000 = Do not compare data bytes |                  |                 |                                    |            |                    |       |  |  |

|               |                                                                                           |                  |                 |                                    |            |                    |       |  |  |

#### REGISTER 23-8: CxEC: CANX TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0      |

|----------|----------|----------|----------|----------|----------|----------|----------|

| TERRCNT7 | TERRCNT6 | TERRCNT5 | TERRCNT4 | TERRCNT3 | TERRCNT2 | TERRCNT1 | TERRCNT0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R-0      |

|----------|----------|----------|----------|----------|----------|----------|----------|

| RERRCNT7 | RERRCNT6 | RERRCNT5 | RERRCNT4 | RERRCNT3 | RERRCNT2 | RERRCNT1 | RERRCNT0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 TERRCNT<7:0>: Transmit Error Count bits

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

#### REGISTER 23-9: CxCFG1: CANx BAUD RATE CONFIGURATION REGISTER 1

| U-0                       | U-0                                                                                                                                | U-0                                                                                                                      | U-0                                                   | U-0               | U-0              | U-0                | U-0   |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------|------------------|--------------------|-------|--|

| 0-0                       | 0-0                                                                                                                                | 0-0                                                                                                                      | 0-0                                                   | 0-0               | 0-0              | 0-0                | 0-0   |  |

|                           | _                                                                                                                                  |                                                                                                                          | _                                                     | —                 | _                |                    |       |  |

| bit 15                    |                                                                                                                                    |                                                                                                                          |                                                       |                   |                  |                    | bit 8 |  |

|                           |                                                                                                                                    |                                                                                                                          |                                                       |                   |                  |                    |       |  |

| R/W-0                     | /W-0 R/W-0 R/W-0 R/W-0 R/W                                                                                                         |                                                                                                                          |                                                       | R/W-0             | R/W-0            | R/W-0              |       |  |

| SJW1                      | SJW0                                                                                                                               | BRP5                                                                                                                     | BRP4                                                  | BRP3              | BRP2             | BRP1               | BRP0  |  |

| bit 7                     |                                                                                                                                    |                                                                                                                          |                                                       |                   |                  |                    | bit ( |  |

|                           |                                                                                                                                    |                                                                                                                          |                                                       |                   |                  |                    |       |  |

| Legend:                   |                                                                                                                                    |                                                                                                                          |                                                       |                   |                  |                    |       |  |

| R = Readabl               | le bit                                                                                                                             | W = Writable                                                                                                             | bit                                                   | U = Unimplen      | nented bit, read | l as '0'           |       |  |

|                           |                                                                                                                                    |                                                                                                                          |                                                       |                   |                  | x = Bit is unknown |       |  |

| -n = Value at             | t POR                                                                                                                              | '1' = Bit is set                                                                                                         |                                                       | '0' = Bit is clea | ared             | x = Bit is unkr    | nown  |  |

| -n = Value at             | t POR                                                                                                                              | '1' = Bit is set                                                                                                         |                                                       | '0' = Bit is clea | ared             | x = Bit is unkr    | IOWN  |  |

| -n = Value at<br>bit 15-8 |                                                                                                                                    | '1' = Bit is set<br>ted: Read as '                                                                                       |                                                       | '0' = Bit is clea | ared             | x = Bit is unkr    | iown  |  |

|                           | Unimplemer                                                                                                                         |                                                                                                                          | 0'                                                    |                   | ared             | x = Bit is unkr    | nown  |  |

| bit 15-8                  | Unimplemer                                                                                                                         | ted: Read as '<br>Synchronization                                                                                        | 0'                                                    |                   | ared             | x = Bit is unkr    | nown  |  |

| bit 15-8                  | Unimplemer<br>SJW<1:0>: S                                                                                                          | t <b>ed:</b> Read as '<br>Synchronization<br>s 4 x TQ                                                                    | 0'                                                    |                   | ared             | x = Bit is unkr    | iown  |  |

| bit 15-8                  | Unimplemer<br>SJW<1:0>: S<br>11 = Length                                                                                           | ted: Read as '<br>Synchronization<br>s 4 x TQ<br>s 3 x TQ                                                                | 0'                                                    |                   | ared             | x = Bit is unkr    | iown  |  |

| bit 15-8                  | Unimplemer<br>SJW<1:0>: S<br>11 = Length<br>10 = Length                                                                            | ted: Read as '<br>Synchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ                                                    | 0'                                                    |                   | ared             | x = Bit is unkr    | iown  |  |

| bit 15-8                  | Unimplemen<br>SJW<1:0>: S<br>11 = Length<br>10 = Length<br>01 = Length<br>00 = Length                                              | ted: Read as '<br>Synchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ                                                    | o'<br>I Jump Width I                                  |                   | ared             | x = Bit is unkr    | iown  |  |

| bit 15-8<br>bit 7-6       | Unimplemen<br>SJW<1:0>: S<br>11 = Length<br>10 = Length<br>01 = Length<br>00 = Length<br>BRP<5:0>: E                               | ted: Read as '<br>Synchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 2 x TQ<br>s 1 x TQ                            | 0'<br>I Jump Width I<br>caler bits                    |                   | ared             | x = Bit is unkr    | iown  |  |

| bit 15-8<br>bit 7-6       | Unimplemen<br>SJW<1:0>: S<br>11 = Length<br>10 = Length<br>01 = Length<br>00 = Length<br>BRP<5:0>: E                               | ted: Read as '<br>Synchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 1 x TQ<br>saud Rate Pres                      | 0'<br>I Jump Width I<br>caler bits                    |                   | ared             | x = Bit is unkr    | iown  |  |