Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                          |

| Number of I/O              | 33                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 17x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

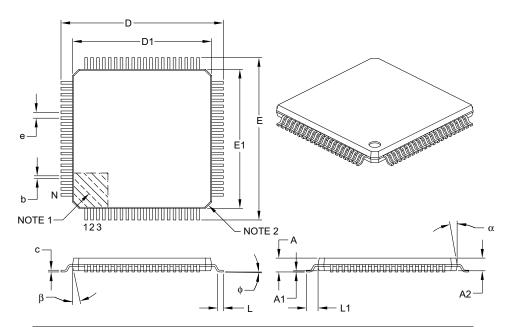

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs704-e-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

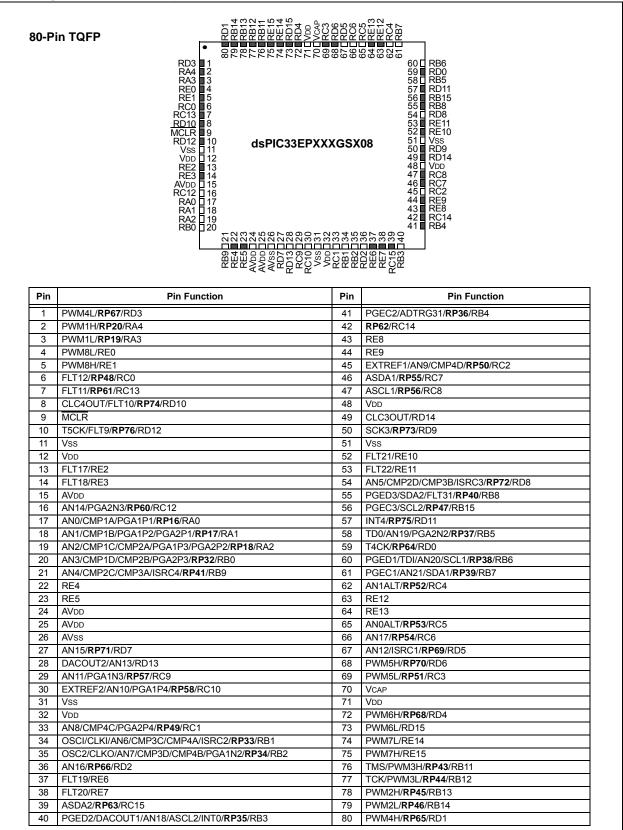

## **Pin Diagrams (Continued)**

Legend: Shaded pins are up to 5 VDC tolerant.

**RPn** represents remappable peripheral functions. See Table 11-12 and Table 11-13 for the complete list of remappable sources.

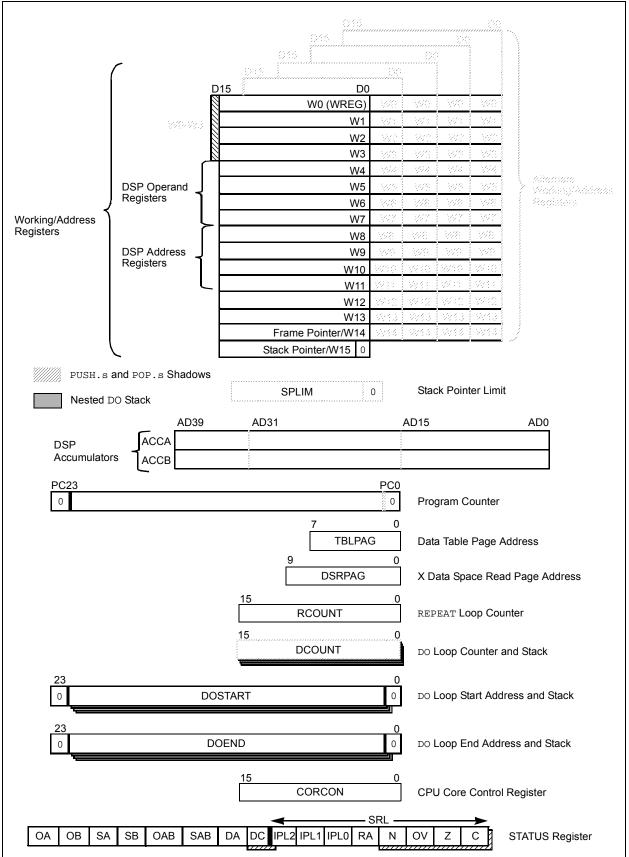

## 4.6.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions, and the DSP accumulator class of instructions, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

- **Note:** Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

## 4.6.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the MAC class of instructions:

- Register Indirect

- · Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

### 4.6.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

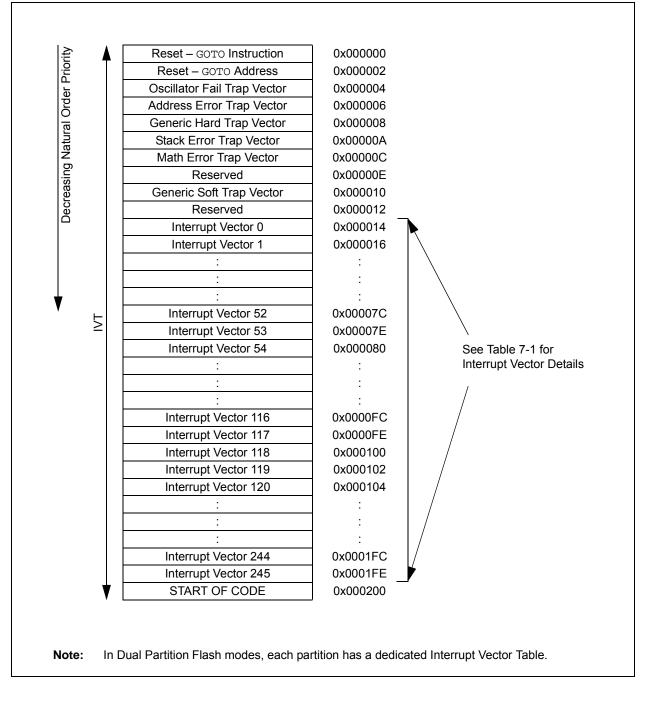

### FIGURE 7-1: dsPIC33EPXXXGS70X/80X FAMILY INTERRUPT VECTOR TABLE

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme, based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA Channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU Interrupt after Half or Full Block Transfer Complete

- Byte or Word Transfers

- · Fixed Priority Channel Arbitration

- Manual (software) or Automatic (peripheral DMA requests) Transfer Initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM Start addresses after each block transfer complete)

- DMA Request for each Channel can be Selected from any Supported Interrupt Source

- Debug Support Features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA<br>Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|----------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0      | 00000000                             | —                                                       | _                                                      |

| IC1 – Input Capture 1            | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2            | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3            | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4            | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1           | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2           | 00000110                             | —                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3           | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4           | 00011010                             | _                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                    | 00000111                             | —                                                       | —                                                      |

| TMR3 – Timer3                    | 00001000                             | —                                                       | —                                                      |

| TMR4 – Timer4                    | 00011011                             | —                                                       | —                                                      |

| TMR5 – Timer5                    | 00011100                             | —                                                       | —                                                      |

| UART1RX – UART1 Receiver         | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter      | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver         | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter      | 00011111                             | _                                                       | 0x0234 (U2TXREG)                                       |

| CAN1 – RX Data Ready             | 00100010                             | 0x0440 (C1RXD)                                          |                                                        |

| CAN1 – TX Data Request           | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| CAN2 – RX Data Ready             | 00110111                             | 0X0540(C2RXD)                                           | _                                                      |

| CAN2 – TX Data Request           | 01000111                             | _                                                       | 0X0542(C2TXD)                                          |

## TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

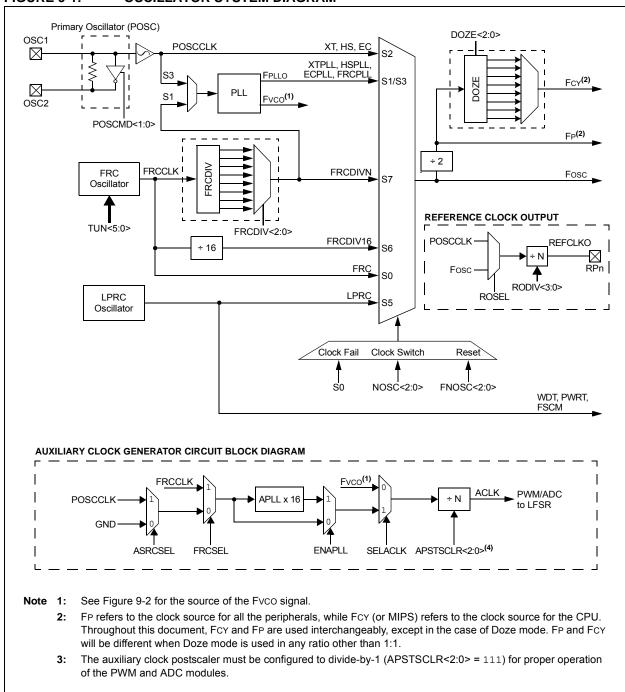

### FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

### REGISTER 11-37: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| bit 15 bit 15<br>U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0<br>— RP35R6 RP35R5 RP35R4 RP35R3 RP35R2 RP35R1 RP35R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |            |                            |        |                      |                                |                 |        |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------|----------------------------|--------|----------------------|--------------------------------|-----------------|--------|--|--|--|

| bit 15       Image: constraint of the second constraint | U-0             | R/W-0      | R/W-0                      | R/W-0  | R/W-0                | R/W-0                          | R/W-0           | R/W-0  |  |  |  |

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 | RP36R6     | RP36R5                     | RP36R4 | RP36R3               | RP36R2                         | RP36R1          | RP36R0 |  |  |  |

| —       RP35R6       RP35R5       RP35R4       RP35R3       RP35R2       RP35R1       RP35R0         bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 15          |            | ·                          |        |                      |                                |                 | bit 8  |  |  |  |

| —       RP35R6       RP35R5       RP35R4       RP35R3       RP35R2       RP35R1       RP35R0         bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |            |                            |        |                      |                                |                 |        |  |  |  |

| bit 7       bit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'       bit 14-8       RP36R<6:0>: Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U-0             | R/W-0      | R/W-0                      | R/W-0  | R/W-0                | R/W-0                          | R/W-0           | R/W-0  |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'         bit 14-8       RP36R<6:0>: Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 | RP35R6     | RP35R5                     | RP35R4 | RP35R3               | RP35R2                         | RP35R1          | RP35R0 |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'         bit 14-8       RP36R<6:0>: Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 7           | -          |                            |        |                      |                                |                 | bit 0  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'         bit 14-8       RP36R<6:0>: Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |            |                            |        |                      |                                |                 |        |  |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'       x = Bit is unknown         bit 14-8       RP36R<6:0>: Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Legend:         |            |                            |        |                      |                                |                 |        |  |  |  |

| bit 15       Unimplemented: Read as '0'         bit 14-8       RP36R<6:0>: Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R = Readable    | bit        | W = Writable               | bit    | U = Unimpler         | Unimplemented bit, read as '0' |                 |        |  |  |  |

| bit 14-8 <b>RP36R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -n = Value at I | POR        | '1' = Bit is set           |        | '0' = Bit is cleared |                                | x = Bit is unki | nown   |  |  |  |

| bit 14-8 <b>RP36R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |            |                            |        |                      |                                |                 |        |  |  |  |

| (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15          | Unimplemen | ted: Read as '             | 0'     |                      |                                |                 |        |  |  |  |

| bit 7 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 14-8        |            |                            |        |                      |                                |                 |        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 7           | Unimplemen | Unimplemented: Read as '0' |        |                      |                                |                 |        |  |  |  |

bit 6-0 **RP35R<6:0>:** Peripheral Output Function is Assigned to RP35 Output Pin bits (see Table 11-13 for peripheral function numbers)

### REGISTER 11-38: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0                                                                                              | R/W-0                      | R/W-0        | R/W-0  | R/W-0                                   | R/W-0            | R/W-0  | R/W-0  |  |  |  |

|--------------------------------------------------------------------------------------------------|----------------------------|--------------|--------|-----------------------------------------|------------------|--------|--------|--|--|--|

| —                                                                                                | RP38R6                     | RP38R5       | RP38R4 | RP38R3                                  | RP38R2           | RP38R1 | RP38R0 |  |  |  |

| bit 15                                                                                           |                            |              |        |                                         |                  |        | bit 8  |  |  |  |

|                                                                                                  |                            |              |        |                                         |                  |        |        |  |  |  |

| U-0                                                                                              | R/W-0                      | R/W-0        | R/W-0  | R/W-0                                   | R/W-0            | R/W-0  | R/W-0  |  |  |  |

| —                                                                                                | RP37R6                     | RP37R5       | RP37R4 | RP37R3                                  | RP37R2           | RP37R1 | RP37R0 |  |  |  |

| bit 7                                                                                            |                            |              |        |                                         |                  |        | bit 0  |  |  |  |

|                                                                                                  |                            |              |        |                                         |                  |        |        |  |  |  |

| Legend:                                                                                          |                            |              |        |                                         |                  |        |        |  |  |  |

| R = Readable                                                                                     | bit                        | W = Writable | bit    | U = Unimpler                            | nented bit, read | as '0' |        |  |  |  |

| -n = Value at POR '1' = Bit is set                                                               |                            |              |        | '0' = Bit is cleared x = Bit is unknown |                  |        | nown   |  |  |  |

|                                                                                                  |                            |              |        |                                         |                  |        |        |  |  |  |

| bit 15                                                                                           | Unimplemented: Read as '0' |              |        |                                         |                  |        |        |  |  |  |

| bit 14-8 <b>RP38R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP38 Output Pin bits |                            |              |        |                                         |                  |        |        |  |  |  |

- (see Table 11-13 for peripheral function numbers)

- bit 7 Unimplemented: Read as '0'

- bit 6-0 **RP37R<6:0>:** Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 11-13 for peripheral function numbers)

| U-0    | R/W-0   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| —      | RP181R6 | RP181R5 | RP181R4 | RP181R3 | RP181R2 | RP181R1 | RP181R0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

|        |         |         |         |         |         |         |         |

| 11-0   | R/W-0   | R/W-0   | R/\/_0  | R/W-0   | R/\\/_0 | R/W-0   | R/\\/_0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | RP180R6 | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 |

| U-0   | R/W-0   |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15 Unimplemented: Read as '0'

bit 14-8 **RP181R<6:0>:** Peripheral Output Function is Assigned to RP181 Output Pin bits (see Table 11-13 for peripheral function numbers)

bit 7 Unimplemented: Read as '0'

bit 6-0 **RP180R<6:0>:** Peripheral Output Function is Assigned to RP180 Output Pin bits (see Table 11-13 for peripheral function numbers)

## 16.0 HIGH-SPEED PWM

Note: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM Module" (DS70000323) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The high-speed PWM on dsPIC33EPXXXGS70X/80X devices supports a wide variety of PWM modes and output formats. This PWM module is ideal for power conversion applications, such as:

- AC/DC Converters

- DC/DC Converters

- Power Factor Correction

- Uninterruptible Power Supply (UPS)

- Inverters

- Battery Chargers

- · Digital Lighting

### 16.1 Features Overview

The high-speed PWM module incorporates the following features:

- Eight PWMx Generators with Two Outputs per Generator

- · Two Master Time Base modules

- Individual Time Base and Duty Cycle for each

PWM Output

- Duty Cycle, Dead Time, Phase Shift and a Frequency Resolution of 1.04 ns

- Independent Fault and Current-Limit Inputs

- · Redundant Output

- True Independent Output

- Center-Aligned PWM mode

- · Output override control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Dual Trigger from PWMx to Analog-to-Digital Converter (ADC)

- PWMxL and PWMxH Output Pin Swapping

- Independent PWMx Frequency, Duty Cycle and Phase-Shift Changes

- Enhanced Leading-Edge Blanking (LEB) Functionality

- PWM Capture Functionality

**Note:** Duty cycle, dead time, phase shift and frequency resolution is 8.32 ns in Center-Aligned PWM mode.

Figure 16-1 conceptualizes the PWM module in a simplified block diagram. Figure 16-2 illustrates how the module hardware is partitioned for each PWMx output pair for the Complementary PWM mode.

The PWM module contains eight PWM generators. The module has up to 16 PWMx output pins: PWM1H/ PWM1L through PWM8H/PWM8L. For complementary outputs, these 16 I/O pins are grouped into high/low pairs. PWM1 through PWM6 can be used to trigger an ADC conversion.

### 16.2 Feature Description

The PWM module is designed for applications that require:

- High resolution at high PWM frequencies

- The ability to drive Standard, Edge-Aligned, Center-Aligned Complementary mode and Push-Pull mode outputs

- The ability to create multiphase PWM outputs

Two common, medium power converter topologies are push-pull and half-bridge. These designs require the PWM output signal to be switched between alternate pins, as provided by the Push-Pull PWM mode.

Phase-shifted PWM describes the situation where each PWM generator provides outputs, but the phase relationship between the generator outputs is specifiable and changeable.

Multiphase PWM is often used to improve DC/DC Converter load transient response, and reduce the size of output filter capacitors and inductors. Multiple DC/DC Converters are often operated in parallel, but phase shifted in time. A single PWM output, operating at 250 kHz, has a period of 4  $\mu$ s but an array of four PWM channels, staggered by 1  $\mu$ s each, yields an effective switching frequency of 1 MHz. Multiphase PWM applications typically use a fixed-phase relationship.

Variable phase PWM is useful in Zero Voltage Transition (ZVT) power converters. Here, the PWM duty cycle is always 50% and the power flow is controlled by varying the relative phase shift between the two PWM generators.

## REGISTER 17-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER<sup>(1,2)</sup> (CONTINUED)

| bit 4   | OC1CS: Clock Source for OC1 bit                                                                                                                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Generates clock pulse when the broadcast command is executed</li> <li>0 = Does not generate clock pulse when the broadcast command is executed</li> </ul>                         |

| bit 3   | OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| bit 2   | OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| bit 1   | OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| bit 0   | OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| Note 1: | This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and                                                                                                       |

2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

PTGSTRT = 1).

## REGISTER 19-1: I2CxCONL: I2Cx CONTROL REGISTER LOW (CONTINUED)

| bit 6 | <ul> <li>STREN: SCLx Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave)</li> <li>Used in conjunction with the SCLREL bit.</li> <li>1 = Enables software or receives clock stretching</li> <li>0 = Disables software or receives clock stretching</li> </ul> |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                                                  |

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                                                    |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                                |

|       | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit; hardware is clear at the end of the master Acknowledge sequence</li> <li>0 = Acknowledge sequence is not in progress</li> </ul>                                            |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                |

|       | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C; hardware is clear at the end of the eighth bit of the master receive data byte</li> <li>0 = Receive sequence is not in progress</li> </ul>                                                                           |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as $l^2C$ master)                                                                                                                                                                                                    |

|       | <ul> <li>1 = Initiates Stop condition on SDAx and SCLx pins; hardware is clear at the end of the master Stop sequence</li> </ul>                                                                                                                                           |

|       | 0 = Stop condition is not in progress                                                                                                                                                                                                                                      |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                               |

|       | <ul> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins; hardware is clear at the end of the<br/>master Repeated Start sequence</li> </ul>                                                                                                                   |

|       | 0 = Repeated Start condition is not in progress                                                                                                                                                                                                                            |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                |

|       | 1 = Initiates Start condition on SDAx and SCLx pins; hardware is clear at the end of the master Start sequence                                                                                                                                                             |

0 = Start condition is not in progress

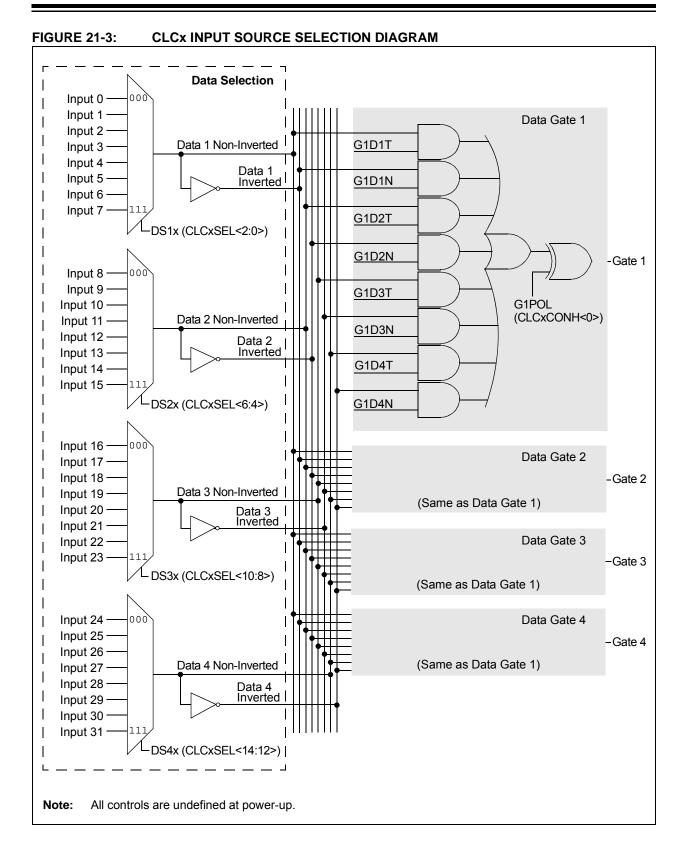

## REGISTER 21-1: CLCxCONL: CLCx CONTROL REGISTER (LOW) (CONTINUED)

- bit 2-0 MODE<2:0>: CLCx Mode bits

- 111 = Single Input Transparent Latch with S and R

- 110 = JK Flip-Flop with R

- 101 = Two-Input D Flip-Flop with R

- 100 = Single Input D Flip-Flop with S and R

- 011 = SR Latch

- 010 = Four-Input AND

- 001 = Four-Input OR-XOR

- 000 = Four-Input AND-OR

### REGISTER 21-2: CLCxCONH: CLCx CONTROL REGISTER (HIGH)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | G4POL | G3POL | G2POL | G1POL |

| bit 7 |     |     |     |       |       |       | bit 0 |

#### l egend.

| Legena.           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                                 |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| bit 3    | G4POL: Gate 4 Polarity Control bit                                                                                                         |  |  |  |  |

|          | <ul><li>1 = Channel 4 logic output is inverted when applied to the logic cell</li><li>0 = Channel 4 logic output is not inverted</li></ul> |  |  |  |  |

| bit 2    | G3POL: Gate 3 Polarity Control bit                                                                                                         |  |  |  |  |

|          | <ul><li>1 = Channel 3 logic output is inverted when applied to the logic cell</li><li>0 = Channel 3 logic output is not inverted</li></ul> |  |  |  |  |

| bit 1    | G2POL: Gate 2 Polarity Control bit                                                                                                         |  |  |  |  |

|          | <ul><li>1 = Channel 2 logic output is inverted when applied to the logic cell</li><li>0 = Channel 2 logic output is not inverted</li></ul> |  |  |  |  |

| bit 0    | G1POL: Gate 1 Polarity Control bit                                                                                                         |  |  |  |  |

|          | <ul><li>1 = Channel 1 logic output is inverted when applied to the logic cell</li><li>0 = Channel 1 logic output is not inverted</li></ul> |  |  |  |  |

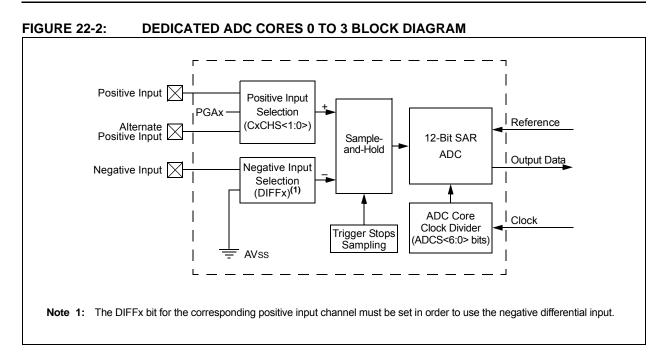

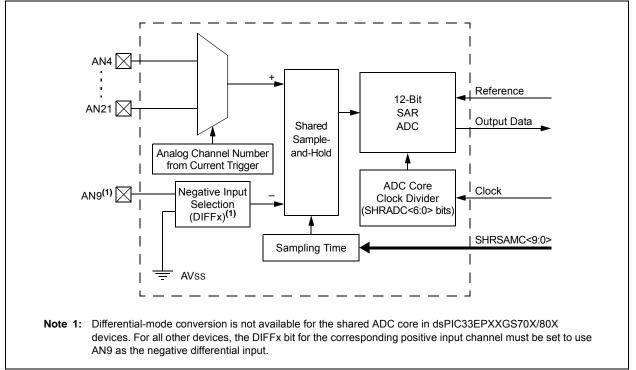

## FIGURE 22-3: SHARED ADC CORE BLOCK DIAGRAM

**REGISTER 22-29: ADCAL0H: ADC CALIBRATION REGISTER 0 HIGH**

#### R-0. HSC U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 CAL3RDY \_\_\_\_ \_\_\_\_ \_\_\_\_ CAL3SKIP **CAL3DIFF** CAL3EN **CAL3RUN** bit 15 bit 8 R-0, HSC U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 CAL2RDY CAL2SKIP CAL2DIFF CAL2EN CAL2RUN \_\_\_\_ \_\_\_\_ bit 7 bit 0 Legend: U = Unimplemented bit, read as '0' R = Readable bit W = Writable bit HSC = Hardware Settable/Clearable bit -n = Value at POR x = Bit is unknown '1' = Bit is set '0' = Bit is cleared bit 15 CAL3RDY: Dedicated ADC Core 3 Calibration Status Flag bit 1 = Dedicated ADC Core 3 calibration is finished 0 = Dedicated ADC Core 3 calibration is in progress bit 14-12 Unimplemented: Read as '0' bit 11 CAL3SKIP: Dedicated ADC Core 3 Calibration Bypass bit 1 = After power-up, the dedicated ADC Core 3 will not be calibrated 0 = After power-up, the dedicated ADC Core 3 will be calibrated bit 10 CAL3DIFF: Dedicated ADC Core 3 Differential-Mode Calibration bit 1 = Dedicated ADC Core 3 will be calibrated in Differential Input mode 0 = Dedicated ADC Core 3 will be calibrated in Single-Ended Input mode bit 9 CAL3EN: Dedicated ADC Core 3 Calibration Enable bit 1 = Dedicated ADC Core 3 calibration bits (CALxRDY, CALxSKIP, CALxDIFF and CALxRUN) can be accessed by software 0 = Dedicated ADC Core 3 calibration bits are disabled CAL3RUN: Dedicated ADC Core 3 Calibration Start bit bit 8 1 = If this bit is set by software, the dedicated ADC Core 3 calibration cycle is started; this bit is automatically cleared by hardware 0 = Software can start the next calibration cycle bit 7 CAL2RDY: Dedicated ADC Core 2 Calibration Status Flag bit 1 = Dedicated ADC Core 2 calibration is finished 0 = Dedicated ADC Core 2 calibration is in progress bit 6-4 Unimplemented: Read as '0' bit 3 CAL2SKIP: Dedicated ADC Core 2 Calibration Bypass bit 1 = After power-up, the dedicated ADC Core 2 will not be calibrated 0 = After power-up, the dedicated ADC Core 2 will be calibrated bit 2 CAL2DIFF: Dedicated ADC Core 2 Differential-Mode Calibration bit 1 = Dedicated ADC Core 2 will be calibrated in Differential Input mode 0 = Dedicated ADC Core 2 will be calibrated in Single-Ended Input mode bit 1 CAL2EN: Dedicated ADC Core 2 Calibration Enable bit 1 = Dedicated ADC Core 2 calibration bits (CALxRDY, CALxSKIP, CALxDIFF and CALxRUN) can be accessed by software 0 = Dedicated ADC Core 2 calibration bits are disabled CAL2RUN: Dedicated ADC Core 2 Calibration Start bit bit 0 1 = If this bit is set by software, the dedicated ADC Core 2 calibration cycle is started; this bit is automatically cleared by hardware 0 = Software can start the next calibration cycle

### REGISTER 23-11: CxFEN1: CANx ACCEPTANCE FILTER ENABLE REGISTER 1

| R/W-1                             | R/W-1 | R/W-1            | R/W-1        | R/W-1            | R/W-1    | R/W-1           | R/W-1 |

|-----------------------------------|-------|------------------|--------------|------------------|----------|-----------------|-------|

|                                   |       |                  | FLTEI        | N<15:8>          |          |                 |       |

| bit 15                            |       |                  |              |                  |          |                 | bit 8 |

| R/W-1                             | R/W-1 | R/W-1            | R/W-1        | R/W-1            | R/W-1    | R/W-1           | R/W-1 |

| _                                 |       |                  | FLTE         | N<7:0>           |          |                 |       |

| bit 7                             |       |                  |              |                  |          |                 | bit 0 |

| Legend:                           |       |                  |              |                  |          |                 |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimpler | nented bit, rea  | d as '0' |                 |       |

| -n = Value at P                   | POR   | '1' = Bit is set |              | '0' = Bit is cle | ared     | x = Bit is unki | nown  |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n

0 = Disables Filter n

### REGISTER 23-12: CxBUFPNT1: CANx FILTERS 0-3 BUFFER POINTER REGISTER 1

| R/W-0                                  | R/W-0                                                         | R/W-0                                                                                                                              | R/W-0                                                                                                     | R/W-0                                | R/W-0            | R/W-0                       | R/W-0 |

|----------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------|------------------|-----------------------------|-------|

| F3BP3                                  | F3BP2                                                         | F3BP1                                                                                                                              | F3BP0                                                                                                     | F2BP3                                | F2BP2            | F2BP1                       | F2BP0 |

| bit 15                                 |                                                               | ·                                                                                                                                  |                                                                                                           |                                      |                  |                             | bit 8 |

| R/W-0                                  | R/W-0                                                         | R/W-0                                                                                                                              | R/W-0                                                                                                     | R/W-0                                | R/W-0            | R/W-0                       | R/W-0 |

| F1BP3                                  | F1BP2                                                         | F1BP1                                                                                                                              | F1BP0                                                                                                     | F0BP3                                | F0BP2            | F0BP1                       | F0BP0 |

| bit 7                                  |                                                               |                                                                                                                                    |                                                                                                           |                                      |                  |                             | bit 0 |

|                                        |                                                               |                                                                                                                                    |                                                                                                           |                                      |                  |                             |       |

| Legend:                                |                                                               |                                                                                                                                    |                                                                                                           |                                      |                  |                             |       |

|                                        |                                                               |                                                                                                                                    |                                                                                                           |                                      |                  |                             |       |

| R = Readabl                            | e bit                                                         | W = Writable                                                                                                                       | bit                                                                                                       | U = Unimpler                         | mented bit, read | d as '0'                    |       |

| R = Readabl<br>-n = Value at           |                                                               | W = Writable<br>'1' = Bit is set                                                                                                   |                                                                                                           | U = Unimpler<br>'0' = Bit is cle     | ,                | d as '0'<br>x = Bit is unkr | nown  |

|                                        |                                                               |                                                                                                                                    |                                                                                                           | •                                    | ,                |                             | nown  |

|                                        | POR                                                           |                                                                                                                                    | 1                                                                                                         | ʻ0' = Bit is cle                     | ,                |                             | nown  |

| -n = Value at                          | F3BP<3:0>:                                                    | '1' = Bit is set                                                                                                                   | k for Filter 3 b                                                                                          | ʻ0' = Bit is cle<br>its              | ,                |                             | iown  |

| -n = Value at                          | <b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter                      | '1' = Bit is set<br>RX Buffer Mas                                                                                                  | k for Filter 3 b<br>n RX FIFO bu                                                                          | '0' = Bit is cle<br>its<br>ffer      | ,                |                             | nown  |

| -n = Value at                          | <b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter                      | '1' = Bit is set<br>RX Buffer Mas<br>hits received in                                                                              | k for Filter 3 b<br>n RX FIFO bu                                                                          | '0' = Bit is cle<br>its<br>ffer      | ,                |                             | nown  |

| -n = Value at                          | <b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter                      | '1' = Bit is set<br>RX Buffer Mas<br>hits received in                                                                              | k for Filter 3 b<br>n RX FIFO bu                                                                          | '0' = Bit is cle<br>its<br>ffer      | ,                |                             | nown  |

| -n = Value at                          | <b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter                      | '1' = Bit is set<br>RX Buffer Mas<br>hits received in                                                                              | k for Filter 3 b<br>n RX FIFO bu                                                                          | '0' = Bit is cle<br>its<br>ffer      | ,                |                             | nown  |

| -n = Value at                          | F3BP<3:0>:<br>1111 = Filter<br>1110 = Filter<br>0001 = Filter | '1' = Bit is set<br>RX Buffer Mas<br>hits received in<br>hits received in                                                          | k for Filter 3 b<br>n RX FIFO bu<br>n RX Buffer 14<br>n RX Buffer 1                                       | '0' = Bit is cle<br>its<br>ffer      | ,                |                             | nown  |