Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

|                            |                                                                                  |

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, I2S, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EPROM Size                 | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| /oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 17x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs704-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.6 Instruction Addressing Modes

The addressing modes shown in Table 4-17 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

#### 4.6.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.6.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- · Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- · 5-Bit or 10-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

TABLE 4-17: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

#### 5.0 **FLASH PROGRAM MEMORY**

**Note 1:** This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Dual Partition Flash Program Memory" (DS70005156) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

> 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGS70X/80X family devices contain internal Program Flash Memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- · Enhanced In-Circuit Serial Programming (Enhanced ICSP)

- · Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33EPXXXGS70X/80X family device to be serially programmed while in the end application circuit. This is done with a programming clock and programming data (PGECx/PGEDx) line, and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

Enhanced In-Circuit Serial Programming uses an on-board bootloader, known as the Program Executive, to manage the programming process. Using an SPI data frame format, the Program Executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data with a single program memory word and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

#### 5.1 **Table Instructions and Flash Programming**

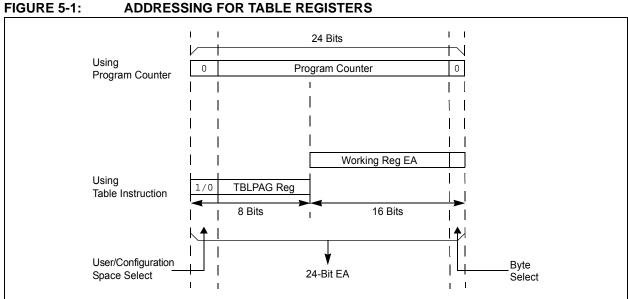

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These instructions allow direct read and write access to the program memory space, from the data memory, while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1. The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes. The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

### REGISTER 9-7: LFSR: LINEAR FEEDBACK SHIFT REGISTER

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      |       |       |       | LFSR<14:8> | >     |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | LFSF  | R<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-0 LFSR<14:0>: Pseudorandom Data bits

## 10.0 POWER-SAVING FEATURES

# Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGS70X/80X family devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

dsPIC33EPXXXGS70X/80X family devices car manage power consumption in four ways:

- · Clock Frequency

- Instruction-Based Sleep and Idle modes

- · Software-Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

# 10.1 Clock Frequency and Clock Switching

The dsPIC33EPXXXGS70X/80X family devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0** "Oscillator Configuration".

# 10.2 Instruction-Based Power-Saving Modes

The dsPIC33EPXXXGS70X/80X family devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into Sleep mode

PWRSAV #IDLE\_MODE ; Put the device into Idle mode

#### 12.0 TIMER1

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

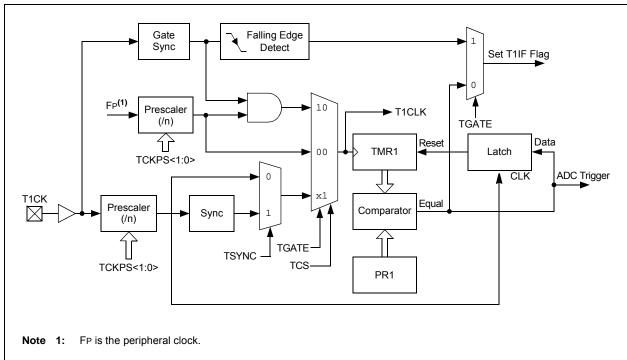

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be Operated in Asynchronous Counter mode from an External Clock Source

- The External Clock Input (T1CK) can Optionally be Synchronized to the Internal Device Clock and the Clock Synchronization is Performed after the prescaler

A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- · Timer mode

- · Gated Timer mode

- · Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer1 Clock Source Select bit (TCS): T1CON<1>

- Timer1 External Clock Input Synchronization Select bit (TSYNC): T1CON<2>

- Timer1 Gated Time Accumulation Enable bit (TGATE): T1CON<6>

Timer control bit settings for different operating modes are provided in Table 12-1.

TABLE 12-1: TIMER1 MODE SETTINGS

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | х     |

| Gated Timer             | 0   | 1     | х     |

| Synchronous<br>Counter  | 1   | х     | 1     |

| Asynchronous<br>Counter | 1   | х     | 0     |

FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

# REGISTER 16-22: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER (x = 1 to 8) (CONTINUED)

```

bit 7-3 FLTSRC<4:0>: Fault Control Signal Source Select for PWMx Generator bits

```

11111 = Reserved

10001 = Reserved

10000 = Analog Comparator 4

01111 = Analog Comparator 3

01110 = Analog Comparator 2

01101 = Analog Comparator 1

01100 = Fault 12

01011 = Fault 11

01010 = Fault 10

01001 = Fault 9

01000 = Fault 8

00111 = Fault 7

00110 = Fault 6

00101 = Fault 5

00100 = Fault 4

00011 = Fault 3

00010 = Fault 2

00001 = Fault 1

00000 = Reserved

bit 2 FLTPOL: Fault Polarity for PWMx Generator bit<sup>(1)</sup>

1 = The selected Fault source is active-low

0 = The selected Fault source is active-high

bit 1-0 FLTMOD<1:0>: Fault Mode for PWMx Generator bits

11 = Fault input is disabled

10 = Reserved

01 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (cycle)

00 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (latched condition)

Note 1: These bits should be changed only when PTEN = 0 (PTCON<15>).

## REGISTER 16-23: STRIGX: PWMx SECONDARY TRIGGER COMPARE VALUE REGISTER (x = 1 to 8)<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|-----------|-------|-------|-------|

|        |       |       | STRGCN | /IP<12:5> |       |       |       |

| bit 15 |       |       |        |           |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|-------|-------|------------|-------|-------|-----|-----|-------|

|       | S     | TRGCMP<4:0 | _     | _     | _   |     |       |

| bit 7 |       |            |       |       |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

bit 15-3 STRGCMP<12:0>: Secondary Trigger Compare Value bits

When the secondary PWMx functions in the local time base, this register contains the compare values that can trigger the ADC module.

bit 2-0 **Unimplemented:** Read as '0'

Note 1: STRIGx cannot generate the PWM trigger interrupts.

## TABLE 17-2: PTG OUTPUT DESCRIPTIONS

| PTG Output<br>Number | PTG Output Description                    |

|----------------------|-------------------------------------------|

| PTGO0                | Trigger/synchronization source for OC1    |

| PTGO1                | Trigger/synchronization source for OC2    |

| PTGO2                | Trigger/synchronization source for OC3    |

| PTGO3                | Trigger/synchronization source for OC4    |

| PTGO4                | Clock source for OC1                      |

| PTGO5                | Clock source for OC2                      |

| PTGO6                | Clock source for OC3                      |

| PTGO7                | Clock source for OC4                      |

| PTGO8                | Trigger/synchronization source for IC1    |

| PTGO9                | Trigger/synchronization source for IC2    |

| PTGO10               | Trigger/synchronization source for IC3    |

| PTGO11               | Trigger/synchronization source for IC4    |

| PTGO12               | Sample trigger for ADC                    |

| PTGO13               | Reserved                                  |

| PTGO14               | Reserved                                  |

| PTGO15               | Reserved                                  |

| PTGO16               | PWM time base synchronous source for PWM3 |

| PTGO17               | PWM time base synchronous source for PWM4 |

| PTGO18               | PWM time base synchronous source for PWM5 |

| PTGO19               | PWM time base synchronous source for PWM6 |

| PTGO20               | Reserved                                  |

| PTGO21               | Reserved                                  |

| PTGO22               | Reserved                                  |

| PTGO23               | Reserved                                  |

| PTGO24               | Reserved                                  |

| PTGO25               | Reserved                                  |

| PTGO26               | CLC1 input                                |

| PTGO27               | CLC2 input                                |

| PTGO28               | CLC3 input                                |

| PTGO29               | CLC4 input                                |

| PTGO30               | PTG output to PPS input selection, RPI6   |

| PTGO31               | PTG output to PPS input selection, RPI7   |

### REGISTER 23-24: Cxrxovf1: CANx RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0  | R/C-0 | R/C-0 | R/C-0 | R/C-0               | R/C-0 | R/C-0 | R/C-0 |

|--------|-------|-------|-------|---------------------|-------|-------|-------|

|        |       |       | RXOVE | <sup>-</sup> <15:8> |       |       |       |

| bit 15 |       |       |       |                     |       |       | bit 8 |

| R/C-0 | R/C-0 | R/C-0 | R/C-0 | R/C-0  | R/C-0 | R/C-0 | R/C-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | RXOV  | F<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

**Legend:** C = Writable bit, but only '0' can be Written to Clear bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 RXOVF<15:0>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 23-25: CxRXOVF2: CANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0  | R/C-0        | R/C-0 | R/C-0 | R/C-0 | R/C-0 | R/C-0 | R/C-0 |  |  |  |  |

|--------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|        | RXOVF<31:24> |       |       |       |       |       |       |  |  |  |  |

| bit 15 |              |       |       |       |       |       | bit 8 |  |  |  |  |

| R/C-0 | R/C-0 | R/C-0 | R/C-0 | R/C-0   | R/C-0 | R/C-0 | R/C-0 |

|-------|-------|-------|-------|---------|-------|-------|-------|

|       |       |       | RXOVF | <23:16> |       |       |       |

| bit 7 |       |       |       |         |       |       | bit 0 |

**Legend:** C = Writable bit, but only '0' can be Written to Clear bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 **RXOVF<31:16>:** Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### BUFFER 21-5: CANX MESSAGE BUFFER WORD 4

| R/W-x        | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Byte 3<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15       |       |       |       |       |       |       |       |  |  |

| R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Byte 2<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7       |       |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Byte 3<15:8>:** CANx Message Byte 3 bits bit 7-0 **Byte 2<7:0>:** CANx Message Byte 2 bits

#### BUFFER 21-6: CANX MESSAGE BUFFER WORD 5

| R/W-x    | R/W-x        | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |  |

|----------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|

|          | Byte 5<15:8> |       |       |       |       |       |       |  |  |  |

| bit 15 b |              |       |       |       |       |       |       |  |  |  |

| R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Byte 4<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7       |       |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Byte 5<15:8>:** CANx Message Byte 5 bits bit 7-0 **Byte 4<7:0>:** CANx Message Byte 4 bits

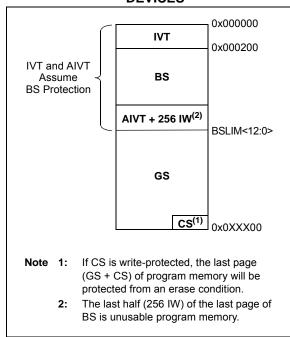

The different device security segments are shown in Figure 27-3. Here, all three segments are shown but are not required. If only basic code protection is required, then GS can be enabled independently or combined with CS. if desired.

FIGURE 27-3: SECURITY SEGMENTS

EXAMPLE FOR

dsPIC33EPXXXGS70X/80X

DEVICES

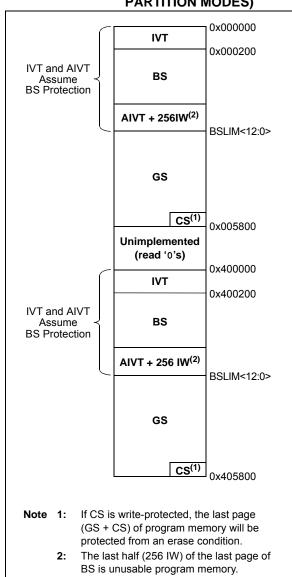

dsPIC33EPXXXGS70X/80X family devices can be operated in Dual Partition mode, where security is required for each partition. When operating in Dual Partition mode, the Active and Inactive Partitions both contain unique copies of the Reset vector, Interrupt Vector Tables (IVT and AIVT, if enabled) and the Flash Configuration Words. Both partitions have the three security segments described previously. Code may not be executed from the Inactive Partition, but it may be programmed by, and read from, the Active Partition, subject to defined code protection. Figure 27-4 and Figure 27-5 show the different security segments for devices operating in Dual Partition mode.

The device may also operate in a Protected Dual Partition mode or in Privileged Dual Partition mode. In Protected Dual Partition mode, Partition 1 is permanently erase/write-protected. This implementation allows for a "Factory Default" mode, which provides a fail-safe backup image to be stored in Partition 1. For example, a fail-safe bootloader can be placed in Partition 1, along with a fail-safe backup code image, which can be used or rewritten into Partition 2 in the event of a failed Flash update to Partition 2.

Privileged Dual Partition mode performs the same function as Protected Dual Partition mode, except additional constraints are applied in an effort to prevent code in the Boot Segment and General Segment from being used against each other.

FIGURE 27-4: SECURITY SEGMENTS

EXAMPLE FOR

dsPIC33EP64GS70X/80X

DEVICES (DUAL

PARTITION MODES)

## 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>TM</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- · Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- · Third-party development tools

# 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

#### Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- · Multiple projects

- · Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

## 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

#### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

## 29.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM™ and dsPICDEM™ demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELoq® security ICs, CAN, IrDA®, PowerSmart battery management, SEEVAL® evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

## TABLE 30-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                                  | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) <sup>(1)</sup> Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |   |      |      |                      |  |  |

|--------------------|--------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|------|----------------------|--|--|

| Param<br>No.       | Symbol | abol Characteristic Min. Typ. Max. Units Condition               |                                                                                                                                                                                                                                                                 |   |      |      |                      |  |  |

| Operating Voltage  |        |                                                                  |                                                                                                                                                                                                                                                                 |   |      |      |                      |  |  |

| DC10               | VDD    | Supply Voltage                                                   | 3.0                                                                                                                                                                                                                                                             | _ | 3.6  | V    |                      |  |  |

| DC12               | VDR    | RAM Retention Voltage <sup>(2)</sup>                             | _                                                                                                                                                                                                                                                               | _ | 1.95 | V    | +25°C, +85°C, +125°C |  |  |

|                    |        |                                                                  | _                                                                                                                                                                                                                                                               |   | 2.0  | V    | -40°C                |  |  |

| DC16               | VPOR   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal | _                                                                                                                                                                                                                                                               | _ | Vss  | V    |                      |  |  |

| DC17               | SVDD   | VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal     | 1.0                                                                                                                                                                                                                                                             | _ | _    | V/ms | 0V-3V in 3 ms        |  |  |

- Note 1: Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, PGAs and comparators) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: This is the limit to which VDD may be lowered and the RAM contents will always be retained.

## TABLE 30-5: FILTER CAPACITOR (CEFC) SPECIFICATIONS

|              | Standard Operating Conditions (unless otherwise stated):  Operating temperature $-40^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{Ta} \leq +125^{\circ}\text{C}$ for Extended |  |  |  |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Param<br>No. | Symbol   Characteristics   Min   Tyn   Max   Units   Comments                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|              | CEFC External Filter Capacitor 4.7 — 10 μF Capacitor must have a low series resistance (<1 Ohm)                                                                                                                                          |  |  |  |  |  |  |  |  |

**Note 1:** Typical VCAP Voltage = 1.8 volts when VDD ≥ VDDMIN.

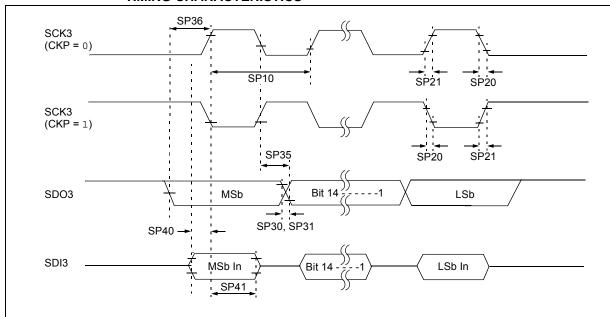

FIGURE 30-21: SPI3 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS<sup>(1,2)</sup>

Note 1: For dsPIC33EPXXXGSX06 and dsPIC33EPXXXGSX08 devices with a fixed SCK3 pin.

2: Refer to Figure 30-1 for load conditions.

TABLE 30-41: SPI3 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING REQUIREMENTS<sup>(5)</sup>

| AC CHARACTERISTICS |                       |                                               | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                     |      |       |                             |

|--------------------|-----------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                                                                                                                                                                                                             | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP10               | FscP                  | Maximum SCK3 Frequency                        | _                                                                                                                                                                                                                                                | _                   | 25   | MHz   | (Note 3)                    |

| SP20               | TscF                  | SCK3 Output Fall Time                         | _                                                                                                                                                                                                                                                | _                   |      | ns    | See Parameter DO32 (Note 4) |

| SP21               | TscR                  | SCK3 Output Rise Time                         | 1                                                                                                                                                                                                                                                | _                   | l    | ns    | See Parameter DO31 (Note 4) |

| SP30               | TdoF                  | SDO3 Data Output Fall Time                    | _                                                                                                                                                                                                                                                | _                   |      | ns    | See Parameter DO32 (Note 4) |

| SP31               | TdoR                  | SDO3 Data Output Rise Time                    | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO3 Data Output Valid after SCK3 Edge        |                                                                                                                                                                                                                                                  | 6                   | 20   | ns    |                             |

| SP36               | TdoV2sc,<br>TdoV2scL  | SDO3 Data Output Setup to First SCK3 Edge     | 20                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI3 Data<br>Input to SCK3 Edge | 20                                                                                                                                                                                                                                               | _                   |      | ns    |                             |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI3 Data Input to SCK3 Edge     | 15                                                                                                                                                                                                                                               | _                   |      | ns    |                             |

Note 1: These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK3 is 100 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI3 pins.

- 5: For dsPIC33EPXXXGSX06 and dsPIC33EPXXXGSX08 devices with a fixed SCK3 pin.

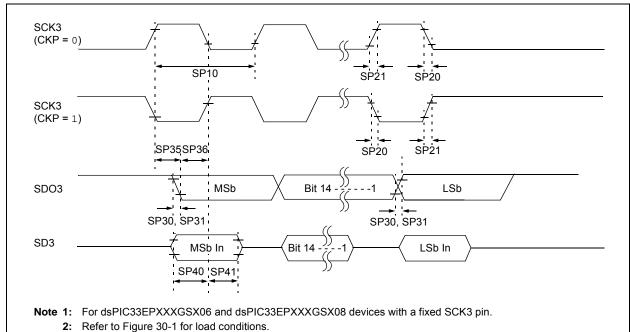

FIGURE 30-22: SPI3 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS<sup>(1,2)</sup>

TABLE 30-42: SPI3 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING REQUIREMENTS<sup>(5)</sup>

| AC CHARACTERISTICS |                       |                                               | Standard Operating Co<br>(unless otherwise state<br>Operating temperature |                     |      |       |                             |  |

|--------------------|-----------------------|-----------------------------------------------|---------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                                      | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP10               | FscP                  | Maximum SCK3 Frequency                        | _                                                                         | _                   | 25   | MHz   | -40°C to +125°C (Note 3)    |  |

| SP20               | TscF                  | SCK3 Output Fall Time                         | _                                                                         | _                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP21               | TscR                  | SCK3 Output Rise Time                         | _                                                                         | _                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO3 Data Output Fall Time                    | _                                                                         | _                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO3 Data Output Rise Time                    | _                                                                         | _                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO3 Data Output Valid after SCK3 Edge        | _                                                                         | 6                   | 20   | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO3 Data Output Setup to First SCK3 Edge     | 20                                                                        | _                   | _    | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI3 Data<br>Input to SCK3 Edge | 20                                                                        | _                   | _    | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI3 Data Input to SCK3Edge      | 20                                                                        | _                   |      | ns    |                             |  |

- Note 1: These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK3 is 100 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI3 pins.

- 5: For dsPIC33EPXXXGSX06 and dsPIC33EPXXXGSX08 devices with a fixed SCK3 pin.

## 32.0 PACKAGING INFORMATION

## 32.1 Package Marking Information

28-Lead SOIC (7.50 mm)

28-Lead UQFN (6x6x0.55 mm)

28-Lead QFN-S (6x6x0.9 mm)

44-Lead TQFP (10x10x1 mm)

Example

Example

Example

Example

Legend: XX...X Customer-specific information

Y ear code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

**Note:** In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

# 28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (2N) - 6x6x0.55 mm Body [UQFN] With 4.65x4.65 mm Exposed Pad and Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                             | MILLIMETERS |          |           |      |  |  |

|-----------------------------|-------------|----------|-----------|------|--|--|

| Dimension                   | Limits      | MIN      | NOM       | MAX  |  |  |

| Number of Terminals         | N           |          | 28        |      |  |  |

| Pitch                       | е           |          | 0.65 BSC  |      |  |  |

| Overall Height              | Α           | 0.45     | 0.50      | 0.55 |  |  |

| Standoff                    | A1          | 0.00     | 0.02      | 0.05 |  |  |

| Terminal Thickness          | A3          |          | 0.127 REF |      |  |  |

| Overall Width               | Е           | 6.00 BSC |           |      |  |  |

| Exposed Pad Width           | E2          | 4.55     | 4.65      | 4.75 |  |  |

| Overall Length              | D           |          | 6.00 BSC  |      |  |  |

| Exposed Pad Length          | D2          | 4.55     | 4.65      | 4.75 |  |  |

| Exposed Pad Corner Chamfer  | Р           | ı        | 0.35      | -    |  |  |

| Terminal Width              | b           | 0.25     | 0.30      | 0.35 |  |  |

| Corner Anchor Pad           | b1          | 0.35     | 0.40      | 0.43 |  |  |

| Corner Pad, Metal Free Zone | b2          | 0.15     | 0.20      | 0.25 |  |  |

| Terminal Length             | L           | 0.30     | 0.40      | 0.50 |  |  |

| Terminal-to-Exposed-Pad     | K           | 0.20     | -         | -    |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-385B Sheet 2 of 2

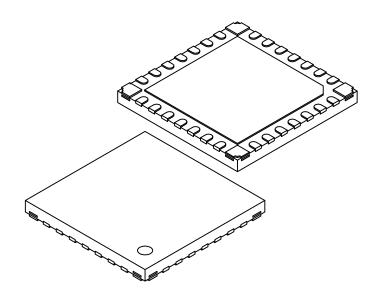

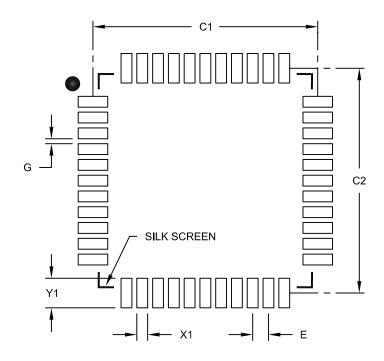

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | N   | <b>ILLIMETER</b> | S     |      |  |  |

|--------------------------|-----|------------------|-------|------|--|--|

| Dimension                | MIN | NOM              | MAX   |      |  |  |

| Contact Pitch            | Е   | 0.80 BSC         |       |      |  |  |

| Contact Pad Spacing      | C1  |                  | 11.40 |      |  |  |

| Contact Pad Spacing      | C2  |                  | 11.40 |      |  |  |

| Contact Pad Width (X44)  | X1  |                  |       | 0.55 |  |  |

| Contact Pad Length (X44) | Y1  |                  |       | 1.50 |  |  |

| Distance Between Pads    | G   | 0.25             |       |      |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

| NOTES: |  |  |  |  |

|--------|--|--|--|--|

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |