Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                          |

| Number of I/O              | 33                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 17x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

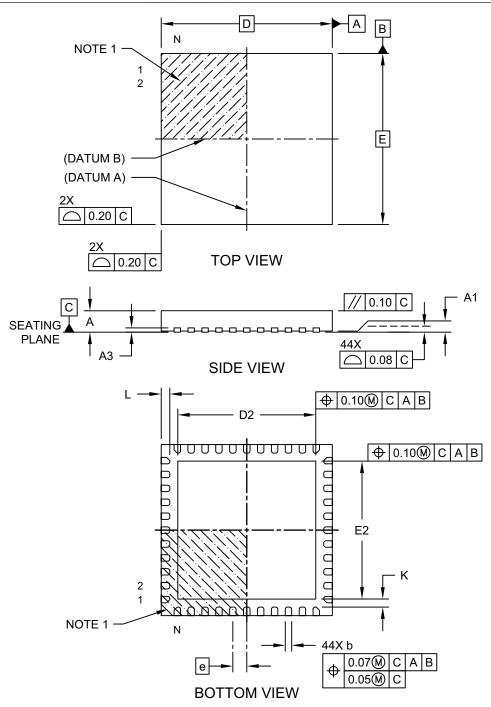

| Package / Case             | 48-TQFP                                                                          |

| Supplier Device Package    | 48-TQFP (7x7)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs705-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Register | Address | All Resets         | Register | Address | All Resets                              | Register | Address | All Resets                              |

|----------|---------|--------------------|----------|---------|-----------------------------------------|----------|---------|-----------------------------------------|

| PORTA    |         |                    | ANSELB   | E1E     | 0000001011101111                        | CNPDD    | E3C     | 000000000000000000000000000000000000000 |

| TRISA    | E00     | 000000000011111    | PORTC    |         |                                         | ANSELD   | E3E     | 0110000110100000                        |

| PORTA    | E02     | 000000000000000000 | TRISC    | E20     | 0111011111111111                        | PORTE    |         |                                         |

| LATA     | E04     | 000000000000000000 | PORTC    | E22     | 000000000000000000                      | TRISE    | E40     | 11111111111111111                       |

| ODCA     | E06     | 000000000000000000 | LATC     | E24     | 000000000000000000                      | PORTE    | E42     | 000000000000000000                      |

| CNENA    | E08     | 000000000000000000 | ODCC     | E26     | 000000000000000000                      | LATE     | E44     | 000000000000000000                      |

| CNPUA    | E0A     | 000000000000000000 | CNENC    | E28     | 000000000000000000                      | ODCE     | E46     | 000000000000000000                      |

| CNPDA    | E0C     | 000000000000000000 | CNPUC    | E2A     | 000000000000000000                      | CNENE    | E48     | 000000000000000000                      |

| ANSELA   | E0E     | 000000000000111    | CNPDC    | E2C     | 000000000000000000                      | CNPUE    | E4A     | 000000000000000000                      |

| PORTB    |         |                    | ANSELC   | E2E     | 0001011001110111                        | CNPDE    | E4C     | 000000000000000000000000000000000000000 |

| TRISB    | E10     | 0111101111111111   | PORTD    |         |                                         | ANSELE   | E4E     | 110000010000000                         |

| PORTB    | E12     | 000000000000000000 | TRISD    | E30     | 11111111111111111                       | CPU      |         |                                         |

| LATB     | E14     | 000000000000000000 | PORTD    | E32     | 000000000000000000                      | VISI     | F88     | 000000000000000000                      |

| ODCB     | E16     | 000000000000000000 | LATD     | E34     | 000000000000000000000000000000000000000 | JTAG     |         |                                         |

| CNENB    | E18     | 000000000000000000 | ODCD     | E36     | 000000000000000000                      | JDATAH   | FF0     | 00000000000000000                       |

| CNPUB    | E1A     | 000000000000000000 | CNEND    | E38     | 000000000000000000                      | JDATAL   | FF2     | 00000000000000000                       |

| CNPDB    | E1C     | 000000000000000000 | CNPUD    | E3A     | 000000000000000000                      |          |         |                                         |

### TABLE 4-15: SFR BLOCK E00h-F00h

Legend: x = unknown or indeterminate value. Address values are in hexadecimal. Reset values are in binary.

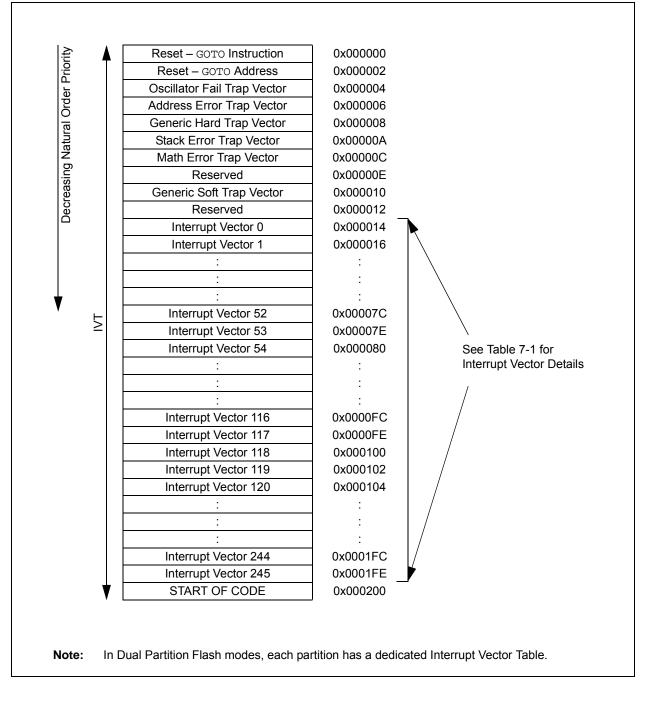

## 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/ 80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS7000600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGS70X/80X family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGS70X/80X family CPU.

The interrupt controller has the following features:

- Six Processor Exceptions and Software Traps

- Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with a Unique Vector for each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- Fixed Interrupt Entry and Return Latencies

- Alternate Interrupt Vector Table (AIVT) for Debug Support

## 7.1 Interrupt Vector Table

The dsPIC33EPXXXGS70X/80X family Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory, starting at location, 000004h. The IVT contains six non-maskable trap vectors and up to 246 sources of interrupts. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT), shown in Figure 7-2, is available only when the Boot Segment is defined and the AIVT has been enabled. To enable the Alternate Interrupt Vector Table, the Configuration bit, AIVTDIS in the FSEC register, must be programmed and the AIVTEN bit must be set (INTCON2<8> = 1). When the AIVT is enabled, all interrupt and exception processes use the alternate vectors instead of the default vectors. The AIVT begins at the start of the last page of the Boot Segment, defined by BSLIM<12:0>. The second half of the page is no longer usable space. The Boot Segment must be at least 2 pages to enable the AIVT.

Note: Although the Boot Segment must be enabled in order to enable the AIVT, application code does not need to be present inside of the Boot Segment. The AIVT (and IVT) will inherit the Boot Segment code protection.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGS70X/80X family devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

#### FIGURE 7-1: dsPIC33EPXXXGS70X/80X FAMILY INTERRUPT VECTOR TABLE

#### REGISTER 8-5: DMAxSTBH: DMA CHANNEL x START ADDRESS REGISTER B (HIGH)

| U-0    | U-0        | U-0   | U-0   | R/W-0 | U-0   | U-0   | U-0   |  |  |  |

|--------|------------|-------|-------|-------|-------|-------|-------|--|--|--|

|        | _          |       |       |       | —     |       | _     |  |  |  |

| bit 15 |            |       |       |       |       |       | bit 8 |  |  |  |

|        |            |       |       |       |       |       |       |  |  |  |

| R/W-0  | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|        | STB<23:16> |       |       |       |       |       |       |  |  |  |

| bit 7  |            |       |       |       |       |       | bit 0 |  |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: DMA Secondary Start Address bits (source or destination)

#### REGISTER 8-6: DMAxSTBL: DMA CHANNEL x START ADDRESS REGISTER B (LOW)

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0    | R/W-0 |

|----------------------------------------------------------------------------|-------|-------|-------|--------|-------|----------|-------|

|                                                                            |       |       | STB   | <15:8> |       |          |       |

| bit 15                                                                     |       |       |       |        |       |          | bit 8 |

|                                                                            |       |       |       |        |       |          |       |

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0    | R/W-0 |

|                                                                            |       |       | STE   | 3<7:0> |       |          |       |

| bit 7                                                                      |       |       |       |        |       |          | bit 0 |

|                                                                            |       |       |       |        |       |          |       |

| Legend:                                                                    |       |       |       |        |       |          |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |       |       |       |        |       | d as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |       |       |        | nown  |          |       |

bit 15-0 STB<15:0>: DMA Secondary Start Address bits (source or destination)

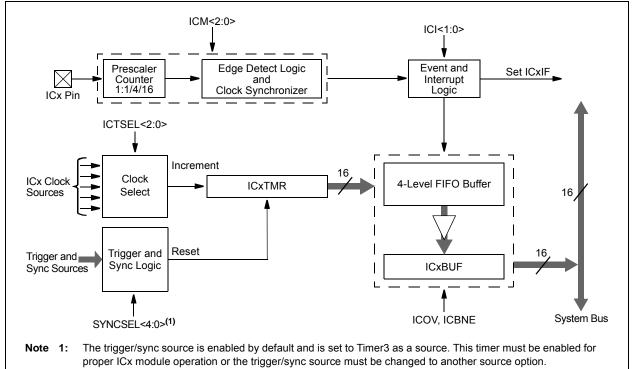

## 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/ 80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture with Dedicated Timer" (DS70000352) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurements. The dsPIC33EPXXXGS70X/80X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-Configurable for 32-Bit Operation in all modes by Cascading Two Adjacent modules

- Synchronous and Trigger modes of Output Compare Operation, with up to 21 User-Selectable Trigger/Sync Sources available

- A 4-Level FIFO Buffer for Capturing and Holding Timer Values for Several Events

- Configurable Interrupt Generation

- Up to Six Clock Sources available for each module, Driving a Separate Internal 16-Bit Counter

## 14.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 14.1.1 KEY RESOURCES

- "Input Capture with Dedicated Timer" (DS70000352) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### FIGURE 14-1: INPUT CAPTURE x MODULE BLOCK DIAGRAM

### REGISTER 17-12: PTGQPTR: PTG STEP QUEUE POINTER REGISTER<sup>(1)</sup>

| U-0             | U-0 | U-0              | U-0                                     | U-0                                | U-0         | U-0   | U-0   |

|-----------------|-----|------------------|-----------------------------------------|------------------------------------|-------------|-------|-------|

| —               | —   | —                | —                                       | —                                  | —           |       | —     |

| bit 15          |     |                  |                                         |                                    | •           |       | bit 8 |

|                 |     |                  |                                         |                                    |             |       |       |

| U-0             | U-0 | U-0              | R/W-0                                   | R/W-0                              | R/W-0       | R/W-0 | R/W-0 |

| —               | —   | —                |                                         |                                    | PTGQPTR<4:0 | >     |       |

| bit 7           |     |                  |                                         |                                    |             |       | bit 0 |

|                 |     |                  |                                         |                                    |             |       |       |

| Legend:         |     |                  |                                         |                                    |             |       |       |

| R = Readable I  | bit | W = Writable     | bit                                     | U = Unimplemented bit, read as '0' |             |       |       |

| -n = Value at P | OR  | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |                                    |             |       | nown  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 **PTGQPTR<4:0>:** PTG Step Queue Pointer Register bits This register points to the currently active Step command in the Step queue.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## **REGISTER 17-13: PTGQUEX: PTG STEP QUEUE REGISTER x (x = 0-15)**<sup>(1,3)</sup>

| R/W-0                        | R/W-0 | R/W-0 | R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------------------------|-------|-------|-----------|----------------------|-------|-------|-------|--|--|

|                              |       |       | STEP(2x + | - 1)<7:0> <b>(2)</b> |       |       |       |  |  |

| bit 15                       |       |       |           |                      |       |       | bit 8 |  |  |

|                              |       |       |           |                      |       |       |       |  |  |

| R/W-0                        | R/W-0 | R/W-0 | R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 |  |  |

| STEP(2x)<7:0> <sup>(2)</sup> |       |       |           |                      |       |       |       |  |  |

| bit 7                        |       |       |           |                      |       |       | bit ( |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8STEP(2x + 1)<7:0>: PTG Step Queue Pointer Register bits<sup>(2)</sup><br/>A queue location for storage of the STEP(2x +1) command byte.bit 7-0STEP(2x)<7:0>: PTG Step Queue Pointer Register bits<sup>(2)</sup>

A queue location for storage of the STEP(2x) command byte.

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: Refer to Table 17-1 for the Step command encoding.

- 3: The Step registers maintain their values on any type of Reset.

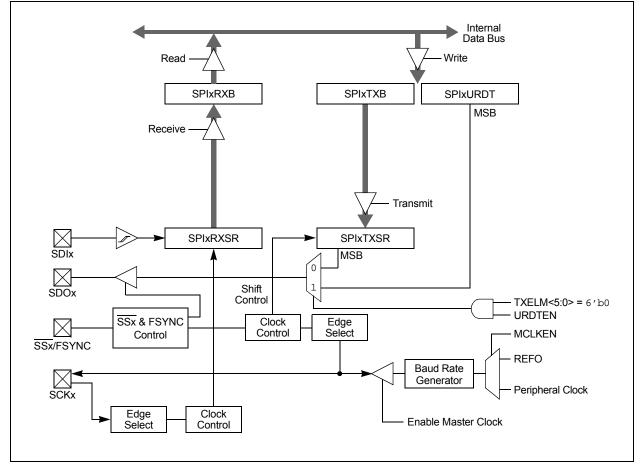

To set up the SPIx module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L and SPIxCON1H registers with the MSTEN bit (SPIxCON1L<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTATL<6>).

- 4. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- 5. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

To set up the SPIx module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF registers.

- 2. If using interrupts:

- a) Clear the SPIxBUFL and SPIxBUFH registers.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with the MSTEN bit (SPIxCON1L<5>) = 0.

- 4. Clear the SMP bit.

- If the CKE bit (SPIxCON1L<8>) is set, then the SSEN bit (SPIxCON1L<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTATL<6>).

- Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

## FIGURE 18-1: SPIX MODULE BLOCK DIAGRAM (STANDARD MODE)

## 20.3 UART Control Registers

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER

| R/W-0                 | U-0                                                                   | R/W-0                                                   | R/W-0                          | R/W-0                          | U-0                                    | R/W-0                                                  | R/W-0         |  |  |

|-----------------------|-----------------------------------------------------------------------|---------------------------------------------------------|--------------------------------|--------------------------------|----------------------------------------|--------------------------------------------------------|---------------|--|--|

| UARTEN <sup>(1)</sup> | _                                                                     | USIDL                                                   | IREN <sup>(2)</sup>            | RTSMD                          | _                                      | UEN1                                                   | UEN0          |  |  |

| bit 15                |                                                                       |                                                         |                                | •                              |                                        |                                                        | bit 8         |  |  |

|                       |                                                                       |                                                         |                                |                                |                                        |                                                        |               |  |  |

| R/W-0, HC             | R/W-0                                                                 | R/W-0, HC                                               | R/W-0                          | R/W-0                          | R/W-0                                  | R/W-0                                                  | R/W-0         |  |  |

| WAKE                  | LPBACK                                                                | ABAUD                                                   | URXINV                         | BRGH                           | PDSEL1                                 | PDSEL0                                                 | STSEL         |  |  |

| bit 7                 |                                                                       |                                                         |                                |                                |                                        |                                                        | bit (         |  |  |

| Legend:               |                                                                       | HC = Hardwar                                            | e Clearable b                  | it                             |                                        |                                                        |               |  |  |

| R = Readable          | e bit                                                                 | W = Writable b                                          |                                |                                | ented bit, read                        | l as '0'                                               |               |  |  |

| -n = Value at         |                                                                       | '1' = Bit is set                                        |                                | '0' = Bit is clea              |                                        | x = Bit is unkn                                        | own           |  |  |

| bit 15                | 1 = UARTx i<br>0 = UARTx i<br>minimal                                 | s disabled; all U                                       | ARTx pins are<br>ARTx pins are |                                |                                        | ed by UEN<1:0<br>UARTx power co                        |               |  |  |

| bit 14                | Unimplemented: Read as '0'                                            |                                                         |                                |                                |                                        |                                                        |               |  |  |

| bit 13                | USIDL: UARTx Stop in Idle Mode bit                                    |                                                         |                                |                                |                                        |                                                        |               |  |  |

|                       |                                                                       | nues module op<br>es module opera                       |                                |                                | le mode                                |                                                        |               |  |  |

| bit 12                | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup> |                                                         |                                |                                |                                        |                                                        |               |  |  |

|                       |                                                                       | oder and decod                                          |                                |                                |                                        |                                                        |               |  |  |

| bit 11                | RTSMD: Mod                                                            | SMD: Mode Selection for UxRTS Pin bit                   |                                |                                |                                        |                                                        |               |  |  |

|                       |                                                                       | oin is in Simplex<br>oin is in Flow Co                  |                                |                                |                                        |                                                        |               |  |  |

| bit 10                | Unimplemen                                                            | ted: Read as '0                                         | ,                              |                                |                                        |                                                        |               |  |  |

| bit 9-8               | UEN<1:0>: U                                                           | JARTx Pin Enab                                          | le bits                        |                                |                                        |                                                        |               |  |  |

|                       | 10 = UxTX, U<br>01 = UxTX, U                                          | JxRX, UxCTS a<br>JxRX and UxRT<br>nd UxRX pins a        | nd UxRTS pin<br>S pins are en  | s are enabled a abled and used | n <u>d used</u><br><u>UxCTS pin is</u> | controlled by PC<br>controlled by PC<br>BCLKx pins are | ORT latches   |  |  |

| bit 7                 | WAKE: Wake                                                            | e-up on Start Bit                                       | Detect During                  | g Sleep Mode E                 | nable bit                              |                                                        |               |  |  |

|                       | in hardw                                                              | continues to sam<br>are on the follow<br>-up is enabled |                                |                                | generated on                           | the falling edge;                                      | bit is cleare |  |  |

| bit 6                 | LPBACK: UA                                                            | ARTx Loopback                                           | Mode Select                    | bit                            |                                        |                                                        |               |  |  |

|                       |                                                                       | Loopback mode<br>k mode is disab                        |                                |                                |                                        |                                                        |               |  |  |

| "d                    |                                                                       | -                                                       |                                |                                |                                        | 0000582) in the<br>JARTx module fo                     | or receive or |  |  |

|                       | -                                                                     | nly available for                                       | the 16y PDC                    | modo (BBCH -                   | 0)                                     |                                                        |               |  |  |

2: This feature is only available for the 16x BRG mode (BRGH = 0).

## 21.1 Control Registers

The CLCx module is controlled by the following registers:

- CLCxCONL

- CLCxCONH

- CLCxSEL

- CLCxGLSL

- CLCxGLSH

The CLCx Control registers (CLCxCONL and CLCxCONH) are used to enable the module and interrupts, control the output enable bit, select output polarity and select the logic function. The CLCx Control registers also allow the user to control the logic polarity of not only the cell output, but also some intermediate variables. The CLCx Input MUX Select register (CLCxSEL) allows the user to select up to 4 data input sources using the 4 data input selection multiplexers. Each multiplexer has a list of 8 data sources available.

The CLCx Gate Logic Input Select registers (CLCxGLSL and CLCxGLSH) allow the user to select which outputs from each of the selection MUXes are used as inputs to the input gates of the logic cell. Each data source MUX outputs both a true and a negated version of its output. All of these 8 signals are enabled, ORed together by the logic cell input gates.

### REGISTER 21-1: CLCxCONL: CLCx CONTROL REGISTER (LOW)

| D 444 0                |                                                            |                                            |                              |                   |                  |                 |       |  |  |  |

|------------------------|------------------------------------------------------------|--------------------------------------------|------------------------------|-------------------|------------------|-----------------|-------|--|--|--|

| R/W-0                  | U-0                                                        | U-0                                        | U-0                          | R/W-0             | R/W-0            | U-0             | U-0   |  |  |  |

| LCEN                   | —                                                          | —                                          | —                            | INTP              | INTN             | —               | —     |  |  |  |

| bit 15                 |                                                            |                                            |                              |                   |                  |                 | bit 8 |  |  |  |

|                        |                                                            |                                            |                              |                   |                  |                 |       |  |  |  |

| R-0                    | R-0                                                        | R/W-0                                      | U-0                          | U-0               | R/W-0            | R/W-0           | R/W-0 |  |  |  |

| LCOE                   | LCOUT LCPOL — — MODE2 MODE1 MO                             |                                            |                              |                   |                  |                 |       |  |  |  |

| bit 7                  |                                                            |                                            |                              |                   |                  |                 | bit 0 |  |  |  |

| Logondi                |                                                            |                                            |                              |                   |                  |                 |       |  |  |  |

| Legend:<br>R = Readabl | e hit                                                      | W = Writable t                             | nit                          | II – Unimplen     | nented bit, read | 1 ac '0'        |       |  |  |  |

| -n = Value at          |                                                            | '1' = Bit is set                           | JIL                          | '0' = Bit is clea |                  | x = Bit is unkr |       |  |  |  |

|                        | IFUR                                                       | I – DILIS SEL                              |                              |                   | areu             |                 | IOWIT |  |  |  |

| bit 15                 | LCEN: CLCx                                                 | Enable bit                                 |                              |                   |                  |                 |       |  |  |  |

|                        |                                                            | enabled and mi                             | kina input siar              | nals              |                  |                 |       |  |  |  |

|                        |                                                            | disabled and ha                            |                              |                   |                  |                 |       |  |  |  |

| bit 14-12              | Unimplemer                                                 | nted: Read as 'o                           | ,                            |                   |                  |                 |       |  |  |  |

| bit 11                 | INTP: CLCx                                                 | Positive Edge In                           | terrupt Enable               | e bit             |                  |                 |       |  |  |  |

|                        |                                                            | will be generate<br>will not be gene       |                              | ng edge occurs    | on LCOUT         |                 |       |  |  |  |

| bit 10                 | INTN: CLCx Negative Edge Interrupt Enable bit              |                                            |                              |                   |                  |                 |       |  |  |  |

|                        | 1 = Interrupt                                              | will be generate<br>will not be gene       | ed when a falli              |                   | on LCOUT         |                 |       |  |  |  |

| bit 9-8                | Unimplemer                                                 | nted: Read as '0                           | ,                            |                   |                  |                 |       |  |  |  |

| bit 7                  | LCOE: CLCx                                                 | Port Enable bit                            |                              |                   |                  |                 |       |  |  |  |

|                        | 1 = CLCx port pin output is enabled                        |                                            |                              |                   |                  |                 |       |  |  |  |

|                        | 0 = CLCx port pin output is disabled                       |                                            |                              |                   |                  |                 |       |  |  |  |

|                        | LCOUT: CLCx Data Output Status bit                         |                                            |                              |                   |                  |                 |       |  |  |  |

| bit 6                  |                                                            | •                                          | status bit                   |                   |                  |                 |       |  |  |  |

| bit 6                  | 1 = CLCx out                                               | tput high                                  | Satus Dit                    |                   |                  |                 |       |  |  |  |

|                        | 1 = CLCx out<br>0 = CLCx out                               | tput high<br>tput low                      |                              |                   |                  |                 |       |  |  |  |

| bit 6<br>bit 5         | 1 = CLCx out<br>0 = CLCx out<br><b>LCPOL:</b> CLC          | tput high<br>tput low<br>Cx Output Polarit | y Control bit                |                   |                  |                 |       |  |  |  |

|                        | 1 = CLCx out<br>0 = CLCx out<br>LCPOL: CLC<br>1 = The outp | tput high<br>tput low                      | y Control bit<br>is inverted | ed                |                  |                 |       |  |  |  |

### REGISTER 22-4: ADCON2H: ADC CONTROL REGISTER 2 HIGH

| R-0, HSC | R-0, HSC | r-0 | r-0 | r-0 | r-0 | R/W-0    | R/W-0    |

|----------|----------|-----|-----|-----|-----|----------|----------|

| REFRDY   | REFERR   | —   | —   | —   | —   | SHRSAMC9 | SHRSAMC8 |

| bit 15   |          |     |     |     |     |          | bit 8    |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SHRSAMC7 | SHRSAMC6 | SHRSAMC5 | SHRSAMC4 | SHRSAMC3 | SHRSAMC2 | SHRSAMC1 | SHRSAMC0 |

| bit 7    | ·        |          |          |          |          |          | bit 0    |

| Legend:           | r = Reserved bit | U = Unimplemented bit, read as '0'      |  |  |

|-------------------|------------------|-----------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | HSC = Hardware Settable/Clearable bit   |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |  |

| bit 15    | <b>REFRDY:</b> Band Gap and Reference Voltage Ready Flag bit<br>1 = Band gap is ready<br>0 = Band gap is not ready                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14    | <b>REFERR:</b> Band Gap or Reference Voltage Error Flag bit<br>1 = Band gap was removed after the ADC module was enabled (ADON = 1)<br>0 = No band gap error was detected                                        |

| bit 13-10 | Reserved: Maintain as '0'                                                                                                                                                                                        |

| bit 9-0   | <pre>SHRSAMC&lt;9:0&gt;: Shared ADC Core Sample Time Selection bits These bits specify the number of shared ADC Core Clock Periods (TADCORE) for the shared ADC core sample time. 111111111 = 1025 TADCORE</pre> |

### REGISTER 22-10: ADCON5H: ADC CONTROL REGISTER 5 HIGH

| U-0          | U-0                                                                                                                                                                               | U-0                                                                                                                                                               | U-0            | R/W-0                               | R/W-0           | R/W-0           | R/W-0         |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------|-----------------|-----------------|---------------|--|--|--|--|--|

| —            |                                                                                                                                                                                   |                                                                                                                                                                   | —              | WARMTIME3                           | WARMTIME2       | WARMTIME1       | WARMTIME0     |  |  |  |  |  |

| bit 15       |                                                                                                                                                                                   |                                                                                                                                                                   |                |                                     |                 |                 | bit 8         |  |  |  |  |  |

|              |                                                                                                                                                                                   |                                                                                                                                                                   |                |                                     |                 |                 |               |  |  |  |  |  |

| R/W-0        | U-0                                                                                                                                                                               | U-0                                                                                                                                                               | U-0            | R/W-0                               | R/W-0           | R/W-0           | R/W-0         |  |  |  |  |  |

| SHRCIE       | _                                                                                                                                                                                 |                                                                                                                                                                   |                | C3CIE                               | C2CIE           | C1CIE           | COCIE         |  |  |  |  |  |

| bit 7        |                                                                                                                                                                                   |                                                                                                                                                                   |                |                                     |                 |                 | bit 0         |  |  |  |  |  |

| Legend:      |                                                                                                                                                                                   |                                                                                                                                                                   |                |                                     |                 |                 |               |  |  |  |  |  |

| R = Readab   | le bit                                                                                                                                                                            | W = Writable                                                                                                                                                      | bit            | U = Unimplem                        | ented bit, read | as '0'          |               |  |  |  |  |  |

| -n = Value a |                                                                                                                                                                                   | '1' = Bit is set                                                                                                                                                  |                | '0' = Bit is clea                   |                 | x = Bit is unkn | own           |  |  |  |  |  |

|              |                                                                                                                                                                                   |                                                                                                                                                                   | -              |                                     |                 |                 | -             |  |  |  |  |  |

| bit 15-12    | Unimpleme                                                                                                                                                                         | nted: Read as                                                                                                                                                     | '0'            |                                     |                 |                 |               |  |  |  |  |  |

| bit 11-8     | WARMTIME                                                                                                                                                                          | E<3:0>: ADC De                                                                                                                                                    | edicated Core  | x Power-up Del                      | ay bits         |                 |               |  |  |  |  |  |

|              |                                                                                                                                                                                   |                                                                                                                                                                   | wer-up delay   | in the number o                     | f the Core Sour | ce Clock Perio  | ds (TCORESRC) |  |  |  |  |  |

|              | for all ADC                                                                                                                                                                       |                                                                                                                                                                   |                |                                     |                 |                 |               |  |  |  |  |  |

|              | -                                                                                                                                                                                 | 68 Source Cloc                                                                                                                                                    |                |                                     |                 |                 |               |  |  |  |  |  |

|              |                                                                                                                                                                                   | 1110 = 16384 Source Clock Periods<br>1101 = 8192 Source Clock Periods                                                                                             |                |                                     |                 |                 |               |  |  |  |  |  |

|              |                                                                                                                                                                                   | 1100 = 4096 Source Clock Periods                                                                                                                                  |                |                                     |                 |                 |               |  |  |  |  |  |

|              | 1011 <b>= 204</b>                                                                                                                                                                 | 1011 = 2048 Source Clock Periods                                                                                                                                  |                |                                     |                 |                 |               |  |  |  |  |  |

|              |                                                                                                                                                                                   | 1010 = 1024 Source Clock Periods                                                                                                                                  |                |                                     |                 |                 |               |  |  |  |  |  |

|              |                                                                                                                                                                                   | 1001 = 512 Source Clock Periods                                                                                                                                   |                |                                     |                 |                 |               |  |  |  |  |  |

|              |                                                                                                                                                                                   | 1000 = 256 Source Clock Periods<br>0111 = 128 Source Clock Periods                                                                                                |                |                                     |                 |                 |               |  |  |  |  |  |

|              |                                                                                                                                                                                   | Source Clock Pe                                                                                                                                                   |                |                                     |                 |                 |               |  |  |  |  |  |

|              |                                                                                                                                                                                   | Source Clock Pe                                                                                                                                                   |                |                                     |                 |                 |               |  |  |  |  |  |

|              |                                                                                                                                                                                   | Source Clock Pe                                                                                                                                                   |                |                                     |                 |                 |               |  |  |  |  |  |

|              |                                                                                                                                                                                   | Source Clock Pe                                                                                                                                                   |                |                                     |                 |                 |               |  |  |  |  |  |

| bit 7        |                                                                                                                                                                                   |                                                                                                                                                                   | -              | mon Interrupt Er                    |                 |                 |               |  |  |  |  |  |

|              | <ul> <li>1 = Common interrupt will be generated when ADC core is powered and ready for operation</li> <li>0 = Common interrupt is disabled for an ADC core ready event</li> </ul> |                                                                                                                                                                   |                |                                     |                 |                 |               |  |  |  |  |  |

| bit 6-4      |                                                                                                                                                                                   | nted: Read as                                                                                                                                                     |                | ADC core ready                      | event           |                 |               |  |  |  |  |  |

| bit 3        | -                                                                                                                                                                                 |                                                                                                                                                                   |                | ommon Interrunt                     | Fnable bit      |                 |               |  |  |  |  |  |

| bit o        |                                                                                                                                                                                   | <b>C3CIE:</b> Dedicated ADC Core 3 Ready Common Interrupt Enable bit<br>1 = Common interrupt will be generated when ADC Core 3 is powered and ready for operation |                |                                     |                 |                 |               |  |  |  |  |  |

|              | <ul> <li>0 = Common interrupt is disabled for an ADC Core 3 ready event</li> </ul>                                                                                                |                                                                                                                                                                   |                |                                     |                 |                 |               |  |  |  |  |  |

| bit 2        | C2CIE: Dedicated ADC Core 2 Ready Common Interrupt Enable bit                                                                                                                     |                                                                                                                                                                   |                |                                     |                 |                 |               |  |  |  |  |  |

|              |                                                                                                                                                                                   |                                                                                                                                                                   |                | when ADC Core                       |                 | nd ready for op | eration       |  |  |  |  |  |

| bit 1        |                                                                                                                                                                                   | -                                                                                                                                                                 |                | ADC Core 2 read<br>common Interrupt | -               |                 |               |  |  |  |  |  |

|              |                                                                                                                                                                                   |                                                                                                                                                                   | -              | when ADC Core                       |                 | nd ready for on | eration       |  |  |  |  |  |

|              |                                                                                                                                                                                   |                                                                                                                                                                   |                | ADC Core 1 read                     |                 |                 | Gradion       |  |  |  |  |  |

| bit 0        | COCIE: Ded                                                                                                                                                                        | icated ADC Co                                                                                                                                                     | re 0 Ready Co  | ommon Interrupt                     | Enable bit      |                 |               |  |  |  |  |  |

|              | 1 = Commo                                                                                                                                                                         | n interrupt will b                                                                                                                                                | e generated v  | when ADC Core                       | 0 is powered a  | nd ready for op | eration       |  |  |  |  |  |

|              | 0 = Commo                                                                                                                                                                         | n interrupt is dis                                                                                                                                                | abled for an A | ADC Core 0 read                     | dy event        |                 |               |  |  |  |  |  |

| R/W-0         | R/W-0                                         | R/W-0                                                                     | R/W-0            | R/W-0                               | R/W-0            | R/W-0              | R/W-0  |  |  |  |

|---------------|-----------------------------------------------|---------------------------------------------------------------------------|------------------|-------------------------------------|------------------|--------------------|--------|--|--|--|

| F15BP3        | F15BP2                                        | F15BP1                                                                    | F15BP0           | F14BP3                              | F14BP2           | F14BP1             | F14BP0 |  |  |  |

| bit 15        |                                               |                                                                           |                  |                                     |                  |                    | bit 8  |  |  |  |

|               |                                               |                                                                           |                  |                                     |                  |                    |        |  |  |  |

| R/W-0         | R/W-0                                         | R/W-0                                                                     | R/W-0            | R/W-0                               | R/W-0            | R/W-0              | R/W-0  |  |  |  |

| F13BP3        | F13BP2                                        | F13BP1                                                                    | F13BP0           | F12BP3                              | F12BP2           | F12BP1             | F12BP0 |  |  |  |

| bit 7         |                                               |                                                                           |                  |                                     |                  |                    | bit 0  |  |  |  |

|               |                                               |                                                                           |                  |                                     |                  |                    |        |  |  |  |

| Legend:       |                                               |                                                                           |                  |                                     |                  |                    |        |  |  |  |

| R = Readable  | e bit                                         | W = Writable bit                                                          |                  | U = Unimpler                        | l as '0'         |                    |        |  |  |  |

| -n = Value at | POR                                           | '1' = Bit is set                                                          |                  | '0' = Bit is cleared                |                  | x = Bit is unknown |        |  |  |  |

|               |                                               |                                                                           |                  |                                     |                  |                    |        |  |  |  |

| bit 15-12     | F15BP<3:0>: RX Buffer Mask for Filter 15 bits |                                                                           |                  |                                     |                  |                    |        |  |  |  |

|               | 1111 = Filter hits received in RX FIFO buffer |                                                                           |                  |                                     |                  |                    |        |  |  |  |

|               | 1110 <b>= Filte</b> r                         | hits received in                                                          | n RX Buffer 14   | 1                                   |                  |                    |        |  |  |  |

|               | •                                             |                                                                           |                  |                                     |                  |                    |        |  |  |  |

|               | •                                             |                                                                           |                  |                                     |                  |                    |        |  |  |  |

|               | 0001 = Filter                                 | hits received in                                                          | n RX Buffer 1    |                                     |                  |                    |        |  |  |  |

|               | 0000 <b>= Filte</b> r                         | hits received in                                                          | n RX Buffer 0    |                                     |                  |                    |        |  |  |  |

| bit 11-8      | F14BP<3:0>                                    | F14BP<3:0>: RX Buffer Mask for Filter 14 bits (same values as bits 15-12) |                  |                                     |                  |                    |        |  |  |  |

| bit 7-4       | F13BP<3:0>: RX Buffer Mask for Filter 13      |                                                                           |                  | 13 bits (same values as bits 15-12) |                  |                    |        |  |  |  |

| bit 7-4       | F13BP<3:0>                                    | : RX Buffer Ma                                                            | sk for Filter 13 | 3 bits (same va                     | lues as bits 15- | 12)                |        |  |  |  |

### REGISTER 23-15: CxBUFPNT4: CANx FILTERS 12-15 BUFFER POINTER REGISTER 4

bit 3-0 F12BP<3:0>: RX Buffer Mask for Filter 12 bits (same values as bits 15-12)

### BUFFER 21-7: CANx MESSAGE BUFFER WORD 6

| R/W-x                              | R/W-x | R/W-x | R/W-x            | R/W-x        | R/W-x           | R/W-x     | R/W-x |

|------------------------------------|-------|-------|------------------|--------------|-----------------|-----------|-------|

|                                    |       |       | Byte             | 7<15:8>      |                 |           |       |

| bit 15                             |       |       |                  |              |                 |           | bit 8 |

|                                    |       |       |                  |              |                 |           |       |

| R/W-x                              | R/W-x | R/W-x | R/W-x            | R/W-x        | R/W-x           | R/W-x     | R/W-x |

|                                    |       |       | Byte             | 6<7:0>       |                 |           |       |

| bit 7                              |       |       |                  |              |                 |           | bit 0 |

|                                    |       |       |                  |              |                 |           |       |

| Legend:                            |       |       |                  |              |                 |           |       |

| R = Readable bit W = Writable bit  |       |       | bit              | U = Unimpler | nented bit, rea | ıd as '0' |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle | ared         | x = Bit is unkı | nown      |       |

| bit 15-8 | Byte 7<15:8>: CANx Message Byte 7 bits |

|----------|----------------------------------------|

|          |                                        |

bit 7-0 Byte 6<7:0>: CANx Message Byte 6 bits

### BUFFER 21-8: CANx MESSAGE BUFFER WORD 7

| U-0    | U-0 | U-0 | R/W-x | R/W-x | R/W-x         | R/W-x | R/W-x |

|--------|-----|-----|-------|-------|---------------|-------|-------|

| _      | —   | —   |       |       | FILHIT<4:0>(1 | )     |       |

| bit 15 |     |     |       |       |               |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | _   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15-13 | Unimplemented: Read as '0'                                     |

|-----------|----------------------------------------------------------------|

| bit 12-8  | FILHIT<4:0>: Filter Hit Code bits <sup>(1)</sup>               |

|           | Encodes number of filter that resulted in writing this buffer. |

| bit 7-0   | Unimplemented: Read as '0'                                     |

Note 1: Only written by module for receive buffers, unused for transmit buffers.

## 24.2 Module Description

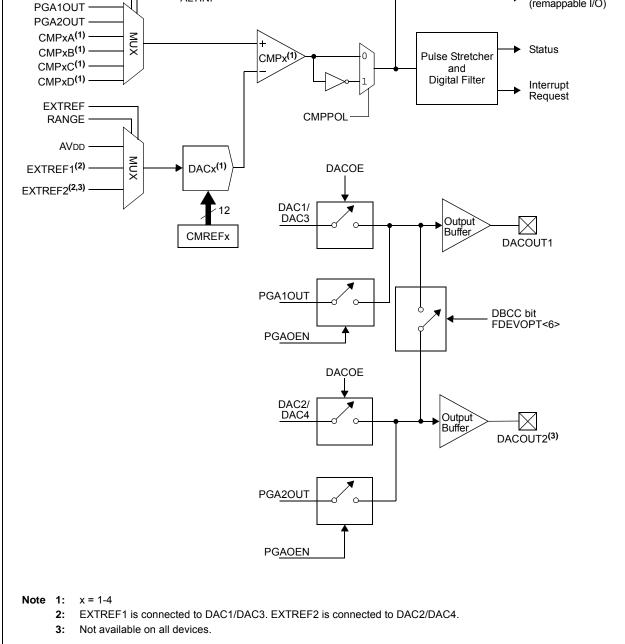

**FIGURE 24-1:**

Figure 24-1 shows a functional block diagram of one analog comparator from the high-speed analog comparator module. The analog comparator provides high-speed operation with a typical delay of 15 ns. The negative input of the comparator is always connected to the DACx circuit. The positive input of the comparator is connected to an analog multiplexer that selects the desired source pin. The analog comparator input pins are typically shared with pins used by the Analog-to-Digital Converter (ADC) module. Both the comparator and the ADC can use the same pins at the same time. This capability enables a user to measure an input voltage with the ADC and detect voltage transients with the comparator.

HIGH-SPEED ANALOG COMPARATOR x MODULE BLOCK DIAGRAM

| R/W-0           | U-0                                                          | R/W-0                                                                                | R/W-0                               | R/W-0                  | R/W-0            | R/W-0            | R/W-0           |  |  |

|-----------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------|------------------------|------------------|------------------|-----------------|--|--|

| CMPON           | _                                                            | CMPSIDL                                                                              | HYSSEL1                             | HYSSELO                | FLTREN           | FCLKSEL          | DACOE           |  |  |

| bit 15          |                                                              |                                                                                      |                                     |                        |                  |                  | bit 8           |  |  |

|                 |                                                              |                                                                                      |                                     |                        |                  |                  |                 |  |  |

| R/W-0           | R/W-0                                                        | R/W-0                                                                                | R/W-0                               | HC-0, HS               | R/W-0            | R/W-0            | R/W-0           |  |  |

| INSEL1          | INSEL0                                                       | EXTREF                                                                               | HYSPOL                              | CMPSTAT                | ALTINP           | CMPPOL           | RANGE           |  |  |

| bit 7           |                                                              | I                                                                                    |                                     |                        | I                |                  | bit 0           |  |  |

|                 |                                                              |                                                                                      |                                     |                        |                  |                  |                 |  |  |

| Legend:         |                                                              | HC = Hardware                                                                        | e Clearable bit                     | HS = Hardwa            | are Settable bit |                  |                 |  |  |

| R = Readable    | bit                                                          | W = Writable b                                                                       | bit                                 | U = Unimpler           | mented bit, read | l as '0'         |                 |  |  |

| -n = Value at I | POR                                                          | '1' = Bit is set                                                                     |                                     | '0' = Bit is cle       | ared             | x = Bit is unkr  | iown            |  |  |

| bit 15          | 1 = Compara                                                  | mparator Opera<br>tor module is er<br>tor module is di                               | nabled                              | s power consu          | imption)         |                  |                 |  |  |

| bit 14          | Unimplemen                                                   | ted: Read as 'd                                                                      | )'                                  |                        |                  |                  |                 |  |  |

| bit 13          | CMPSIDL: C                                                   | omparator Stop                                                                       | in Idle Mode b                      | it                     |                  |                  |                 |  |  |

|                 | 0 = Continue<br>If a device has                              | ues module opera<br>s module opera<br>s multiple compa                               | tion in Idle moo<br>rators, any CMF | de<br>PSIDL bit set to |                  | omparators while | e in Idle mode. |  |  |

| bit 12-11       |                                                              | <b>HYSSEL&lt;1:0&gt;:</b> Comparator Hysteresis Select bits<br>11 = 45 mV hysteresis |                                     |                        |                  |                  |                 |  |  |

|                 | 10 = 30 mV h<br>01 = 15 mV h                                 | nysteresis                                                                           | ed                                  |                        |                  |                  |                 |  |  |

| bit 10          | FLTREN: Dig                                                  | ital Filter Enabl                                                                    | e bit                               |                        |                  |                  |                 |  |  |

|                 | 1 = Digital filt<br>0 = Digital filt                         |                                                                                      |                                     |                        |                  |                  |                 |  |  |

| bit 9           | FCLKSEL: D                                                   | igital Filter and                                                                    | Pulse Stretche                      | r Clock Select         | bit              |                  |                 |  |  |

|                 | •                                                            | er and pulse str<br>er and pulse str                                                 | •                                   |                        |                  |                  |                 |  |  |