Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                           |

| Number of I/O              | 33                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 17x12b; D/A 1x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 48-TQFP                                                                           |

| Supplier Device Package    | 48-TQFP (7x7)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs705t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                                       |     |

|-------|-----------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Digital Signal Controllers |     |

| 3.0   | CPU                                                                   |     |

| 4.0   | Memory Organization                                                   |     |

| 5.0   | Flash Program Memory                                                  |     |

| 6.0   | Resets                                                                |     |

| 7.0   | Interrupt Controller                                                  |     |

| 8.0   | Direct Memory Access (DMA)                                            |     |

| 9.0   | Oscillator Configuration                                              | 103 |

| 10.0  | Power-Saving Features                                                 | 115 |

| 11.0  | I/O Ports                                                             | 125 |

| 12.0  | Timer1                                                                |     |

| 13.0  | Timer2/3 and Timer4/5                                                 | 173 |

| 14.0  | Input Capture                                                         | 177 |

| 15.0  | Output Compare                                                        | 181 |

| 16.0  | High-Speed PWM                                                        |     |

| 17.0  |                                                                       |     |

| 18.0  |                                                                       |     |

| 19.0  |                                                                       |     |

| 20.0  |                                                                       |     |

| 21.0  |                                                                       |     |

| 22.0  | <b>J</b> - [ <b>J J J J</b>                                           |     |

| 23.0  |                                                                       |     |

| 24.0  | High-Speed Analog Comparator                                          |     |

| 25.0  |                                                                       |     |

| 26.0  | Constant-Current Source                                               |     |

| 27.0  | Special Features                                                      |     |

| 28.0  | Instruction Set Summary                                               |     |

| 29.0  |                                                                       |     |

| 30.0  |                                                                       |     |

|       | DC and AC Device Characteristics Graphs                               |     |

|       | Packaging Information                                                 |     |

| Appe  | endix A: Revision History                                             |     |

| Index | Χ                                                                     |     |

|       | Microchip Web Site                                                    |     |

|       | omer Change Notification Service                                      |     |

|       | omer Support                                                          |     |

| Prod  | uct Identification System                                             |     |

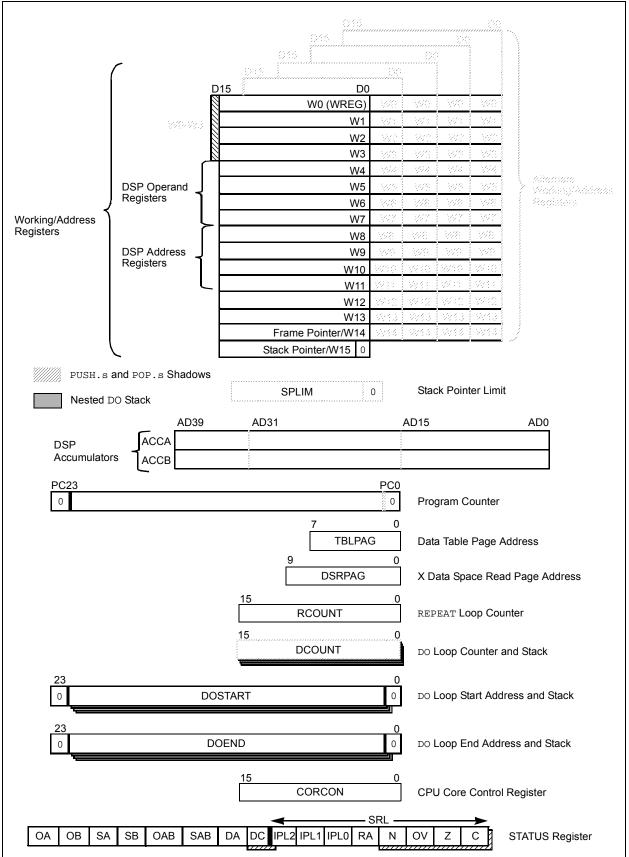

### 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 3.6.1 KEY RESOURCES

- "dsPIC33E Enhanced CPU" (DS70005158) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **"Oscillator Module"** (DS70005131) in the *"dsPIC33/PIC24 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGS70X/80X family oscillator system provides:

- On-Chip Phase-Locked Loop (PLL) to Boost Internal Operating Frequency on Select Internal and External Oscillator Sources

- On-the-Fly Clock Switching between Various Clock Sources

- Doze mode for System Power Savings

- Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown

- Configuration Bits for Clock Source Selection

- Auxiliary PLL for ADC and PWM

A simplified diagram of the oscillator system is shown in Figure 9-1.

### REGISTER 9-7: LFSR: LINEAR FEEDBACK SHIFT REGISTER

| U-0                                | R/W-0 | R/W-0                | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|----------------------|-------|------------------------------------|-------|-------|-------|

| —                                  |       |                      |       | LFSR<14:8>                         | ,     |       |       |

| bit 15                             |       |                      |       |                                    |       |       | bit 8 |

|                                    |       |                      |       |                                    |       |       |       |

| R/W-0                              | R/W-0 | R/W-0                | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |                      | LFS   | R<7:0>                             |       |       |       |

| bit 7                              |       |                      |       |                                    |       |       | bit C |

|                                    |       |                      |       |                                    |       |       |       |

| Legend:                            |       |                      |       |                                    |       |       |       |

| R = Readable bit W = Writable bit  |       |                      | bit   | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cleared |       | x = Bit is unknown                 |       |       |       |

bit 15 Unimplemented: Read as '0'

bit 14-0 LFSR<14:0>: Pseudorandom Data bits

| Function               | RPnR<6:0> | Output Name                                                 |

|------------------------|-----------|-------------------------------------------------------------|

| Default PORT           | 0000000   | RPn tied to Default Pin                                     |

| U1TX                   | 0000001   | RPn tied to UART1 Transmit                                  |

| U1RTS                  | 0000010   | RPn tied to UART1 Request-to-Send                           |

| U2TX                   | 0000011   | RPn tied to UART2 Transmit                                  |

| U2RTS                  | 0000100   | RPn tied to UART2 Request-to-Send                           |

| SDO1                   | 0000101   | RPn tied to SPI1 Data Output                                |

| SCK1                   | 0000110   | RPn tied to SPI1 Clock Output                               |

| SS1                    | 0000111   | RPn tied to SPI1 Slave Select                               |

| SDO2                   | 0001000   | RPn tied to SPI2 Data Output                                |

| SCK2                   | 0001001   | RPn tied to SPI2 Clock Output                               |

| SS2                    | 0001010   | RPn tied to SPI2 Slave Select                               |

| C1TX                   | 0001110   | RPn tied to CAN1 Transmit                                   |

| C2TX                   | 0001111   | RPn tied to CAN2 Transmit                                   |

| OC1                    | 0010000   | RPn tied to Output Compare 1 Output                         |

| OC2                    | 0010001   | RPn tied to Output Compare 2 Output                         |

| OC3                    | 0010010   | RPn tied to Output Compare 3 Output                         |

| OC4                    | 0010011   | RPn tied to Output Compare 4 Output                         |

| ACMP1                  | 0011000   | RPn tied to Analog Comparator 1 Output                      |

| ACMP2                  | 0011001   | RPn tied to Analog Comparator 2 Output                      |

| ACMP3                  | 0011010   | RPn tied to Analog Comparator 3 Output                      |

| SDO3                   | 0011111   | RPn tied to SPI3 Data Output                                |

| SCK3                   | 0100000   | RPn tied to SPI3 Clock Output                               |

| SS3                    | 0100001   | RPn tied to SPI3 Slave Select                               |

| SYNCO1                 | 0101101   | RPn tied to PWM Primary Master Time Base Sync Output        |

| SYNCO2                 | 0101110   | RPn tied to PWM Secondary Master Time Base Sync Output      |

| REFCLKO                | 0110001   | RPn tied to Reference Clock Output                          |

| ACMP4                  | 0110010   | RPn tied to Analog Comparator 4 Output                      |

| PWM4H                  | 0110011   | RPn tied to PWM Output Pins Associated with PWM Generator 4 |

| PWM4L                  | 0110100   | RPn tied to PWM Output Pins Associated with PWM Generator 4 |

| PWM5H                  | 0110101   | RPn tied to PWM Output Pins Associated with PWM Generator 5 |

| PWM5L                  | 0110110   | RPn tied to PWM Output Pins Associated with PWM Generator 5 |

| PWM6H                  | 0111001   | RPn tied to PWM Output Pins Associated with PWM Generator 6 |

| PWM6L                  | 0111010   | RPn tied to PWM Output Pins Associated with PWM Generator 6 |

| PWM7H                  | 0111011   | RPn tied to PWM Output Pins Associated with PWM Generator 7 |

| PWM7L                  | 0111100   | RPn tied to PWM Output Pins Associated with PWM Generator 7 |

| PWM8H                  | 0111101   | RPn tied to PWM Output Pins Associated with PWM Generator 8 |

| PWM8L                  | 0111110   | RPn tied to PWM Output Pins Associated with PWM Generator 8 |

| CLC1OUT                | 0111111   | RPn tied to CLC1 Output                                     |

| CLC2OUT                | 1000000   | RPn tied to CLC2 Output                                     |

| CLC3OUT <sup>(1)</sup> | 1000001   | RPn tied to CLC3 Output                                     |

| CLC4OUT <sup>(1)</sup> | 1000010   | RPn tied to CLC4 Output                                     |

Note 1: PPS outputs are only available on dsPIC33EPXXXGS702 (28-pin) devices.

| U-0    | R/W-0   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| —      | RP181R6 | RP181R5 | RP181R4 | RP181R3 | RP181R2 | RP181R1 | RP181R0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

|        |         |         |         |         |         |         |         |

| 11-0   | R/W-0   | R/W-0   | R/\/_0  | R/W-0   | R/\\/_0 | R/W-0   | R/\\/_0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | RP180R6 | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 |

| U-0   | R/W-0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 Unimplemented: Read as '0'

bit 14-8 **RP181R<6:0>:** Peripheral Output Function is Assigned to RP181 Output Pin bits (see Table 11-13 for peripheral function numbers)

bit 7 Unimplemented: Read as '0'

bit 6-0 **RP180R<6:0>:** Peripheral Output Function is Assigned to RP180 Output Pin bits (see Table 11-13 for peripheral function numbers)

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | IC32  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0                 | R/W-0, HS               | U-0 | R/W-0       | R/W-1       | R/W-1       | R/W-0       | R/W-1       |

|-----------------------|-------------------------|-----|-------------|-------------|-------------|-------------|-------------|

| ICTRIG <sup>(2)</sup> | TRIGSTAT <sup>(3)</sup> |     | SYNCSEL4(4) | SYNCSEL3(4) | SYNCSEL2(4) | SYNCSEL1(4) | SYNCSEL0(4) |

| bit 7                 |                         |     |             |             |             |             | bit 0       |

| Legend:           | HS = Hardware Settable bi | t                           |                    |

|-------------------|---------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-9 <b>Unimplemented:</b> Read as '0' |

|--------------------------------------------|

|--------------------------------------------|

bit 8 **IC32:** Input Capture x 32-Bit Timer Mode Select bit (Cascade mode)

- 1 = Odd ICx and even ICx form a single 32-bit input capture module<sup>(1)</sup>

- 0 = Cascade module operation is disabled

#### bit 7 ICTRIG: Input Capture x Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source is used to trigger the input capture timer (Trigger mode)

- 0 = Input source is used to synchronize the input capture timer to a timer of another module (Synchronization mode)

#### bit 6 **TRIGSTAT:** Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

- bit 5 Unimplemented: Read as '0'

- Note 1: The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own sync or trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

### 17.2 PTG Control Registers

### REGISTER 17-1: PTGCST: PTG CONTROL/STATUS REGISTER

|                 | U-0                                                                                                      | R/W-0                                                  | R/W-0                  | U-0              | R/W-0                 | R/W-0                  | R/W-0                 |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------|------------------|-----------------------|------------------------|-----------------------|--|--|

| PTGEN           | _                                                                                                        | PTGSIDL                                                | PTGTOGL                | _                | PTGSWT <sup>(2)</sup> | PTGSSEN                | PTGIVIS               |  |  |

| bit 15          |                                                                                                          |                                                        |                        | •                |                       |                        | bit 8                 |  |  |

|                 |                                                                                                          |                                                        |                        |                  |                       |                        |                       |  |  |

| R/W-0           | HS-0                                                                                                     | U-0                                                    | U-0                    | U-0              | U-0                   | R/W-0                  | R/W-0                 |  |  |

| PTGSTRT         | PTGWDTO                                                                                                  |                                                        |                        |                  | _                     | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1</sup> |  |  |

| bit 7           |                                                                                                          |                                                        |                        |                  |                       |                        | bit                   |  |  |

| Legend:         |                                                                                                          | HS = Hardware                                          | e Settable bit         |                  |                       |                        |                       |  |  |

| R = Readable    | bit                                                                                                      | W = Writable b                                         |                        | U = Unimple      | mented bit, rea       | d as '0'               |                       |  |  |

| -n = Value at F | POR                                                                                                      | '1' = Bit is set                                       |                        | '0' = Bit is cle |                       | x = Bit is unkr        | iown                  |  |  |

|                 |                                                                                                          |                                                        |                        |                  |                       |                        |                       |  |  |

| bit 15          |                                                                                                          | 6 Module Enable                                        | e bit                  |                  |                       |                        |                       |  |  |

|                 |                                                                                                          | ule is enabled                                         |                        |                  |                       |                        |                       |  |  |

| bit 14          |                                                                                                          | nted: Read as '0                                       | ,                      |                  |                       |                        |                       |  |  |

| bit 13          | -                                                                                                        | TG Stop in Idle I                                      |                        |                  |                       |                        |                       |  |  |

|                 |                                                                                                          | ues module ope                                         |                        | vice enters Id   | le mode               |                        |                       |  |  |

|                 | 0 = Continue                                                                                             | s module opera                                         | tion in Idle mod       | е                |                       |                        |                       |  |  |

| bit 12          | PTGTOGL: F                                                                                               | PTG TRIG Outp                                          | ut Toggle Mode         | bit              |                       |                        |                       |  |  |

|                 | 0 = Each exe                                                                                             | the state of the<br>ecution of the Pt<br>the PTGPWDx I | GTRIG comma            |                  |                       |                        | rmined by the         |  |  |

| bit 11          | Unimplemen                                                                                               | ted: Read as 'o                                        | ,                      |                  |                       |                        |                       |  |  |

| bit 10          | PTGSWT: PT                                                                                               | G Software Trig                                        | ger bit <sup>(2)</sup> |                  |                       |                        |                       |  |  |

|                 |                                                                                                          | the PTG module                                         |                        | <b>ff</b> + )    |                       |                        |                       |  |  |

| <b>h</b> # 0    |                                                                                                          | (clearing this b                                       |                        | nect)            |                       |                        |                       |  |  |

| bit 9           |                                                                                                          | PTG Enable Sing<br>Single-Step mod                     |                        |                  |                       |                        |                       |  |  |

|                 |                                                                                                          | Single-Step mo                                         |                        |                  |                       |                        |                       |  |  |

| bit 8           |                                                                                                          | G Counter/Time                                         |                        | rol bit          |                       |                        |                       |  |  |

|                 |                                                                                                          | f the PTGSDLI                                          | •                      |                  | registers retur       | n the current v        | alues of the          |  |  |

|                 | 0 = Reads of                                                                                             | nding Counter/<br>f the PTGSDLIN                       | I, PTGCxLIM or         |                  |                       | he value previo        | usly written t        |  |  |

| bit 7           | those PTG Limit registers  PTCSTPT. Start PTC Sequencer bit                                              |                                                        |                        |                  |                       |                        |                       |  |  |

|                 | <b>PTGSTRT:</b> Start PTG Sequencer bit<br>1 = Starts to sequentially execute commands (Continuous mode) |                                                        |                        |                  |                       |                        |                       |  |  |

|                 | <ul> <li>0 = Stops executing commands</li> </ul>                                                         |                                                        |                        |                  |                       |                        |                       |  |  |

|                 |                                                                                                          |                                                        |                        |                  |                       |                        |                       |  |  |

| bit 6           | PTGWDTO:                                                                                                 | PTG Watchdog                                           | Timer Time-out         | Status bit       |                       |                        |                       |  |  |

| bit 6           | 1 = PTG Wat                                                                                              | PTG Watchdog<br>chdog Timer ha<br>chdog Timer ha       | s timed out            |                  |                       |                        |                       |  |  |

2: This bit is only used with the PTGCTRL Step command software trigger option.

To set up the SPIx module for Audio mode:

- 1. Clear the SPIxBUFL and SPIxBUFH registers.

- 2. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- a) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with AUDEN (SPIxCON1H<15>) = 1.

- 4. Clear the SPIROV bit (SPIxSTATL<6>).

- Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- 6. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

#### REGISTER 18-1: SPIxCON1L: SPIx CONTROL REGISTER 1 LOW

| Legend:<br>R = Readable |       | W = Writable |        |                         | ented bit read          | (0)   |                    |

|-------------------------|-------|--------------|--------|-------------------------|-------------------------|-------|--------------------|

| bit 7                   |       |              |        |                         |                         |       | bit 0              |

| SSEN <sup>(2)</sup>     | CKP   | MSTEN        | DISSDI | DISSCK                  | MCLKEN <sup>(3)</sup>   | SPIFE | ENHBUF             |

| R/W-0                   | R/W-0 | R/W-0        | R/W-0  | R/W-0                   | R/W-0                   | R/W-0 | R/W-0              |

| bit 15                  |       |              |        |                         |                         |       | bit 8              |

| SPIEN                   | _     | SPISIDL      | DISSDO | MODE32 <sup>(1,4)</sup> | MODE16 <sup>(1,4)</sup> | SMP   | CKE <sup>(1)</sup> |

| R/W-0                   | U-0   | R/W-0        | R/W-0  | R/W-0                   | R/W-0                   | R/W-0 | R/W-0              |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 15 SPIEN: SPIx On bit

- 1 = Enables module

- 0 = Turns off and resets module, disables clocks, disables interrupt event generation, allows SFR modifications

#### bit 14 Unimplemented: Read as '0'

- bit 13 SPISIDL: SPIx Stop in Idle Mode bit

- 1 = Halts in CPU Idle mode

- 0 = Continues to operate in CPU Idle mode

#### bit 12 DISSDO: Disable SDOx Output Port bit

1 = SDOx pin is not used by the module; pin is controlled by port function

#### 0 = SDOx pin is controlled by the module

#### bit 11-10 MODE32 and MODE16: Serial Word Length Select bits<sup>(1,4)</sup>

| MODE32 | MODE16 | AUDEN | Communication                                         |

|--------|--------|-------|-------------------------------------------------------|

| 1      | x      |       | 32-Bit                                                |

| 0      | 1      | 0     | 16-Bit                                                |

| 0      | 0      |       | 8-Bit                                                 |

| 1      | 1      |       | 24-Bit Data, 32-Bit FIFO, 32-Bit Channel/64-Bit Frame |

| 1      | 0      | -     | 32-Bit Data, 32-Bit FIFO, 32-Bit Channel/64-Bit Frame |

| 0      | 1      | T     | 16-Bit Data, 16-Bit FIFO, 32-Bit Channel/64-Bit Frame |

| 0      | 0 0    |       | 16-Bit FIFO, 16-Bit Channel/32-Bit Frame              |

#### **Note 1:** When AUDEN (SPIxCON1H<15>) = 1, this module functions as if CKE = 0, regardless of its actual value.

- 2: When FRMEN = 1, SSEN is not used.

- 3: MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows FRMSYPW.

#### REGISTER 18-5: SPIxSTATH: SPIx STATUS REGISTER HIGH

| U-0    | U-0 | R-0, HSC              | R-0, HSC              | R-0, HSC              | R-0, HSC | R-0, HSC | R-0, HSC |

|--------|-----|-----------------------|-----------------------|-----------------------|----------|----------|----------|

| —      | —   | RXELM5 <sup>(3)</sup> | RXELM4 <sup>(2)</sup> | RXELM3 <sup>(1)</sup> | RXELM2   | RXELM1   | RXELM0   |

| bit 15 |     |                       |                       |                       |          |          | bit 8    |

| U-0   | U-0 | R-0, HSC              | R-0, HSC              | R-0, HSC              | R-0, HSC | R-0, HSC | R-0, HSC |

|-------|-----|-----------------------|-----------------------|-----------------------|----------|----------|----------|

| _     | —   | TXELM5 <sup>(3)</sup> | TXELM4 <sup>(2)</sup> | TXELM3 <sup>(1)</sup> | TXELM2   | TXELM1   | TXELM0   |

| bit 7 |     |                       |                       |                       |          |          | bit 0    |

| Legend:           | HSC = Hardware Settable/Clearable bit |                             |                    |  |  |  |

|-------------------|---------------------------------------|-----------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read | d as '0'           |  |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared        | x = Bit is unknown |  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RXELM<5:0>:** Receive Buffer Element Count bits (valid in Enhanced Buffer mode)<sup>(1,2,3)</sup>

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **TXELM<5:0>:** Transmit Buffer Element Count bits (valid in Enhanced Buffer mode)<sup>(1,2,3)</sup>

**Note 1:** RXELM3 and TXELM3 bits are only present when FIFODEPTH = 8 or higher.

2: RXELM4 and TXELM4 bits are only present when FIFODEPTH = 16 or higher.

3: RXELM5 and TXELM5 bits are only present when FIFODEPTH = 32.

### REGISTER 22-26: ADTRIGxL: ADC CHANNEL TRIGGER x SELECTION REGISTER LOW (x = 0 to 5) (CONTINUED)

bit 4-0 TRGSRC(4x)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits 11111 = ADTRG31 11110 = PTG Trigger Output 30 11101 = PWM Generator 6 current-limit trigger 11100 = PWM Generator 5 current-limit trigger 11011 = PWM Generator 4 current-limit trigger 11010 = PWM Generator 3 current-limit trigger 11001 = PWM Generator 2 current-limit trigger 11000 = PWM Generator 1 current-limit trigger 10111 = Output Compare 2 trigger 10110 = Output Compare 1 trigger 10101 = CLC2 output 10100 = PWM Generator 6 secondary trigger 10011 = PWM Generator 5 secondary trigger 10010 = PWM Generator 4 secondary trigger 10001 = PWM Generator 3 secondary trigger 10000 = PWM Generator 2 secondary trigger 01111 = PWM Generator 1 secondary trigger 01110 = PWM secondary Special Event Trigger 01101 = Timer2 period match 01100 = Timer1 period match 01011 = CLC1 output 01010 = PWM Generator 6 primary trigger 01001 = PWM Generator 5 primary trigger 01000 = PWM Generator 4 primary trigger 00111 = PWM Generator 3 primary trigger 00110 = PWM Generator 2 primary trigger 00101 = PWM Generator 1 primary trigger 00100 = PWM Special Event Trigger 00011 = Reserved 00010 = Level software trigger 00001 = Common software trigger

00000 = No trigger is enabled

#### 23.4 CAN Message Buffers

CAN Message Buffers are part of RAM memory. They are not CAN Special Function Registers. The user application must directly write into the RAM area that is configured for CAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: CANx MESSAGE BUFFER WORD 0

| U-0                           | U-0                                | U-0                                                                                                                           | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x |  |  |

|-------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|------------------|-----------------|-------|--|--|

| _                             |                                    |                                                                                                                               | SID10         | SID9             | SID8             | SID7            | SID6  |  |  |

| bit 15                        |                                    |                                                                                                                               |               | •<br>•           |                  |                 | bit 8 |  |  |

|                               |                                    |                                                                                                                               |               |                  |                  |                 |       |  |  |

| R/W-x                         | R/W-x R/W-x R/W-x                  |                                                                                                                               | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x |  |  |

| SID5                          | SID4                               | SID4 SID3 SID2                                                                                                                |               |                  | SID0             | SRR             | IDE   |  |  |

| bit 7                         |                                    |                                                                                                                               |               |                  |                  |                 | bit 0 |  |  |

| <b>Legend:</b><br>R = Readabl | e bit                              | W = Writable                                                                                                                  | bit           | U = Unimpler     | mented bit, read | d as '0'        |       |  |  |

| -n = Value at                 | -n = Value at POR '1' = Bit is set |                                                                                                                               |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |

|                               |                                    |                                                                                                                               |               |                  |                  |                 |       |  |  |

| bit 15-13                     | Unimplemen                         | ted: Read as '                                                                                                                | 0'            |                  |                  |                 |       |  |  |

| bit 12-2                      | SID<10:0>: S                       | Standard Identif                                                                                                              | ier bits      |                  |                  |                 |       |  |  |

| bit 1                         | SRR: Substit                       | ute Remote Re                                                                                                                 | quest bit     |                  |                  |                 |       |  |  |

|                               | When IDE =                         | 0:                                                                                                                            |               |                  |                  |                 |       |  |  |

|                               | 1 = Message                        | will request rer                                                                                                              | note transmis | ssion            |                  |                 |       |  |  |

|                               | 0 = Normal message                 |                                                                                                                               |               |                  |                  |                 |       |  |  |

|                               | When IDE =                         | 1:                                                                                                                            |               |                  |                  |                 |       |  |  |

|                               | The SRR bit                        | must be set to '                                                                                                              | 1'.           |                  |                  |                 |       |  |  |

| bit 0                         | IDE: Extende                       | d Identifier bit                                                                                                              |               |                  |                  |                 |       |  |  |

|                               |                                    | <ul> <li>1 = Message will transmit an Extended Identifier</li> <li>0 = Message will transmit a Standard Identifier</li> </ul> |               |                  |                  |                 |       |  |  |

|                               |                                    |                                                                                                                               |               |                  |                  |                 |       |  |  |

#### BUFFER 21-2: CANx MESSAGE BUFFER WORD 1

| U-0                               | U-0   | U-0              | U-0     | R/W-x                              | R/W-x | R/W-x           | R/W-x |

|-----------------------------------|-------|------------------|---------|------------------------------------|-------|-----------------|-------|

| —                                 | —     | —                | — — EIC |                                    |       | <17:14>         |       |

| bit 15                            |       |                  |         |                                    |       |                 | bit 8 |

|                                   |       |                  |         |                                    |       |                 |       |

| R/W-x                             | R/W-x | R/W-x            | R/W-x   | R/W-x                              | R/W-x | R/W-x           | R/W-x |

|                                   |       |                  | EID     | <13:6>                             |       |                 |       |

| bit 7                             |       |                  |         |                                    |       |                 | bit ( |

|                                   |       |                  |         |                                    |       |                 |       |

| Legend:                           |       |                  |         |                                    |       |                 |       |

| R = Readable bit W = Writable bit |       |                  | bit     | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at POR '1' = B         |       | '1' = Bit is set |         | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

NOTES:

| R/W-0           | U-0                                                           | R/W-0                                                  | R/W-0                               | R/W-0                  | R/W-0            | R/W-0            | R/W-0           |  |  |

|-----------------|---------------------------------------------------------------|--------------------------------------------------------|-------------------------------------|------------------------|------------------|------------------|-----------------|--|--|

| CMPON           | _                                                             | CMPSIDL                                                | HYSSEL1                             | HYSSELO                | FLTREN           | FCLKSEL          | DACOE           |  |  |

| bit 15          |                                                               |                                                        |                                     |                        |                  |                  | bit 8           |  |  |

|                 |                                                               |                                                        |                                     |                        |                  |                  |                 |  |  |

| R/W-0           | R/W-0                                                         | R/W-0                                                  | R/W-0                               | HC-0, HS               | R/W-0            | R/W-0            | R/W-0           |  |  |

| INSEL1          | INSEL0                                                        | EXTREF                                                 | HYSPOL                              | CMPSTAT                | ALTINP           | CMPPOL           | RANGE           |  |  |

| bit 7           |                                                               | I                                                      |                                     |                        | I                |                  | bit 0           |  |  |

|                 |                                                               |                                                        |                                     |                        |                  |                  |                 |  |  |

| Legend:         |                                                               | HC = Hardware                                          | e Clearable bit                     | HS = Hardwa            | are Settable bit |                  |                 |  |  |

| R = Readable    | bit                                                           | W = Writable b                                         | bit                                 | U = Unimpler           | mented bit, read | l as '0'         |                 |  |  |

| -n = Value at I | POR                                                           | '1' = Bit is set                                       |                                     | '0' = Bit is cle       | ared             | x = Bit is unkr  | iown            |  |  |

| bit 15          | 1 = Compara                                                   | mparator Opera<br>tor module is er<br>tor module is di | nabled                              | s power consu          | Imption)         |                  |                 |  |  |

| bit 14          | Unimplemen                                                    | ted: Read as 'd                                        | )'                                  |                        |                  |                  |                 |  |  |

| bit 13          | CMPSIDL: C                                                    | omparator Stop                                         | in Idle Mode b                      | it                     |                  |                  |                 |  |  |

|                 | 0 = Continue<br>If a device has                               | ues module opera<br>s module opera<br>s multiple compa | tion in Idle moo<br>rators, any CMF | de<br>PSIDL bit set to |                  | omparators while | e in Idle mode. |  |  |

| bit 12-11       |                                                               | <b>)&gt;:</b> Comparator                               | Hysteresis Sel                      | ect bits               |                  |                  |                 |  |  |

|                 | 11 = 45 mV k<br>10 = 30 mV k<br>01 = 15 mV k<br>00 = No hyste | nysteresis                                             | ed                                  |                        |                  |                  |                 |  |  |

| bit 10          | FLTREN: Dig                                                   | ital Filter Enabl                                      | e bit                               |                        |                  |                  |                 |  |  |

|                 | 1 = Digital filt<br>0 = Digital filt                          |                                                        |                                     |                        |                  |                  |                 |  |  |

| bit 9           | FCLKSEL: D                                                    | igital Filter and                                      | Pulse Stretche                      | r Clock Select         | bit              |                  |                 |  |  |

|                 | •                                                             | er and pulse str<br>er and pulse str                   | •                                   |                        |                  |                  |                 |  |  |

| bit 8           | DACOE: DAG                                                    | Cx Output Enab                                         | le bit                              |                        |                  |                  |                 |  |  |

|                 |                                                               | alog voltage is o<br>alog voltage is r                 |                                     |                        |                  |                  |                 |  |  |

| bit 7-6         | INSEL<1:0>:                                                   | INSEL<1:0>: Input Source Select for Comparator bits    |                                     |                        |                  |                  |                 |  |  |

|                 | 11 = Selects<br>10 = Selects<br>01 = Selects<br>00 = Selects  |                                                        | in<br>in<br>in<br>in                |                        |                  |                  |                 |  |  |

|                 | 01 = Selects<br>00 = Selects                                  | PGA2 output<br>PGA1 output                             |                                     |                        | an china tina    | The software     |                 |  |  |

#### REGISTER 24-1: CMPxCON: COMPARATOR x CONTROL REGISTER

**Note 1:** DACOUTx can be associated only with a single comparator at any given time. The software must ensure that multiple comparators do not enable the DACx output by setting their respective DACOE bit.

### 25.2 PGA Resources

Many useful resources are provided on the main product page of the Microchip website for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 25.2.1 KEY RESOURCES

- "Programmable Gain Amplifier (PGA)" (DS70005146) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 25-1: PGAxCON: PGAx CONTROL REGISTER

| R/W-0                              | R/W-0        | R/W-0                                           | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|------------------------------------|--------------|-------------------------------------------------|-----------------|------------------|------------------|-----------------|--------|--|--|--|--|

| PGAEN                              | PGAOEN       | SELPI2                                          | SELPI1          | SELPI0           | SELNI2           | SELNI1          | SELNI0 |  |  |  |  |

| bit 15                             |              |                                                 |                 |                  |                  | <u>.</u>        | bit 8  |  |  |  |  |

|                                    |              |                                                 |                 |                  |                  |                 |        |  |  |  |  |

| U-0                                | U-0          | U-0                                             | U-0             | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| _                                  | _            | _                                               | _               | _                | GAIN2            | GAIN1           | GAIN0  |  |  |  |  |

| bit 7                              |              | •                                               |                 |                  |                  | -               | bit C  |  |  |  |  |

|                                    |              |                                                 |                 |                  |                  |                 |        |  |  |  |  |

| Legend:                            |              |                                                 |                 |                  |                  |                 |        |  |  |  |  |

| R = Readable bit W = Writable bit  |              |                                                 |                 | U = Unimpler     | mented bit, read | 1 as '0'        |        |  |  |  |  |

| -n = Value at POR '1' = Bit is set |              |                                                 | t               | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |  |  |  |

|                                    |              |                                                 |                 |                  |                  |                 |        |  |  |  |  |

| bit 15                             | PGAEN: PGA   | Ax Enable bit                                   |                 |                  |                  |                 |        |  |  |  |  |

|                                    | 1 = PGAx mo  | = PGAx module is enabled                        |                 |                  |                  |                 |        |  |  |  |  |

|                                    | 0 = PGAx mo  | odule is disable                                | d (reduces po   | wer consumpt     | ion)             |                 |        |  |  |  |  |

| bit 14                             | PGAOEN: PO   | GAx Output En                                   | able bit        |                  |                  |                 |        |  |  |  |  |

|                                    | 1 = PGAx out | 1 = PGAx output is connected to the DACOUTx pin |                 |                  |                  |                 |        |  |  |  |  |

|                                    | 0 = PGAx out | tput is not conr                                | nected to the I | DACOUTx pin      |                  |                 |        |  |  |  |  |

| bit 13-11                          | SELPI<2:0>:  | PGAx Positive                                   | e Input Selecti | on bits          |                  |                 |        |  |  |  |  |

|                                    | 111 = Reserv | ved                                             |                 |                  |                  |                 |        |  |  |  |  |

|                                    | 110 = Reserv | 110 = Reserved                                  |                 |                  |                  |                 |        |  |  |  |  |

|                                    | 101 = Reserv | 101 = Reserved                                  |                 |                  |                  |                 |        |  |  |  |  |

|                                    | 100 = Reserv | ved                                             |                 |                  |                  |                 |        |  |  |  |  |

|                                    | 011 = PGAxF  | -                                               |                 |                  |                  |                 |        |  |  |  |  |

|                                    | 010 = PGAxF  | >3                                              |                 |                  |                  |                 |        |  |  |  |  |

|                                    |              | 22                                              |                 |                  |                  |                 |        |  |  |  |  |

001 = PGAxP2 000 = PGAxP1

### bit 10-8 **SELNI<2:0>:** PGAx Negative Input Selection bits

- 111 = Reserved 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = Ground (Single-Ended mode)

- 010 = PGAxN3

- 001 = PGAxN2

- 000 = Ground (Single-Ended mode)

- bit 7-3 Unimplemented: Read as '0'

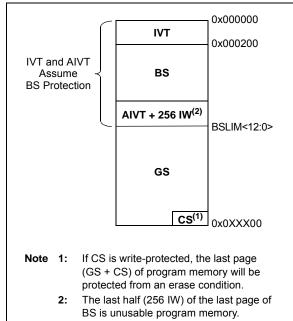

The different device security segments are shown in Figure 27-3. Here, all three segments are shown but are not required. If only basic code protection is required, then GS can be enabled independently or combined with CS, if desired.

#### FIGURE 27-3: SECURITY SEGMENTS EXAMPLE FOR dsPIC33EPXXXGS70X/80X DEVICES

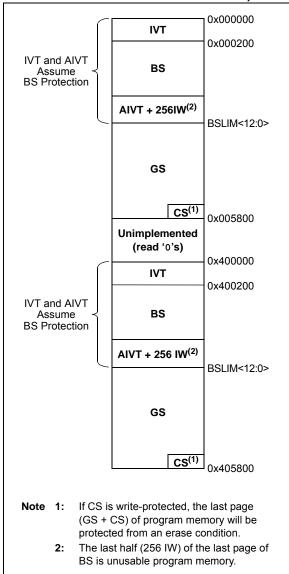

dsPIC33EPXXXGS70X/80X family devices can be operated in Dual Partition mode, where security is required for each partition. When operating in Dual Partition mode, the Active and Inactive Partitions both contain unique copies of the Reset vector, Interrupt Vector Tables (IVT and AIVT, if enabled) and the Flash Configuration Words. Both partitions have the three security segments described previously. Code may not be executed from the Inactive Partition, but it may be programmed by, and read from, the Active Partition, subject to defined code protection. Figure 27-4 and Figure 27-5 show the different security segments for devices operating in Dual Partition mode.

The device may also operate in a Protected Dual Partition mode or in Privileged Dual Partition mode. In Protected Dual Partition mode, Partition 1 is permanently erase/write-protected. This implementation allows for a "Factory Default" mode, which provides a fail-safe backup image to be stored in Partition 1. For example, a fail-safe bootloader can be placed in Partition 1, along with a fail-safe backup code image, which can be used or rewritten into Partition 2.

Privileged Dual Partition mode performs the same function as Protected Dual Partition mode, except additional constraints are applied in an effort to prevent code in the Boot Segment and General Segment from being used against each other.

FIGURE 27-4:

SECURITY SEGMENTS EXAMPLE FOR dsPIC33EP64GS70X/80X DEVICES (DUAL PARTITION MODES)

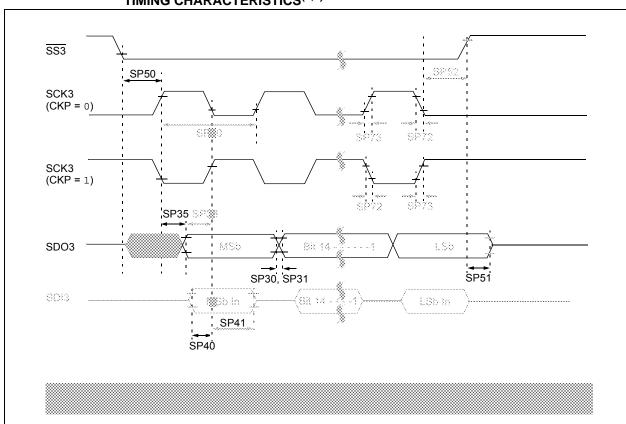

#### FIGURE 30-25: SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS<sup>(1,2)</sup>

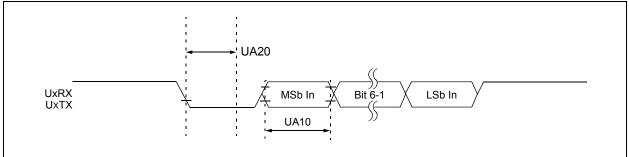

#### FIGURE 30-32: UARTX MODULE I/O TIMING CHARACTERISTICS

#### TABLE 30-50: UARTX MODULE I/O TIMING REQUIREMENTS

|              |         |                                                   | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                     |      |       |            |  |

|--------------|---------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|------------|--|

| Param<br>No. | Symbol  | Characteristic <sup>(1)</sup>                     | Min.                                                                                                                                | Тур. <sup>(2)</sup> | Max. | Units | Conditions |  |

| UA10         | TUABAUD | UARTx Baud Time                                   | 66.67                                                                                                                               |                     | _    | ns    |            |  |

| UA11         | FBAUD   | UARTx Baud Frequency                              | —                                                                                                                                   | _                   | 15   | Mbps  |            |  |

| UA20         | TCWF    | Start Bit Pulse Width to Trigger<br>UARTx Wake-up | 500                                                                                                                                 | —                   | _    | ns    |            |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 30-51: ANALOG CURRENT SPECIFICATIONS

| AC CHARACTERISTICS |        |                                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                     |      |       |                                                                                                                    |  |

|--------------------|--------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>         | Min.                                                                                                                                | Тур. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                         |  |

| AVD01              | IDD    | Analog Modules Current<br>Consumption | _                                                                                                                                   | 9                   |      |       | Characterized data with the<br>following modules enabled:<br>APLL, 5 ADC Cores, 2 PGAs<br>and 4 Analog Comparators |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.