Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                          |

| Number of I/O              | 51                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs706-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

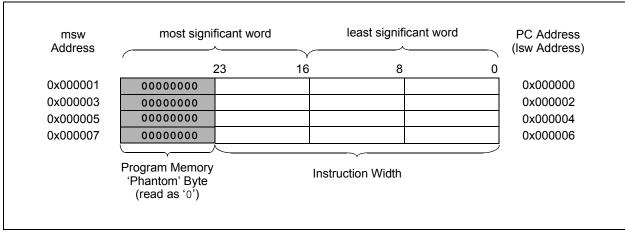

#### 4.2.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-5).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

#### 4.2.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGS70X/80X family devices reserve the addresses between 0x000000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1 "Interrupt Vector Table"**.

#### FIGURE 4-5: PROGRAM MEMORY ORGANIZATION

| TABLE 7-1: | INTERRUPT VECTOR DETAILS ( | (CONTINUED) | ) |

|------------|----------------------------|-------------|---|

|            |                            |             |   |

| Interrupt Source               | Vector | IRQ   | IVT Address       | In                  | terrupt Bit Lo      | ocation                     |

|--------------------------------|--------|-------|-------------------|---------------------|---------------------|-----------------------------|

| interrupt Source               | #      | #     | IVI Address       | Flag                | Enable              | Priority                    |

| T4 – Timer4                    | 35     | 27    | 0x00004A          | IFS1<11><br>T4IF    | IEC1<11><br>T4IE    | IPC6<14:12><br>T4IP<2:0>    |

| T5 – Timer5                    | 36     | 28    | 0x00004C          | IFS1<12><br>T5IF    | IEC1<12><br>T5IE    | IPC7<2:0><br>T5IP<2:0>      |

| INT2 – External Interrupt 2    | 37     | 29    | 0x00004E          | IFS1<13><br>INT2IF  | IEC1<13><br>INT2IE  | IPC7<6:4><br>INT2IP<2:0>    |

| U2RX – UART2 Receiver          | 38     | 30    | 0x000050          | IFS1<14><br>U2RXIF  | IEC1<14><br>U2RXIE  | IPC7<10:8><br>U2RXIP<2:0>   |

| U2TX – UART2 Transmitter       | 39     | 31    | 0x000052          | IFS1<15><br>U2TXIF  | IEC1<15><br>U2TXIE  | IPC7<14:12><br>U2TXIP<2:0>  |

| SPI2TX – SPI2 Transfer Done    | 40     | 32    | 0x000054          | IFS2<0><br>SPI2TXIF | IEC2<0><br>SPI2TXIE | IPC8<2:0><br>SPI2TXIP<2:0>  |

| SPI2RX – SPI2 Receive Done     | 41     | 33    | 0x000056          | IFS2<1><br>SPI2RXIF | IEC2<1><br>SPI2RXIE | IPC8<6:4><br>SPI2RXIP<2:0>  |

| C1RX – CAN1 RX Data Ready      | 42     | 34    | 0x000058          | IFS2<2><br>C1RXIF   | IEC2<2><br>C1RXIE   | IPC8<10:8><br>C1RXIP<2:0>   |

| C1 – CAN1 Combined Error       | 43     | 35    | 0x000059          | IFS2<3><br>C1IF     | IEC2<3><br>C1IE     | IPC8<14:12><br>C1IP<2:0>    |

| DMA3 – DMA Channel 3           | 44     | 36    | 0x00005A          | IFS2<4><br>DMA3IF   | IEC2<4><br>DMA3IE   | IPC9<2:0><br>DMA3IP<2:0>    |

| IC3 – Input Capture 3          | 45     | 37    | 0x00005E          | IFS2<5><br>IC3IF    | IEC2<5><br>IC3IE    | IPC9<6:4><br>IC3IP<2:0>     |

| IC4 – Input Capture 4          | 46     | 38    | 0x000060          | IFS2<6><br>IC4IF    | IEC2<6><br>IC4IE    | IPC9<10:8><br>IC4IP<2:0>    |

| Reserved                       | 47-56  | 39-48 | 0x000062-0x000074 | _                   | _                   | _                           |

| SI2C2 – I2C2 Slave Event       | 57     | 49    | 0x000076          | IFS3<1><br>SI2C2IF  | IEC3<1><br>SI2C2IE  | IPC12<6:4><br>SI2C2IP<2:0>  |

| MI2C2 – I2C2 Master Event      | 58     | 50    | 0x000078          | IFS3<2><br>MI2C2IF  | IEC3<2><br>MI2C2IE  | IPC12<10:8><br>MI2C2IP<2:0> |

| Reserved                       | 59-61  | 51-53 | 0x00007A-0x00007E | _                   | —                   | _                           |

| INT4 – External Interrupt 4    | 62     | 54    | 0x000080          | IFS3<6><br>INT4IF   | IEC3<6><br>INT4IE   | IPC13<10:8><br>INT4IP<2:0>  |

| C2RX – CAN2 RX Data Ready      | 63     | 55    | 0x000082          | IFS3<7><br>C2RXIF   | IEC3<7><br>C2RXIE   | IPC13<14:12><br>C2RXIP<2:0> |

| C2 – CAN 2 Combined Error      | 64     | 56    | 0x000083          | IFS3<8><br>C2IF     | IEC3<8><br>C2IE     | IPC14<2:0><br>C2IP<2:0>     |

| PSEM – PWM Special Event Match | 65     | 57    | 0x000086          | IFS3<9><br>PSEMIF   | IEC3<9><br>PSEMIE   | IPC14<6:4><br>PSEMIP<2:0>   |

| Reserved                       | 66-72  | 58-64 | 0x000088-0x000094 | _                   | _                   | _                           |

| U1E – UART1 Error Interrupt    | 73     | 65    | 0x000096          | IFS4<1><br>U1EIF    | IEC4<1><br>U1EIE    | IPC16<6:4><br>U1EIP<2:0>    |

| U2E – UART2 Error Interrupt    | 74     | 66    | 0x000098          | IFS4<2><br>U2EIF    | IEC4<2><br>U2EIE    | IPC16<10:8><br>U2EIP<2:0>   |

| Reserved                       | 75-77  | 67-69 | 0x00009A-0x0000A2 | _                   | _                   | _                           |

| C1TX – CAN1 TX Data Request    | 78     | 70    | 0x0000A0          | IFS4<6><br>C1TXIF   | IEC4<6><br>C1TXIE   | IPC17<10:8><br>C1TXIP<2:0>  |

| C2TX – CAN2 TX Data Request    | 79     | 71    | 0x0000A           | IFS4<7><br>C2TXIF   | IEC4<7><br>C2TXIE   | IPC17<14:12><br>C2TXIP<2:0> |

| Reserved                       | 80     | 72    | 0x0000A4          | _                   | _                   | _                           |

#### REGISTER 8-3: DMAxSTAH: DMA CHANNEL x START ADDRESS REGISTER A (HIGH)

| U-0          | U-0   | U-0            | U-0   | U-0         | U-0              | U-0    | U-0   |

|--------------|-------|----------------|-------|-------------|------------------|--------|-------|

| —            | _     | —              | _     | —           | —                | —      |       |

| bit 15       |       |                |       | ·           |                  |        | bit 8 |

|              |       |                |       |             |                  |        |       |

| R/W-0        | R/W-0 | R/W-0          | R/W-0 | R/W-0       | R/W-0            | R/W-0  | R/W-0 |

|              |       |                | STA<  | 23:16>      |                  |        |       |

| bit 7        |       |                |       |             |                  |        | bit 0 |

|              |       |                |       |             |                  |        |       |

| Legend:      |       |                |       |             |                  |        |       |

| R = Readable | bit   | W = Writable b | it    | U = Unimple | mented bit, read | as '0' |       |

$\kappa$  =  $\kappa$  eadable bitV = VVritable bit<math>U = Unimplemented bit, read as '0'<math>-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STA<23:16>: DMA Primary Start Address bits (source or destination)

#### REGISTER 8-4: DMAxSTAL: DMA CHANNEL x START ADDRESS REGISTER A (LOW)

| R/W-0                                                                | R/W-0   | R/W-0 | R/W-0 | R/W-0           | R/W-0 | R/W-0   | R/W-0   |

|----------------------------------------------------------------------|---------|-------|-------|-----------------|-------|---------|---------|

| 10.00-0                                                              | 10,00-0 |       |       |                 |       | 10.00-0 | 10.00-0 |

|                                                                      |         |       | STA   | <15:8>          |       |         |         |

| bit 15                                                               |         |       |       |                 |       |         | bit 8   |

|                                                                      |         |       |       |                 |       |         |         |

| R/W-0                                                                | R/W-0   | R/W-0 | R/W-0 | R/W-0           | R/W-0 | R/W-0   | R/W-0   |

|                                                                      |         |       | STA   | <7:0>           |       |         |         |

| bit 7                                                                |         |       |       |                 |       |         | bit 0   |

| Legend:                                                              |         |       |       |                 |       |         |         |

| -                                                                    |         |       |       |                 |       |         |         |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |         |       |       |                 |       |         |         |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is u |         |       |       | x = Bit is unkr | nown  |         |         |

bit 15-0 STA<15:0>: DMA Primary Start Address bits (source or destination)

#### REGISTER 11-31: RPINR45: PERIPHERAL PIN SELECT INPUT REGISTER 45

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| CLCINAR7 | CLCINAR6 | CLCINAR5 | CLCINAR4 | CLCINAR3 | CLCINAR2 | CLCINAR1 | CLCINAR0 |

| bit 15   | •        |          |          |          |          |          | bit 8    |

|          |          |          |          |          |          |          |          |

| U-0      |

| _        | _        | _        | _        |          | _        | _        | _        |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8CLCINAR<7:0>: Assign CLC Input A (CLCINA) to the Corresponding RPn Pin bits<br/>See Table 11-11 which contains a list of remappable inputs for the index value.bit 7-0Unimplemented: Read as '0'

#### REGISTER 11-32: RPINR46: PERIPHERAL PIN SELECT INPUT REGISTER 46

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     | •   |     |     | bit 8 |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| CLCINBR7 | CLCINBR6 | CLCINBR5 | CLCINBR4 | CLCINBR3 | CLCINBR2 | CLCINBR1 | CLCINBR0 |

| bit 7    | •        |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **CLCINBR<7:0>:** Assign CLC Input B (CLCINB) to the Corresponding RPn Pin bits See Table 11-11 which contains a list of remappable inputs for the index value.

### 15.2 Output Compare Control Registers

#### REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

|                 | U-0         | OCSIDL              | OCTSEL2           | OCTSEL1           | OCTSEL0           |                 |        |

|-----------------|-------------|---------------------|-------------------|-------------------|-------------------|-----------------|--------|

| R/W-0<br>ENFLTA | U-0         |                     |                   |                   | OCISELU           |                 |        |

| ENFLTA          | U-0         |                     |                   |                   |                   |                 | bit    |

| ENFLTA          | 00          | U-0                 | R/W-0, HSC        | R/W-0             | R/W-0             | R/W-0           | R/W-0  |

| bit 7           | _           |                     | OCFLTA            | TRIGMODE          | OCM2              | OCM1            | OCM0   |

|                 |             |                     |                   |                   |                   |                 | bit    |

| Legend:         |             | USC - Hardwa        | are Settable/Cle  | arablo bit        |                   |                 |        |

| R = Readab      | lo hit      | W = Writable b      |                   |                   | ented bit, read a | ae 'O'          |        |

| -n = Value a    |             | '1' = Bit is set    | п                 | '0' = Bit is clea |                   | x = Bit is unkr |        |

|                 |             |                     |                   |                   |                   |                 | 101111 |

| bit 15-14       | Unimpleme   | ented: Read as '0   | ,                 |                   |                   |                 |        |

| bit 13          | OCSIDL: 0   | utput Compare x     | Stop in Idle Mo   | de Control bit    |                   |                 |        |

|                 | 1 = Output  | Compare x halts     | in CPU Idle mo    | de                |                   |                 |        |

|                 | 0 = Output  | Compare x contir    | ues to operate    | in CPU Idle mo    | de                |                 |        |

| bit 12-10       | OCTSEL<2    | :0>: Output Com     | oare x Clock Se   | lect bits         |                   |                 |        |

|                 | 111 = Perip | heral clock (FP)    |                   |                   |                   |                 |        |

|                 | 110 = Rese  |                     |                   |                   |                   |                 |        |

|                 | 101 = Rese  |                     | was of the OCy    |                   |                   |                 |        |

|                 |             | K is the clock sou  |                   |                   | Ironous clock is  | supported)      |        |

|                 |             | K is the clock sou  |                   |                   |                   |                 |        |

|                 |             | K is the clock sou  |                   |                   |                   |                 |        |

|                 | 000 = T2CL  | K is the clock sou  | urce of the OCx   |                   |                   |                 |        |

| bit 9-8         | Unimpleme   | ented: Read as '0   | ,                 |                   |                   |                 |        |

| bit 7           | ENFLTA: Fa  | ault A Input Enabl  | e bit             |                   |                   |                 |        |

|                 | 1 = Output  | Compare Fault A     | input (OCFA) is   | s enabled         |                   |                 |        |

|                 | 0 = Output  | Compare Fault A     | input (OCFA) is   | s disabled        |                   |                 |        |

| bit 6-5         | Unimpleme   | ented: Read as '0   | ,                 |                   |                   |                 |        |

| bit 4           | OCFLTA: P   | WM Fault A Cond     | lition Status bit |                   |                   |                 |        |

|                 |             | ault A condition c  |                   |                   |                   |                 |        |

|                 | 0 = No PW   | M Fault A condition | on on the OCFA    | pin has occurre   | ed                |                 |        |

| bit 3           |             | : Trigger Status N  |                   |                   |                   |                 |        |

|                 |             | TAT (OCxCON2<       | ,                 | /hen OCxRS = (    | OCxTMR or in s    | oftware         |        |

|                 | 0 = TRIGS   | TAT is cleared on   | y by software     |                   |                   |                 |        |

**Note 1:** OCxR and OCxRS are double-buffered in PWM mode only.

#### 16.0 HIGH-SPEED PWM

Note: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM Module" (DS70000323) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

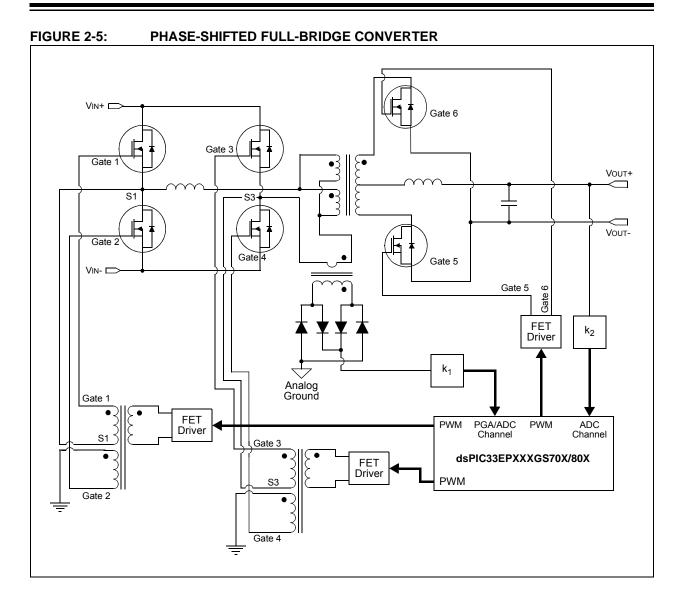

The high-speed PWM on dsPIC33EPXXXGS70X/80X devices supports a wide variety of PWM modes and output formats. This PWM module is ideal for power conversion applications, such as:

- AC/DC Converters

- DC/DC Converters

- Power Factor Correction

- Uninterruptible Power Supply (UPS)

- Inverters

- Battery Chargers

- · Digital Lighting

#### 16.1 Features Overview

The high-speed PWM module incorporates the following features:

- Eight PWMx Generators with Two Outputs per Generator

- · Two Master Time Base modules

- Individual Time Base and Duty Cycle for each

PWM Output

- Duty Cycle, Dead Time, Phase Shift and a Frequency Resolution of 1.04 ns

- Independent Fault and Current-Limit Inputs

- · Redundant Output

- True Independent Output

- Center-Aligned PWM mode

- · Output override control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Dual Trigger from PWMx to Analog-to-Digital Converter (ADC)

- PWMxL and PWMxH Output Pin Swapping

- Independent PWMx Frequency, Duty Cycle and Phase-Shift Changes

- Enhanced Leading-Edge Blanking (LEB) Functionality

- PWM Capture Functionality

**Note:** Duty cycle, dead time, phase shift and frequency resolution is 8.32 ns in Center-Aligned PWM mode.

Figure 16-1 conceptualizes the PWM module in a simplified block diagram. Figure 16-2 illustrates how the module hardware is partitioned for each PWMx output pair for the Complementary PWM mode.

The PWM module contains eight PWM generators. The module has up to 16 PWMx output pins: PWM1H/ PWM1L through PWM8H/PWM8L. For complementary outputs, these 16 I/O pins are grouped into high/low pairs. PWM1 through PWM6 can be used to trigger an ADC conversion.

#### 16.2 Feature Description

The PWM module is designed for applications that require:

- High resolution at high PWM frequencies

- The ability to drive Standard, Edge-Aligned, Center-Aligned Complementary mode and Push-Pull mode outputs

- The ability to create multiphase PWM outputs

Two common, medium power converter topologies are push-pull and half-bridge. These designs require the PWM output signal to be switched between alternate pins, as provided by the Push-Pull PWM mode.

Phase-shifted PWM describes the situation where each PWM generator provides outputs, but the phase relationship between the generator outputs is specifiable and changeable.

Multiphase PWM is often used to improve DC/DC Converter load transient response, and reduce the size of output filter capacitors and inductors. Multiple DC/DC Converters are often operated in parallel, but phase shifted in time. A single PWM output, operating at 250 kHz, has a period of 4  $\mu$ s but an array of four PWM channels, staggered by 1  $\mu$ s each, yields an effective switching frequency of 1 MHz. Multiphase PWM applications typically use a fixed-phase relationship.

Variable phase PWM is useful in Zero Voltage Transition (ZVT) power converters. Here, the PWM duty cycle is always 50% and the power flow is controlled by varying the relative phase shift between the two PWM generators.

#### **REGISTER 16-15:** PHASEX: PWMx PRIMARY PHASE-SHIFT REGISTER (x = 1 to 8)<sup>(1,2)</sup>

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|--------------|-------|------------------|-------|--------------|------------------|----------|-------|

|              |       |                  | PHASE | Ex<15:8>     |                  |          |       |

| bit 15       |       |                  |       |              |                  |          | bit 8 |

|              |       |                  |       |              |                  |          |       |

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|              |       |                  | PHAS  | Ex<7:0>      |                  |          |       |

| bit 7        |       |                  |       |              |                  |          | bit 0 |

|              |       |                  |       |              |                  |          |       |

| Legend:      |       |                  |       |              |                  |          |       |

| R = Readable | bit   | W = Writable bit |       | U = Unimplen | nented bit, read | l as '0' |       |

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWMx Generator bits

- **Note 1:** If PWMCONx<9> = 0, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Phase-shift value for PWMxH only

- When the PHASEx/SPHASEx registers provide the phase shift with respect to the master time base; therefore, the valid range is 0x0000 through period

- **2:** If PWMCONx<9> = 1, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Independent time base period value for PWMxH only

- When the PHASEx/SPHASEx registers provide the local period, the valid range is 0x0000-0xFFF8

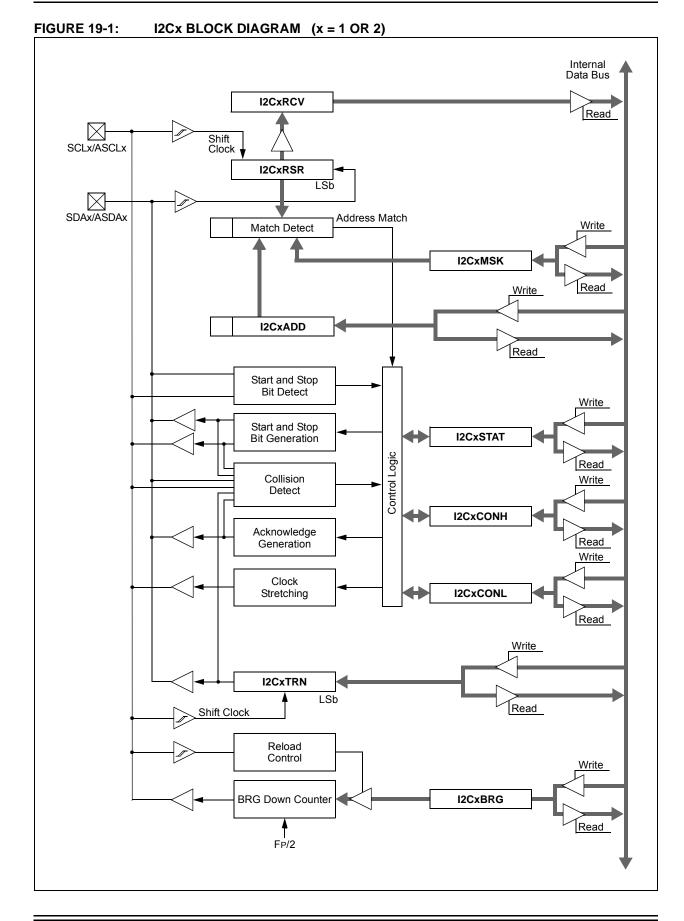

### 19.2 I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCONL: I2Cx CONTROL REGISTER LOW

| R/W-0  | U-0 | R/W-0   | R/W-1, HC | R/W-0  | R/W-0 | R/W-0  | R/W-0 |

|--------|-----|---------|-----------|--------|-------|--------|-------|

| I2CEN  | —   | I2CSIDL | SCLREL    | STRICT | A10M  | DISSLW | SMEN  |

| bit 15 |     |         |           |        |       |        | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0, HC |

|-------|-------|-------|-----------|-----------|-----------|-----------|-----------|

| GCEN  | STREN | ACKDT | ACKEN     | RCEN      | PEN       | RSEN      | SEN       |

| bit 7 |       |       |           |           |           |           | bit 0     |

| Legend:           | HC = Hardware Clearable bit |                             |                    |  |  |

|-------------------|-----------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared        | x = Bit is unknown |  |  |

| bit 15 | I2CEN: I2Cx Enable bit                                                                                                                                                                                                                                                                                                              |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | <ul> <li>1 = Enables the I2Cx module and configures the SDAx and SCLx pins as serial port pins</li> <li>0 = Disables the I2Cx module; all I<sup>2</sup>C pins are controlled by port functions</li> </ul>                                                                                                                           |

| bit 14 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                          |

| bit 13 | I2CSIDL: I2Cx Stop in Idle Mode bit                                                                                                                                                                                                                                                                                                 |

|        | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                                                                                                                             |

| bit 12 | SCLREL: SCLx Release Control bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                                                                                                                         |

|        | <ul> <li>1 = Releases SCLx clock</li> <li>0 = Holds SCLx clock low (clock stretch)</li> </ul>                                                                                                                                                                                                                                       |

|        | If STREN = 1:<br>Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware is clear<br>at the beginning of every slave data byte transmission. Hardware is clear at the end of every slave<br>address byte reception. Hardware is clear at the end of every slave data byte reception. |

|        | If STREN = 0:<br>Bit is R/S (i.e., software can only write '1' to release clock). Hardware is clear at the beginning of every slave data byte transmission. Hardware is clear at the end of every slave address byte reception.                                                                                                     |

| bit 11 | STRICT: Strict I2Cx Reserved Address Enable bit                                                                                                                                                                                                                                                                                     |

|        | <ul> <li>1 = <u>Strict Reserved Addressing is Enabled:</u><br/>In Slave mode, the device will NACK any reserved address. In Master mode, the device is allowed<br/>to generate addresses within the reserved address space.</li> </ul>                                                                                              |

|        | <ul> <li>0 = <u>Reserved Addressing is Acknowledged:</u><br/>In Slave mode, the device will ACK any reserved address. In Master mode, the device should not<br/>address a slave device with a reserved address.</li> </ul>                                                                                                          |

| bit 10 | A10M: 10-Bit Slave Address bit                                                                                                                                                                                                                                                                                                      |

|        | <ul><li>1 = I2CxADD is a 10-bit slave address</li><li>0 = I2CxADD is a 7-bit slave address</li></ul>                                                                                                                                                                                                                                |

| bit 9  | DISSLW: Disable Slew Rate Control bit                                                                                                                                                                                                                                                                                               |

|        | <ul><li>1 = Slew rate control is disabled</li><li>0 = Slew rate control is enabled</li></ul>                                                                                                                                                                                                                                        |

| bit 8  | SMEN: SMBus Input Levels bit                                                                                                                                                                                                                                                                                                        |

|        | <ul> <li>1 = Enables I/O pin thresholds compliant with SMBus specification</li> <li>0 = Disables SMBus input thresholds</li> </ul>                                                                                                                                                                                                  |

| bit 7  | GCEN: General Call Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                                                                                                                            |

|        | <ul> <li>1 = Enables interrupt when a general call address is received in I2CxRSR (module is enabled for reception)</li> <li>0 = General call address is disabled</li> </ul>                                                                                                                                                        |

|        |                                                                                                                                                                                                                                                                                                                                     |

#### 20.1 UART Helpful Tips

- In multi-node, direct connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pullup or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the UxRX pin.

- b) If URXINV = 1, use a pull-down resistor on the UxRX pin.

- 2. The first character received on a wake-up from Sleep mode, caused by activity on the UxRX pin of the UARTx module, will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 20.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 20.2.1 KEY RESOURCES

- "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

REGISTER 22-3: ADCON2L: ADC CONTROL REGISTER 2 LOW

| R/W-0            | R/W-0                                                                                                                       | r-0                                                                                                                        | R/W-0                                                                                                                | r-0                                                                                                | R/W-0                                                                                                    | R/W-0                                                                                                                                                                | R/W-0                                                                                                                             |

|------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| REFCIE           | REFERCIE                                                                                                                    | —                                                                                                                          | EIEN                                                                                                                 | —                                                                                                  | SHREISEL2(1)                                                                                             | SHREISEL1 <sup>(1)</sup>                                                                                                                                             | SHREISEL0(1)                                                                                                                      |

| bit 15           |                                                                                                                             |                                                                                                                            |                                                                                                                      |                                                                                                    |                                                                                                          |                                                                                                                                                                      | bit 8                                                                                                                             |

|                  |                                                                                                                             |                                                                                                                            |                                                                                                                      |                                                                                                    |                                                                                                          |                                                                                                                                                                      |                                                                                                                                   |

| U-0              | R/W-0                                                                                                                       | R/W-0                                                                                                                      | R/W-0                                                                                                                | R/W-0                                                                                              | R/W-0                                                                                                    | R/W-0                                                                                                                                                                | R/W-0                                                                                                                             |

| _                | SHRADCS6                                                                                                                    | SHRADCS5                                                                                                                   | SHRADCS4                                                                                                             | SHRADCS3                                                                                           | SHRADCS2                                                                                                 | SHRADCS1                                                                                                                                                             | SHRADCS0                                                                                                                          |

| bit 7            |                                                                                                                             |                                                                                                                            |                                                                                                                      |                                                                                                    |                                                                                                          |                                                                                                                                                                      | bit 0                                                                                                                             |

|                  |                                                                                                                             |                                                                                                                            |                                                                                                                      |                                                                                                    |                                                                                                          |                                                                                                                                                                      |                                                                                                                                   |

| Legend:          |                                                                                                                             | r = Reserved                                                                                                               | bit                                                                                                                  |                                                                                                    |                                                                                                          |                                                                                                                                                                      |                                                                                                                                   |

| R = Reada        | able bit                                                                                                                    | W = Writable                                                                                                               | bit                                                                                                                  | U = Unimpler                                                                                       | mented bit, read                                                                                         | as '0'                                                                                                                                                               |                                                                                                                                   |

| -n = Value       | at POR                                                                                                                      | '1' = Bit is set                                                                                                           |                                                                                                                      | '0' = Bit is cle                                                                                   | ared                                                                                                     | x = Bit is unkno                                                                                                                                                     | wn                                                                                                                                |

| bit 15<br>bit 14 | 1 = Common<br>0 = Common<br><b>REFERCIE:</b> E<br>1 = Common                                                                | interrupt will b<br>interrupt is dis<br>3and Gap or R<br>interrupt will b                                                  | e generated w<br>abled for the k<br>eference Volta<br>e generated w                                                  | when the band<br>band gap read<br>age Error Com<br>when a band ga                                  | imon Interrupt E                                                                                         | e ready<br>Enable bit<br>voltage error is o                                                                                                                          | detected                                                                                                                          |

| bit 13           | Reserved: M                                                                                                                 | •                                                                                                                          |                                                                                                                      | 5-1                                                                                                |                                                                                                          | <b>,</b>                                                                                                                                                             |                                                                                                                                   |

| bit 12           | EIEN: Early I                                                                                                               | nterrupts Enab                                                                                                             | le bit                                                                                                               |                                                                                                    |                                                                                                          |                                                                                                                                                                      |                                                                                                                                   |

|                  | 1 = The early                                                                                                               | interrupt featu                                                                                                            | re is enabled                                                                                                        | •                                                                                                  |                                                                                                          | s (when the EIS <sup>-</sup><br>hen the ANxRD`                                                                                                                       | • •                                                                                                                               |

| bit 11           | Reserved: M                                                                                                                 | aintain as '0'                                                                                                             |                                                                                                                      |                                                                                                    |                                                                                                          |                                                                                                                                                                      |                                                                                                                                   |

| bit 10-8         | SHREISEL<2                                                                                                                  | 2:0>: Shared C                                                                                                             | ore Early Inte                                                                                                       | rrupt Time Sel                                                                                     | ection bits <sup>(1)</sup>                                                                               |                                                                                                                                                                      |                                                                                                                                   |

|                  | 110 = Early ir<br>101 = Early ir<br>100 = Early ir<br>011 = Early ir<br>010 = Early ir<br>001 = Early ir                    | nterrupt is set a<br>nterrupt is set a | and interrupt is<br>and interrupt is<br>and interrupt is<br>and interrupt is<br>and interrupt is<br>and interrupt is | s generated 7<br>s generated 6<br>s generated 5<br>s generated 4<br>s generated 3<br>s generated 2 | TADCORE Clocks<br>TADCORE Clocks<br>TADCORE Clocks<br>TADCORE Clocks<br>TADCORE Clocks<br>TADCORE Clocks | prior to when the<br>prior to when the | e data is ready<br>e data is ready |

| bit 7            | Unimplemen                                                                                                                  | ted: Read as '                                                                                                             | 0'                                                                                                                   |                                                                                                    |                                                                                                          |                                                                                                                                                                      |                                                                                                                                   |

| bit 6-0          | SHRADCS<6                                                                                                                   | :0>: Shared A                                                                                                              | DC Core Inpu                                                                                                         | t Clock Divide                                                                                     | r bits                                                                                                   |                                                                                                                                                                      |                                                                                                                                   |

|                  | Clock Period)<br>1111111 = 2<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• |                                                                                                                            | ck Periods<br>Periods<br>Periods                                                                                     | RESRC (Source                                                                                      | Clock Periods)                                                                                           | for one shared                                                                                                                                                       | TADCORE (Core                                                                                                                     |

|                  |                                                                                                                             | Source Clock                                                                                                               |                                                                                                                      |                                                                                                    |                                                                                                          |                                                                                                                                                                      |                                                                                                                                   |

|                  | For the 6-bit shar<br>from '100' to '11:                                                                                    | ed ADC core r<br>1', are not valic                                                                                         | esolution (SHF<br>I and should ne                                                                                    | ot be used. Fo                                                                                     | r the 8-bit share                                                                                        |                                                                                                                                                                      | lution                                                                                                                            |

(SHRRES<1:0> = 01), the SHREISEL<2:0> settings, '110' and '111', are not valid and should not be used.

### REGISTER 22-32: ADCMPxENL: ADC DIGITAL COMPARATOR x CHANNEL ENABLE REGISTER LOW (x = 0 or 1)

| bit 15      | R/W/0  | R/W-0 |

|-------------|--------|-------|-------|-------|-------|-------|-------|-------|

| bit 15      |        |       |       |       |       |       |       |       |

|             | bit 15 |       |       |       |       |       |       | bit   |

| CMPEN<15:8> | _      | R/W-0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **CMPEN<15:0>:** Comparator Enable for Corresponding Input Channels bits

0 = Conversion result for corresponding channel is not used by the comparator

### REGISTER 22-33: ADCMPxENH: ADC DIGITAL COMPARATOR x CHANNEL ENABLE REGISTER HIGH (x = 0 or 1)

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------------|-----|-----|-----|-----|-----|-----|-------|

| —            | —   | —   | —   | —   | —   | —   | —     |

| bit 15 bit 8 |     |     |     |     |     |     |       |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|---------|-------|-------|

| —     | —   |       |       | CMPEN | <21:16> |       |       |

| bit 7 |     |       |       |       |         |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0

CMPEN<21:16>: Comparator Enable for Corresponding Input Channels bits

1 = Conversion result for corresponding channel is used by the comparator

0 = Conversion result for corresponding channel is not used by the comparator

<sup>1 =</sup> Conversion result for corresponding channel is used by the comparator

#### BUFFER 21-7: CANx MESSAGE BUFFER WORD 6

| R/W-x                              | R/W-x | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x | R/W-x |

|------------------------------------|-------|-------|------------------|-----------------|-----------------|-------|-------|

|                                    |       |       | Byte             | 7<15:8>         |                 |       |       |

| bit 15                             |       |       |                  |                 |                 |       | bit 8 |

|                                    |       |       |                  |                 |                 |       |       |

| R/W-x                              | R/W-x | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x | R/W-x |

|                                    |       |       | Byte             | 6<7:0>          |                 |       |       |

| bit 7                              |       |       |                  |                 |                 |       | bit 0 |

|                                    |       |       |                  |                 |                 |       |       |

| Legend:                            |       |       |                  |                 |                 |       |       |

| R = Readable bit W = Writable bit  |       | bit   | U = Unimpler     | nented bit, rea | ıd as '0'       |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle | ared            | x = Bit is unkı | nown  |       |

| bit 15-8 | Byte 7<15:8>: CANx Message Byte 7 bits |

|----------|----------------------------------------|

|          |                                        |

bit 7-0 Byte 6<7:0>: CANx Message Byte 6 bits

#### BUFFER 21-8: CANx MESSAGE BUFFER WORD 7

| U-0    | U-0 | U-0 | R/W-x                      | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|----------------------------|-------|-------|-------|-------|

| _      | —   | —   | FILHIT<4:0> <sup>(1)</sup> |       |       |       |       |

| bit 15 |     |     |                            |       |       |       | bit 8 |

| U-0       | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-----------|-----|-----|-----|-----|-----|-----|-------|

| —         | —   | —   | _   | —   | —   | —   | —     |

| bit 7 bit |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-13 | Unimplemented: Read as '0'                                     |

|-----------|----------------------------------------------------------------|

| bit 12-8  | FILHIT<4:0>: Filter Hit Code bits <sup>(1)</sup>               |

|           | Encodes number of filter that resulted in writing this buffer. |

| bit 7-0   | Unimplemented: Read as '0'                                     |

Note 1: Only written by module for receive buffers, unused for transmit buffers.

#### REGISTER 24-1: CMPxCON: COMPARATOR x CONTROL REGISTER (CONTINUED)

| bit 5 | EXTREF: Enable External Reference bit                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = External source provides reference to DACx (maximum DAC voltage is determined by the external<br/>voltage source)</li> </ul>                                 |

|       | 0 = AVDD provides reference to DACx (maximum DAC voltage is AVDD)                                                                                                         |

| bit 4 | HYSPOL: Comparator Hysteresis Polarity Select bit                                                                                                                         |

|       | <ul> <li>1 = Hysteresis is applied to the falling edge of the comparator output</li> <li>0 = Hysteresis is applied to the rising edge of the comparator output</li> </ul> |

| bit 3 | CMPSTAT: Comparator Current State bit                                                                                                                                     |

|       | Reflects the current output state of Comparator x, including the setting of the CMPPOL bit.                                                                               |

| bit 2 | ALTINP: Alternate Input Select bit                                                                                                                                        |

|       | 1 = INSEL<1:0> bits select alternate inputs                                                                                                                               |

|       | 0 = INSEL<1:0> bits select comparator inputs                                                                                                                              |

| bit 1 | CMPPOL: Comparator Output Polarity Control bit                                                                                                                            |

|       | 1 = Output is inverted                                                                                                                                                    |

|       | 0 = Output is non-inverted                                                                                                                                                |

| bit 0 | RANGE: DACx Output Voltage Range Select bit                                                                                                                               |

|       | <ul> <li>1 = AVDD is the maximum DACx output voltage</li> <li>0 = Unimplemented, do not use</li> </ul>                                                                    |

|       |                                                                                                                                                                           |

**Note 1:** DACOUTx can be associated only with a single comparator at any given time. The software must ensure that multiple comparators do not enable the DACx output by setting their respective DACOE bit.

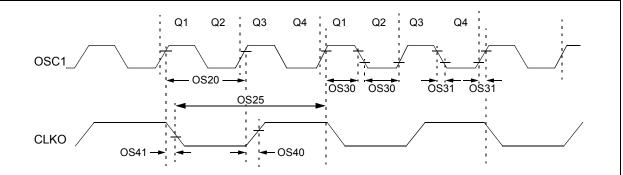

#### FIGURE 30-2: EXTERNAL CLOCK TIMING

| AC CHARACTERISTICS |               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |             |                     |             |            |                               |

|--------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------|-------------|------------|-------------------------------|

| Param<br>No.       | Sym           | Characteristic                                                                                                                                                                                                                                                                          | Min.        | Тур. <sup>(1)</sup> | Max.        | Units      | Conditions                    |

| OS10               | Fin           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                                                                                                                                                                                                      | DC          | —                   | 60          | MHz        | EC                            |

|                    |               | Oscillator Crystal Frequency                                                                                                                                                                                                                                                            | 3.5<br>10   | _                   | 10<br>40    | MHz<br>MHz | XT<br>HS                      |

| OS20               | Tosc          | Tosc = 1/Fosc                                                                                                                                                                                                                                                                           | 8.33        | _                   | DC          | ns         | +125°C                        |

|                    |               | Tosc = 1/Fosc                                                                                                                                                                                                                                                                           | 7.14        | _                   | DC          | ns         | +85°C                         |

| OS25 Tcy           | TCY           | Instruction Cycle Time <sup>(2)</sup>                                                                                                                                                                                                                                                   | 16.67       | _                   | DC          | ns         | +125°C                        |

|                    |               | Instruction Cycle Time <sup>(2)</sup>                                                                                                                                                                                                                                                   | 14.28       | _                   | DC          | ns         | +85°C                         |

| OS30               | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time                                                                                                                                                                                                                                            | 0.45 x Tosc | —                   | 0.55 x Tosc | ns         | EC                            |

| OS31               | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time                                                                                                                                                                                                                                           | -           | —                   | 20          | ns         | EC                            |

| OS40               | TckR          | CLKO Rise Time <sup>(3,4)</sup>                                                                                                                                                                                                                                                         |             | 5.2                 |             | ns         |                               |

| OS41               | TckF          | CLKO Fall Time <sup>(3,4)</sup>                                                                                                                                                                                                                                                         | _           | 5.2                 | _           | ns         |                               |

| OS42               | Gм            | External Oscillator<br>Transconductance <sup>(4)</sup>                                                                                                                                                                                                                                  | -           | 12                  | _           | mA/V       | HS, VDD = 3.3V,<br>TA = +25°C |

|                    |               |                                                                                                                                                                                                                                                                                         | _           | 6                   | _           | mA/V       | XT, VDD = 3.3V,<br>TA = +25°C |

#### TABLE 30-17: EXTERNAL CLOCK TIMING REQUIREMENTS

Note 1: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

2: Instruction cycle period (Tcr) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Minimum" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Maximum" cycle time limit is "DC" (no clock) for all devices.

- **3:** Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: This parameter is characterized but not tested in manufacturing.

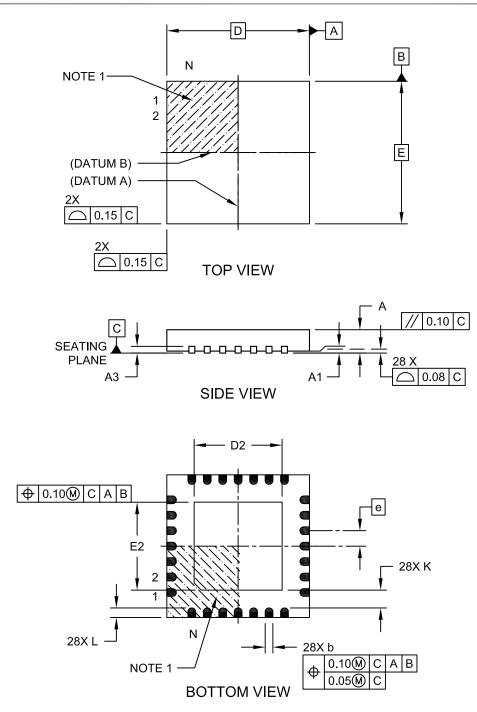

### 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-124C Sheet 1 of 2

### 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units                 |          | MILLIMETERS |      |  |  |

|-------------------------|-----------------------|----------|-------------|------|--|--|

| Dimensio                | Dimension Limits      |          | NOM         | MAX  |  |  |

| Number of Pins          |                       |          | 28          |      |  |  |

| Pitch                   | е                     |          | 0.65 BSC    |      |  |  |

| Overall Height          | А                     | 0.80     | 0.90        | 1.00 |  |  |

| Standoff                | A1                    | 0.00     | 0.02        | 0.05 |  |  |

| Terminal Thickness      | Thickness A3 0.20 REF |          | 0.20 REF    |      |  |  |

| Overall Width           | E                     | 6.00 BSC |             |      |  |  |

| Exposed Pad Width       | E2                    | 3.65     | 3.70        | 4.70 |  |  |

| Overall Length          | D                     | 6.00 BSC |             |      |  |  |

| Exposed Pad Length      | D2                    | 3.65     | 3.70        | 4.70 |  |  |

| Terminal Width          | b                     | 0.23     | 0.30        | 0.35 |  |  |

| Terminal Length         | L                     | 0.30     | 0.40        | 0.50 |  |  |

| Terminal-to-Exposed Pad | К                     | 0.20     | -           | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124C Sheet 2 of 2

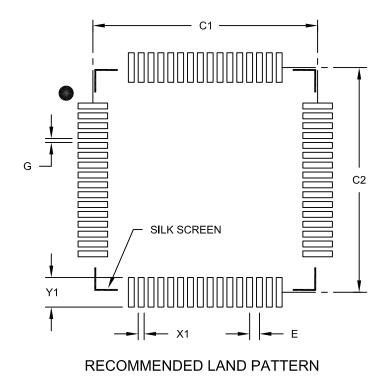

64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Units MILLIMETERS **Dimension Limits** MIN NOM MAX Contact Pitch 0.50 BSC Е Contact Pad Spacing C1 11.40 Contact Pad Spacing C2 11.40 Contact Pad Width (X64) 0.30 X1 Contact Pad Length (X64) Y1 1.50 0.20 **Distance Between Pads** G

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B

| Timing Diagrams                               |     |

|-----------------------------------------------|-----|

| BOR and Master Clear Reset Characteristics    | 391 |

| CANx I/O                                      | 426 |

| External Clock                                | 388 |

| High-Speed PWMx Fault Characteristics         | 397 |

| High-Speed PWMx Module Characteristics        | 397 |

| I/O Characteristics                           | 391 |

| I2Cx Bus Data (Master Mode)                   |     |

| I2Cx Bus Data (Slave Mode)                    | 424 |

| I2Cx Bus Start/Stop Bits (Master Mode)        |     |

| I2Cx Bus Start/Stop Bits (Slave Mode)         | 424 |

| Input Capture x (ICx) Characteristics         |     |

| OCx/PWMx Characteristics                      |     |

| Output Compare x (OCx) Characteristics        |     |

| SPI1, SPI2 and SPI3 Master Mode (Full-Duplex, |     |