Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                               |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                          |

| Number of I/O              | 51                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs706-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.5.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible, regardless of the contents of the Data Space Read Page register. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space in combination with DSRPAG = 0x00. Consequently, DSRPAG is initialized to 0x001 at Reset.

- Note 1: DSRPAG should not be used to access Page 0. An EDS access with DSRPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSRPAG in software has no effect.

The remaining PSV pages are only accessible using the DSRPAG register in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

## 4.5.3 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP), and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack     |

|-------|-----------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the |

|       | hardware.                               |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGS70X/80X devices and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

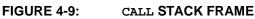

The Software Stack Pointer always points to the first available free word and fills the software stack, working from lower toward higher addresses. Figure 4-9 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes). When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-9. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore, restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

## 4.9 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXXGS70X/80X family architecture uses a 24-bit wide Program Space (PS) and a 16-bit wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGS70X/80X family devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

## TABLE 4-19: PROGRAM SPACE ADDRESS CONSTRUCTION

| Access Type            | Access        | Program Space Address |              |                     |                    |     |  |

|------------------------|---------------|-----------------------|--------------|---------------------|--------------------|-----|--|

|                        | Space         | <23>                  | <22:16>      | <15>                | <14:1>             | <0> |  |

| Instruction Access     | User          | 0                     | 0 PC<22:1> 0 |                     |                    |     |  |

| (Code Execution)       |               | 0xxx xxxx xxxx        |              |                     | xxx xxxx xxxx xxx0 |     |  |

| TBLRD/TBLWT            | User          | TBI                   | _PAG<7:0>    |                     | Data EA<15:0>      |     |  |

| (Byte/Word Read/Write) |               | 0x                    | xxx xxxx     | XXXX XXXX XXXX XXXX |                    |     |  |

|                        | Configuration | TBLPAG<7:0>           |              |                     | Data EA<15:0>      |     |  |

|                        |               | 1x                    | xx xxxx      | xxxx                | XXXX XXXX XX       | xx  |  |

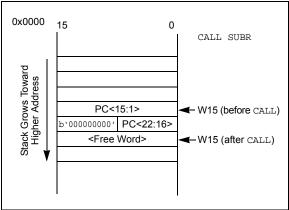

#### FIGURE 4-12: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

**Note 1:** The Least Significant bit (LSb) of Program Space addresses is always fixed as '0' to maintain word alignment of data in the Program and Data Spaces.

**2:** Table operations are not required to be word-aligned. Table Read operations are permitted in the configuration memory space.

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

- bit 2 STKERR: Stack Error Trap Status bit

- 1 = Stack error trap has occurred

- 0 = Stack error trap has not occurred

- bit 1 OSCFAIL: Oscillator Failure Trap Status bit

- 1 = Oscillator failure trap has occurred

- 0 = Oscillator failure trap has not occurred

- bit 0 Unimplemented: Read as '0'

### REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

| U-0                               | U-0          | U-0                        | U-0                                | U-0              | U-0   | U-0             | R/W-0            |  |  |  |

|-----------------------------------|--------------|----------------------------|------------------------------------|------------------|-------|-----------------|------------------|--|--|--|

|                                   | _            | —                          | _                                  | _                | _     | —               | NAE              |  |  |  |

| bit 15                            |              |                            | •                                  | •                | •     |                 | bit 8            |  |  |  |

|                                   |              |                            |                                    |                  |       |                 |                  |  |  |  |

| U-0                               | U-0          | U-0                        | R/W-0                              | U-0              | U-0   | U-0             | R/W-0            |  |  |  |

| _                                 | _            | —                          | DOOVR                              | —                | _     | —               | APLL             |  |  |  |

| bit 7                             | •            |                            | •                                  |                  | •     |                 | bit (            |  |  |  |

|                                   |              |                            |                                    |                  |       |                 |                  |  |  |  |

| Legend:                           |              |                            |                                    |                  |       |                 |                  |  |  |  |

| R = Readable bit W = Writable bit |              | bit                        | U = Unimplemented bit, read as '0' |                  |       |                 |                  |  |  |  |

| -n = Value a                      | t POR        | '1' = Bit is set           | :                                  | '0' = Bit is cle | eared | x = Bit is unkr | = Bit is unknown |  |  |  |

|                                   |              |                            |                                    |                  |       |                 |                  |  |  |  |

| bit 15-9                          | Unimpleme    | nted: Read as              | '0'                                |                  |       |                 |                  |  |  |  |

| bit 8                             | NAE: NVM /   | Address Error S            | oft Trap Status                    | s bit            |       |                 |                  |  |  |  |

|                                   | 1 = NVM ad   | dress error soft           | trap has occur                     | rred             |       |                 |                  |  |  |  |

|                                   | 0 = NVM ad   | dress error soft           | trap has not o                     | ccurred          |       |                 |                  |  |  |  |

| bit 7-5                           | Unimpleme    | Unimplemented: Read as '0' |                                    |                  |       |                 |                  |  |  |  |

| bit 4                             | DOOVR: DO    | Stack Overflow             | / Soft Trap Sta                    | tus bit          |       |                 |                  |  |  |  |

|                                   | 1 = DO stack | overflow soft tr           | ap has occurr                      | ed               |       |                 |                  |  |  |  |

|                                   | 0 = DO stack | overflow soft tr           | ap has not oc                      | curred           |       |                 |                  |  |  |  |

|                                   |              |                            |                                    |                  |       |                 |                  |  |  |  |

- bit 3-1 Unimplemented: Read as '0'

- bit 0 APLL: Auxiliary PLL Loss of Lock Soft Trap Status bit

- 1 = APLL lock soft trap has occurred

- 0 = APLL lock soft trap has not occurred

### REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0             | U-0 | U-0              | U-0 | U-0                                     | U-0 | U-0 | U-0   |

|-----------------|-----|------------------|-----|-----------------------------------------|-----|-----|-------|

| _               | —   | —                |     | —                                       |     | —   |       |

| bit 15          |     |                  |     |                                         |     |     | bit 8 |

|                 |     |                  |     |                                         |     |     |       |

| U-0             | U-0 | U-0              | U-0 | U-0                                     | U-0 | U-0 | R/W-0 |

| —               | —   |                  |     | —                                       | —   | —   | SGHT  |

| bit 7           |     |                  |     |                                         |     |     | bit 0 |

|                 |     |                  |     |                                         |     |     |       |

| Legend:         |     |                  |     |                                         |     |     |       |

| R = Readable b  | oit | W = Writable     | bit | U = Unimplemented bit, read as '0'      |     |     |       |

| -n = Value at P | OR  | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |     | nown  |

bit 15-1 Unimplemented: Read as '0'

SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

bit 0

NOTES:

| R/W-0         | R/W-0        | R/W-0                               | R/W-0      | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|---------------|--------------|-------------------------------------|------------|-------------------|------------------|-----------------|--------|

| PWM8MD        | PWM7MD       | PWM6MD                              | PWM5MD     | PWM4MD            | PWM3MD           | PWM2MD          | PWM1MD |

| bit 15        |              |                                     |            |                   |                  |                 | bit 8  |

|               |              |                                     |            |                   |                  |                 |        |

| U-0           | U-0          | U-0                                 | U-0        | U-0               | U-0              | U-0             | R/W-0  |

|               | —            |                                     |            | —                 |                  |                 | SPI3MD |

| bit 7         |              |                                     |            |                   |                  |                 | bit C  |

| Legend:       |              |                                     |            |                   |                  |                 |        |

| R = Readable  | e bit        | W = Writable                        | oit        | U = Unimplem      | nented bit, read | 1 as '0'        |        |

| -n = Value at | POR          | '1' = Bit is set                    |            | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

|               |              |                                     |            |                   |                  |                 |        |

| bit 15        | PWM8MD: P    | WM8 Module D                        | isable bit |                   |                  |                 |        |

|               | -            | odule is disable<br>odule is enable |            |                   |                  |                 |        |

| bit 14        |              | WM7 Module D                        | -          |                   |                  |                 |        |

| DIL 14        |              | odule is disable                    |            |                   |                  |                 |        |

|               |              | odule is enable                     |            |                   |                  |                 |        |

| bit 13        | PWM6MD: P    | WM6 Module D                        | isable bit |                   |                  |                 |        |

|               |              | odule is disable<br>odule is enable |            |                   |                  |                 |        |

| bit 12        | PWM5MD: P    | WM5 Module D                        | isable bit |                   |                  |                 |        |

|               | -            | odule is disable                    |            |                   |                  |                 |        |

| L:1 44        |              | odule is enable                     |            |                   |                  |                 |        |

| bit 11        |              | WM4 Module D<br>odule is disable    |            |                   |                  |                 |        |

|               |              | odule is enable                     |            |                   |                  |                 |        |

| bit 10        | PWM3MD: P    | WM3 Module D                        | isable bit |                   |                  |                 |        |

|               |              | odule is disable                    |            |                   |                  |                 |        |

|               |              | odule is enable                     |            |                   |                  |                 |        |

| bit 9         |              | WM2 Module D                        |            |                   |                  |                 |        |

|               |              | odule is disable<br>odule is enable | -          |                   |                  |                 |        |

| bit 8         |              | WM1 Module D                        |            |                   |                  |                 |        |

|               |              | odule is disable                    |            |                   |                  |                 |        |

|               | 0 = PWM1 m   | odule is enable                     | d          |                   |                  |                 |        |

| bit 7-1       | Unimplemen   | ted: Read as 'o                     | )'         |                   |                  |                 |        |

| bit 0         |              | 3 Module Disat                      | ole bit    |                   |                  |                 |        |

|               |              | lule is disabled                    |            |                   |                  |                 |        |

|               | 0 = SP13 mod | lule is enabled                     |            |                   |                  |                 |        |

## REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | IC32  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0                 | R/W-0, HS               | U-0 | R/W-0       | R/W-1       | R/W-1       | R/W-0       | R/W-1       |

|-----------------------|-------------------------|-----|-------------|-------------|-------------|-------------|-------------|

| ICTRIG <sup>(2)</sup> | TRIGSTAT <sup>(3)</sup> |     | SYNCSEL4(4) | SYNCSEL3(4) | SYNCSEL2(4) | SYNCSEL1(4) | SYNCSEL0(4) |

| bit 7                 |                         |     |             |             |             |             | bit 0       |

| Legend:           | HS = Hardware Settable bi | t                           |                    |

|-------------------|---------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-9 <b>Unimplemented:</b> Read as '0' |

|--------------------------------------------|

|--------------------------------------------|

bit 8 **IC32:** Input Capture x 32-Bit Timer Mode Select bit (Cascade mode)

- 1 = Odd ICx and even ICx form a single 32-bit input capture module<sup>(1)</sup>

- 0 = Cascade module operation is disabled

### bit 7 ICTRIG: Input Capture x Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source is used to trigger the input capture timer (Trigger mode)

- 0 = Input source is used to synchronize the input capture timer to a timer of another module (Synchronization mode)

#### bit 6 **TRIGSTAT:** Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

- bit 5 Unimplemented: Read as '0'

- Note 1: The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own sync or trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output is set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output is set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

### REGISTER 16-6: STCON2: PWMx SECONDARY CLOCK DIVIDER SELECT REGISTER

| U-0             | U-0 | U-0                                                 | U-0 | U-0                                     | U-0   | U-0   | U-0   |

|-----------------|-----|-----------------------------------------------------|-----|-----------------------------------------|-------|-------|-------|

| —               | _   | —                                                   | _   | —                                       | —     | —     | —     |

| bit 15          |     | ·                                                   |     | •                                       |       | •     | bit 8 |

|                 |     |                                                     |     |                                         |       |       |       |

| U-0             | U-0 | U-0                                                 | U-0 | U-0                                     | R/W-0 | R/W-0 | R/W-0 |

|                 |     | —                                                   |     | — PCLKDIV<2:0> <sup>(1)</sup>           |       |       | [1]   |

| bit 7           |     |                                                     |     | •                                       |       |       | bit 0 |

|                 |     |                                                     |     |                                         |       |       |       |

| Legend:         |     |                                                     |     |                                         |       |       |       |

| R = Readable    | bit | W = Writable bit U = Unimplemented bit, read as '0' |     |                                         |       |       |       |

| -n = Value at F | POR | '1' = Bit is set                                    |     | '0' = Bit is cleared x = Bit is unknown |       |       | iown  |

bit 15-3 Unimplemented: Read as '0'

bit 2-0

- PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved

- 110 = Divide-by-64, maximum PWM timing resolution

- 101 = Divide-by-32, maximum PWM timing resolution

- 100 = Divide-by-16, maximum PWM timing resolution

- 011 = Divide-by-8, maximum PWM timing resolution

- 010 = Divide-by-4, maximum PWM timing resolution

- 001 = Divide-by-2, maximum PWM timing resolution

- 000 = Divide-by-1, maximum PWM timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

### **REGISTER 16-7:** STPER: PWMx SECONDARY MASTER TIME BASE PERIOD REGISTER<sup>(1,2)</sup>

| R/W-1                              | R/W-1 | R/W-1 | R/W-1                                   | R/W-1                              | R/W-1 | R/W-1 | R/W-1 |  |

|------------------------------------|-------|-------|-----------------------------------------|------------------------------------|-------|-------|-------|--|

|                                    |       |       | STPE                                    | R<15:8>                            |       |       |       |  |

| bit 15                             |       |       |                                         |                                    |       |       | bit 8 |  |

|                                    |       |       |                                         |                                    |       |       |       |  |

| R/W-1                              | R/W-1 | R/W-1 | R/W-1                                   | R/W-1                              | R/W-1 | R/W-1 | R/W-1 |  |

|                                    |       |       | STPE                                    | ER<7:0>                            |       |       |       |  |

| bit 7                              |       |       |                                         |                                    |       | bit 0 |       |  |

|                                    |       |       |                                         |                                    |       |       |       |  |

| Legend:                            |       |       |                                         |                                    |       |       |       |  |

| R = Readable bit W = Writable bit  |       |       | bit                                     | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknown |                                    |       | nown  |       |  |

bit 15-0 STPER<15:0>: Secondary Master Time Base (SMTMR) Period Value bits

Note 1: The PWMx time base has a minimum value of 0x0010 and a maximum value of 0xFFF8.

2: Any period value that is less than 0x0028 must have the Least Significant 3 bits set to '0', thus yielding a period resolution at 8.32 ns (at fastest auxiliary clock rate).

## REGISTER 16-8: SSEVTCMP: PWMx SECONDARY SPECIAL EVENT COMPARE REGISTER<sup>(1)</sup>

| R/W-0   | R/W-0 | R/W-0       | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|---------|-------|-------------|--------|----------|-------|-------|-------|

|         |       |             | SSEVTC | MP<12:5> |       |       |       |

| bit 15  |       |             |        |          |       |       | bit 8 |

|         |       |             |        |          |       |       |       |

| R/W-0   | R/W-0 | R/W-0       | R/W-0  | R/W-0    | U-0   | U-0   | U-0   |

|         | S     | SEVTCMP<4:0 | )>     |          | —     | —     | —     |

| bit 7   |       |             |        |          |       |       | bit 0 |

|         |       |             |        |          |       |       |       |

| Legend: |       |             |        |          |       |       |       |

| _ogona.           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 15-3 SSEVTCMP<12:0>: Special Event Compare Count Value bits

bit 2-0 Unimplemented: Read as '0'

Note 1: One LSB = 1.04 ns (at fastest auxiliary clock rate); therefore, the minimum SSEVTCMP resolution is 8.32 ns.

## **REGISTER 16-9:** CHOP: PWMx CHOP CLOCK GENERATOR REGISTER<sup>(1)</sup>

| R/W-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    |

|----------|-----|-----|-----|-----|-----|----------|----------|

| CHPCLKEN | _   | —   | —   | —   | —   | CHOPCLK6 | CHOPCLK5 |

| bit 15   |     |     | •   |     |     |          | bit 8    |

| R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | U-0 | U-0 | U-0   |

|----------|----------|----------|----------|----------|-----|-----|-------|

| CHOPCLK4 | CHOPCLK3 | CHOPCLK2 | CHOPCLK1 | CHOPCLK0 | —   | —   | —     |

| bit 7    |          |          |          |          |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15

CHPCLKEN: Enable Chop Clock Generator bit

1 = Chop clock generator is enabled

0 = Chop clock generator is disabled

bit 14-10

Unimplemented: Read as '0'

bit 9-3

CHOPCLK<6:0>: Chop Clock Divider bits

Value is in 8.32 ns increments. The frequency of the chop clock signal is given by:

Chop Frequency = 1/(16.64 \* (CHOP<7:3> + 1) \* Primary Master PWM Input Clock Period)

bit 2-0 Unimplemented: Read as '0'

**Note 1:** The chop clock generator operates with the primary PWMx clock prescaler (PCLKDIV<2:0>) in the PTCON2 register (Register 16-2).

# 17.0 PERIPHERAL TRIGGER GENERATOR (PTG) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Peripheral Trigger Generator (PTG)" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 17.1 Module Introduction

The Peripheral Trigger Generator (PTG) provides a means to schedule complex, high-speed peripheral operations that would be difficult to achieve using software. The PTG module uses 8-bit commands, called "Steps", that the user writes to the PTG Queue register (PTGQUE0-PTQUE15) which performs operations, such as wait for input signal, generate output trigger and wait for timer.

The PTG module has the following major features:

- Multiple Clock Sources

- Two 16-Bit General Purpose Timers

- Two 16-Bit General Limit Counters

- Configurable for Rising or Falling Edge Triggering

- Generates Processor Interrupts to include:

- Four configurable processor interrupts

- Interrupt on a Step event in Single-Step modeInterrupt on a PTG Watchdog Timer time-out

- Able to Receive Trigger Signals from these Peripherals:

- ADC

- PWM

- Output Compare

- Input Capture

- Comparator

- INT2

- Able to Trigger or Synchronize to these Peripherals:

- Watchdog Timer

- Output Compare

- Input Capture

- ADC

- PWM

- Comparator

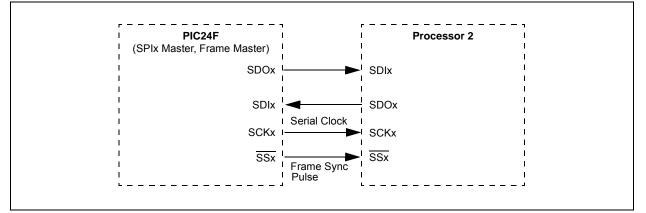

### FIGURE 18-5: SPIX MASTER, FRAME MASTER CONNECTION DIAGRAM

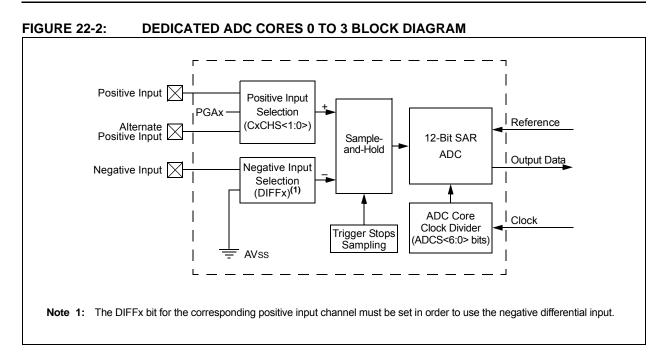

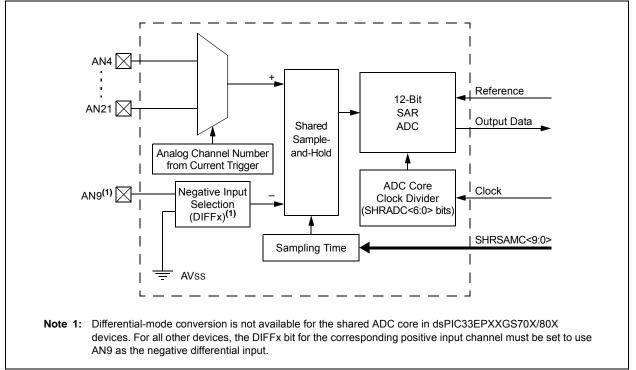

## FIGURE 22-3: SHARED ADC CORE BLOCK DIAGRAM

| REGISTER     | 22-7: ADC                                                                                                                                                                                                                                                                                                                                                                                            | ON4L: ADC C                                                                                                  | ONTROL R                                                                           | EGISTER 4 L                                                                                                                  | wo                                                                          |                                  |                |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------|----------------|

| U-0          | U-0                                                                                                                                                                                                                                                                                                                                                                                                  | U-0                                                                                                          | U-0                                                                                | U-0                                                                                                                          | U-0                                                                         | U-0                              | U-0            |

| _            | —                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                                                                            | —                                                                                  | —                                                                                                                            | —                                                                           | —                                | —              |

| bit 15       |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                              |                                                                                    |                                                                                                                              |                                                                             |                                  | bit 8          |

| U-0          | U-0                                                                                                                                                                                                                                                                                                                                                                                                  | U-0                                                                                                          | U-0                                                                                | R/W-0                                                                                                                        | R/W-0                                                                       | R/W-0                            | R/W-0          |

| _            | —                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                            |                                                                                    | SAMC3EN                                                                                                                      | SAMC2EN                                                                     | SAMC1EN                          | SAMC0EN        |

| bit 7        |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                              |                                                                                    |                                                                                                                              |                                                                             |                                  | bit 0          |

| Legend:      |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                              |                                                                                    |                                                                                                                              |                                                                             |                                  |                |

| R = Readat   | ole bit                                                                                                                                                                                                                                                                                                                                                                                              | W = Writable                                                                                                 | bit                                                                                | U = Unimplen                                                                                                                 | nented bit, read                                                            | d as '0'                         |                |

| -n = Value a | at POR                                                                                                                                                                                                                                                                                                                                                                                               | '1' = Bit is set                                                                                             |                                                                                    | '0' = Bit is clea                                                                                                            |                                                                             | x = Bit is unkr                  | nown           |

| bit 2        | time spe<br>0 = After trig<br>next core<br>SAMC2EN: I<br>1 = After trig<br>time spe<br>0 = After trig                                                                                                                                                                                                                                                                                                | cified by the SA<br>ger, the sampli<br>e clock cycle<br>Dedicated ADC<br>ger, the conver<br>cified by the SA | AMC<9:0> bits<br>ng will be sto<br>Core 2 Conve<br>sion will be d<br>AMC<9:0> bits | elayed and the as in the ADCORE<br>pped immediate<br>ersion Delay Ena<br>elayed and the<br>s in the ADCORE<br>pped immediate | E3L register<br>ly and the con<br>able bit<br>ADC core will<br>E2L register | version will be<br>continue samp | started on the |

| bit 1        | <ul> <li>SAMC1EN: Dedicated ADC Core 1 Conversion Delay Enable bit</li> <li>1 = After trigger, the conversion will be delayed and the ADC core will continue sampling during the time specified by the SAMC&lt;9:0&gt; bits in the ADCORE1L register</li> <li>0 = After trigger, the sampling will be stopped immediately and the conversion will be started on the next core clock cycle</li> </ul> |                                                                                                              |                                                                                    |                                                                                                                              |                                                                             |                                  |                |

| bit 0        | <ul> <li>SAMCOEN: Dedicated ADC Core 0 Conversion Delay Enable bit</li> <li>1 = After trigger, the conversion will be delayed and the ADC core will continue sampling during the time specified by the SAMC&lt;9:0&gt; bits in the ADCORE0L register</li> <li>0 = After trigger, the sampling will be stopped immediately and the conversion will be started on the next core clock cycle</li> </ul> |                                                                                                              |                                                                                    |                                                                                                                              |                                                                             |                                  |                |

## 27.7 JTAG Interface

The dsPIC33EPXXXGS70X/80X family devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface is provided in future revisions of the document.

| Note: | Refer to "Programming and Diagnostics"       |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|

|       | (DS70608) in the "dsPIC33/PIC24 Family       |  |  |  |  |  |

|       | Reference Manual" for further information on |  |  |  |  |  |

|       | usage, configuration and operation of the    |  |  |  |  |  |

|       | JTAG interface.                              |  |  |  |  |  |

## 27.8 In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

The dsPIC33EPXXXGS70X/80X family devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for details about In-Circuit Serial Programming  $\mathbb{C}(\mathsf{LSP}^{\mathsf{TM}})$ .

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

# 27.9 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or REAL ICE<sup>™</sup> emulator is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/ Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{\text{MCLR}}$ , VDD, VSS and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

## 27.10 Code Protection and CodeGuard™ Security

dsPIC33EPXXXGS70X/80X devices offer multiple levels of security for protecting individual intellectual property. The program Flash protection can be broken up into three segments: Boot Segment (BS), General Segment (GS) and Configuration Segment (CS). Boot Segment has the highest security privilege and can be thought to have limited restrictions when accessing other segments. General Segment has the least security and is intended for the end user system code. Configuration Segment contains only the device user configuration data which is located at the end of the program memory space.

The code protection features are controlled by the Configuration registers, FSEC and FBSLIM. The FSEC register controls the code-protect level for each segment and if that segment is write-protected. The size of BS and GS will depend on the BSLIM<12:0> bits setting and if the Alternate Interrupt Vector Table (AIVT) is enabled. The BSLIM<12:0> bits define the number of pages for BS with each page containing 512 IW. The smallest BS size is one page, which will consist of the Interrupt Vector Table (IVT) and 256 IW of code protection.

If the AIVT is enabled, the last page of BS will contain the AIVT and will not contain any BS code. With AIVT enabled, the smallest BS size is now two pages (1024 IW), with one page for the IVT and BS code, and the other page for the AIVT. Write protection of the BS does not cover the AIVT. The last page of BS can always be programmed or erased by BS code. The General Segment will start at the next page and will consume the rest of program Flash except for the Flash Configuration Words. The IVT will assume GS security only if BS is not enabled. The IVT is protected from being programmed or page erased when either security segment has enabled write protection.

Note: Refer to "CodeGuard™ Intermediate Security" (DS70005182) in the "dsPIC33/ PIC24 Family Reference Manual" for further information on usage, configuration and operation of CodeGuard Security.

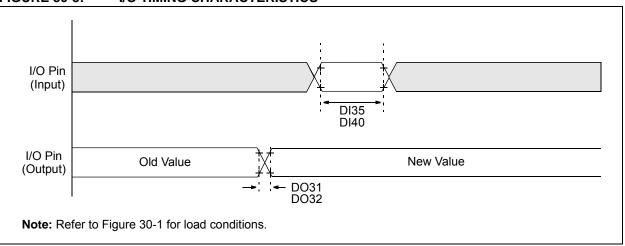

### TABLE 30-22: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq T_A \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq T_A \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                     |      |       |            |

|--------------------|--------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|------------|

| Param<br>No.       | Symbol | Characteristic                    | Min.                                                                                                                                                                                                                                                                                  | Тур. <sup>(1)</sup> | Max. | Units | Conditions |

| DO31               | TioR   | Port Output Rise Time             | _                                                                                                                                                                                                                                                                                     | 5                   | 10   | ns    |            |

| DO32               | TIOF   | Port Output Fall Time             | _                                                                                                                                                                                                                                                                                     | 5                   | 10   | ns    |            |

| DI35               | TINP   | INTx Pin High or Low Time (input) | 20                                                                                                                                                                                                                                                                                    | _                   |      | ns    |            |

| DI40               | TRBP   | CNx High or Low Time (input)      | 2                                                                                                                                                                                                                                                                                     | —                   | _    | Тсү   |            |

**Note 1:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

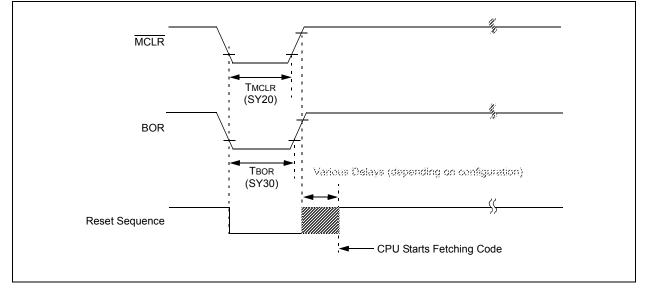

## FIGURE 30-4: BOR AND MASTER CLEAR RESET TIMING CHARACTERISTICS

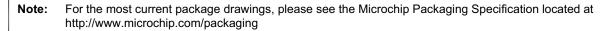

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

# RECOMMENDED LAND PATTERN

|                                  | Ν      | <b>IILLIMETER</b> | S        |      |

|----------------------------------|--------|-------------------|----------|------|

| Dimension                        | Limits | MIN               | NOM      | MAX  |

| Contact Pitch                    | E      |                   | 0.65 BSC |      |

| Optional Center Pad Width        | X2     |                   |          | 6.60 |

| Optional Center Pad Length       | Y2     |                   |          | 6.60 |

| Contact Pad Spacing              | C1     |                   | 8.00     |      |

| Contact Pad Spacing              | C2     |                   | 8.00     |      |

| Contact Pad Width (X44)          | X1     |                   |          | 0.35 |

| Contact Pad Length (X44)         | Y1     |                   |          | 0.85 |

| Contact Pad to Contact Pad (X40) | G1     | 0.30              |          |      |

| Contact Pad to Center Pad (X44)  | G2     | 0.28              |          |      |

| Thermal Via Diameter             | V      |                   | 0.33     |      |

| Thermal Via Pitch                | EV     |                   | 1.20     |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing No. C04-2103C

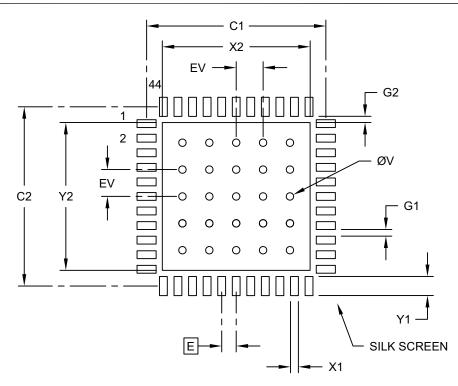

## 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**DETAIL 1**

|                          | MILLIMETERS |           |           |      |

|--------------------------|-------------|-----------|-----------|------|

| Dimension                | MIN         | NOM       | MAX       |      |

| Number of Leads          | Ν           |           | 64        |      |

| Lead Pitch               | е           |           | 0.50 BSC  |      |

| Overall Height           | Α           | -         | -         | 1.20 |

| Molded Package Thickness | A2          | 0.95      | 1.00      | 1.05 |

| Standoff                 | A1          | 0.05      | -         | 0.15 |

| Foot Length              | L           | 0.45      | 0.60      | 0.75 |

| Footprint                | L1          | 1.00 REF  |           |      |

| Foot Angle               | ¢           | 0°        | 3.5°      | 7°   |

| Overall Width            | Е           |           | 12.00 BSC |      |

| Overall Length           | D           |           | 12.00 BSC |      |

| Molded Package Width     | E1          |           | 10.00 BSC |      |

| Molded Package Length    | D1          | 10.00 BSC |           |      |

| Lead Thickness           | С           | 0.09      | -         | 0.20 |

| Lead Width               | b           | 0.17      | 0.22      | 0.27 |

| Mold Draft Angle Top     | α           | 11°       | 12°       | 13°  |

| Mold Draft Angle Bottom  | β           | 11°       | 12°       | 13°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085C Sheet 2 of 2

###

| Oscillator               |     |

|--------------------------|-----|

| Control Registers        |     |

| Resources                |     |

| Oscillator Configuration | 103 |

| Output Compare           |     |

| Control Registers        |     |

| Resources                |     |

| Р                        |     |

| Packaging                |     |

| Packaging                                 | 439 |

|-------------------------------------------|-----|

| Details                                   | 441 |

| Marking                                   | 439 |

| Peripheral Module Disable (PMD)           | 117 |

| Peripheral Pin Select (PPS)               |     |

| Available Peripherals                     |     |

| Available Pins                            |     |

| Control                                   | 135 |

| Control Registers                         |     |

| Input Mapping                             |     |

| Output Mapping                            |     |

| Output Selection for Remappable Pins      |     |

| Selectable Input Sources                  |     |

| Peripheral Trigger Generator (PTG) Module |     |

| Peripheral Trigger Generator. See PTG.    |     |

| Pinout I/O Descriptions (table)           | 12  |

| Power-Saving Features                     |     |

| Clock Frequency and Switching             |     |

| Resources                                 |     |

| Program Address Space                     |     |

| Construction                              |     |

| Data Access from Program Memory Using     |     |

| Table Instructions                        | 59  |

| Memory Map (dsPIC33EP128GS70X/80X Device  |     |

| Dual Partition)                           |     |

| Memory Map (dsPIC33EP128GS70X/80X         |     |

| Devices)                                  | 33  |

| Memory Map (dsPIC33EP64GS70X/80X Devices  |     |

| Dual Partition)                           |     |

| Memory Map (dsPIC33EP64GS70X/80X          |     |

| Devices)                                  | 32  |

| Table Read High Instructions (TBLRDH)     |     |

| Table Read Low Instructions (TBLRDL)      |     |

| Program Memory                            |     |

| Interfacing with Data Memory Spaces       | 58  |

| Organization                              |     |

| Reset Vector                              |     |

| Programmable Gain Amplifier (PGA)         |     |

| Description                               |     |

| Resources                                 |     |

| Programmable Gain Amplifier. See PGA.     |     |

| Programmer's Model                        | 23  |

| Register Descriptions                     |     |

| PTG                                       |     |

| Control Registers                         | 215 |

| Introduction                              |     |

| Output Descriptions                       |     |

| Step Commands and Format                  |     |

| Pulse-Width Modulator. See PWM.           | 223 |

|                                           |     |

### **R** Reg

| jisters                                          |

|--------------------------------------------------|

| ACLKCON (Auxiliary Clock Divisor Control) 112    |

| ADCAL0L (ADC Calibration 0 High) 300             |

| ADCAL0L (ADC Calibration 0 Low)                  |

| ADCAL1H (ADC Calibration 1 High) 301             |

| ADCMPxCON (ADC Digital Comparator x              |

| Control)                                         |

| ADCMPxENH (ADC Digital Comparator x              |

| Channel Enable High)                             |

| ADCMPxENL (ADC Digital Comparator x              |

| Channel Enable Low)                              |

| ADCON1H (ADC Control 1 High)277                  |

| ADCON1L (ADC Control 1 Low)                      |

| ADCON2H (ADC Control 2 High)                     |

|                                                  |

| ADCON2L (ADC Control 2 Low)                      |

| ADCON3H (ADC Control 3 High)                     |

| ADCON3L (ADC Control 3 Low)                      |

| ADCON4H (ADC Control 4 High)                     |

| ADCON4L (ADC Control 4 Low)                      |

| ADCON5H (ADC Control 5 High) 285                 |

| ADCON5L (ADC Control 5 Low) 284                  |

| ADCORExH (Dedicated ADC Core x                   |

| Control High) 287                                |

| ADCORExL (Dedicated ADC Core x                   |

| Control Low) 286                                 |

| ADEIEH (ADC Early Interrupt Enable High) 289     |

| ADEIEL (ADC Early Interrupt Enable Low) 289      |

| ADEISTATH (ADC Early Interrupt Status High) 290  |

| ADEISTATL (ADC Early Interrupt Status Low) 290   |

| ADFLxCON (ADC Digital Filter x Control) 304      |

| ADIEH (ADC Interrupt Enable High) 293            |

| ADIEL (ADC Interrupt Enable Low) 293             |

| ADLVLTRGH (ADC Level-Sensitive Trigger           |

| Control High)                                    |

| ADLVLTRGL (ADC Level-Sensitive Trigger           |

| Control Low)                                     |

| ADMOD0H (ADC Input Mode Control 0 High)          |

| ADMODOL (ADC Input Mode Control 0 Low)           |

| ADMOD1L (ADC Input Mode Control 1 Low)           |

| ADSTATH (ADC Data Ready Status High)             |

| ADSTATL (ADC Data Ready Status High)             |

| ADTRIGXH (ADC Channel Trigger x                  |

| Selection High)                                  |

|                                                  |

| ADTRIGxL (ADC Channel Trigger x                  |

| Selection Low)                                   |

| ALTDTRx (PWMx Alternate Dead-Time)               |

| ANSELx (Analog Select Control x)                 |

| AUXCONx (PWMx Auxiliary Control) 211             |

| CHOP (PWMx Chop Clock Generator) 196             |

| CLCxCONH (CLCx Control High) 263                 |

| CLCxCONL (CLCx Control Low) 262                  |

| CLCxGLSH (CLCx Gate Logic Input Select High) 271 |

| CLCxGLSL (CLCx Gate Logic Input Select Low) 269  |

| CLCxSEL (CLCx Input MUX Select) 264              |

| CLKDIV (Clock Divisor) 109                       |

| CMPxCON (Comparator x Control) 337               |

| CMPxDAC (Comparator x DAC Control)               |

| CNENx (Input Change Notification                 |

| Interrupt Enable x) 133                          |

| · · ·                                            |

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Examples:<br>dsPIC33EP64GS804-I/PT:<br>dsPIC33, Enhanced Performance,<br>64-Kbyte Program Memory, SMPS,<br>44-Pin, Industrial Temperature,<br>TQFP Package. |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | (if applicable)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                             |

| Package              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                             |

| Pattern              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                             |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                             |

| Architecture:        | 33 = 16-Bit Digital Signal Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                             |

| Flash Memory Family: | EP = Enhanced Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                             |

| Product Group:       | GS = SMPS Family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                             |

| Pin Count:           | 02 = 28-pin<br>04 = 44-pin<br>05 = 48-pin<br>06 = 64-pin<br>08 = 80-pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                             |

| Temperature Range:   | $ \begin{array}{rcl} I &=& -40^\circ C \text{ to } +85^\circ C \text{ (Industrial)} \\ E &=& -40^\circ C \text{ to } +125^\circ C \text{ (Extended)} \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                             |

| Package:             | ML       =       Plastic Quad, No Lead Package – (44-pin) 8x8 mm body (QFN)         MM       =       Plastic Quad, No Lead Package – (28-pin) 6x6 mm body (QFN-S)         2N       =       Plastic Quad Flat, No Lead Package – (28-pin) 6x6 mm body (UQFN)         PT       =       Plastic Thin Quad Flatpack – (44-pin) 10x10 mm body (TQFP)         PT       =       Plastic Thin Quad Flatpack – (48-pin) 7x7 mm body (TQFP)         PT       =       Plastic Thin Quad Flatpack – (64-pin) 10x10 mm body (TQFP)         PT       =       Plastic Thin Quad Flatpack – (64-pin) 10x10 mm body (TQFP)         PT       =       Plastic Thin Quad Flatpack – (64-pin) 10x10 mm body (TQFP)         PT       =       Plastic Thin Quad Flatpack – (80-pin) 12x12 mm body (TQFP)         SO       =       Plastic Small Outline, Wide – (28-pin) 7.50 mm body (SOIC) |                                                                                                                                                             |