Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                           |

| Number of I/O              | 51                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs706t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

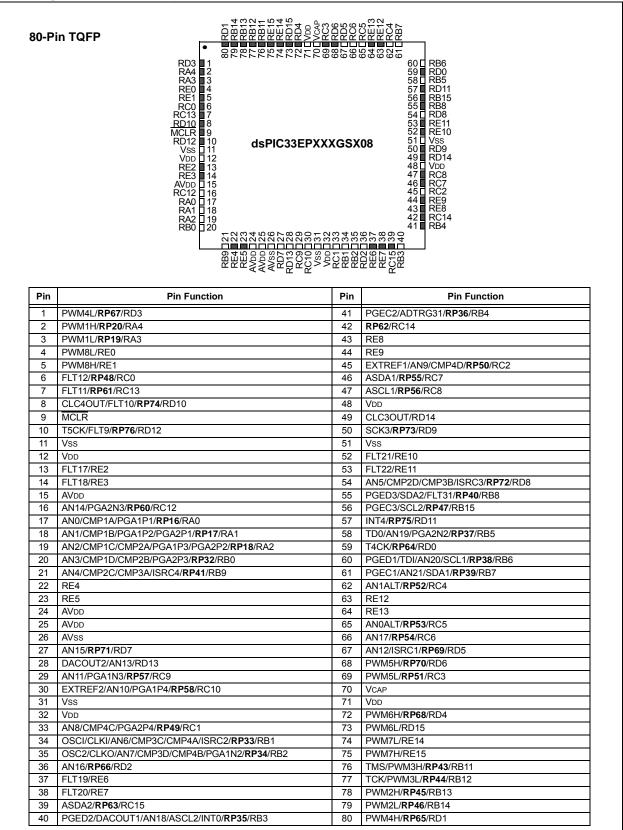

# **Pin Diagrams (Continued)**

Legend: Shaded pins are up to 5 VDC tolerant.

**RPn** represents remappable peripheral functions. See Table 11-12 and Table 11-13 for the complete list of remappable sources.

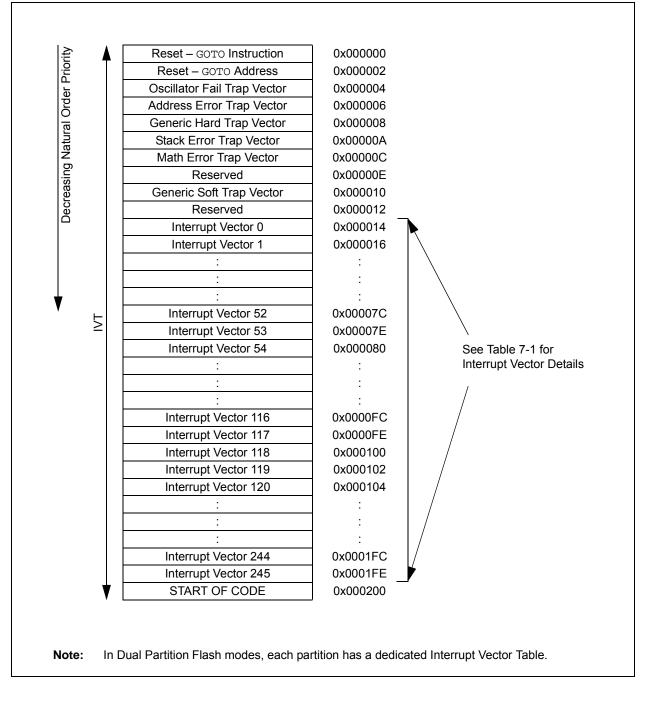

#### FIGURE 7-1: dsPIC33EPXXXGS70X/80X FAMILY INTERRUPT VECTOR TABLE

#### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

bit 4-0

**PLLPRE<4:0>:** PLL Phase Detector Input Divider Select bits (also denoted as 'N1', PLL prescaler) 11111 = Input divided by 33

•

00001 = Input divided by 3

00000 = Input divided by 2 (default)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- **2:** This bit is cleared when the ROI bit is set and an interrupt occurs.

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

#### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0   |

|--------|-----|-----|-----|-----|-----|-----|---------|

| —      | —   | —   | —   | —   | —   | —   | PLLDIV8 |

| bit 15 |     |     |     |     |     |     | bit 8   |

| R/W-0       | R/W-0 | R/W-1 | R/W-1 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PLLDIV<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |  |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 15-9 Unimplemented: Read as '0'

### REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

| U-0          | U-0               | U-0                                   | U-0        | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|--------------|-------------------|---------------------------------------|------------|-------------------|------------------|-----------------|--------|

| _            | —                 | —                                     | _          | CMP4MD            | CMP3MD           | CMP2MD          | CMP1MD |

| bit 15       |                   |                                       |            |                   |                  |                 | bit 8  |

|              |                   |                                       |            |                   |                  |                 |        |

| U-0          | U-0               | U-0                                   | R/W-0      | R/W-0             | U-0              | R/W-0           | U-0    |

| —            |                   |                                       | DMAMD      | PTGMD             | —                | PGA1MD          |        |

| bit 7        |                   |                                       |            |                   |                  |                 | bit 0  |

| Legend:      |                   |                                       |            |                   |                  |                 |        |

| R = Readat   | ole bit           | W = Writable                          | bit        | U = Unimplen      | nented bit, read | d as '0'        |        |

| -n = Value a | at POR            | '1' = Bit is se                       | t          | '0' = Bit is clea |                  | x = Bit is unkn | iown   |

|              |                   |                                       |            |                   |                  |                 |        |

| bit 15-12    | Unimpleme         | nted: Read as                         | 0'         |                   |                  |                 |        |

| bit 11       | CMP4MD: (         | CMP4 Module D                         | isable bit |                   |                  |                 |        |

|              |                   | nodule is disable                     |            |                   |                  |                 |        |

|              |                   | nodule is enable                      |            |                   |                  |                 |        |

| bit 10       |                   | CMP3 Module D                         |            |                   |                  |                 |        |

|              |                   | nodule is disable<br>nodule is enable |            |                   |                  |                 |        |

| bit 9        |                   | CMP2 Module D                         |            |                   |                  |                 |        |

| bit 0        |                   | nodule is disable                     |            |                   |                  |                 |        |

|              | -                 | nodule is enable                      |            |                   |                  |                 |        |

| bit 8        | CMP1MD: (         | CMP1 Module D                         | isable bit |                   |                  |                 |        |

|              | 1 = CMP1 n        | nodule is disable                     | ed         |                   |                  |                 |        |

|              | 0 = CMP1 n        | nodule is enable                      | d          |                   |                  |                 |        |

| bit 7-5      | Unimpleme         | ented: Read as                        | 0'         |                   |                  |                 |        |

| bit 4        |                   | MA Module Disa                        |            |                   |                  |                 |        |

|              |                   | odule is disabled<br>odule is enabled |            |                   |                  |                 |        |

| bit 3        |                   | G Module Disal                        |            |                   |                  |                 |        |

| DILS         | _                 | dule is disabled                      |            |                   |                  |                 |        |

|              |                   | dule is enabled                       |            |                   |                  |                 |        |

| bit 2        | Unimpleme         | nted: Read as                         | 0'         |                   |                  |                 |        |

| bit 1        | -                 | PGA1 Module Di                        |            |                   |                  |                 |        |

|              | 1 = PGA1 m        | nodule is disable                     | d          |                   |                  |                 |        |

|              | 0 <b>= PGA1 m</b> | nodule is enable                      | d          |                   |                  |                 |        |

| bit 0        | Unimpleme         | nted: Read as                         | 0'         |                   |                  |                 |        |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cleared |                 | x = Bit is unknown |       |

|-------------------|-------|------------------|-------|----------------------|-----------------|--------------------|-------|

| R = Readable      | bit   | W = Writable     | bit   | U = Unimplen         | nented bit, rea | d as '0'           |       |

| Legend:           |       |                  |       |                      |                 |                    |       |

|                   |       |                  |       |                      |                 |                    |       |

| bit 7             | •     | 1                | •     |                      |                 |                    | bit ( |

| IC1R7             | IC1R6 | IC1R5            | IC1R4 | IC1R3                | IC1R2           | IC1R1              | IC1R0 |

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0                | R/W-0           | R/W-0              | R/W-0 |

| bit 15            |       |                  |       |                      |                 |                    | bit 8 |

| IC2R7             | IC2R6 | IC2R5            | IC2R4 | IC2R3                | IC2R2           | IC2R1              | IC2R0 |

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0                | R/W-0           | R/W-0              | R/W-0 |

| bit 15-8 | IC2R<7:0>: Assign Input Capture 2 (IC2) to the Corresponding RPn Pin bits       |

|----------|---------------------------------------------------------------------------------|

|          | See Table 11-11 which contains a list of remappable inputs for the index value. |

| bit 7-0  | IC1R<7:0>: Assign Input Capture 1 (IC1) to the Corresponding RPn Pin bits       |

|          | See Table 11-11 which contains a list of remappable inputs for the index value. |

### REGISTER 11-14: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| IC4R7  | IC4R6 | IC4R5 | IC4R4 | IC4R3 | IC4R2 | IC4R1 | IC4R0 |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IC3R7 | IC3R6 | IC3R5 | IC3R4 | IC3R3 | IC3R2 | IC3R1 | IC3R0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-8IC4R<7:0>: Assign Input Capture 4 (IC4) to the Corresponding RPn Pin bits<br/>See Table 11-11 which contains a list of remappable inputs for the index value.bit 7-0IC3R<7:0>: Assign Input Capture 3 (IC3) to the Corresponding RPn Pin bits<br/>See Table 11-11 which contains a list of remappable inputs for the index value.

#### REGISTER 11-21: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|-------|-------|-------|-------|

| —      | —     | —     | —     | —     | —     | -     | —     |

| bit 15 |       |       |       | •     |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| SS1R7  | SS1R6 | SS1R5 | SS1R4 | SS1R3 | SS1R2 | SS1R1 | SS1R0 |

| bit 7  |       |       | ·     |       | ·     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **SS1R<7:0>:** Assign SPI1 Slave Select (SS1) to the Corresponding RPn Pin bits See Table 11-11 which contains a list of remappable inputs for the index value.

#### REGISTER 11-22: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| R/W-0                              | R/W-0    | R/W-0        | R/W-0                                  | R/W-0                              | R/W-0    | R/W-0    | R/W-0    |  |

|------------------------------------|----------|--------------|----------------------------------------|------------------------------------|----------|----------|----------|--|

| SCK2INR7                           | SCK2INR6 | SCK2INR5     | SCK2INR4                               | SCK2INR3                           | SCK2INR2 | SCK2INR1 | SCK2INR0 |  |

| bit 15                             |          |              |                                        |                                    |          | •        | bit 8    |  |

|                                    |          |              |                                        |                                    |          |          |          |  |

| R/W-0                              | R/W-0    | R/W-0        | R/W-0                                  | R/W-0                              | R/W-0    | R/W-0    | R/W-0    |  |

| SDI2R7                             | SDI2R6   | SDI2R5       | SDI2R4                                 | SDI2R3                             | SDI2R2   | SDI2R1   | SDI2R0   |  |

| bit 7                              |          |              |                                        |                                    |          |          | bit 0    |  |

|                                    |          |              |                                        |                                    |          |          |          |  |

| Legend:                            |          |              |                                        |                                    |          |          |          |  |

| R = Readable                       | bit      | W = Writable | bit                                    | U = Unimplemented bit, read as '0' |          |          |          |  |

| -n = Value at POR '1' = Bit is set |          |              | '0' = Bit is cleared x = Bit is unknow |                                    |          | nown     |          |  |

bit 15-8SCK2INR<7:0>: Assign SPI2 Clock Input (SCK2) to the Corresponding RPn Pin bits<br/>See Table 11-11 which contains a list of remappable inputs for the index value.bit 7-0SDI2R<7:0>: Assign SPI2 Data Input (SDI2) to the Corresponding RPn Pin bits

See Table 11-11 which contains a list of remappable inputs for the index value.

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

- 11111 = OCxRS compare event is used for synchronization

- 11110 = INT2 pin synchronizes or triggers OCx

- 11101 = INT1 pin synchronizes or triggers OCx

- 11100 = Reserved

- 11011 = CMP4 module synchronizes or triggers OCx

- 11010 = CMP3 module synchronizes or triggers OCx

- 11001 = CMP2 module synchronizes or triggers OCx

- 11000 = CMP1 module synchronizes or triggers OCx

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 input capture interrupt event synchronizes or triggers OCx

- 10010 = IC3 input capture interrupt event synchronizes or triggers OCx

- 10001 = IC2 input capture interrupt event synchronizes or triggers OCx

- 10000 = IC1 input capture interrupt event synchronizes or triggers OCx

- 01111 = Timer5 synchronizes or triggers OCx

- 01110 = Timer4 synchronizes or triggers OCx

- 01101 = Timer3 synchronizes or triggers OCx

- 01100 = Timer2 synchronizes or triggers OCx (default)

- 01011 = Timer1 synchronizes or triggers OCx

- 01010 = PTG Trigger Output x<sup>(3)</sup>

- 01001 = Reserved

- 01000 = IC4 input capture event synchronizes or triggers OCx

- 00111 = IC3 input capture event synchronizes or triggers OCx

- 00110 = IC2 input capture event synchronizes or triggers OCx

- 00101 = IC1 input capture event synchronizes or triggers OCx

- 00100 = OC4 module synchronizes or triggers  $OCx^{(1,2)}$

- 00011 = OC3 module synchronizes or triggers  $OCx^{(1,2)}$

- $00010 = OC2 \text{ module synchronizes or triggers } OCx^{(1,2)}$

- 00001 = OC1 module synchronizes or triggers  $OCx^{(1,2)}$

- 00000 = No sync or trigger source for OCx

- Note 1: Do not use the OCx module as its own synchronization or trigger source.

- 2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

- 3: For each OCMPx instance, a different PTG trigger out is used:

- OCMP1 PTG trigger out [0]

- OCMP2 PTG trigger out [1]

- OCMP3 PTG trigger out [2]

- OCMP4 PTG trigger out [3]

### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCIx feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

#### REGISTER 16-2: PTCON2: PWMx CLOCK DIVIDER SELECT REGISTER

| U-0                                                                  | U-0 | U-0              | U-0    | U-0                                     | U-0             | U-0   | U-0   |

|----------------------------------------------------------------------|-----|------------------|--------|-----------------------------------------|-----------------|-------|-------|

| _                                                                    | —   | —                | —      | —                                       | —               | —     | —     |

| bit 15                                                               |     |                  |        |                                         |                 |       | bit 8 |

|                                                                      |     |                  |        |                                         |                 |       |       |

| U-0                                                                  | U-0 | U-0              | U-0    | U-0                                     | R/W-0           | R/W-0 | R/W-0 |

|                                                                      | _   | _                | —      | —                                       | PCLKDIV<2:0>(1) |       |       |

| bit 7                                                                |     |                  |        |                                         |                 |       | bit 0 |

|                                                                      |     |                  |        |                                         |                 |       |       |

| Legend:                                                              |     |                  |        |                                         |                 |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |                  | as '0' |                                         |                 |       |       |

| -n = Value at I                                                      | POR | '1' = Bit is set |        | '0' = Bit is cleared x = Bit is unknown |                 |       | nown  |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

111 = Reserved

- 110 = Divide-by-64, maximum PWM timing resolution

- 101 = Divide-by-32, maximum PWM timing resolution

- 100 = Divide-by-16, maximum PWM timing resolution

- 011 = Divide-by-8, maximum PWM timing resolution

- 010 = Divide-by-4, maximum PWM timing resolution

- 001 = Divide-by-2, maximum PWM timing resolution

- 000 = Divide-by-1, maximum PWM timing resolution (power-on default)

**Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

### REGISTER 16-22: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER (x = 1 to 8) (CONTINUED)

| bit 7-3 | FLTSRC<4:0>: Fault Control Signal Source Select for PWMx Generator bits<br>11111 = Reserved<br>10001 = Reserved<br>10000 = Analog Comparator 4<br>01111 = Analog Comparator 3<br>01110 = Analog Comparator 2<br>01101 = Analog Comparator 1<br>01100 = Fault 12<br>01011 = Fault 11<br>01010 = Fault 11<br>01010 = Fault 10<br>01001 = Fault 9<br>01000 = Fault 8<br>00111 = Fault 7 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 00110 = Fault 7 $00110 = Fault 6$ $00101 = Fault 5$ $00100 = Fault 4$ $00011 = Fault 3$ $00010 = Fault 2$ $00001 = Fault 1$ $00000 = Reserved$                                                                                                                                                                                                                                       |

| bit 2   | <b>FLTPOL:</b> Fault Polarity for PWMx Generator bit <sup>(1)</sup><br>1 = The selected Fault source is active-low<br>0 = The selected Fault source is active-high                                                                                                                                                                                                                   |

| bit 1-0 | FLTMOD<1:0>: Fault Mode for PWMx Generator bits<br>11 = Fault input is disabled<br>10 = Reserved<br>01 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (cycle)<br>00 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (latched condition)                                                                                       |

Note 1: These bits should be changed only when PTEN = 0 (PTCON<15>).

### REGISTER 16-23: STRIGX: PWMX SECONDARY TRIGGER COMPARE VALUE REGISTER (x = 1 to 8)<sup>(1)</sup>

| R/W-0        | R/W-0       | R/W-0                                               | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0        |

|--------------|-------------|-----------------------------------------------------|-----------------|-------------------|-----------------|-----------------|--------------|

|              |             |                                                     | STRGC           | MP<12:5>          |                 |                 |              |

| bit 15       |             |                                                     |                 |                   |                 |                 | bit 8        |

| R/W-0        | R/W-0       | R/W-0                                               | R/W-0           | R/W-0             | U-0             | U-0             | U-0          |

|              |             | STRGCMP<4:0                                         | >               |                   |                 | _               | _            |

| bit 7        |             |                                                     |                 |                   |                 |                 | bit (        |

| Legend:      |             |                                                     |                 |                   |                 |                 |              |

| R = Readab   | le bit      | W = Writable                                        | bit             | U = Unimplem      | nented bit, rea | d as '0'        |              |

| -n = Value a | t POR       | '1' = Bit is set                                    |                 | '0' = Bit is clea | ared            | x = Bit is unkr | iown         |

| bit 15-3     | When the se | <12:0>: Seconda<br>econdary PWMx<br>ger the ADC mod | functions in th | •                 |                 | contains the co | mpare values |

| bit 2-0      |             | nted: Read as '                                     |                 |                   |                 |                 |              |

Note 1: STRIGx cannot generate the PWM trigger interrupts.

### REGISTER 21-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER (CONTINUED)

| bit 3 | G3D2T: Gate 3 Data Source 2 True Enable bit                                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Data Source 2 non-inverted signal is enabled for Gate 3                                                                                           |

|       | 0 = Data Source 2 non-inverted signal is disabled for Gate 3                                                                                          |

| bit 2 | G3D2N: Gate 3 Data Source 2 Negated Enable bit                                                                                                        |

|       | <ul> <li>1 = Data Source 2 inverted signal is enabled for Gate 3</li> <li>0 = Data Source 2 inverted signal is disabled for Gate 3</li> </ul>         |

| bit 1 | G3D1T: Gate 3 Data Source 1 True Enable bit                                                                                                           |

|       | <ul> <li>1 = Data Source 1 non-inverted signal is enabled for Gate 3</li> <li>0 = Data Source 1 non-inverted signal is disabled for Gate 3</li> </ul> |

| bit 0 | G3D1N: Gate 3 Data Source 1 Negated Enable bit                                                                                                        |

|       | 1 = Data Source 1 inverted signal is enabled for Gate 3                                                                                               |

|       | 0 = Data Source 1 inverted signal is disabled for Gate 3                                                                                              |

#### REGISTER 22-22: ADIEL: ADC INTERRUPT ENABLE REGISTER LOW

| R/W-0                             | R/W-0  | R/W-0            | R/W-0                   | R/W-0             | R/W-0          | R/W-0           | R/W-0          |

|-----------------------------------|--------|------------------|-------------------------|-------------------|----------------|-----------------|----------------|

|                                   |        |                  | IE<                     | :15:8>            |                |                 |                |

| bit 15                            |        |                  |                         |                   |                |                 | bit 8          |

|                                   | 5444.0 | <b>D</b> # 44 0  | <b>D</b> # <b>M</b> / 0 | 5444.0            | <b>D</b> 444 0 | <b>D</b> 444.0  | <b>D</b> 444 0 |

| R/W-0                             | R/W-0  | R/W-0            | R/W-0                   | R/W-0             | R/W-0          | R/W-0           | R/W-0          |

|                                   |        |                  | IE                      | <7:0>             |                |                 |                |

| bit 7                             |        |                  |                         |                   |                |                 | bit 0          |

| Legend:                           |        |                  |                         |                   |                |                 |                |

| R = Readable bit W = Writable bit |        | bit              | U = Unimpler            | nented bit, rea   | id as '0'      |                 |                |

| -n = Value at POR '1' =           |        | '1' = Bit is set |                         | '0' = Bit is clea | ared           | x = Bit is unkr | nown           |

bit 15-0 IE<15:0>: Common Interrupt Enable bits

1 = Common and individual interrupts are enabled for the corresponding channel

0 = Common and individual interrupts are disabled for the corresponding channel

### **REGISTER 22-23: ADIEH: ADC INTERRUPT ENABLE REGISTER HIGH**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   |       |       | IE<2  | 1:16> |       |       |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0

IE<21:16>: Common Interrupt Enable bits

1 = Common and individual interrupts are enabled for the corresponding channel

0 = Common and individual interrupts are disabled for the corresponding channel

# REGISTER 22-26: ADTRIGxL: ADC CHANNEL TRIGGER x SELECTION REGISTER LOW (x = 0 to 5) (CONTINUED)

bit 4-0 TRGSRC(4x)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits 11111 = ADTRG31 11110 = PTG Trigger Output 30 11101 = PWM Generator 6 current-limit trigger 11100 = PWM Generator 5 current-limit trigger 11011 = PWM Generator 4 current-limit trigger 11010 = PWM Generator 3 current-limit trigger 11001 = PWM Generator 2 current-limit trigger 11000 = PWM Generator 1 current-limit trigger 10111 = Output Compare 2 trigger 10110 = Output Compare 1 trigger 10101 = CLC2 output 10100 = PWM Generator 6 secondary trigger 10011 = PWM Generator 5 secondary trigger 10010 = PWM Generator 4 secondary trigger 10001 = PWM Generator 3 secondary trigger 10000 = PWM Generator 2 secondary trigger 01111 = PWM Generator 1 secondary trigger 01110 = PWM secondary Special Event Trigger 01101 = Timer2 period match 01100 = Timer1 period match 01011 = CLC1 output 01010 = PWM Generator 6 primary trigger 01001 = PWM Generator 5 primary trigger 01000 = PWM Generator 4 primary trigger 00111 = PWM Generator 3 primary trigger 00110 = PWM Generator 2 primary trigger 00101 = PWM Generator 1 primary trigger 00100 = PWM Special Event Trigger 00011 = Reserved 00010 = Level software trigger 00001 = Common software trigger

00000 = No trigger is enabled

# REGISTER 22-34: ADFLxCON: ADC DIGITAL FILTER x CONTROL REGISTER

| FLEN       MODE1       MODE0       OVRSAM2       OVRSAM1       OVRSAM0       IE       RI         bit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | REGISTER               | 22-34: ADFL<br>(x = 0                                                                                                                                                                                                                                   | _xCON: ADC<br>) or 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DIGITAL FIL                                             | TER x CONT               | ROL REGIS       | FER             |           |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------|-----------------|-----------------|-----------|--|--|

| FLEN       MODE1       MODE0       OVRSAM2       OVRSAM1       OVRSAM0       IE       RI         bit 15       Image: State                                                                                                                                  | R/W-0                  | R/W-0                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                   | R/W-0                    | R/W-0           | R/W-0           | R-0, HSC  |  |  |

| U-0       U-0       R/W-0       R/W       R/W       R/W       R/W       R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FLEN                   | MODE1                                                                                                                                                                                                                                                   | MODE0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OVRSAM2                                                 | OVRSAM1                  | OVRSAM0         | IE              | RDY       |  |  |

| -       -       FLCHSEL4       FLCHSEL3       FLCHSEL2       FLCHSEL1       FLCHSEL1         bit 7         Legend:       U = Unimplemented bit, read as '0'         R = Readable bit       W = Writable bit       HSC = Hardware Settable/Clearable bit         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       FLEN: Filter Enable bit       -       -       -         0 = Filter is disabled and the RDY bit is cleared       -       -       -       -         bit 14-13       MODE<1:0>: Filter Mode bits       -       -       -       -         1 = Averaging mode       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 15                 |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                         |                          |                 |                 | bit 8     |  |  |

| bit 7 Legend: U = Unimplemented bit, read as '0' R = Readable bit W = Writable bit HSC = Hardware Settable/Clearable bit -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 FLEN: Filter Enable bit 1 = Filter is enabled 0 = Filter is disabled and the RDY bit is cleared bit 14-13 MODE<1:0:: Filter Mode bits 11 = Averaging mode 10 = Reserved 00 = Oversampling mode 10 = Reserved 00 = Oversampling mode 11 = 128 (16-bit result in the ADFLxDAT register is in 12.4 format) 110 = 32x (16-bit result in the ADFLxDAT register is in 12.4 format) 101 = 8x (14-bit result in the ADFLxDAT register is in 12.4 format) 101 = 256x (16-bit result in the ADFLxDAT register is in 12.4 format) 011 = 256x (16-bit result in the ADFLxDAT register is in 12.4 format) 010 = 64x (13-bit result in the ADFLxDAT register is in 12.4 format) 011 = 256x (16-bit result in the ADFLxDAT register is in 12.4 format) 011 = 126x 110 = 128. 110 = 128. 110 = 128. 111 = 128 100 = 32. 111 = 128 100 = 32. 111 = 128 100 = 32. 111 = 128 100 = 32. 111 = 128 101 = 4X 100 = 32. 111 = 128 101 = 4X 100 = 32. 111 = 128 101 = 4X 100 = 32. 111 = 128 101 = 4X 100 = 32. 111 = 128 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 101 = | U-0                    | U-0                                                                                                                                                                                                                                                     | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                   | R/W-0                    | R/W-0           | R/W-0           | R/W-0     |  |  |

| Legend:       U = Unimplemented bit, read as '0'         R = Readable bit       W = Writable bit       HSC = Hardware Settable/Clearable bit         .n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       FLEN: Filter Enable bit       1 = Filter is disabled and the RDY bit is cleared       x = Bit is unknown         bit 14.13       MODE<1:0>: Filter Mode bits       1 = Averaging mode       10 = Reserved         00 = Oversampling mode       00 = Oversampling mode       10 = Reserved       11 = 128x (16-bit result in the ADFLxDAT register is in 12.4 format)         110 = 32x (15-bit result in the ADFLxDAT register is in 12.3 format)       101 = 8x (14-bit result in the ADFLxDAT register is in 12.4 format)         101 = 256x (16-bit result in the ADFLxDAT register is in 12.4 format)       010 = 0 = 2x (13-bit result in the ADFLxDAT register is in 12.4 format)         010 = 0 = 32x (15-bit result in the ADFLxDAT register is in 12.4 format)       011 = 256x (16-bit result in the ADFLxDAT register is in 12.4 format)         011 = 128x (13-bit result in the ADFLxDAT register is in 12.4 format)       010 = 64x (13-bit result in the ADFLxDAT register is in 12.1 format)         011 = 128x       101 = 128x       101 = 128x         100 = 128x       101 = 128x       101 = 128x         101 = 128x       101 = 128x       101 = 128x         101 = 128x       101 = 128x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | —                      | —                                                                                                                                                                                                                                                       | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FLCHSEL4                                                | FLCHSEL3                 | FLCHSEL2        | FLCHSEL1        | FLCHSEL0  |  |  |

| R = Readable bit       W = Writable bit       HSC = Hardware Settable/Clearable bit         .n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       FLEN: Filter Enable bit       1       = Filter is enabled       0         0 = Filter is disabled and the RDY bit is cleared       0 = Filter is disabled and the RDY bit is cleared       0         bit 14-13       MODE-1:0>: Filter Mode bits       1       = Reserved       0         0 = Reserved       00 = Oversampling mode       0       = Coresampling mode         0 = Reserved       00 = Oversampling mode       0       = Norsampling mode         bit 12-10       OVRSAM       = Site result in the ADFLxDAT register is in 12.4 format)       110 = 32x (15-bit result in the ADFLxDAT register is in 12.3 format)         101 = 32x (14-bit result in the ADFLxDAT register is in 12.1 format)       100 = 2x (13-bit result in the ADFLxDAT register is in 12.2 format)       001 = 4x (14-bit result in the ADFLxDAT register is in 12.2 format)         001 = 4x (14-bit result in the ADFLxDAT register is in 12.2 format)       001 = 4x (14-bit result in the ADFLxDAT register is in 12.1 format)         001 = 16x (14-bit result in the ADFLxDAT register is in 12.1 format)       111 = 256x         111 = 256x       111 = 256x       111 = 256x         111 = 256x       111 = 256x       111 = 256x       111 = 256                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 7                  |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                         |                          |                 |                 | bit (     |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       FLEN: Filter Enable bit       1 = Filter is enabled       0 = Filter is disabled and the RDY bit is cleared         bit 14-13       MODE<1:0>: Filter Mode bits       1 = Averaging mode       0 = Reserved         01 = Reserved       00 = Oversampling mode       0 = Reserved       0 = Oversampling mode         bit 12-10       OVRSAM       2:0>: Filter Averaging/Oversampling Ratio bits       If MODE         I11 = 128x (16-bit result in the ADFLxDAT register is in 12.4 format)       10 = 32x (15-bit result in the ADFLxDAT register is in 12.3 format)         100 = 2x (15-bit result in the ADFLxDAT register is in 12.4 format)       100 = 2x (14-bit result in the ADFLxDAT register is in 12.4 format)         101 = 256x (16-bit result in the ADFLxDAT register is in 12.4 format)       000 = 4x (13-bit result in the ADFLxDAT register is in 12.1 format)         010 = 64x (15-bit result in the ADFLxDAT register is in 12.1 format)       000 = 4x (13-bit result in the ADFLxDAT register is in 12.1 format)         011 = 128x       10 = 128x       10 = 64x         100 = 32x       11 = 16x       10 = 8x         010 = 42x       10 = 64x       10 = 2x         101 = 16x       10 = 8x       10 = 8x         010 = 8x       10 = 16x       10 = 16x         010 = 8x       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Legend:                |                                                                                                                                                                                                                                                         | U = Unimpler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | mented bit, read                                        | as '0'                   |                 |                 |           |  |  |

| bit 15       FLEN: Filter Enabled         0 = Filter is enabled         0 = Filter is disabled and the RDY bit is cleared         bit 14-13         MODE<1:0>: Filter Mode bits         11 = Averaging mode         10 = Reserved         01 = Reserved         00 = Oversampling mode         bit 12-10       OVRSAM<2:0>: Filter Averaging/Oversampling Ratio bits         If MODE<1:0> = 00;         111 = 128x (16-bit result in the ADFLxDAT register is in 12.4 format)         100 = 32x (15-bit result in the ADFLxDAT register is in 12.4 format)         101 = 8x (14-bit result in the ADFLxDAT register is in 12.4 format)         101 = 2x (13-bit result in the ADFLxDAT register is in 12.4 format)         101 = 2x (14-bit result in the ADFLxDAT register is in 12.4 format)         101 = 25x (16-bit result in the ADFLxDAT register is in 12.4 format)         010 = 64x (15-bit result in the ADFLxDAT register is in 12.1 format)         001 = 64x (15-bit result in the ADFLxDAT register is in 12.1 format)         000 = 4x (13-bit result in the ADFLxDAT register is in 12.1 format)         000 = 4x (13-bit result in the ADFLxDAT register is in 12.1 format)         011 = 128x         101 = 128x         101 = 64x         100 = 4x         001 = 4x         000 = 2x         bit 9       IE: Filte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R = Readab             | le bit                                                                                                                                                                                                                                                  | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit                                                     | HSC = Hardw              | /are Settable/C | learable bit    |           |  |  |

| <ul> <li>i = Filter is enabled         <ul> <li>i = Filter is disabled and the RDY bit is cleared</li> <li>bit 14-13</li> <li>MODE</li> <li>i = Averaging mode                  10 = Reserved                  01 = Reserved                  00 = Oversampling mode</li> <li>bit 12-10</li> <li>OVRSAM</li> <li>i = Averaging mode</li> <li>i = Reserved                  00 = Oversampling mode</li> <li>bit 12-10</li> <li>OVRSAM</li> <li>i = Reserved</li> <li>i = Reserved</li> <li>i = 128x (16-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 32x (15-bit result in the ADFLxDAT register is in 12.3 format)</li> <li>i = 8x (14-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 8x (14-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 256x (16-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 26x (16-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 126x (14-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 26x (16-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 126x it result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 128x it is in 12.4 format)</li> <li>i = 128x it is in 12.4 format)</li> <li>i = 128x it is in 12.2 format)</li> <li>i = 128x it is in 12.4 format)</li> <li>i = 44x it is a state is in 12.4 format)</li> <li>i = 26x it is in 12.4 format)</li> <li>i = 16x it is a state is is in 12.4 format)</li> <li>i = 16x it is a state is is is is is is a state is is is is a state is is is is is is a state is is is is is a state is is is is is is cleared by hardware when the result is result will be ready is is is cleared by hardware when the resu</li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                            | -n = Value a           | It POR                                                                                                                                                                                                                                                  | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | t                                                       | '0' = Bit is cle         | ared            | x = Bit is unki | nown      |  |  |

| bit 14-13 MODE<1:0:: Filter Mode bits<br>11 = Averaging mode<br>10 = Reserved<br>01 = Reserved<br>00 = Oversampling mode<br>bit 12-10 OVRSAM<2:0:: Filter Averaging/Oversampling Ratio bits<br><u>If MODE&lt;1:0&gt; = 00</u> :<br>111 = 128x (16-bit result in the ADFLxDAT register is in 12.4 format)<br>110 = 32x (15-bit result in the ADFLxDAT register is in 12.2 format)<br>101 = 8x (14-bit result in the ADFLxDAT register is in 12.2 format)<br>102 = 2x (13-bit result in the ADFLxDAT register is in 12.4 format)<br>103 = 64x (15-bit result in the ADFLxDAT register is in 12.4 format)<br>104 = 45x (16-bit result in the ADFLxDAT register is in 12.4 format)<br>105 = 64x (15-bit result in the ADFLxDAT register is in 12.2 format)<br>106 = 4x (13-bit result in the ADFLxDAT register is in 12.2 format)<br>107 = 16x (14-bit result in the ADFLxDAT register is in 12.1 format)<br>111 = 256x<br>111 = 256x<br>110 = 128x<br>101 = 64x<br>100 = 32x<br>011 = 16x<br>000 = 2x<br>bit 9 IE: Filter Common ADC Interrupt Enable bit<br>1 = Common ADC interrupt Will be generated when the filter result will be ready<br>0 = Common ADC interrupt will be generated for the filter<br>bit 8 RDY: Oversampling Filter Data Ready Flag bit<br>This bit is cleared by hardware when the result is read from the ADFLxDAT register.<br>1 = Data in the ADFLxDAT register is read from the ADFLxDAT register.<br>1 = Data in the ADFLxDAT register is read from the ADFLxDAT register.<br>1 = Data in the ADFLxDAT register is read from the ADFLxDAT register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 15                 | 1 = Filter is e                                                                                                                                                                                                                                         | nabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                         |                          |                 |                 |           |  |  |

| <ul> <li>11 = Averaging mode</li> <li>10 = Reserved</li> <li>01 = Reserved</li> <li>00 = Oversampling mode</li> <li>bit 12-10</li> <li>OVRSAM&lt;2:0&gt;: Filter Averaging/Oversampling Ratio bits</li> <li><u>If MODE&lt;1:0&gt; = 00:</u></li> <li>111 = 128x (16-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>101 = 32x (15-bit result in the ADFLxDAT register is in 12.3 format)</li> <li>101 = 8x (14-bit result in the ADFLxDAT register is in 12.1 format)</li> <li>101 = 256x (16-bit result in the ADFLxDAT register is in 12.1 format)</li> <li>011 = 256x (16-bit result in the ADFLxDAT register is in 12.1 format)</li> <li>010 = 64x (15-bit result in the ADFLxDAT register is in 12.3 format)</li> <li>001 = 16x (14-bit result in the ADFLxDAT register is in 12.3 format)</li> <li>000 = 4x (13-bit result in the ADFLxDAT register is in 12.3 format)</li> <li>001 = 16x (14-bit result in the ADFLxDAT register is in 12.1 format)</li> <li>111 = 256x</li> <li>110 = 128x</li> <li>100 = 32x</li> <li>111 = 26ax</li> <li>100 = 32x</li> <li>111 = 26ax</li> <li>100 = 32x</li> <li>111 = 18x</li> <li>100 = 32x</li> <li>111 = 16x</li> <li>110 = 128x</li> <li>111 = 100 = 100000000000000000000000000</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        | 0 = Filter is d                                                                                                                                                                                                                                         | isabled and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | e RDY bit is clea                                       | ared                     |                 |                 |           |  |  |