Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 33                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 17x12b; D/A 1x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

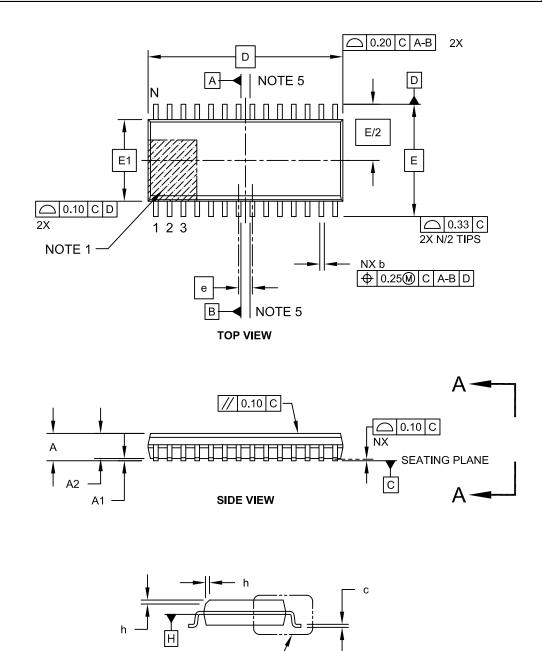

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 44-QFN (8x8)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs804t-i-ml |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, MPLAB ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) (DS51765)

- "Development Tools Design Advisory" (DS51764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS51616)

- "Using MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator" (poster) (DS51749)

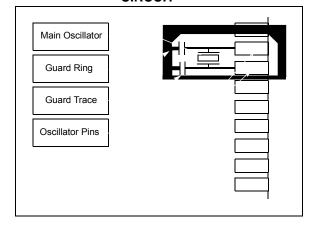

## 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| Register     | Address | All Resets                              | Register  | Address | All Resets                              | Register  | Address | All Resets                              |

|--------------|---------|-----------------------------------------|-----------|---------|-----------------------------------------|-----------|---------|-----------------------------------------|

| I2C1 and I2C | 2       |                                         | U1STA     | 222     | 000000010010000                         | SPI1BRGH  | 252     | 000000000000000000000000000000000000000 |

| I2C1CONL     | 200     | 0001000000000000                        | U1TXREG   | 224     | 0000000xxxxxxxxx                        | SPI1IMSKL | 254     | 000000000000000000000000000000000000000 |

| I2C1CONH     | 202     | 000000000000000000000000000000000000000 | U1RXREG   | 226     | 000000000000000000000000000000000000000 | SPI1IMSKH | 256     | 000000000000000000000000000000000000000 |

| I2C1STAT     | 204     | 000000000000000000000000000000000000000 | U1BRG     | 228     | 000000000000000000000000000000000000000 | SPI1URDTL | 258     | 000000000000000000000000000000000000000 |

| I2C1ADD      | 206     | 000000000000000000000000000000000000000 | U2MODE    | 230     | 000000000000000000000000000000000000000 | SPI1URDTH | 25A     | 000000000000000000000000000000000000000 |

| I2C1MSK      | 208     | 000000000000000000000000000000000000000 | U2STA     | 232     | 000000010010000                         | SPI2CON1L | 260     | 000000000000000000000000000000000000000 |

| I2C1BRG      | 20A     | 000000000000000000000000000000000000000 | U2TXREG   | 234     | 0000000xxxxxxxxx                        | SPI2CON1H | 262     | 000000000000000000000000000000000000000 |

| I2C1TRN      | 20C     | 0000000011111111                        | U2RXREG   | 236     | 000000000000000000000000000000000000000 | SPI2CON2L | 264     | 000000000000000000000000000000000000000 |

| I2C1RCV      | 20E     | 000000000000000000000000000000000000000 | U2BRG     | 238     | 000000000000000000000000000000000000000 | SPI2CON2H | 266     | 000000000000000000000000000000000000000 |

| I2C2CON1     | 210     | 0001000000000000                        | SPI       |         |                                         | SPI2STATL | 268     | 0000000000101000                        |

| I2C2CON2     | 212     | 000000000000000000000000000000000000000 | SPI1CON1L | 240     | 000000000000000000000000000000000000000 | SPI2STATH | 26A     | 000000000000000000000000000000000000000 |

| I2C2STAT     | 214     | 000000000000000000000000000000000000000 | SPI1CON1H | 242     | 000000000000000000000000000000000000000 | SPI2BUFL  | 26C     | 000000000000000000000000000000000000000 |

| I2C2ADD      | 216     | 000000000000000000000000000000000000000 | SPI1CON2L | 244     | 000000000000000000000000000000000000000 | SPI2BUFH  | 26E     | 000000000000000000000000000000000000000 |

| I2C2MSK      | 218     | 000000000000000000000000000000000000000 | SPI1CON2H | 246     | 000000000000000000000000000000000000000 | SPI3STAT  | 270     | 000xxxxxxxxxxxx                         |

| I2C2BRG      | 21A     | 000000000000000000000000000000000000000 | SPI1STATL | 248     | 000000000101000                         | SPI2BRGH  | 272     | 000000000000000000000000000000000000000 |

| I2C2TRN      | 21C     | 0000000011111111                        | SPI1STATH | 24A     | 000000000000000000000000000000000000000 | SPI2IMSKL | 274     | 000000000000000000000000000000000000000 |

| I2C2RCV      | 21E     | 000000000000000000000000000000000000000 | SPI1BUFL  | 24C     | 000000000000000000000000000000000000000 | SPI2IMSKH | 276     | 000000000000000000000000000000000000000 |

| UART1 and    | UART2   |                                         | SPI1BUFH  | 24E     | 000000000000000000000000000000000000000 | SPI2URDTL | 278     | 000000000000000000000000000000000000000 |

| U1MODE       | 220     | 000000000000000000000000000000000000000 | SPI1BRGL  | 250     | 000xxxxxxxxxxx                          | SPI2URDTH | 27A     | 000000000000000000000000000000000000000 |

TABLE 4-4: SFR BLOCK 200h

Legend: x = unknown or indeterminate value. Address values are in hexadecimal. Reset values are in binary.

## TABLE 4-5: SFR BLOCK 300h

| Register  | Address | All Resets                              | Register  | Address | All Resets         | Register  | Address | All Resets                              |

|-----------|---------|-----------------------------------------|-----------|---------|--------------------|-----------|---------|-----------------------------------------|

| ADC       |         |                                         | ADCMP0ENH | 33A     | 000000000000000000 | ADTRIG4L  | 390     | 000000000000000000000000000000000000000 |

| ADCON1L   | 300     | 000000000000000000                      | ADCMP0LO  | 33C     | 000000000000000000 | ADTRIG4H  | 392     | 000000000000000000000000000000000000000 |

| ADCON1H   | 302     | 000000001100000                         | ADCMP0HI  | 33E     | 000000000000000000 | ADCMP0CON | 3A0     | 000000000000000000000000000000000000000 |

| ADCON2L   | 304     | 000000000000000000000000000000000000000 | ADCMP1ENL | 340     | 000000000000000000 | ADCMP1CON | 3A4     | 000000000000000000000000000000000000000 |

| ADCON2H   | 306     | 000000000000000000000000000000000000000 | ADCMP1ENH | 342     | 000000000000000000 | ADBASE    | 3C0     | 000000000000000000000000000000000000000 |

| ADCON3L   | 308     | 000000000000000000000000000000000000000 | ADCMP1LO  | 344     | 000000000000000000 | ADLVLTRGL | 3D0     | 000000000000000000000000000000000000000 |

| ADCON3H   | 30A     | 000000000000000000000000000000000000000 | ADCMP1HI  | 346     | 000000000000000000 | ADLVLTRGH | 3D2     | 000000000000000000000000000000000000000 |

| ADCON4L   | 30C     | 000000000000000000000000000000000000000 | ADFL0DAT  | 368     | 000000000000000000 | ADCORE0L  | 3D4     | 000000000000000000000000000000000000000 |

| ADCON4H   | 30E     | 000000000000000000000000000000000000000 | ADFL0CON  | 36A     | 000000000000000000 | ADCORE0H  | 3D6     | 0000001100000000                        |

| ADMOD0L   | 310     | 000000000000000000000000000000000000000 | ADFL1DAT  | 36C     | 000000000000000000 | ADCORE1L  | 3D8     | 000000000000000000000000000000000000000 |

| ADMOD0H   | 312     | 000000000000000000000000000000000000000 | ADFL1CON  | 36E     | 000000000000000000 | ADCORE1H  | 3DA     | 0000001100000000                        |

| ADMOD1L   | 314     | 000000000000000000000000000000000000000 | ADTRIG0L  | 380     | 000000000000000000 | ADCORE2L  | 3DC     | 000000000000000000000000000000000000000 |

| ADIEL     | 320     | 000000000000000000000000000000000000000 | ADTRIG0H  | 382     | 000000000000000000 | ADCORE2H  | 3DE     | 0000001100000000                        |

| ADIEH     | 322     | 000000000000000000000000000000000000000 | ADTRIG1L  | 384     | 000000000000000000 | ADCORE3L  | 3E0     | 000000000000000000000000000000000000000 |

| ADCSS1L   | 328     | 000000000000000000000000000000000000000 | ADTRIG1H  | 386     | 000000000000000000 | ADCORE3H  | 3E2     | 0000001100000000                        |

| ADCSS1H   | 32A     | 000000000000000000                      | ADTRIG2L  | 388     | 000000000000000000 | ADEIEL    | 3F0     | 000000000000000000000000000000000000000 |

| ADSTATL   | 330     | 000000000000000000                      | ADTRIG2H  | 38A     | 000000000000000000 | ADEIEH    | 3F2     | 000000000000000000000000000000000000000 |

| ADSTATH   | 332     | 000000000000000000                      | ADTRIG3L  | 38C     | 000000000000000000 | ADEISTATL | 3F8     | 000000000000000000000000000000000000000 |

| ADCMP0ENL | 338     | 000000000000000000                      | ADTRIG3H  | 38E     | 000000000000000000 | ADEISTATH | 3FA     | 000000000000000000000000000000000000000 |

Legend: x = unknown or indeterminate value. Address values are in hexadecimal. Reset values are in binary.

## 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/ 80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS7000600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGS70X/80X family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGS70X/80X family CPU.

The interrupt controller has the following features:

- Six Processor Exceptions and Software Traps

- Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with a Unique Vector for each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- Fixed Interrupt Entry and Return Latencies

- Alternate Interrupt Vector Table (AIVT) for Debug Support

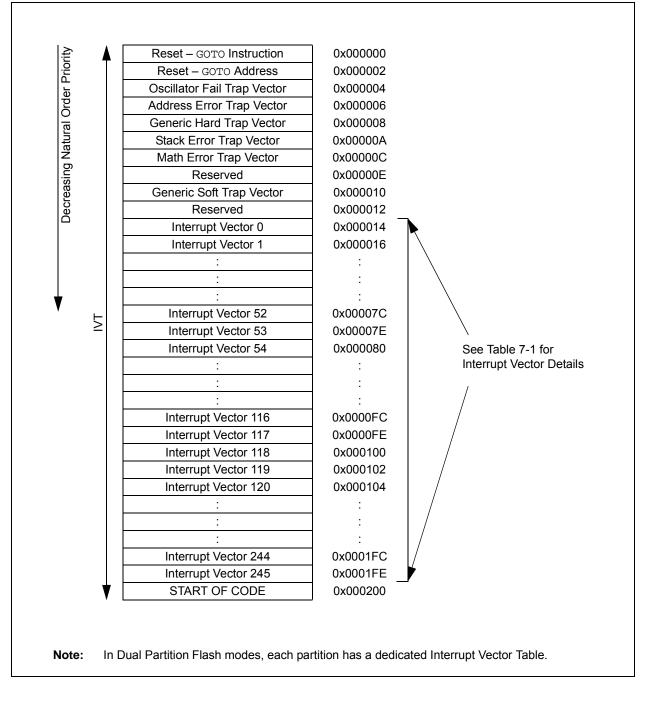

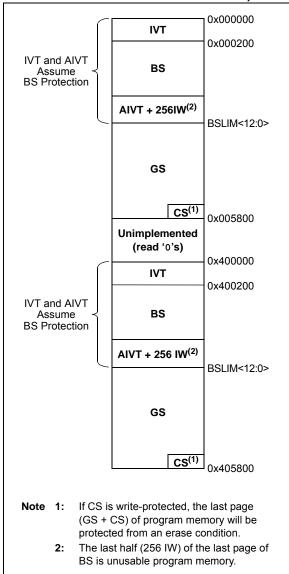

## 7.1 Interrupt Vector Table

The dsPIC33EPXXXGS70X/80X family Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory, starting at location, 000004h. The IVT contains six non-maskable trap vectors and up to 246 sources of interrupts. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

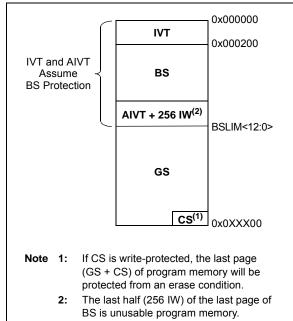

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT), shown in Figure 7-2, is available only when the Boot Segment is defined and the AIVT has been enabled. To enable the Alternate Interrupt Vector Table, the Configuration bit, AIVTDIS in the FSEC register, must be programmed and the AIVTEN bit must be set (INTCON2<8> = 1). When the AIVT is enabled, all interrupt and exception processes use the alternate vectors instead of the default vectors. The AIVT begins at the start of the last page of the Boot Segment, defined by BSLIM<12:0>. The second half of the page is no longer usable space. The Boot Segment must be at least 2 pages to enable the AIVT.

Note: Although the Boot Segment must be enabled in order to enable the AIVT, application code does not need to be present inside of the Boot Segment. The AIVT (and IVT) will inherit the Boot Segment code protection.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGS70X/80X family devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

### FIGURE 7-1: dsPIC33EPXXXGS70X/80X FAMILY INTERRUPT VECTOR TABLE

### TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

|                                   | Vector  | IRQ<br># | IVT Address       | Interrupt Bit Location |                       |                                |  |

|-----------------------------------|---------|----------|-------------------|------------------------|-----------------------|--------------------------------|--|

| Interrupt Source                  | #       |          | IVI Address       | Flag                   | Enable                | Priority                       |  |

| AN17 Conversion Done              | 168     | 160      | 0x000154          | IFS10<0><br>AN17IF     | IEC10<0><br>AN17IE    | IPC40<2:0><br>AN17IP<2:0>      |  |

| AN18 Conversion Done              | 169     | 161      | 0x000156          | IFS10<1><br>AN18IF     | IEC10<1><br>AN18IE    | IPC40<6:4><br>AN18IP<2:0>      |  |

| AN19 Conversion Done              | 170     | 162      | 0x000158          | IFS10<2><br>AN19IF     | IEC10<2><br>AN19IE    | IPC40<10:8><br>AN19IP<2:0>     |  |

| AN20 Conversion Done              | 171     | 163      | 0x00015A          | IFS10<3><br>AN20IF     | IEC10<3><br>AN20IE    | IPC40<14:12><br>AN20IP<2:0>    |  |

| AN21 Conversion Done              | 172     | 164      | 0x00015C          | IFS10<4><br>AN21IF     | IEC10<4><br>AN21IE    | IPC41<2:0><br>AN21IP<2:0>      |  |

| Reserved                          | 173-180 | 165-172  | 0x00015C-0x00016C | _                      | —                     | —                              |  |

| I2C1 – I2C1 Bus Collision         | 181     | 173      | 0x00016E          | IFS10<13><br>I2C1IF    | IEC10<13><br>I2C1IE   | IPC43<6:4><br>I2C1IP<2:0>      |  |

| I2C2 – I2C2 Bus Collision         | 182     | 174      | 0x000170          | IFS10<14><br>I2C2IF    | IEC10<14><br>I2C2IE   | IPC43<10:8><br>I2C2IP<2:0>     |  |

| Reserved                          | 183-184 | 175-176  | 0x000172-0x000174 | —                      | _                     | —                              |  |

| ADCMP0 – ADC Digital Comparator 0 | 185     | 177      | 0x000176          | IFS11<1><br>ADCMP0IF   | IEC11<1><br>ADCMP0IE  | IPC44<6:4><br>ADCMP0IP<2:0>    |  |

| ADCMP1 – ADC Digital Comparator 1 | 186     | 178      | 0x000178          | IFS11<2><br>ADCMP1IF   | IEC11<2><br>ADCMP1IE  | IPC44<10:8><br>ADCMP1IP<2:0>   |  |

| ADFLTR0 – ADC Filter 0            | 187     | 179      | 0x00017A          | IFS11<3><br>ADFLTR0IF  | IEC11<3><br>ADFLTR0IE | IPC44<14:12><br>ADFLTR0IP<2:0> |  |

| ADFLTR1 – ADC Filter 1            | 188     | 180      | 0x00017C          | IFS11<4><br>ADFLTR1IF  | IEC11<4><br>ADFLTR1IE | IPC45<2:0><br>ADFLTR1IP<2:0>   |  |

| Reserved                          | 189-253 | 181-245  | 0x00017E-0x000192 | —                      | —                     | _                              |  |

## 8.1 DMA Controller Registers

Each DMA Controller Channel x (where x = 0 through 3) contains the following registers:

- 16-Bit DMA Channel x Control Register (DMAxCON)

- 16-Bit DMA Channel x IRQ Select Register (DMAxREQ)

- 32-Bit DMA Channel x Start Address Register A (DMAxSTAL/H)

- 32-Bit DMA Channel x Start Address Register B (DMAxSTBL/H)

- 16-Bit DMA Channel x Peripheral Address Register (DMAxPAD)

- 14-Bit DMA Channel x Transfer Count Register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADRL/H) are common to all DMA Controller channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The interrupt flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding interrupt enable control bits (DMAxIE) are located in an IECx register in the interrupt controller and the corresponding interrupt priority control bits (DMAxIP) are located in an IPCx register in the interrupt controller.

### REGISTER 8-1: DMAxCON: DMA CHANNEL x CONTROL REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|--------|-------|-------|-------|-------|-----|-----|-------|

| CHEN   | SIZE  | DIR   | HALF  | NULLW | —   | —   | —     |

| bit 15 |       |       |       |       |     |     | bit 8 |

| U-0   | U-0 | R/W-0  | R/W-0  | U-0 | U-0 | R/W-0 | R/W-0 |

|-------|-----|--------|--------|-----|-----|-------|-------|

| _     | —   | AMODE1 | AMODE0 | —   | —   | MODE1 | MODE0 |

| bit 7 |     |        |        |     |     |       | bit 0 |

### Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15   | CHEN: DMA Channel Enable bit                                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Channel is enabled                                                                                                                                |

|          | 0 = Channel is disabled                                                                                                                               |

| bit 14   | SIZE: DMA Data Transfer Size bit                                                                                                                      |

|          | 1 = Byte<br>0 = Word                                                                                                                                  |

| bit 13   | DIR: Transfer Direction bit (source/destination bus select)                                                                                           |

|          | <ul> <li>1 = Reads from RAM address, writes to peripheral address</li> <li>0 = Reads from peripheral address, writes to RAM address</li> </ul>        |

| bit 12   | HALF: Block Transfer Interrupt Select bit                                                                                                             |

|          | <ul> <li>1 = Initiates interrupt when half of the data has been moved</li> <li>0 = Initiates interrupt when all of the data has been moved</li> </ul> |

| bit 11   | NULLW: Null Data Peripheral Write Mode Select bit                                                                                                     |

|          | <ul> <li>1 = Null data write to peripheral in addition to RAM write (DIR bit must also be clear)</li> <li>0 = Normal operation</li> </ul>             |

| bit 10-6 | Unimplemented: Read as '0'                                                                                                                            |

| bit 5-4  | AMODE<1:0>: DMA Channel Addressing Mode Select bits                                                                                                   |

|          | 11 = Reserved                                                                                                                                         |

|          | 10 = Peripheral Indirect mode                                                                                                                         |

|          | <ul><li>01 = Register Indirect without Post-Increment mode</li><li>00 = Register Indirect with Post-Increment mode</li></ul>                          |

| bit 3-2  | Unimplemented: Read as '0'                                                                                                                            |

| bit 1-0  | MODE<1:0>: DMA Channel Operating Mode Select bits                                                                                                     |

|          | 11 = One-Shot, Ping-Pong modes are enabled (one block transfer from/to each DMA buffer)                                                               |

|          | 10 = Continuous, Ping-Pong modes are enabled<br>01 = One-Shot, Ping-Pong modes are disabled                                                           |

|          | 00 = Continuous, Ping-Pong modes are disabled                                                                                                         |

|          |                                                                                                                                                       |

## REGISTER 8-14: DMAPPS: DMA PING-PONG STATUS REGISTER

| U-0    | U-0  | U-0  | U-0  | U-0 | U-0 | U-0 | U-0   |

|--------|------|------|------|-----|-----|-----|-------|

| —      | —    | —    | —    | —   | —   | —   | —     |

| bit 15 |      |      |      |     |     |     | bit 8 |

|        |      |      |      |     |     |     |       |

| 11.0   | 11.0 | 11.0 | 11.0 | D٥  | DA  | D۵  |       |

| U-0   | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   | R-0   |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | PPST3 | PPST2 | PPST1 | PPST0 |

| bit 7 |     |     |     |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                                                  |

|----------|---------------------------------------------------------------------------------------------|

| bit 3    | PPST3: Channel 3 Ping-Pong Mode Status Flag bit                                             |

|          | <ul><li>1 = DMA3STB register is selected</li><li>0 = DMA3STA register is selected</li></ul> |

| bit 2    | PPST2: Channel 2 Ping-Pong Mode Status Flag bit                                             |

|          | 1 = DMA2STB register is selected                                                            |

|          | 0 = DMA2STA register is selected                                                            |

| bit 1    | <b>PPST1:</b> Channel 1 Ping-Pong Mode Status Flag bit                                      |

|          | 1 = DMA1STB register is selected                                                            |

|          | 0 = DMA1STA register is selected                                                            |

| bit 0    | <b>PPST0:</b> Channel 0 Ping-Pong Mode Status Flag bit                                      |

|          | 1 = DMA0STB register is selected                                                            |

|          | 0 = DMA0STA register is selected                                                            |

| REGISTER         | 9-0. KEFU                                                                                                                                                                                                                                                  | CON. REFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LENCE USC                                                                                                                                                                                                             | ILLATOR CO            |                       | ISTER                 |                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| R/W-0            | U-0                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

| ROON             |                                                                                                                                                                                                                                                            | ROSSLP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ROSEL                                                                                                                                                                                                                 | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |

| bit 15           |                                                                                                                                                                                                                                                            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       | •                     | •                     | •                     | bit 8                 |

|                  |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| U-0              | U-0                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                   | U-0                   | U-0                   | U-0                   | U-0                   |

| <br>bit 7        | _                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       | _                     | _                     | _                     | bit (                 |

|                  |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| Legend:          |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| R = Readabl      | le bit                                                                                                                                                                                                                                                     | W = Writable I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | pit                                                                                                                                                                                                                   | U = Unimplem          | nented bit, read      | l as '0'              |                       |

| -n = Value at    | t POR                                                                                                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                       | '0' = Bit is clea     | ared                  | x = Bit is unkn       | iown                  |

| bit 15<br>bit 14 | 1 = Reference<br>0 = Reference                                                                                                                                                                                                                             | ence Oscillator<br>e oscillator outp<br>e oscillator outp<br>ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ut is enabled o<br>ut is disabled                                                                                                                                                                                     |                       | 2)                    |                       |                       |

| bit 13           | -                                                                                                                                                                                                                                                          | ference Oscilla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       | an hit                |                       |                       |                       |

| bit 15           | 1 = Reference                                                                                                                                                                                                                                              | e oscillator outp<br>oscillator outp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ut continues to                                                                                                                                                                                                       | run in Sleep          |                       |                       |                       |

| bit 12           | 1 = Oscillator                                                                                                                                                                                                                                             | rence Oscillato<br>crystal is used<br>ock is used as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | as the referen                                                                                                                                                                                                        | ce clock              |                       |                       |                       |

| bit 11-8         | 1111 = Refer<br>1110 = Refer<br>1101 = Refer<br>100 = Refer<br>1011 = Refer<br>1010 = Refer<br>1001 = Refer<br>000 = Refer<br>0111 = Refer<br>0110 = Refer<br>0101 = Refer<br>0101 = Refer<br>0101 = Refer<br>0101 = Refer<br>0100 = Refer<br>0100 = Refer | Reference Ose<br>ence clock dividence clock | ded by 32,768<br>ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 | bits <sup>(1)</sup>   |                       |                       |                       |

| bit 7-0          | Unimplement                                                                                                                                                                                                                                                | ted: Read as 'o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | )'                                                                                                                                                                                                                    |                       |                       |                       |                       |

|                  |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                       |                       |                       |                       |

#### REGISTER 9-6: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.6 "Peripheral Pin Select (PPS)" for more information.

## TABLE 11-8: PORTC REGISTER MAP<sup>(1)</sup>

|              | -      |          |             |        |        |             |             |       |       |       |           |       |       |       |       |       |

|--------------|--------|----------|-------------|--------|--------|-------------|-------------|-------|-------|-------|-----------|-------|-------|-------|-------|-------|

| File<br>Name | Bit 15 | Bit 14   | Bit 13      | Bit 12 | Bit 11 | Bit 10      | Bit 9       | Bit 8 | Bit 7 | Bit 6 | Bit 5     | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| TRISC        |        | TRISC    | C<15:12>    |        |        |             | TRISC<10:0> |       |       |       |           |       |       |       |       |       |

| PORTC        |        | RC<      | :15:12>     |        | _      |             | RC<10:0>    |       |       |       |           |       |       |       |       |       |

| LATC         |        | LATC     | <15:12>     |        | _      |             | LATC<10:0>  |       |       |       |           |       |       |       |       |       |

| ODCC         |        | ODCC     | C<15:12>    |        | _      |             | ODCC<10:0>  |       |       |       |           |       |       |       |       |       |

| CNENC        |        | CNIEC    | C<15:12>    |        | _      |             |             |       |       | CI    | NIEC<10:0 | >     |       |       |       |       |

| CNPUC        |        | CNPU     | C<15:12>    |        |        |             |             |       |       | CN    | NPUC<10:0 | )>    |       |       |       |       |

| CNPDC        |        | CNPD     | C<15:12>    |        | _      | CNPDC<10:0> |             |       |       |       |           |       |       |       |       |       |

| ANSELC       | _      | _        | —           | ANSC12 | _      | ANSC<       | <10:9>      | _     |       | ŀ     | ANSC<6:4  | >     | _     | ANSC  | <2:1> | _     |

| Logondu      |        | lomontod | read as 'o' |        |        |             |             |       |       |       |           |       |       |       |       |       |

**Legend:** — = unimplemented, read as '0'.

Note 1: Refer to Table 11-3 for bit availability on each pin count variant.

## TABLE 11-9: PORTD REGISTER MAP<sup>(1)</sup>

|              |        | ••••                                                                                                  | CCOOLE |   |   |   |  |       |         |  |       |   |   |       |   |   |

|--------------|--------|-------------------------------------------------------------------------------------------------------|--------|---|---|---|--|-------|---------|--|-------|---|---|-------|---|---|

| File<br>Name | Bit 15 | Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |        |   |   |   |  |       |         |  |       |   |   |       |   |   |

| TRISD        |        | TRISD<15:0>                                                                                           |        |   |   |   |  |       |         |  |       |   |   |       |   |   |

| PORTD        |        |                                                                                                       |        |   |   |   |  | RD<   | 15:0>   |  |       |   |   |       |   |   |

| LATD         |        | LATD<15:0>                                                                                            |        |   |   |   |  |       |         |  |       |   |   |       |   |   |

| ODCD         |        |                                                                                                       |        |   |   |   |  | ODCD  | )<15:0> |  |       |   |   |       |   |   |

| CNEND        |        |                                                                                                       |        |   |   |   |  | CNIED | 0<15:0> |  |       |   |   |       |   |   |

| CNPUD        |        |                                                                                                       |        |   |   |   |  | CNPU  | D<15:0> |  |       |   |   |       |   |   |

| CNPDD        |        |                                                                                                       |        |   |   |   |  | CNPD  | D<15:0> |  |       |   |   |       |   |   |

| ANSELD       | —      |                                                                                                       | ANSD13 | _ | _ | — |  | ANSE  | )<8:7>  |  | ANSD5 | _ | _ | ANSD2 | — | — |

**Legend:** — = unimplemented, read as '0'.

Note 1: Refer to Table 11-4 for bit availability on each pin count variant.

## REGISTER 11-3: LATX: PORTX DATA LATCH REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|----------------|-------|------------------|-------|--------------|------------------|----------|-------|

|                |       |                  | LATx  | <15:8>       |                  |          |       |

| bit 15         |       |                  |       |              |                  |          | bit 8 |

|                |       |                  |       |              |                  |          |       |

| R/W-0          | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                |       |                  | LAT   | x<7:0>       |                  |          |       |

| bit 7          |       |                  |       |              |                  |          | bit 0 |

|                |       |                  |       |              |                  |          |       |

| Legend:        |       |                  |       |              |                  |          |       |

| R = Readable b | bit   | W = Writable bit | t     | U = Unimpler | mented bit, read | l as '0' |       |

-n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown)

bit 15-8 LATx<15:0>: PORTx Data Latch bits

1 = The latch content is '1'

0 = The latch content is '0'

Note 1: See Table 11-1, Table 11-2, Table 11-3, Table 11-4 and Table 11-5 for individual bit availability in this register.

## **REGISTER 11-4:** ODCx: PORTx OPEN-DRAIN CONTROL REGISTER<sup>(1)</sup>

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------------------------------------------------------------------------|-------|-------|-------|------------------------------------|-------|-------|-------|--|--|

|                                                                            |       |       | ODC   | x<15:8>                            |       |       |       |  |  |

| bit 15                                                                     |       |       |       |                                    |       |       | bit 8 |  |  |

|                                                                            |       |       |       |                                    |       |       |       |  |  |

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                                                            |       |       | ODO   | Cx<7:0>                            |       |       |       |  |  |

| bit 7                                                                      |       |       |       |                                    |       |       | bit 0 |  |  |

|                                                                            |       |       |       |                                    |       |       |       |  |  |

| Legend:                                                                    |       |       |       |                                    |       |       |       |  |  |

| R = Readable bit W = Writable bit                                          |       |       |       | U = Unimplemented bit, read as '0' |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |       |       | nown                               |       |       |       |  |  |

bit 15-8 **PORTx<15:0>:** PORTx Open-Drain Control bits

1 = The pin acts as an open-drain output pin if TRISx is '0'

0 = The pin acts as a normal pin

Note 1: See Table 11-1, Table 11-2, Table 11-3, Table 11-4 and Table 11-5 for individual bit availability in this register.

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| T1CKR7 | T1CKR6 | T1CKR5 | T1CKR4 | T1CKR3 | T1CKR2 | T1CKR1 | T1CKR0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| U-0    |

#### REGISTER 11-11: RPINR2: PERIPHERAL PIN SELECT INPUT REGISTER 2

|         | — | _ | _ | — | — | — | —     |

|---------|---|---|---|---|---|---|-------|

| bit 7   |   |   |   |   |   |   | bit 0 |

|         |   |   |   |   |   |   |       |

| Legend: |   |   |   |   |   |   |       |

| Logona.           |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 15-8 **T1CKR<7:0>:** Assign Timer1 External Clock (T1CK) to the Corresponding RPn Pin bits See Table 11-11 which contains a list of remappable inputs for the index value. bit 7-0 **Unimplemented:** Read as '0'

#### REGISTER 11-12: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| T3CKR7 | T3CKR6 | T3CKR5 | T3CKR4 | T3CKR3 | T3CKR2 | T3CKR1 | T3CKR0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-0  |

| bit 7  |        |        |        |        |        |        | bit 0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| T2CKR7 | T2CKR6 | T2CKR5 | T2CKR4 | T2CKR3 | T2CKR2 | T2CKR1 | T2CKR0 |

| R/W-0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8T3CKR<7:0>: Assign Timer3 External Clock (T3CK) to the Corresponding RPn Pin bits<br/>See Table 11-11 which contains a list of remappable inputs for the index value.bit 7-0T2CKR<7:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn Pin bits<br/>See Table 11-11 which contains a list of remappable inputs for the index value.

© 2016-2017 Microchip Technology Inc.

## REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCIx feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

#### REGISTER 16-2: PTCON2: PWMx CLOCK DIVIDER SELECT REGISTER

| U-0             | U-0 | U-0              | U-0 | U-0               | U-0                                 | U-0         | U-0   |  |

|-----------------|-----|------------------|-----|-------------------|-------------------------------------|-------------|-------|--|

| _               | —   | —                | —   | —                 | —                                   | —           | —     |  |

| bit 15          |     |                  |     |                   |                                     |             | bit 8 |  |

|                 |     |                  |     |                   |                                     |             |       |  |

| U-0             | U-0 | U-0              | U-0 | U-0               | R/W-0                               | R/W-0       | R/W-0 |  |

|                 | _   | _                | —   | —                 | F                                   | CLKDIV<2:0> | (1)   |  |

| bit 7           |     |                  |     |                   |                                     |             | bit 0 |  |

|                 |     |                  |     |                   |                                     |             |       |  |

| Legend:         |     |                  |     |                   |                                     |             |       |  |

| R = Readable    | bit | W = Writable b   | oit | U = Unimplem      | ented bit, read                     | as '0'      |       |  |

| -n = Value at I | POR | '1' = Bit is set |     | '0' = Bit is clea | = Bit is cleared x = Bit is unknown |             |       |  |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

111 = Reserved

- 110 = Divide-by-64, maximum PWM timing resolution

- 101 = Divide-by-32, maximum PWM timing resolution

- 100 = Divide-by-16, maximum PWM timing resolution

- 011 = Divide-by-8, maximum PWM timing resolution

- 010 = Divide-by-4, maximum PWM timing resolution

- 001 = Divide-by-2, maximum PWM timing resolution

- 000 = Divide-by-1, maximum PWM timing resolution (power-on default)

**Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| R/W-0                   | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                                                          | U-0                                                                                                                                      | R/W-0                                                                            | R/W-0            | R/W-0           | R/W-0     |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------|-----------------|-----------|--|--|--|

| HRPDIS                  | HRDDIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                              |                                                                                                                                          | BLANKSEL3                                                                        | BLANKSEL2        | BLANKSEL1       | BLANKSELO |  |  |  |

| bit 15                  | TIRDDIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                              |                                                                                                                                          | DEANICOLLU                                                                       | DEANICOLLZ       | DEANINOLLI      | bit 8     |  |  |  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                          |                                                                                  |                  |                 | 5110      |  |  |  |

| U-0                     | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                                                                                                                        | R/W-0                                                                                                                                    | R/W-0                                                                            | R/W-0            | R/W-0           | R/W-0     |  |  |  |

| —                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CHOPSEL3                                                                                                                                                     | CHOPSEL2                                                                                                                                 | CHOPSEL1                                                                         | CHOPSEL0         | CHOPHEN         | CHOPLEN   |  |  |  |

| bit 7                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                          |                                                                                  | •                |                 | bit 0     |  |  |  |