Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 33                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | ·                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 17x12b; D/A 1x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

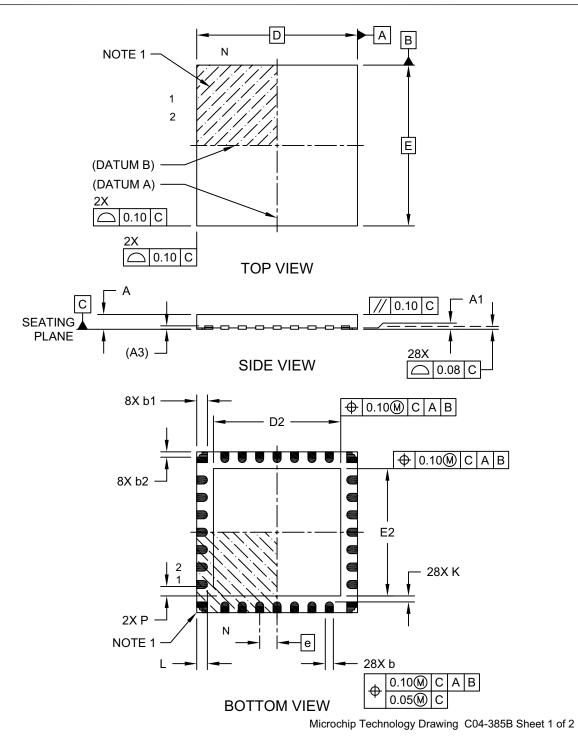

| Package / Case             | 44-TQFP                                                                           |

| Supplier Device Package    | 44-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs804t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

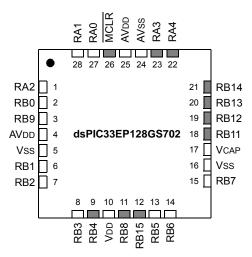

### **Pin Diagrams (Continued)**

#### 28-Pin QFN-S, UQFN

| Pin | Pin Function                              | Pin | Pin Function                              |

|-----|-------------------------------------------|-----|-------------------------------------------|

| 1   | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2    | 15  | PGEC1/AN21/SDA1/RP39/RB7                  |

| 2   | AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0           | 16  | Vss                                       |

| 3   | AN4/CMP2C/CMP3A/ISRC4/RP41/RB9            | 17  | VCAP                                      |

| 4   | AVDD                                      | 18  | TMS/PWM3H/ <b>RP46</b> /RB11              |

| 5   | Vss                                       | 19  | TCK/PWM3L/ <b>RP44</b> /RB12              |

| 6   | OSCI/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1  | 20  | PWM2H/ <b>RP45</b> /RB13                  |

| 7   | OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2 | 21  | PWM2L/ <b>RP46</b> /RB14                  |

| 8   | PGED2/DACOUT1/AN18/INT0/RP35/RB3          | 22  | PWM1H/ <b>RP20</b> /RA4                   |

| 9   | PGEC2/ADTRG31/EXTREF1/ <b>RP36</b> /RB4   | 23  | PWM1L/ <b>RP19</b> /RA3                   |

| 10  | VDD                                       | 24  | AVss                                      |

| 11  | PGED3/SDA2/FLT31/ <b>RP40</b> /RB8        | 25  | AVDD                                      |

| 12  | PGEC3/SCL2/RP47/RB15                      | 26  | MCLR                                      |

| 13  | TDO/AN19/PGA2N2/ <b>RP37</b> /RB5         | 27  | AN0/CMP1A/PGA1P1/RP16/RA0                 |

| 14  | PGED1/TDI/AN20/SCL1/RP38/RB6              | 28  | AN1/CMP1B/PGA1P2/PGA2P1/ <b>RP17</b> /RA1 |

Legend: Shaded pins are up to 5 VDC tolerant.

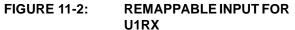

RPn represents remappable peripheral functions. See Table 11-12 and Table 11-13 for the complete list of remappable sources.

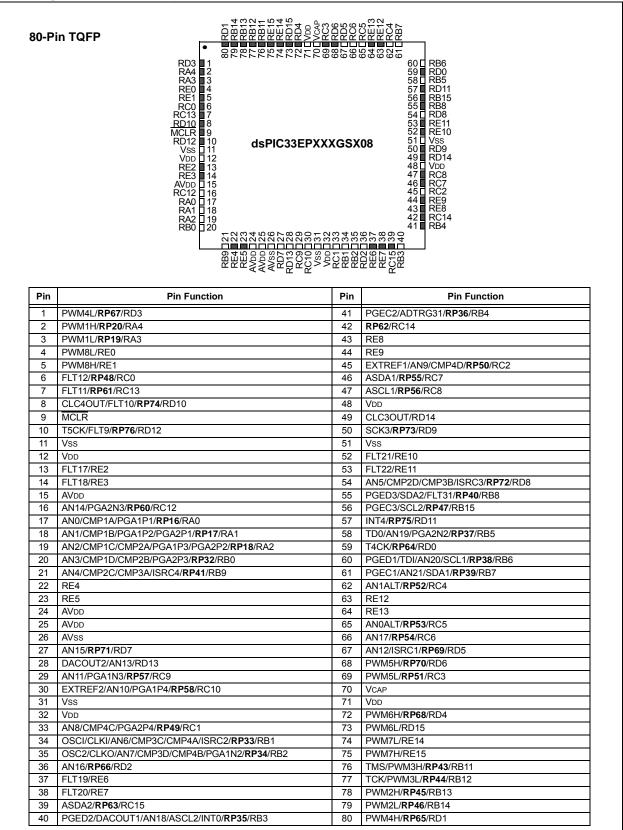

### Pin Diagrams (Continued)

|                                                                                                           | RB6<br>RB5<br>R815                                                                                                                                                                                                                                                                                                                                                                                           | KB8<br>VDD<br>VSS                                                                                                          | RC7<br>RC7<br>RB4<br>RB3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              | 4 4 %                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                           | RB7 1                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            | 33 RB2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                           | RC4 2                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            | 32 RB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                           | RC5 3                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            | 31 🛛 RC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                           | RC6 4                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            | <sup>30</sup> Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                           | RC3                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                            | 29 VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              | IC33EPX                                                                                                                    | <b>XXGSX04</b> 28 RC10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            | 27 🛛 RC9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                           | RB11 8                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                           | RB12 9                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            | 25 RB9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                           | RB13 10                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                            | 24 RB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                           | RB14 11                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                            | <sup>23</sup> RA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                           | 4 0 C                                                                                                                                                                                                                                                                                                                                                                                                        | RC13<br>AVss<br>AVbb                                                                                                       | AVDD<br>RC12<br>RA0<br>RA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Pin                                                                                                       | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                 | Pin                                                                                                                        | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1                                                                                                         | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7                                                                                                                                                                                                                                                                                                                                                                            | 23                                                                                                                         | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1<br>2                                                                                                    | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4                                                                                                                                                                                                                                                                                                                                                | 23<br>24                                                                                                                   | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2<br>AN3/CMP1D/CMP2B/PGA2P3/ <b>RP32</b> /RB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1                                                                                                         | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5                                                                                                                                                                                                                                                                                                                    | 23<br>24<br>25                                                                                                             | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1<br>2<br>3                                                                                               | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4                                                                                                                                                                                                                                                                                                                                                | 23<br>24                                                                                                                   | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2<br>AN3/CMP1D/CMP2B/PGA2P3/ <b>RP32</b> /RB0<br>AN4/CMP2C/CMP3A/ISRC4/ <b>RP41</b> /RB9                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1<br>2<br>3<br>4                                                                                          | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6                                                                                                                                                                                                                                                                                          | 23<br>24<br>25<br>26                                                                                                       | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2<br>AN3/CMP1D/CMP2B/PGA2P3/ <b>RP32</b> /RB0<br>AN4/CMP2C/CMP3A/ISRC4/ <b>RP41</b> /RB9<br>AVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1<br>2<br>3<br>4<br>5                                                                                     | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3                                                                                                                                                                                                                                                                      | 23<br>24<br>25<br>26<br>27                                                                                                 | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2<br>AN3/CMP1D/CMP2B/PGA2P3/ <b>RP32</b> /RB0<br>AN4/CMP2C/CMP3A/ISRC4/ <b>RP41</b> /RB9<br>AVDD<br>AN11/PGA1N3/ <b>RP57</b> /RC9                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1<br>2<br>3<br>4<br>5<br>6                                                                                | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3<br>Vss                                                                                                                                                                                                                                                               | 23<br>24<br>25<br>26<br>27<br>28                                                                                           | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2<br>AN3/CMP1D/CMP2B/PGA2P3/ <b>RP32</b> /RB0<br>AN4/CMP2C/CMP3A/ISRC4/ <b>RP41</b> /RB9<br>AVDD<br>AN11/PGA1N3/ <b>RP57</b> /RC9<br>EXTREF2/AN10/PGA1P4/ <b>RP58</b> /RC10                                                                                                                                                                                                                                                                                                                                                                                 |

| 1<br>2<br>3<br>4<br>5<br>6<br>7                                                                           | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3<br>Vss<br>VcaP                                                                                                                                                                                                                                                       | 23<br>24<br>25<br>26<br>27<br>28<br>28<br>29                                                                               | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/ <b>RP18</b> /RA2<br>AN3/CMP1D/CMP2B/PGA2P3/ <b>RP32</b> /RB0<br>AN4/CMP2C/CMP3A/ISRC4/ <b>RP41</b> /RB9<br>AVDD<br>AN11/PGA1N3/ <b>RP57</b> /RC9<br>EXTREF2/AN10/PGA1P4/ <b>RP58</b> /RC10<br>VDD                                                                                                                                                                                                                                                                                                                                                                          |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8                                                                      | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3<br>Vss<br>VcAP<br>TMS/PWM3H/ <b>RP43</b> /RB11                                                                                                                                                                                                                       | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30                                                                               | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2           AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0           AN4/CMP2C/CMP3A/ISRC4/RP41/RB9           AVDD           AN11/PGA1N3/RP57/RC9           EXTREF2/AN10/PGA1P4/RP58/RC10           VDD           VSS                                                                                                                                                                                                                                                                                                                                                               |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9                                                                 | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3<br>Vss<br>VcAP<br>TMS/PWM3H/ <b>RP43</b> /RB11<br>TCK/PWM3L/ <b>RP44</b> /RB12                                                                                                                                                                                       | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31                                                                         | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2           AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0           AN4/CMP2C/CMP3A/ISRC4/RP41/RB9           AVDD           AN11/PGA1N3/RP57/RC9           EXTREF2/AN10/PGA1P4/RP58/RC10           VDD           VSS           AN8/CMP4C/PGA2P4/RP49/RC1                                                                                                                                                                                                                                                                                                                           |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12                                               | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3<br>Vss<br>VcAP<br>TMS/PWM3H/ <b>RP43</b> /RB11<br>TCK/PWM3L/ <b>RP44</b> /RB12<br>PWM2H/ <b>RP45</b> /RB13<br>PWM2L/ <b>RP46</b> /RB14<br>PWM1H/ <b>RP20</b> /RA4                                                                                                    | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>33                                                 | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2           AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0           AN4/CMP2C/CMP3A/ISRC4/RP41/RB9           AVDD           AN11/PGA1N3/RP57/RC9           EXTREF2/AN10/PGA1P4/RP58/RC10           VDD           VSS           AN8/CMP4C/PGA2P4/RP49/RC1           OSC2/CLK0/AN7/CMP3D/CMP4A/ISRC2/RP33/RB1           OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2           PGED2/DACOUT1/AN18/INT0/RP35/RB3                                                                                                                                                                         |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13                                         | PGEC1/AN21/SDA1/RP39/RB7         AN1ALT/RP52/RC4         AN0ALT/RP53/RC5         AN17/RP54/RC6         RP51/RC3         Vss         Vcap         TMS/PWM3H/RP43/RB11         TCK/PWM3L/RP44/RB12         PWM2L/RP46/RB13         PWM1L/RP46/RB14         PWM1L/RP19/RA3                                                                                                                                      | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>34<br>35                                           | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2           AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0           AN4/CMP2C/CMP3A/ISRC4/RP41/RB9           AVD           AN11/PGA1N3/RP57/RC9           EXTREF2/AN10/PGA1P4/RP58/RC10           VDD           VSS           AN8/CMP4C/PGA2P4/RP49/RC1           OSCI/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1           OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2           PGED2/DACOUT1/AN18/INT0/RP35/RB3           PGEC2/ADTRG31/RP36/RB4                                                                                                                                         |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14                                   | PGEC1/AN21/SDA1/RP39/RB7         AN1ALT/RP52/RC4         AN0ALT/RP53/RC5         AN17/RP54/RC6         RP51/RC3         Vcap         TMS/PWM3H/RP43/RB11         TCK/PWM3L/RP44/RB12         PWM2L/RP46/RB13         PWM1L/RP46/RB14         PWM1L/RP19/RA3         FLT12/RP48/RC0                                                                                                                           | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>34<br>35<br>36                                     | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2           AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0           AN4/CMP2C/CMP3A/ISRC4/RP41/RB9           AVD           AN1/PGA1N3/RP57/RC9           EXTREF2/AN10/PGA1P4/RP58/RC10           VDD           VSS           AN8/CMP4C/PGA2P4/RP49/RC1           OSCI/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1           OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2           PGED2/DACOUT1/AN18/INT0/RP35/RB3           PGEC2/ADTRG31/RP36/RB4           EXTREF1/AN9/CMP4D/RP50/RC2                                                                                                     |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>9<br>10<br>11<br>12<br>13<br>14<br>15                        | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3<br>Vss<br>Vcap<br>TMS/PWM3H/ <b>RP43</b> /RB11<br>TCK/PWM3L/ <b>RP44</b> /RB12<br>PWM2H/ <b>RP45</b> /RB13<br>PWM2L/ <b>RP46</b> /RB14<br>PWM1H/ <b>RP20</b> /RA4<br>PWM1L/ <b>RP19</b> /RA3<br>FLT12/ <b>RP48</b> /RC0<br>FLT11/ <b>RP61</b> /RC13                  | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>33<br>34<br>35<br>36<br>37                         | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2           AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0           AN4/CMP2C/CMP3A/ISRC4/RP41/RB9           AVD           AN1/PGA1N3/RP57/RC9           EXTREF2/AN10/PGA1P4/RP58/RC10           VDD           VSS           AN8/CMP4C/PGA2P4/RP49/RC1           OSCI/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1           OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2           PGED2/DACOUT1/AN18/INT0/RP35/RB3           PGEC2/ADTRG31/RP36/RB4           EXTREF1/AN9/CMP4D/RP50/RC2           ASDA1/RP55/RC7                                                                            |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16                  | PGEC1/AN21/SDA1/RP39/RB7           AN1ALT/RP52/RC4           AN0ALT/RP53/RC5           AN17/RP54/RC6           RP51/RC3           Vss           Vcap           TMS/PWM3H/RP43/RB11           TCK/PWM3L/RP44/RB12           PWM2H/RP45/RB13           PWM2L/RP46/RB14           PWM1L/RP19/RA3           FLT12/RP48/RC0           FLT11/RP61/RC13           AVss                                              | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>33<br>34<br>35<br>36<br>36<br>37<br>38             | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2           AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0           AN4/CMP2C/CMP3A/ISRC4/RP41/RB9           AVD           AVDD           AN11/PGA1N3/RP57/RC9           EXTREF2/AN10/PGA1P4/RP58/RC10           VDD           VSS           AN8/CMP4C/PGA2P4/RP49/RC1           OSCI/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1           OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2           PGED2/DACOUT1/AN18/INT0/RP35/RB3           PGEC2/ADTRG31/RP36/RB4           EXTREF1/AN9/CMP4D/RP50/RC2           ASDA1/RP55/RC7           ASCL1/RP56/RC8                                   |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17            | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7<br>AN1ALT/ <b>RP52</b> /RC4<br>AN0ALT/ <b>RP53</b> /RC5<br>AN17/ <b>RP54</b> /RC6<br><b>RP51</b> /RC3<br>Vss<br>VcAP<br>TMS/PWM3H/ <b>RP43</b> /RB11<br>TCK/PWM3L/ <b>RP44</b> /RB12<br>PWM2H/ <b>RP45</b> /RB13<br>PWM2L/ <b>RP46</b> /RB14<br>PWM1L/ <b>RP46</b> /RB14<br>PWM1L/ <b>RP19</b> /RA3<br>FLT12/ <b>RP48</b> /RC0<br>FLT11/ <b>RP61</b> /RC13<br>AVss<br>AVDD | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>33<br>34<br>35<br>36<br>36<br>37<br>38<br>39       | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2           AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0           AN4/CMP2C/CMP3A/ISRC4/RP41/RB9           AVD           AN1/PGA1N3/RP57/RC9           EXTREF2/AN10/PGA1P4/RP58/RC10           VDD           VSS           AN8/CMP4C/PGA2P4/RP49/RC1           OSC2/CLK0/AN7/CMP3D/CMP4A/ISRC2/RP33/RB1           OSC2/CLK0/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2           PGED2/DACOUT1/AN18/INT0/RP35/RB3           PGEC2/ADTRG31/RP36/RB4           EXTREF1/AN9/CMP4D/RP50/RC2           ASDA1/RP55/RC7           ASCL1/RP56/RC8           Vss                                     |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>7<br>8<br>9<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 | PGEC1/AN21/SDA1/RP39/RB7           AN1ALT/RP52/RC4           AN0ALT/RP53/RC5           AN17/RP54/RC6           RP51/RC3           Vss           VCAP           TMS/PWM3H/RP43/RB11           TCK/PWM3L/RP44/RB12           PWM2H/RP45/RB13           PWM2L/RP46/RB14           PWM1L/RP19/RA3           FLT12/RP48/RC0           FLT11/RP61/RC13           AVss           AVod           MCLR                | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40       | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2           AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0           AN4/CMP2C/CMP3A/ISRC4/RP41/RB9           AVD           AN1/PGA1N3/RP57/RC9           EXTREF2/AN10/PGA1P4/RP58/RC10           VD           VSS           AN8/CMP4C/PGA2P4/RP49/RC1           OSC2/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1           OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2           PGED2/DACOUT1/AN18/INT0/RP35/RB3           PGEC2/ADTRG31/RP36/RB4           EXTREF1/AN9/CMP4D/RP50/RC2           ASDA1/RP55/RC7           ASSCL1/RP56/RC8           VbD                                     |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19     | PGEC1/AN21/SDA1/RP39/RB7           AN1ALT/RP52/RC4           AN0ALT/RP53/RC5           AN17/RP54/RC6           RP51/RC3           Vss           VCAP           TMS/PWM3H/RP43/RB11           TCK/PWM3L/RP44/RB12           PWM2H/RP45/RB13           PWM2L/RP46/RB14           PWM1L/RP19/RA3           FLT12/RP48/RC0           FLT11/RP61/RC13           AVbd           MCLR           AVdd                | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41 | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2           AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0           AN4/CMP2C/CMP3A/ISRC4/RP41/RB9           AVD           AN1/PGA1N3/RP57/RC9           EXTREF2/AN10/PGA1P4/RP58/RC10           Vbb           VSS           AN8/CMP4C/PGA2P4/RP49/RC1           OSC2/CLK0/AN7/CMP3D/CMP4A/ISRC2/RP33/RB1           OSC2/CLK0/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2           PGED2/DACOUT1/AN18/INT0/RP35/RB3           PGEC2/ADTRG31/RP36/RB4           EXTREF1/AN9/CMP4D/RP50/RC2           ASDA1/RP55/RC7           ASSL1/RP56/RC8           VbD           PGED3/SDA2/FLT31/RP40/RB8 |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>7<br>8<br>9<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 | PGEC1/AN21/SDA1/RP39/RB7           AN1ALT/RP52/RC4           AN0ALT/RP53/RC5           AN17/RP54/RC6           RP51/RC3           Vss           VCAP           TMS/PWM3H/RP43/RB11           TCK/PWM3L/RP44/RB12           PWM2H/RP45/RB13           PWM2L/RP46/RB14           PWM1L/RP19/RA3           FLT12/RP48/RC0           FLT11/RP61/RC13           AVss           AVod           MCLR                | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32<br>33<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40       | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2           AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0           AN4/CMP2C/CMP3A/ISRC4/RP41/RB9           AVD           AN1/PGA1N3/RP57/RC9           EXTREF2/AN10/PGA1P4/RP58/RC10           VDD           VSS           AN8/CMP4C/PGA2P4/RP49/RC1           OSC2/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1           OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/RP34/RB2           PGED2/DACOUT1/AN18/INT0/RP35/RB3           PGEC2/ADTRG31/RP36/RB4           EXTREF1/AN9/CMP4D/RP50/RC2           ASDA1/RP55/RC7           ASSCL1/RP56/RC8           VbD                                    |

Legend: Shaded pins are up to 5 VDC tolerant. RPn represents remappable peripheral functions. See Table 11-12 and Table 11-13 for the complete list of remappable sources.

### **Pin Diagrams (Continued)**

Legend: Shaded pins are up to 5 VDC tolerant.

**RPn** represents remappable peripheral functions. See Table 11-12 and Table 11-13 for the complete list of remappable sources.

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-n (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16                       | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default Oscillator mode for an unprogrammed (erased) device.

#### 9.2 Auxiliary Clock Generation

The auxiliary clock generation is used for peripherals that need to operate at a frequency unrelated to the system clock, such as PWM or ADC.

The primary oscillator and internal FRC oscillator sources can be used with an Auxiliary PLL (APLL) to obtain the auxiliary clock. The Auxiliary PLL has a fixed 16x multiplication factor.

The auxiliary clock has the following configuration restrictions:

- For proper PWM operation, auxiliary clock generation must be configured for 120 MHz (see Parameter OS56 in Section 30.0 "Electrical Characteristics"). If a slower frequency is desired, the PWM Input Clock Prescaler (Divider) Select bits (PCLKDIV<2:0>) should be used.

- To achieve 1.04 ns PWM resolution, the auxiliary clock must use the 16x Auxiliary PLL (APLL). All other clock sources will have a minimum PWM resolution of 8 ns.

- If the primary PLL is used as a source for the auxiliary clock, the primary PLL should be configured up to a maximum operation of 30 MIPS or less.

### 9.3 Reference Clock Generation

The reference clock output logic provides the user with the ability to output a clock signal based on the system clock or the crystal oscillator on a device pin. The user application can specify a wide range of clock scaling prior to outputting the reference clock.

### 9.4 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 9.4.1 KEY RESOURCES

- "Oscillator Module" (DS70005131) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| REGISTER         | 9-0. KEFU                                                                                                                                                                                                                                                  | CON. REFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LENCE USC                                                                                                                                                                                                             | ILLATOR CO            |                       | ISTER                 |                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| R/W-0            | U-0                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

| ROON             |                                                                                                                                                                                                                                                            | ROSSLP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ROSEL                                                                                                                                                                                                                 | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |

| bit 15           |                                                                                                                                                                                                                                                            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       | •                     | •                     | •                     | bit 8                 |

|                  |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| U-0              | U-0                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                   | U-0                   | U-0                   | U-0                   | U-0                   |

| <br>bit 7        | _                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       | _                     | _                     | _                     | bit (                 |

|                  |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| Legend:          |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| R = Readabl      | le bit                                                                                                                                                                                                                                                     | W = Writable I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | pit                                                                                                                                                                                                                   | U = Unimplem          | nented bit, read      | l as '0'              |                       |

| -n = Value at    | t POR                                                                                                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                       | '0' = Bit is clea     | ared                  | x = Bit is unkn       | iown                  |

| bit 15<br>bit 14 | 1 = Reference<br>0 = Reference                                                                                                                                                                                                                             | ence Oscillator<br>e oscillator outp<br>e oscillator outp<br>ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ut is enabled o<br>ut is disabled                                                                                                                                                                                     |                       | 2)                    |                       |                       |

| bit 13           | -                                                                                                                                                                                                                                                          | ference Oscilla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       | an hit                |                       |                       |                       |

| bit 15           | 1 = Reference                                                                                                                                                                                                                                              | e oscillator outp<br>oscillator outp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ut continues to                                                                                                                                                                                                       | run in Sleep          |                       |                       |                       |

| bit 12           | 1 = Oscillator                                                                                                                                                                                                                                             | rence Oscillato<br>crystal is used<br>ock is used as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | as the referen                                                                                                                                                                                                        | ce clock              |                       |                       |                       |