Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 51                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

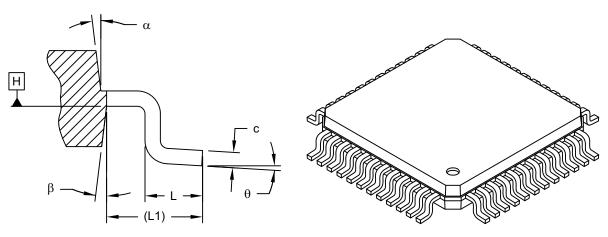

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs806-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Communication Interfaces**

- Two UART modules (15 Mbps):

- Supports LIN/J2602 protocols and IrDA®

- Three Variable Width SPI modules with Operating modes:

- 3-wire SPI

- 8x16 or 8x8 FIFO mode

- I<sup>2</sup>S mode

- Two I<sup>2</sup>C modules (up to 1 Mbaud) with SMBus Support

- Up to Two CAN modules

- Four-Channel DMA

#### Input/Output

- Constant-Current Source (10 µA nominal)

- Sink/Source up to 12 mA/15 mA, respectively; Pin-Specific for Standard VOH/VOL

- 5V Tolerant Pins

- · Selectable, Open-Drain Pull-ups and Pull-Downs

- External Interrupts on all I/O Pins

- Peripheral Pin Select (PPS) to allow Function Remap with Six Virtual I/Os

#### **Qualification and Class B Support**

- AEC-Q100 REVG (Grade 1, -40°C to +125°C)

- Class B Safety Library, IEC 60730

- The 6x6x0.55 mm UQFN Package is Designed and Optimized to ease IPC9592B 2nd Level Temperature Cycle Qualification

#### **Debugger Development Support**

- In-Circuit and In-Application Programming

- Five Program and Three Complex Data Breakpoints

- IEEE 1149.2 Compatible (JTAG) Boundary Scan

- Trace and Run-Time Watch

#### **Digital Peripherals**

- Four Configurable Logic Cells

- Peripheral Trigger Generator

|                   |      | rtes                 |             | (GPIO)                |                       | Re            | ma             | ppal | ole F | Perip              | hera                               | als |                 |                  |     |     | 12-<br>A[     | -            |     |     | r                 |            | Source               |                         |

|-------------------|------|----------------------|-------------|-----------------------|-----------------------|---------------|----------------|------|-------|--------------------|------------------------------------|-----|-----------------|------------------|-----|-----|---------------|--------------|-----|-----|-------------------|------------|----------------------|-------------------------|

| Device            | Pins | Program Memory Bytes | RAM (Bytes) | General Purpose I/O ( | Timers <sup>(1)</sup> | Input Capture | Output Compare | UART | IdS   | PWM <sup>(2)</sup> | External Interrupts <sup>(3)</sup> | CAN | Reference Clock | 1 <sup>2</sup> C | CLC | ÐLd | Analog Inputs | S&H Circuits | V9d | AMA | Analog Comparator | DAC Output | Constant-Current Sou | Packages                |

| dsPIC33EP128GS702 | 28   | 128K                 | 8K          | 20                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 11            | 5            | 2   | 0   | 4                 | 1          | 1                    | SOIC,<br>QFN-S,<br>UQFN |

| dsPIC33EP64GS804  | 44   | 64K                  | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 4   | 4                 | 1          | 1                    |                         |

| dsPIC33EP128GS704 | 44   | 128K                 | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 0   | 4                 | 1          | 1                    | QFN,<br>TQFP            |

| dsPIC33EP128GS804 | 44   | 128K                 | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 4   | 4                 | 1          | 1                    | i Qi i                  |

| dsPIC33EP64GS805  | 48   | 64K                  | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 4   | 4                 | 1          | 1                    |                         |

| dsPIC33EP128GS705 | 48   | 128K                 | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 0   | 4                 | 1          | 1                    | TQFP                    |

| dsPIC33EP128GS805 | 48   | 128K                 | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 4   | 4                 | 1          | 1                    |                         |

| dsPIC33EP64GS806  | 64   | 64K                  | 8K          | 51                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 4   | 4                 | 2          | 1                    |                         |

| dsPIC33EP128GS706 | 64   | 128K                 | 8K          | 51                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 0   | 4                 | 2          | 1                    | TQFP                    |

| dsPIC33EP128GS806 | 64   | 128K                 | 8K          | 51                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 4   | 4                 | 2          | 1                    |                         |

| dsPIC33EP64GS708  | 80   | 64K                  | 8K          | 67                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 0   | 4                 | 2          | 1                    |                         |

| dsPIC33EP64GS808  | 80   | 64K                  | 8K          | 67                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 4   | 4                 | 2          | 1                    | TQFP                    |

| dsPIC33EP128GS708 | 80   | 128K                 | 8K          | 67                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 0   | 4                 | 2          |                      | IQFP                    |

| dsPIC33EP128GS808 | 80   | 128K                 | 8K          | 67                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 4   | 4                 | 2          | 1                    |                         |

Note 1: The external clock for Timer1, Timer2 and Timer3 is remappable.

2: PWM4 through PWM8 are remappable on 28/44/48-pin devices; on 64-pin devices, only PWM7/PWM8 are remappable.

**3:** External interrupts, INT0 and INT4, are not remappable.

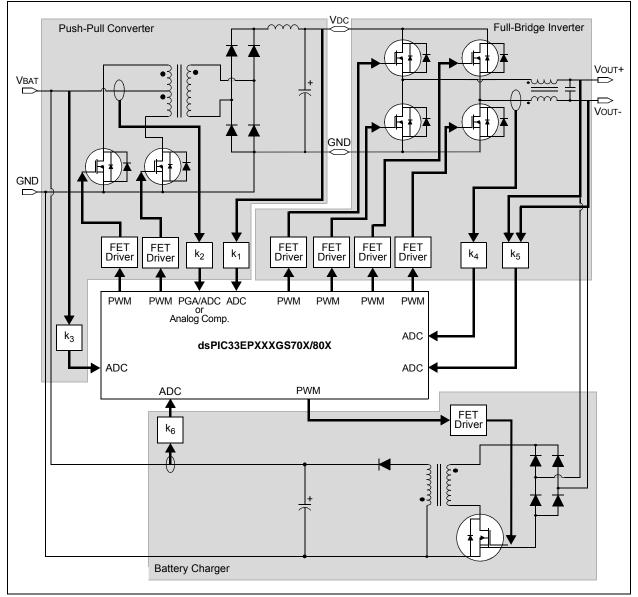

#### FIGURE 2-6: OFF-LINE UPS

### 4.6.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions, and the DSP accumulator class of instructions, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

- **Note:** Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.6.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the MAC class of instructions:

- Register Indirect

- · Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.6.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

#### 4.7 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a Bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.7.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-2).

Note: Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.7.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags, as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W (XWM) register, to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-2). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W (YWM) register, to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit (MODCON<14>) is set.

#### FIGURE 4-10: MODULO ADDRESSING OPERATION EXAMPLE

| Byte<br>Address<br>0x1100 |                                                                   | MOV<br>MOV<br>MOV | #0x1100, W0<br>W0, XMODSRT<br>#0x1163, W0 | ;set modulo start address                             |

|---------------------------|-------------------------------------------------------------------|-------------------|-------------------------------------------|-------------------------------------------------------|

| 0x1100                    |                                                                   | MOV               | W0, MODEND<br>#0x8001, W0                 | ;set modulo end address                               |

|                           |                                                                   | MOV               | W0, MODCON                                | ;enable W1, X AGU for modulo                          |

|                           | ♥ ( )                                                             | MOV               |                                           |                                                       |

| 0x1163                    | $\square$                                                         | MOV               | #0x1110, W1                               | ;point W1 to buffer                                   |

|                           |                                                                   | DO<br>MOV         | AGAIN, #0x31<br>W0, [W1++]                | ;fill the 50 buffer locations ;fill the next location |

|                           | Start Addr = 0x1100<br>End Addr = 0x1163<br>Length = 0x0032 words | AGAIN:            | INC WO, WO                                | ;increment the fill value                             |

#### REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER (CONTINUED)

- bit 3-0 NVMOP<3:0>: NVM Operation Select bits<sup>(1,3,4)</sup>

- 1111 = Reserved

- .

- 0101 = Reserved

- 0100 = Inactive Partition memory erase operation

- 0011 = Memory page erase operation

- 0010 = Memory row program operation

- 0001 = Memory double-word program operation<sup>(5)</sup>

- 0000 = Reserved

- Note 1: These bits can only be reset on a POR.

- 2: If this bit is set, power consumption will be further reduced (IIDLE) and upon exiting Idle mode, there is a delay (TVREG) before Flash memory becomes operational.

- **3:** All other combinations of NVMOP<3:0> are unimplemented.

- 4: Execution of the PWRSAV instruction is ignored while any of the NVM operations are in progress.

- 5: Two adjacent words on a 4-word boundary are programmed during execution of this operation.

- 6: Only applicable when operating in Dual Partition mode.

#### 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/ 80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS7000600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGS70X/80X family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGS70X/80X family CPU.

The interrupt controller has the following features:

- Six Processor Exceptions and Software Traps

- Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with a Unique Vector for each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- Fixed Interrupt Entry and Return Latencies

- Alternate Interrupt Vector Table (AIVT) for Debug Support

#### 7.1 Interrupt Vector Table

The dsPIC33EPXXXGS70X/80X family Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory, starting at location, 000004h. The IVT contains six non-maskable trap vectors and up to 246 sources of interrupts. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT), shown in Figure 7-2, is available only when the Boot Segment is defined and the AIVT has been enabled. To enable the Alternate Interrupt Vector Table, the Configuration bit, AIVTDIS in the FSEC register, must be programmed and the AIVTEN bit must be set (INTCON2<8> = 1). When the AIVT is enabled, all interrupt and exception processes use the alternate vectors instead of the default vectors. The AIVT begins at the start of the last page of the Boot Segment, defined by BSLIM<12:0>. The second half of the page is no longer usable space. The Boot Segment must be at least 2 pages to enable the AIVT.

Note: Although the Boot Segment must be enabled in order to enable the AIVT, application code does not need to be present inside of the Boot Segment. The AIVT (and IVT) will inherit the Boot Segment code protection.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

#### 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGS70X/80X family devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

#### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

#### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have any effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

Note: If a PMD bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

#### 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

#### TABLE 11-1: PORTA PIN AND ANSELA AVAILABILITY

| Device             |      |      |      |      |      |      | PORT | a i/o | Pins |     |     |     |     |     |     |     |

|--------------------|------|------|------|------|------|------|------|-------|------|-----|-----|-----|-----|-----|-----|-----|

| Device             | RA15 | RA14 | RA13 | RA12 | RA11 | RA10 | RA9  | RA8   | RA7  | RA6 | RA5 | RA4 | RA3 | RA2 | RA1 | RA0 |

| dsPIC33EPXXXGSX08  | _    | —    | —    | —    | _    | _    | _    |       | —    | _   |     | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGSX06  |      |      |      | _    | _    | _    | _    | _     | _    | _   | _   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGSX05  |      |      |      | _    | _    | _    | _    | _     | _    | _   | _   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGSX04  |      |      |      |      | _    | _    | _    | _     |      | _   | _   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGS702  |      |      |      |      | _    | _    | _    | _     |      | _   | _   | Х   | Х   | Х   | Х   | Х   |

| ANSELA Bit Present |      |      |      | _    |      |      |      |       |      |     |     |     |     | Х   | Х   | Х   |

#### TABLE 11-2: PORTB PIN AND ANSELB AVAILABILITY

| Davias             |      | PORTB I/O Pins |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

|--------------------|------|----------------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Device             | RB15 | RB14           | RB13 | RB12 | RB11 | RB10 | RB9 | RB8 | RB7 | RB6 | RB5 | RB4 | RB3 | RB2 | RB1 | RB0 |

| dsPIC33EPXXXGSX08  | Х    | Х              | Х    | Х    | Х    | _    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGSX06  | Х    | Х              | Х    | Х    | Х    |      | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGSX05  | Х    | Х              | Х    | Х    | Х    |      | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGSX04  | Х    | Х              | Х    | Х    | Х    |      | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGS702  | Х    | Х              | Х    | Х    | Х    |      | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| ANSELB Bit Present | _    | _              |      |      | _    |      | Х   |     | Х   | Х   | Х   |     | Х   | Х   | Х   | Х   |

#### TABLE 11-3: PORTC PIN AND ANSELC AVAILABILITY

| Deviee             |      |      |      |      |      |      | PORT | C I/O | Pins |     |     |     |     |     |     |     |

|--------------------|------|------|------|------|------|------|------|-------|------|-----|-----|-----|-----|-----|-----|-----|

| Device             | RC15 | RC14 | RC13 | RC12 | RC11 | RC10 | RC9  | RC8   | RC7  | RC6 | RC5 | RC4 | RC3 | RC2 | RC1 | RC0 |

| dsPIC33EPXXXGSX08  | Х    | Х    | Х    | Х    | —    | Х    | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGSX06  | Х    | Х    | Х    | Х    | _    | Х    | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGSX05  | —    | _    | Х    | Х    | _    | Х    | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGSX04  | _    | _    | Х    | Х    | _    | Х    | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGS702  | —    | _    |      |      | _    | _    | _    | _     | _    | —   | _   | _   | _   | —   | —   |     |

| ANSELC Bit Present | —    | _    |      | Х    | _    | Х    | Х    |       |      | Х   | Х   | Х   |     | Х   | Х   | —   |

#### TABLE 11-4: PORTD PIN AND ANSELD AVAILABILITY

| Davias             |      |      |      |      |      |      | PORT | D I/O | Pins |     |     |     |     |     |     |     |

|--------------------|------|------|------|------|------|------|------|-------|------|-----|-----|-----|-----|-----|-----|-----|

| Device             | RD15 | RD14 | RD13 | RD12 | RD11 | RD10 | RD9  | RD8   | RD7  | RD6 | RD5 | RD4 | RD3 | RD2 | RD1 | RD0 |

| dsPIC33EPXXXGSX08  | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGSX06  | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х     | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGSX05  | —    | Х    | _    | _    | _    | Х    | _    | _     | _    | _   | _   | Х   | _   | _   | _   | _   |

| dsPIC33EPXXXGSX04  | _    | Х    |      |      |      | Х    | _    | _     | _    |     | _   | Х   | _   | _   | _   | _   |

| dsPIC33EPXXXGS702  | _    |      | _    | _    | _    | _    | _    | _     | _    | _   | _   | _   | _   | _   | _   | _   |

| ANSELD Bit Present | —    |      | Х    |      |      | _    | _    | Х     | Х    |     | Х   | _   |     | Х   | —   | —   |

#### TABLE 11-5: PORTE PIN AND ANSELE AVAILABILITY

| Device             |      |      |      |      |      |             | PORT | E I/O I | Pins |     |     |     |     |     |     |     |

|--------------------|------|------|------|------|------|-------------|------|---------|------|-----|-----|-----|-----|-----|-----|-----|

| Device             | RE15 | RE14 | RE13 | RE12 | RE11 | <b>RE10</b> | RE9  | RE8     | RE7  | RE6 | RE5 | RE4 | RE3 | RE2 | RE1 | RE0 |

| dsPIC33EPXXXGSX08  | Х    | Х    | Х    | Х    | Х    | Х           | Х    | Х       | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33EPXXXGSX06  | —    | _    | _    | —    | —    | —           | _    | _       | _    | _   | _   | _   | _   | _   | _   | _   |

| dsPIC33EPXXXGSX05  | _    | _    | _    | _    |      | —           |      | _       | _    | _   |     | -   | _   | -   | -   | _   |

| dsPIC33EPXXXGSX04  | _    |      |      |      |      |             |      | _       |      | -   |     |     |     |     |     | -   |

| dsPIC33EPXXXGS702  | _    | _    | _    | _    |      | _           | _    | _       |      | _   | _   | _   | _   | _   | _   | _   |

| ANSELE Bit Present | _    | _    | _    | _    |      | _           | _    | _       | _    | _   | _   | _   | _   | _   | _   | _   |

#### 11.6 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features, while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.6.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions.

#### 11.6.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. One example includes  $I^2C$  modules. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/Os and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.6.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

| U-0               | R/W-0  | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0              | R/W-0  |  |

|-------------------|--------|------------------|--------|------------------|------------------|--------------------|--------|--|

| —                 | RP53R6 | RP53R5           | RP53R4 | RP53R3           | RP53R2           | RP53R1             | RP53R0 |  |

| bit 15            |        |                  |        |                  |                  |                    | bit 8  |  |

|                   |        |                  |        |                  |                  |                    |        |  |

| U-0               | R/W-0  | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0              | R/W-0  |  |

| —                 | RP52R6 | RP52R5           | RP52R4 | RP52R3           | RP52R2           | RP52R1             | RP52R0 |  |

| bit 7             |        |                  |        |                  |                  |                    | bit 0  |  |

|                   |        |                  |        |                  |                  |                    |        |  |

| Legend:           |        |                  |        |                  |                  |                    |        |  |

| R = Readable b    | oit    | W = Writable     | bit    | U = Unimpler     | nented bit, read | l as '0'           |        |  |

| -n = Value at POR |        | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unknown |        |  |

#### REGISTER 11-45: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

| bit 15   | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-8 | <b>RP53R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP53 Output Pin bits (see Table 11-13 for peripheral function numbers) |

| bit 7    | Unimplemented: Read as '0'                                                                                                                |

| bit 6-0  | <b>RP52R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP52 Output Pin bits (see Table 11-13 for peripheral function numbers) |

#### **REGISTER 11-46: RPOR13: PERIPHERAL PIN SELECT OUTPUT REGISTER 13**

| U-0           | R/W-0      | R/W-0                              | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|------------|------------------------------------|--------|------------------|------------------|-----------------|--------|

| —             | RP55R6     | RP55R5                             | RP55R4 | RP55R3           | RP55R2           | RP55R1          | RP55R0 |

| bit 15        |            |                                    |        |                  |                  |                 | bit 8  |

|               |            |                                    |        |                  |                  |                 |        |

| U-0           | R/W-0      | R/W-0                              | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|               | RP54R6     | RP54R5                             | RP54R4 | RP54R3           | RP54R2           | RP54R1          | RP54R0 |

| bit 7         |            |                                    |        |                  |                  |                 | bit 0  |

|               |            |                                    |        |                  |                  |                 |        |

| Legend:       |            |                                    |        |                  |                  |                 |        |

| R = Readable  | bit        | W = Writable                       | bit    | U = Unimpler     | mented bit, read | l as '0'        |        |

| -n = Value at | POR        | '1' = Bit is set                   |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

|               |            |                                    |        |                  |                  |                 |        |

| bit 15        | Unimplemen | ted: Read as '                     | 0'     |                  |                  |                 |        |

| bit 14-8      |            | : Peripheral Ou<br>-13 for periphe | •      | •                | RP55 Output F    | Pin bits        |        |

|               |            |                                    |        |                  |                  |                 |        |

- bit 7 **Unimplemented:** Read as '0'

- RP54R<6:0>: Peripheral Output Function is Assigned to RP54 Output Pin bits bit 6-0 (see Table 11-13 for peripheral function numbers)

### REGISTER 17-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER<sup>(1,2)</sup> (CONTINUED)

| bit 4   | OC1CS: Clock Source for OC1 bit                                                                                                                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Generates clock pulse when the broadcast command is executed</li> <li>0 = Does not generate clock pulse when the broadcast command is executed</li> </ul>                         |

| bit 3   | OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| bit 2   | OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| bit 1   | OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| bit 0   | OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| Note 1: | This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and                                                                                                       |

2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

PTGSTRT = 1).

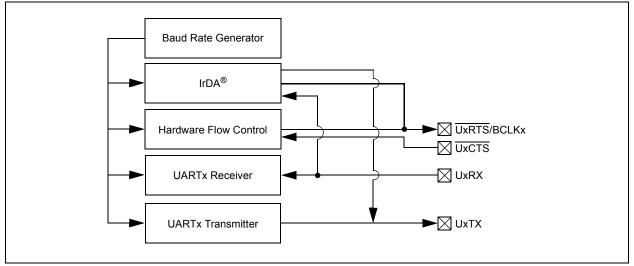

#### 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/ 80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGS70X/80X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGS70X/80X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps in 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps in 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTX SIMPLIFIED BLOCK DIAGRAM

|                 | 22-6: ADCC                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NUSII. ADC C                                                             |                  | GISTER 3 H        | IGH              |                 |         |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------|-------------------|------------------|-----------------|---------|--|--|

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                    | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |  |

| CLKSEL1         | CLKSEL0                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CLKDIV5                                                                  | CLKDIV4          | CLKDIV3 CLKDIV2   |                  | CLKDIV1         | CLKDIV0 |  |  |

| bit 15          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                          |                  |                   |                  |                 | bit 8   |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                          |                  |                   |                  |                 |         |  |  |

| R/W-0           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-0                                                                      | U-0              | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |  |

| SHREN           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —                                                                        | —                | C3EN              | C2EN             | C1EN            | C0EN    |  |  |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                          |                  |                   |                  |                 | bit 0   |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                          |                  |                   |                  |                 |         |  |  |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                          |                  |                   |                  |                 |         |  |  |

| R = Readable    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | W = Writable                                                             | oit              | •                 | nented bit, read |                 |         |  |  |

| -n = Value at I | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                            | '1' = Bit is set                                                         |                  | '0' = Bit is clea | ared             | x = Bit is unkr | IOWN    |  |  |

| bit 15-14       | 11 = APLL<br>10 = FRC                                                                                                                                                                                                                                                                                                                                                                                                                                          | >: ADC Module<br>ystem Clock x 2<br>ystem Clock)                         |                  | Selection bits    |                  |                 |         |  |  |

| bit 13-8        | CLKDIV<5:0>: ADC Module Clock Source Divider bits<br>The divider forms a TCORESRC clock used by all ADC cores (shared and dedicated) from the TSRC ADC<br>module clock source selected by the CLKSEL<1:0> bits. Then, each ADC core individually divides the<br>TCORESRC clock to get a core-specific TADCORE clock using the ADCS<6:0> bits in the ADCORExH<br>register or the SHRADCS<6:0> bits in the ADCON2L register.<br>111111 = 64 Source Clock Periods |                                                                          |                  |                   |                  |                 |         |  |  |

|                 | 000010 = 3 S<br>000001 = 2 S                                                                                                                                                                                                                                                                                                                                                                                                                                   | Source Clock Po<br>Source Clock Po<br>Source Clock Po<br>Source Clock Po | eriods<br>eriods |                   |                  |                 |         |  |  |

| bit 7           | SHREN: Shared ADC Core Enable bit<br>1 = Shared ADC core is enabled<br>0 = Shared ADC core is disabled                                                                                                                                                                                                                                                                                                                                                         |                                                                          |                  |                   |                  |                 |         |  |  |

| bit 6-4         | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ted: Read as 'd                                                          | )'               |                   |                  |                 |         |  |  |

| bit 3           | C3EN: Dedicated ADC Core 3 Enable bits<br>1 = Dedicated ADC Core 3 is enabled<br>0 = Dedicated ADC Core 3 is disabled                                                                                                                                                                                                                                                                                                                                          |                                                                          |                  |                   |                  |                 |         |  |  |

| bit 2           | <b>C2EN:</b> Dedicated ADC Core 2 Enable bits<br>1 = Dedicated ADC Core 2 is enabled<br>0 = Dedicated ADC Core 2 is disabled                                                                                                                                                                                                                                                                                                                                   |                                                                          |                  |                   |                  |                 |         |  |  |

| bit 1           | C1EN: Dedicated ADC Core 1 Enable bits<br>1 = Dedicated ADC Core 1 is enabled<br>0 = Dedicated ADC Core 1 is disabled                                                                                                                                                                                                                                                                                                                                          |                                                                          |                  |                   |                  |                 |         |  |  |

| bit 0           | 1 = Dedicated                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ated ADC Core<br>I ADC Core 0 is<br>I ADC Core 0 is                      | senabled         |                   |                  |                 |         |  |  |

#### REGISTER 22-6: ADCON3H: ADC CONTROL REGISTER 3 HIGH

| U-0          | U-0                  |                                    | R-0       | R-0              | R-0              | R-0             | R-0     |

|--------------|----------------------|------------------------------------|-----------|------------------|------------------|-----------------|---------|

|              | <u> </u>             |                                    | FILHIT4   | FILHIT3          | FILHIT2          | FILHIT1         | FILHIT0 |

| oit 15       |                      |                                    |           |                  |                  |                 | bit 8   |

|              |                      |                                    |           |                  |                  |                 |         |

| U-0          | R-1                  | R-0                                | R-0       | R-0              | R-0              | R-0             | R-0     |

| —            | ICODE6               | ICODE5                             | ICODE4    | ICODE3           | ICODE2           | ICODE1          | ICODE0  |

| oit 7        |                      |                                    |           |                  |                  |                 | bit 0   |

|              |                      |                                    |           |                  |                  |                 |         |

| egend:       |                      |                                    |           |                  |                  |                 |         |

| R = Readabl  |                      | W = Writable                       |           | -                | mented bit, read |                 |         |

| n = Value at | POR                  | '1' = Bit is set                   |           | '0' = Bit is cle | eared            | x = Bit is unkr | IOWN    |

| oit 15-13    | Unimplemen           | ted: Read as '                     | ٥'        |                  |                  |                 |         |

| bit 12-8     | -                    | Filter Hit Num                     |           |                  |                  |                 |         |

| Dit 12-0     | 10000-11111          |                                    |           |                  |                  |                 |         |

|              | 01111 <b>= Filte</b> |                                    |           |                  |                  |                 |         |

|              | •                    |                                    |           |                  |                  |                 |         |

|              | •                    |                                    |           |                  |                  |                 |         |

|              | 00001 <b>= Filte</b> | r 1                                |           |                  |                  |                 |         |

|              | 00000 = Filte        | r 0                                |           |                  |                  |                 |         |

| oit 7        | Unimplemen           | ted: Read as '                     | 0'        |                  |                  |                 |         |

| oit 6-0      | ICODE<6:0>:          | Interrupt Flag                     | Code bits |                  |                  |                 |         |

|              |                      | 11111 = Resei                      |           |                  |                  |                 |         |

|              |                      | IFO almost full<br>eceiver overflo |           |                  |                  |                 |         |

|              |                      | /ake-up interru                    |           |                  |                  |                 |         |

|              | 1000001 <b>=</b> E   |                                    |           |                  |                  |                 |         |

|              | 1000000 = N          | o interrupt                        |           |                  |                  |                 |         |

|              | •                    |                                    |           |                  |                  |                 |         |

|              | •                    | _                                  |           |                  |                  |                 |         |

|              |                      | L1111 = Reser<br>B15 buffer inte   |           |                  |                  |                 |         |

|              | •                    |                                    | παρι      |                  |                  |                 |         |

|              | •                    |                                    |           |                  |                  |                 |         |

|              | •                    | B9 buffer inter                    | runt      |                  |                  |                 |         |

|              |                      | B8 buffer inter                    | •         |                  |                  |                 |         |

|              |                      | RB7 buffer inte                    |           |                  |                  |                 |         |

|              |                      | RB6 buffer inte                    |           |                  |                  |                 |         |

|              |                      | RB5 buffer inte<br>RB4 buffer inte |           |                  |                  |                 |         |

|              |                      | RB3 buffer inte                    |           |                  |                  |                 |         |

|              | 0000010 <b>= T</b>   | RB2 buffer inte                    | errupt    |                  |                  |                 |         |

|              |                      | RB1 buffer inte<br>RB0 buffer inte |           |                  |                  |                 |         |

|              | 0000000 = 11         |                                    | inupt     |                  |                  |                 |         |

#### REGISTER 23-3: CxVEC: CANx INTERRUPT CODE REGISTER

| DC CHARACTERISTICS |        | Standard Operating Co<br>(unless otherwise state<br>Operating temperature |        |                     |      |       |                                                                |  |

|--------------------|--------|---------------------------------------------------------------------------|--------|---------------------|------|-------|----------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                            | Min.   | Тур. <sup>(1)</sup> | Max. | Units | Conditions                                                     |  |

|                    |        | Program Flash Memory                                                      |        |                     |      |       |                                                                |  |

| D130               | Eр     | Cell Endurance                                                            | 10,000 | —                   | _    | E/W   | -40°C to +125°C                                                |  |

| D131               | Vpr    | VDD for Read                                                              | 3.0    | —                   | 3.6  | V     |                                                                |  |

| D132b              | VPEW   | VDD for Self-Timed Write                                                  | 3.0    | —                   | 3.6  | V     |                                                                |  |

| D134               | TRETD  | Characteristic Retention                                                  | 20     | —                   | —    | Year  | Provided no other specifications are violated, -40°C to +125°C |  |

| D135               | IDDP   | Supply Current during<br>Programming <sup>(2)</sup>                       | _      | 10                  | —    | mA    |                                                                |  |

| D136               | IPEAK  | Instantaneous Peak Current<br>During Start-up                             | _      | —                   | 150  | mA    |                                                                |  |

| D137a              | TPE    | Page Erase Time                                                           | 19.7   | —                   | 20.1 | ms    | TPE = 146893 FRC cycles,<br>TA = +85°C <b>(Note 3)</b>         |  |

| D137b              | TPE    | Page Erase Time                                                           | 19.5   | —                   | 20.3 | ms    | TPE = 146893 FRC cycles,<br>Ta = +125°C <b>(Note 3)</b>        |  |

| D138a              | Tww    | Word Write Cycle Time                                                     | 46.5   | —                   | 47.3 | μs    | Tww = 346 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>            |  |

| D138b              | Tww    | Word Write Cycle Time                                                     | 46.0   | —                   | 47.9 | μs    | Tww = 346 FRC cycles,<br>Ta = +125°C <b>(Note 3)</b>           |  |

| D139a              | Trw    | Row Write Time                                                            | 667    | -                   | 679  | μs    | Trw = 4965 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>           |  |

| D139b              | Trw    | Row Write Time                                                            | 660    | -                   | 687  | μs    | Trw = 4965 FRC cycles,<br>Ta = +125°C <b>(Note 3)</b>          |  |

#### TABLE 30-14: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

2: Parameter characterized but not tested in manufacturing.

3: Other conditions: FRC = 7.37 MHz, TUN<5:0> = 011111 (for Minimum), TUN<5:0> = 100000 (for Maximum). This parameter depends on the FRC accuracy (see Table 30-20) and the value of the FRC Oscillator Tuning register (see Register 9-4). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

#### TABLE 30-23: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER TIMING REQUIREMENTS

| AC CHARACTERISTICS |           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$          |      |                     |      |       |                                                                                                             |  |

|--------------------|-----------|----------------------------------------------------------------|------|---------------------|------|-------|-------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                  | Min. | Typ. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                  |  |

| SY00               | Tpu       | Power-up Period                                                | _    | 400                 | 600  | μS    |                                                                                                             |  |

| SY10               | Тоѕт      | Oscillator Start-up Time                                       | —    | 1024 Tosc           | _    | —     | Tosc = OSC1 period                                                                                          |  |

| SY12               | Twdt      | Watchdog Timer<br>Time-out Period                              | 0.81 | _                   | 1.22 | ms    | WDTPRE = 0,<br>WDTPOST<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21 (see Table 30-21) at +85°C |  |

|                    |           |                                                                | 3.25 | _                   | 4.88 | ms    | WDTPRE = 1,<br>WDTPOST<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21 (see Table 30-21) at +85°C |  |

| SY13               | Tioz      | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | 0.68 | 0.72                | 1.2  | μS    |                                                                                                             |  |

| SY20               | TMCLR     | MCLR Pulse Width (low)                                         | 2    | _                   |      | μS    |                                                                                                             |  |

| SY30               | TBOR      | BOR Pulse Width (low)                                          | 1    |                     |      | μS    |                                                                                                             |  |

| SY35               | TFSCM     | Fail-Safe Clock Monitor<br>Delay                               | _    | 500                 | 900  | μS    | -40°C to +85°C                                                                                              |  |

| SY36               | Tvreg     | Voltage Regulator<br>Standby-to-Active mode<br>Transition Time | —    | _                   | 30   | μS    |                                                                                                             |  |

| SY37               | Toscdfrc  | FRC Oscillator Start-up<br>Delay                               | _    | 48                  | _    | μS    |                                                                                                             |  |

| SY38               | TOSCDLPRC | LPRC Oscillator Start-up<br>Delay                              | —    | —                   | 70   | μS    |                                                                                                             |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

### TABLE 30-46:SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)TIMING REQUIREMENTS<sup>(5)</sup>

| AC CHARACTERISTICS |                       |                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                             |

|--------------------|-----------------------|----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP70               | FscP                  | Maximum SCK3 Input Frequency                 | —                                                     | —                   | 25   | MHz   | (Note 3)                    |

| SP72               | TscF                  | SCK3 Input Fall Time                         | —                                                     | —                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP73               | TscR                  | SCK3 Input Rise Time                         | —                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP30               | TdoF                  | SDO3 Data Output Fall Time                   | —                                                     | —                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP31               | TdoR                  | SDO3 Data Output Rise Time                   | —                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO3 Data Output Valid after<br>SCK3 Edge    | —                                                     | 6                   | 20   | ns    |                             |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO3 Data Output Setup to<br>First SCK3 Edge | 20                                                    | —                   | _    | ns    |                             |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI3 Data Input to SCK3 Edge   | 20                                                    | —                   | _    | ns    |                             |