Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| Product Status            | Active                                                                           |

| Core Processor            | dsPIC                                                                            |

| Core Size                 | 16-Bit                                                                           |

| Speed                     | 70 MIPs                                                                          |

| Connectivity              | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| <u> </u>                  |                                                                                  |

| Peripherals               | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                  |

| Number of I/O             | 51                                                                               |

| Program Memory Size       | 128KB (43K x 24)                                                                 |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| RAM Size                  | 8K x 8                                                                           |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters           | A/D 22x12b; D/A 2x12b                                                            |

| Oscillator Type           | Internal                                                                         |

| Operating Temperature     | -40°C ~ 85°C (TA)                                                                |

| Mounting Type             | Surface Mount                                                                    |

| Package / Case            | 64-TQFP                                                                          |

| Supplier Device Package   | 64-TQFP (10x10)                                                                  |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs806-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.3.5 X AND Y DATA SPACES

The dsPIC33EPXXXGS70X/80X core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY. N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

#### 4.4 Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 4.4.1 KEY RESOURCES

- "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

TABLE 4-4: SFR BLOCK 200h

| Register     | Address | All Resets        | Register                | Address | All Resets                    | Register  | Address | All Resets        |

|--------------|---------|-------------------|-------------------------|---------|-------------------------------|-----------|---------|-------------------|

| I2C1 and I2C | 2       |                   | U1STA                   | 222     | 000000010010000               | SPI1BRGH  | 252     | 0000000000000000  |

| I2C1CONL     | 200     | 00010000000000000 | U1TXREG                 | 224     | 0000000xxxxxxxx               | SPI1IMSKL | 254     | 0000000000000000  |

| I2C1CONH     | 202     | 00000000000000000 | U1RXREG                 | 226     | 00000000000000000             | SPI1IMSKH | 256     | 00000000000000000 |

| I2C1STAT     | 204     | 00000000000000000 | U1BRG                   | 228     | 0000000000000000              | SPI1URDTL | 258     | 0000000000000000  |

| I2C1ADD      | 206     | 00000000000000000 | U2MODE                  | 230     | 0000000000000000              | SPI1URDTH | 25A     | 0000000000000000  |

| I2C1MSK      | 208     | 00000000000000000 | U2STA                   | 232     | 000000010010000               | SPI2CON1L | 260     | 0000000000000000  |

| I2C1BRG      | 20A     | 00000000000000000 | U2TXREG                 | 234     | 0000000xxxxxxxx               | SPI2CON1H | 262     | 0000000000000000  |

| I2C1TRN      | 20C     | 0000000011111111  | U2RXREG                 | 236     | 0000000000000000              | SPI2CON2L | 264     | 0000000000000000  |

| I2C1RCV      | 20E     | 00000000000000000 | U2BRG                   | 238     | 0000000000000000              | SPI2CON2H | 266     | 0000000000000000  |

| I2C2CON1     | 210     | 0001000000000000  | SPI                     |         |                               | SPI2STATL | 268     | 000000000101000   |

| I2C2CON2     | 212     | 00000000000000000 | SPI1CON1L               | 240     | 0000000000000000              | SPI2STATH | 26A     | 0000000000000000  |

| I2C2STAT     | 214     | 00000000000000000 | SPI1CON1H               | 242     | 0000000000000000              | SPI2BUFL  | 26C     | 0000000000000000  |

| I2C2ADD      | 216     | 00000000000000000 | SPI1CON2L               | 244     | 0000000000000000              | SPI2BUFH  | 26E     | 0000000000000000  |

| I2C2MSK      | 218     | 00000000000000000 | SPI1CON2H               | 246     | 0000000000000000              | SPI3STAT  | 270     | 000xxxxxxxxxxxx   |

| I2C2BRG      | 21A     | 00000000000000000 | SPI1STATL               | 248     | 000000000101000               | SPI2BRGH  | 272     | 0000000000000000  |

| I2C2TRN      | 21C     | 0000000011111111  | SPI1STATH               | 24A     | 0000000000000000              | SPI2IMSKL | 274     | 0000000000000000  |

| I2C2RCV      | 21E     | 00000000000000000 | SPI1BUFL                | 24C     | 00000000000000000             | SPI2IMSKH | 276     | 0000000000000000  |

| UART1 and l  | JART2   |                   | SPI1BUFH 24E 0000000000 |         | 00000000000000000             | SPI2URDTL | 278     | 0000000000000000  |

| U1MODE       | 220     | 00000000000000000 | SPI1BRGL                | 250     | 000xxxxxxxxxxxxxxxxxxxxxxxxxx | SPI2URDTH | 27A     | 00000000000000000 |

**Legend:** x = unknown or indeterminate value. Address values are in hexadecimal. Reset values are in binary.

TABLE 4-5: SFR BLOCK 300h

| Register  | Address | All Resets        | Register  | Address           | All Resets       | Register  | Address          | All Resets        |

|-----------|---------|-------------------|-----------|-------------------|------------------|-----------|------------------|-------------------|

| ADC       |         | ADCMP0ENH         | 33A       | 00000000000000000 | ADTRIG4L         | 390       | 0000000000000000 |                   |

| ADCON1L   | 300     | 00000000000000000 | ADCMP0LO  | 33C               | 0000000000000000 | ADTRIG4H  | 392              | 0000000000000000  |

| ADCON1H   | 302     | 000000001100000   | ADCMP0HI  | 33E               | 0000000000000000 | ADCMP0CON | 3A0              | 00000000000000000 |

| ADCON2L   | 304     | 0000000000000000  | ADCMP1ENL | 340               | 0000000000000000 | ADCMP1CON | 3A4              | 0000000000000000  |

| ADCON2H   | 306     | 0000000000000000  | ADCMP1ENH | 342               | 0000000000000000 | ADBASE    | 3C0              | 0000000000000000  |

| ADCON3L   | 308     | 0000000000000000  | ADCMP1LO  | 344               | 0000000000000000 | ADLVLTRGL | 3D0              | 00000000000000000 |

| ADCON3H   | 30A     | 0000000000000000  | ADCMP1HI  | 346               | 0000000000000000 | ADLVLTRGH | 3D2              | 0000000000000000  |

| ADCON4L   | 30C     | 0000000000000000  | ADFL0DAT  | 368               | 0000000000000000 | ADCORE0L  | 3D4              | 0000000000000000  |

| ADCON4H   | 30E     | 0000000000000000  | ADFL0CON  | 36A               | 0000000000000000 | ADCORE0H  | 3D6              | 0000001100000000  |

| ADMOD0L   | 310     | 0000000000000000  | ADFL1DAT  | 36C               | 0000000000000000 | ADCORE1L  | 3D8              | 0000000000000000  |

| ADMOD0H   | 312     | 0000000000000000  | ADFL1CON  | 36E               | 0000000000000000 | ADCORE1H  | 3DA              | 0000001100000000  |

| ADMOD1L   | 314     | 0000000000000000  | ADTRIG0L  | 380               | 0000000000000000 | ADCORE2L  | 3DC              | 0000000000000000  |

| ADIEL     | 320     | 0000000000000000  | ADTRIG0H  | 382               | 0000000000000000 | ADCORE2H  | 3DE              | 0000001100000000  |

| ADIEH     | 322     | 0000000000000000  | ADTRIG1L  | 384               | 0000000000000000 | ADCORE3L  | 3E0              | 0000000000000000  |

| ADCSS1L   | 328     | 0000000000000000  | ADTRIG1H  | 386               | 0000000000000000 | ADCORE3H  | 3E2              | 0000001100000000  |

| ADCSS1H   | 32A     | 0000000000000000  | ADTRIG2L  | 388               | 0000000000000000 | ADEIEL    | 3F0              | 0000000000000000  |

| ADSTATL   | 330     | 0000000000000000  | ADTRIG2H  | 38A               | 0000000000000000 | ADEIEH    | 3F2              | 00000000000000000 |

| ADSTATH   | 332     | 0000000000000000  | ADTRIG3L  | 38C               | 0000000000000000 | ADEISTATL | 3F8              | 00000000000000000 |

| ADCMP0ENL | 338     | 00000000000000000 | ADTRIG3H  | 38E               | 0000000000000000 | ADEISTATH | 3FA              | 0000000000000000  |

$\textbf{Legend:} \quad \textbf{x} = \textbf{unknown or indeterminate value}. \ \textbf{Address values are in hexadecimal}. \ \textbf{Reset values are in binary}.$

#### REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R-0    | R-0    | R-0    | R-0    |

|-------|-----|-----|-----|--------|--------|--------|--------|

| _     | _   | _   | _   | PWCOL3 | PWCOL2 | PWCOL1 | PWCOL0 |

| bit 7 |     |     |     |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-4 Unimplemented: Read as '0'

bit 3 PWCOL3: Channel 3 Peripheral Write Collision Flag bit

1 = Write collision is detected0 = No write collision is detected

bit 2 PWCOL2: Channel 2 Peripheral Write Collision Flag bit

1 = Write collision is detected0 = No write collision is detected

bit 1 **PWCOL1:** Channel 1 Peripheral Write Collision Flag bit

1 = Write collision is detected0 = No write collision is detected

bit 0 PWCOL0: Channel 0 Peripheral Write Collision Flag bit

1 = Write collision is detected0 = No write collision is detected

#### REGISTER 11-29: RPINR42: PERIPHERAL PIN SELECT INPUT REGISTER 42

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FLT6R7 | FLT6R6 | FLT6R5 | FLT6R4 | FLT6R3 | FLT6R2 | FLT6R1 | FLT6R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FLT5R7 | FLT5R6 | FLT5R5 | FLT5R4 | FLT5R3 | FLT5R2 | FLT5R1 | FLT5R0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 FLT6R<7:0>: Assign PWM Fault 6 (FLT6) to the Corresponding RPn Pin bits

See Table 11-11 which contains a list of remappable inputs for the index value.

bit 7-0 FLT5R<7:0>: Assign PWM Fault 5 (FLT5) to the Corresponding RPn Pin bits

See Table 11-11 which contains a list of remappable inputs for the index value.

#### REGISTER 11-30: RPINR43: PERIPHERAL PIN SELECT INPUT REGISTER 43

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FLT8R7 | FLT8R6 | FLT8R5 | FLT8R4 | FLT8R3 | FLT8R2 | FLT8R1 | FLT8R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FLT7R7 | FLT7R6 | FLT7R5 | FLT7R4 | FLT7R3 | FLT7R2 | FLT7R1 | FLT7R0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 FLT8R<7:0>: Assign PWM Fault 8 (FLT8) to the Corresponding RPn Pin bits

See Table 11-11 which contains a list of remappable inputs for the index value.

bit 7-0 FLT7R<7:0>: Assign PWM Fault 7 (FLT7) to the Corresponding RPn Pin bits

See Table 11-11 which contains a list of remappable inputs for the index value.

#### REGISTER 15-2: OCXCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

```

bit 4-0

SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

11111 = OCxRS compare event is used for synchronization

11110 = INT2 pin synchronizes or triggers OCx

11101 = INT1 pin synchronizes or triggers OCx

11100 = Reserved

11011 = CMP4 module synchronizes or triggers OCx

11010 = CMP3 module synchronizes or triggers OCx

11001 = CMP2 module synchronizes or triggers OCx

11000 = CMP1 module synchronizes or triggers OCx

10111 = Reserved

10110 = Reserved

10101 = Reserved

10100 = Reserved

10011 = IC4 input capture interrupt event synchronizes or triggers OCx

10010 = IC3 input capture interrupt event synchronizes or triggers OCx

10001 = IC2 input capture interrupt event synchronizes or triggers OCx

10000 = IC1 input capture interrupt event synchronizes or triggers OCx

01111 = Timer5 synchronizes or triggers OCx

01110 = Timer4 synchronizes or triggers OCx

01101 = Timer3 synchronizes or triggers OCx

01100 = Timer2 synchronizes or triggers OCx (default)

01011 = Timer1 synchronizes or triggers OCx

01010 = PTG Trigger Output x^{(3)}

01001 = Reserved

01000 = IC4 input capture event synchronizes or triggers OCx

00111 = IC3 input capture event synchronizes or triggers OCx

00110 = IC2 input capture event synchronizes or triggers OCx

00101 = IC1 input capture event synchronizes or triggers OCx

00100 = OC4 module synchronizes or triggers OCx^{(1,2)}

00011 = OC3 module synchronizes or triggers OCx<sup>(1,2)</sup>

00010 = OC2 module synchronizes or triggers OCx^{(1,2)}

00001 = OC1 module synchronizes or triggers OCx(1,2)

00000 = No sync or trigger source for OCx

```

- **Note 1:** Do not use the OCx module as its own synchronization or trigger source.

- 2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

- 3: For each OCMPx instance, a different PTG trigger out is used:

- OCMP1 PTG trigger out [0]

- OCMP2 PTG trigger out [1]

- OCMP3 PTG trigger out [2]

- OCMP4 PTG trigger out [3]

TABLE 21-1: CLC1 MULTIPLEXER INPUT SOURCES

|          | DSx<2:0> | Signal Source           |

|----------|----------|-------------------------|

|          | 000      | CLCINA                  |

|          | 001      | System Clock            |

| Δ        | 010      | Timer1 Match            |

| 5:0      | 011      | PWM1H                   |

| DS1<2:0> | 100      | PWM5L                   |

| Δ        | 101      | High-Speed PWM Clock    |

|          | 110      | Timer2 Match            |

|          | 111      | Timer3 Match            |

|          | 000      | CLCINB                  |

|          | 001      | CLC2 Out                |

| ۸        | 010      | CMP1 Out                |

| DS2<2:0> | 011      | UART1 TX Out            |

| S2<      | 100      | ADC End-of-Conversion   |

| ă        | 101      | DMA Channel 0 Interrupt |

|          | 110      | PWM1L                   |

|          | 111      | PWM5H                   |

|          | 000      | CLCINA                  |

|          | 001      | CLC1 Out                |

| ^        | 010      | CMP2 Out                |

| 5:0      | 011      | SPI1 SDO Out            |

| DS3<2:0> | 100      | UART1 RX                |

| ă        | 101      | PWM2H                   |

|          | 110      | PWM6L                   |

|          | 111      | OCMP2                   |

|          | 000      | CLCINB                  |

|          | 001      | CLC2 Out                |

| ^        | 010      | CMP3 Out                |

| DS4<2:0> | 011      | SDI1                    |

| 84       | 100      | PTG                     |

| ă        | 101      | ECAN1                   |

|          | 110      | PWM2L                   |

|          | 111      | PWM6H                   |

### REGISTER 21-4: CLCxGLSL: CLCx GATE LOGIC INPUT SELECT LOW REGISTER (CONTINUED)

| bit 3 | <b>G1D2T:</b> Gate 1 Data Source 2 True Enable bit<br>1 = Data Source 2 non-inverted signal is enabled for Gate 1<br>0 = Data Source 2 non-inverted signal is disabled for Gate 1 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | G1D2N: Gate 1 Data Source 2 Negated Enable bit                                                                                                                                    |

|       | <ul><li>1 = Data Source 2 inverted signal is enabled for Gate 1</li><li>0 = Data Source 2 inverted signal is disabled for Gate 1</li></ul>                                        |

| bit 1 | G1D1T: Gate 1 Data Source 1 True Enable bit                                                                                                                                       |

|       | <ul><li>1 = Data Source 1 non-inverted signal is enabled for Gate 1</li><li>0 = Data Source 1 non-inverted signal is disabled for Gate 1</li></ul>                                |

| bit 0 | G1D1N: Gate 1 Data Source 1 Negated Enable bit                                                                                                                                    |

|       | <ul><li>1 = Data Source 1 inverted signal is enabled for Gate 1</li><li>0 = Data Source 1 inverted signal is disabled for Gate 1</li></ul>                                        |

|  |  | TAXAGS/UX/OUX FAMILI |

|--|--|----------------------|

**FIGURE 23-1: CANX MODULE BLOCK DIAGRAM** RxF15 Filter RxF14 Filter RxF13 Filter RxF12 Filter RxF11 Filter **DMA Controller** RxF10 Filter RxF9 Filter RxF8 Filter TRB7 TX/RX Buffer Control Register RxF7 Filter RxF6 Filter TRB6 TX/RX Buffer Control Register RxF5 Filter TRB5 TX/RX Buffer Control Register RxF4 Filter TRB4 TX/RX Buffer Control Register TRB3 TX/RX Buffer Control Register RxF3 Filter RxF2 Filter TRB2 TX/RX Buffer Control Register RxM2 Mask RxF1 Filter TRB1 TX/RX Buffer Control Register RxM1 Mask RxF0 Filter TRB0 TX/RX Buffer Control Register RxM0 Mask Transmit Byte Message Assembly Sequencer Buffer Control Configuration Logic **CAN Protocol** Engine Interrupts CxTX**CxRX**

#### 23.2 Modes of Operation

The CANx module can operate in one of several operation modes selected by the user. These modes include:

- · Initialization mode

- · Disable mode

- · Normal Operation mode

- · Listen Only mode

- · Listen All Messages mode

- · Loopback mode

Modes are requested by setting the REQOP<2:0> bits (CxCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CxCTRL1<7:5>). The module does not change the mode and the OPMODEx bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

| uspic3 | USPIC33EPXXXG3/UX/8UX FAIVILT |  |  |  |  |  |  |

|--------|-------------------------------|--|--|--|--|--|--|

| NOTES: |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

|        |                               |  |  |  |  |  |  |

#### 24.3 Module Applications

This module provides a means for the SMPS dsPIC® DSC devices to monitor voltage and currents in a power conversion application. The ability to detect transient conditions and stimulate the dsPIC DSC processor and/or peripherals, without requiring the processor and ADC to constantly monitor voltages or currents, frees the dsPIC DSC to perform other tasks.

The comparator module has a high-speed comparator and an associated 12-bit DAC that provides a programmable reference voltage to the inverting input of the comparator. The polarity of the comparator output is user-programmable. The output of the module can be used in the following modes:

- Generate an Interrupt

- Trigger an ADC Sample and Convert Process

- Truncate the PWMx Signal (current limit)

- Truncate the PWMx Period (current minimum)

- Disable the PWMx Outputs (Fault latch)

The output of the comparator module may be used in multiple modes at the same time, such as: 1) generate an interrupt, 2) have the ADC take a sample and convert it, and 3) truncate the PWMx output in response to a voltage being detected beyond its expected value.

The comparator module can also be used to wake-up the system from Sleep or Idle mode when the analog input voltage exceeds the programmed threshold voltage.

#### 24.4 Digital-to-Analog Comparator (DAC)

Each analog comparator has a dedicated 12-bit DAC that is used to program the comparator threshold voltage via the CMPxDAC register. The DAC voltage reference source is selected using the EXTREF and RANGE bits in the CMPxCON register.

The EXTREF bit selects either the external voltage reference, EXTREFx, or an internal source as the voltage reference source. The EXTREFx input enables users to connect to a voltage reference that better suits their application. The RANGE bit enables AVDD as the voltage reference source for the DAC when an internal voltage reference is selected.

**Note:** EXTREF2 is not available on all devices.

Each DACx has an output enable bit, DACOE, in the CMPxCON register that enables the DACx reference voltage to be routed to an external output pin (DACOUTx). Refer to Figure 24-1 for connecting the DACx output voltage to the DACOUTx pins.

- Note 1: Ensure that multiple DACOE bits are not set in software. The output on the DACOUTx pin will be indeterminate if multiple comparators enable the DACx output.

- 2: DACOUT2 is not available on all devices.

#### 24.5 Pulse Stretcher and Digital Logic

The analog comparator can respond to very fast transient signals. After the comparator output is given the desired polarity, the signal is passed to a pulse stretching circuit. The pulse stretching circuit has an asynchronous set function and a delay circuit that ensures the minimum pulse width is three system clock cycles wide to allow the attached circuitry to properly respond to a narrow pulse event.

The pulse stretcher circuit is followed by a digital filter. The digital filter is enabled via the FLTREN bit in the CMPxCON register. The digital filter operates with the clock specified via the FCLKSEL bit in the CMPxCON register. The comparator signal must be stable in a high or low state, for at least three of the selected clock cycles, for it to pass through the digital filter.

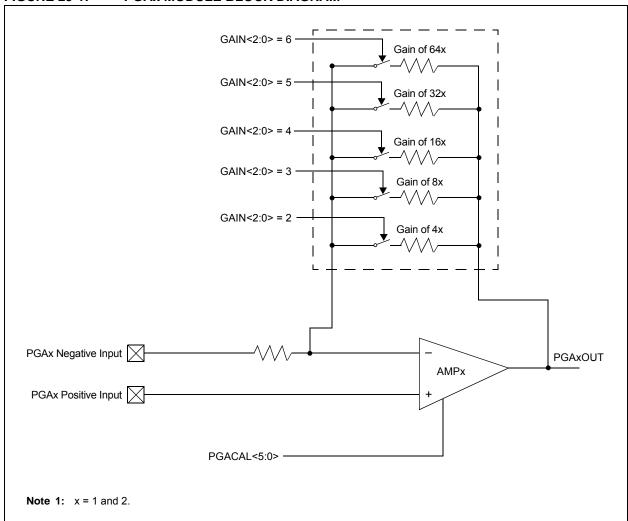

# 25.0 PROGRAMMABLE GAIN AMPLIFIER (PGA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Programmable Gain Amplifier (PGA)" (DS70005146) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGS70X/80X family devices have two Programmable Gain Amplifiers (PGA1, PGA2). The PGA is an op amp-based, non-inverting amplifier with user-programmable gains. The output of the PGA can be connected to a number of dedicated Sample-and-Hold inputs of the Analog-to-Digital Converter and/ or to the high-speed analog comparator module. The PGA has five selectable gains and may be used as a ground referenced amplifier (single-ended) or used with an independent ground reference point.

Key features of the PGA module include:

- Single-Ended or Independent Ground Reference

- Selectable Gains: 4x, 8x, 16x, 32x and 64x

- · High Gain Bandwidth

- · Rail-to-Rail Output Voltage

- · Wide Input Voltage Range

FIGURE 25-1: PGAX MODULE BLOCK DIAGRAM

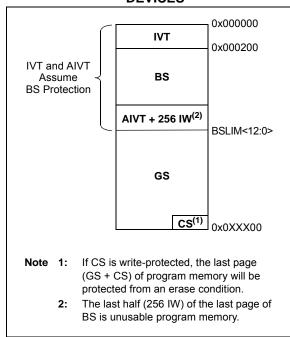

The different device security segments are shown in Figure 27-3. Here, all three segments are shown but are not required. If only basic code protection is required, then GS can be enabled independently or combined with CS. if desired.

FIGURE 27-3: SECURITY SEGMENTS

EXAMPLE FOR

dsPIC33EPXXXGS70X/80X

DEVICES

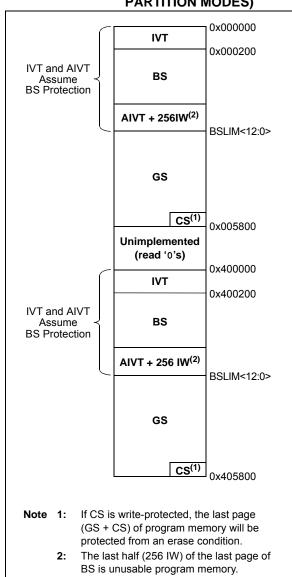

dsPIC33EPXXXGS70X/80X family devices can be operated in Dual Partition mode, where security is required for each partition. When operating in Dual Partition mode, the Active and Inactive Partitions both contain unique copies of the Reset vector, Interrupt Vector Tables (IVT and AIVT, if enabled) and the Flash Configuration Words. Both partitions have the three security segments described previously. Code may not be executed from the Inactive Partition, but it may be programmed by, and read from, the Active Partition, subject to defined code protection. Figure 27-4 and Figure 27-5 show the different security segments for devices operating in Dual Partition mode.

The device may also operate in a Protected Dual Partition mode or in Privileged Dual Partition mode. In Protected Dual Partition mode, Partition 1 is permanently erase/write-protected. This implementation allows for a "Factory Default" mode, which provides a fail-safe backup image to be stored in Partition 1. For example, a fail-safe bootloader can be placed in Partition 1, along with a fail-safe backup code image, which can be used or rewritten into Partition 2 in the event of a failed Flash update to Partition 2.

Privileged Dual Partition mode performs the same function as Protected Dual Partition mode, except additional constraints are applied in an effort to prevent code in the Boot Segment and General Segment from being used against each other.

FIGURE 27-4: SECURITY SEGMENTS

EXAMPLE FOR

dsPIC33EP64GS70X/80X

DEVICES (DUAL

PARTITION MODES)

| NOTES: |  |  |  |

|--------|--|--|--|

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

#### **TABLE 30-20: INTERNAL FRC ACCURACY**

| AC CHA       | RACTERISTICS           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |          |      |       |                                                             |                |  |

|--------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-------|-------------------------------------------------------------|----------------|--|

| Param<br>No. | Characteristic         | Min.                                                                                                                                                                                                                                             | Тур.     | Max. | Units | Conditions                                                  |                |  |

| Internal     | FRC Accuracy @ FRC Fre | equency =                                                                                                                                                                                                                                        | 7.37 MHz | ,(1) |       |                                                             |                |  |

| F20a         | FRC                    | -2                                                                                                                                                                                                                                               | 0.5      | +2   | %     | -40°C ≤ TA ≤ -10°C                                          | VDD = 3.0-3.6V |  |

|              |                        | -0.9                                                                                                                                                                                                                                             | 0.5      | +0.9 | %     | $-10^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ | VDD = 3.0-3.6V |  |

| F20b         | FRC                    | -2                                                                                                                                                                                                                                               | 1        | +2   | %     | $+85^{\circ}C \le TA \le +125^{\circ}C$                     | VDD = 3.0-3.6V |  |

Note 1: Frequency is calibrated at +25°C and 3.3V. TUNx bits can be used to compensate for temperature drift.

#### **TABLE 30-21: INTERNAL LPRC ACCURACY**

| AC CH        | ARACTERISTICS               | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |      |      |       |                                                              |                     |  |

|--------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------------------------------------------------|---------------------|--|

| Param<br>No. | Characteristic              | Min.                                                                                                                                                                                                                                             | Тур. | Max. | Units | Conditions                                                   |                     |  |

| LPRC (       | @ 32.768 kHz <sup>(1)</sup> |                                                                                                                                                                                                                                                  |      |      |       |                                                              |                     |  |

| F21a         | LPRC                        | -30                                                                                                                                                                                                                                              | _    | +30  | %     | -40°C ≤ TA ≤ -10°C                                           | VDD = 3.0-3.6V      |  |

|              |                             | -20                                                                                                                                                                                                                                              |      | +20  | %     | $-10^{\circ}C \le TA \le +85^{\circ}C$                       | VDD = 3.0-3.6V      |  |

| F21b         | LPRC                        | -30                                                                                                                                                                                                                                              | _    | +30  | %     | $+85^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ | $V_{DD} = 3.0-3.6V$ |  |

Note 1: This is the change of the LPRC frequency as VDD changes.

TABLE 30-45: SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING REQUIREMENTS<sup>(5)</sup>

| AC CHA | ARACTERIS <sup>-</sup> | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤ TA ≤ +85°C for Industrial |              |                               |      |       |                             |  |  |

|--------|------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------|------|-------|-----------------------------|--|--|

|        |                        |                                                                                                                                |              | -40°C ≤ Ta ≤ +125°C for Exter |      |       |                             |  |  |

| Param. | Symbol                 | Characteristic <sup>(1)</sup>                                                                                                  | Min.         | Typ. <sup>(2)</sup>           | Max. | Units | Conditions                  |  |  |

| SP70   | FscP                   | Maximum SCK3 Input Frequency                                                                                                   | _            | _                             | 25   | MHz   | (Note 3)                    |  |  |

| SP72   | TscF                   | SCK3 Input Fall Time                                                                                                           | _            | ı                             | _    | ns    | See Parameter DO32 (Note 4) |  |  |

| SP73   | TscR                   | SCK3 Input Rise Time                                                                                                           | _            | ı                             | _    | ns    | See Parameter DO31 (Note 4) |  |  |

| SP30   | TdoF                   | SDO3 Data Output Fall Time                                                                                                     | _            |                               | _    | ns    | See Parameter DO32 (Note 4) |  |  |

| SP31   | TdoR                   | SDO3 Data Output Rise Time                                                                                                     | _            |                               | _    | ns    | See Parameter DO31 (Note 4) |  |  |

| SP35   | TscH2doV,<br>TscL2doV  | SDO3 Data Output Valid after SCK3 Edge                                                                                         | _            | 6                             | 20   | ns    |                             |  |  |

| SP36   | TdoV2scH,<br>TdoV2scL  | SDO3 Data Output Setup to First SCK3 Edge                                                                                      | 20           | -                             | _    | ns    |                             |  |  |

| SP40   | TdiV2scH,<br>TdiV2scL  | Setup Time of SDI3 Data Input to SCK3 Edge                                                                                     | 20           |                               | _    | ns    |                             |  |  |

| SP41   | TscH2diL,<br>TscL2diL  | Hold Time of SDI3 Data Input to SCK3 Edge                                                                                      | 15           |                               | _    | ns    |                             |  |  |

| SP50   | TssL2scH,<br>TssL2scL  | SS3 ↓ to SCK3 ↑ or SCK3 ↓ Input                                                                                                | 120          |                               | _    | ns    |                             |  |  |

| SP51   | TssH2doZ               | SS3 ↑ to SDO3 Output<br>High-Impedance                                                                                         | 10           | _                             | 50   | ns    | (Note 4)                    |  |  |

| SP52   | TscH2ssH,<br>TscL2ssH  | SS3 ↑ after SCK3 Edge                                                                                                          | 1.5 Tcy + 40 | _                             | _    | ns    | (Note 4)                    |  |  |

- **Note 1:** These parameters are characterized, but are not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK3 is 66.7 ns. Therefore, the SCK3 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI3 pins.

- 5: For dsPIC33EPXXXGSX06 and dsPIC33EPXXXGSX08 devices with a fixed SCK3 pin.

TABLE 30-53: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

| AC CH        | ARACTE          | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) (2) Operating temperature $-40^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{Ta} \leq +125^{\circ}\text{C}$ for Extended |       |                                  |         |        |                                       |  |  |  |

|--------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------|---------|--------|---------------------------------------|--|--|--|

| Param<br>No. | Symbol          | Characteristics                                                                                                                                                                                                                                          | Min.  | . Typ. <sup>(1)</sup> Max. Units |         | Units  | Conditions                            |  |  |  |

|              |                 |                                                                                                                                                                                                                                                          |       | Clo                              | ck Para | meters |                                       |  |  |  |

| AD50         | TAD             | ADC Clock Period                                                                                                                                                                                                                                         | 14.28 | _                                |         | ns     |                                       |  |  |  |

|              | Throughput Rate |                                                                                                                                                                                                                                                          |       |                                  |         |        |                                       |  |  |  |

| AD51         | FTP             | SH0-SH3                                                                                                                                                                                                                                                  | _     | _                                | 3.25    | •      | 70 MHz ADC clock, 12 bits, no pending |  |  |  |

|              |                 | SH4                                                                                                                                                                                                                                                      |       | _                                | 3.25    | Msps   | conversion at time of trigger         |  |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

#### TABLE 30-54: HIGH-SPEED ANALOG COMPARATOR MODULE SPECIFICATIONS

| AC/DC        | CHARAC | [ERISTICS                                         | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) <sup>(2)</sup> Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |    |      |    |                                                                                                                    |  |

|--------------|--------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|----|--------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic                                    | Min. Typ. Max. Units Comments                                                                                                                                                                                                                                   |    |      |    |                                                                                                                    |  |

| CM10         | VIOFF  | Input Offset Voltage                              | -35                                                                                                                                                                                                                                                             | ±5 | 35   | mV |                                                                                                                    |  |

| CM11         | VICM   | Input Common-Mode<br>Voltage Range <sup>(1)</sup> | 0                                                                                                                                                                                                                                                               | _  | AVDD | V  |                                                                                                                    |  |

| CM13         | CMRR   | Common-Mode<br>Rejection Ratio                    | 60                                                                                                                                                                                                                                                              | _  | _    | dB |                                                                                                                    |  |

| CM14         | TRESP  | Large Signal Response                             | _                                                                                                                                                                                                                                                               | 15 |      | ns | V+ input step of 100 mV while V- input is held at AVDD/2. Delay measured from analog input pin to PWMx output pin. |  |

| CM15         | VHYST  | Input Hysteresis                                  | 5                                                                                                                                                                                                                                                               | 10 | 20   | mV | Depends on HYSSEL<1:0>                                                                                             |  |

| CM16         | Ton    | Comparator Enabled to Valid Output                | _                                                                                                                                                                                                                                                               | _  | 1    | μs |                                                                                                                    |  |

Note 1: These parameters are for design guidance only and are not tested in manufacturing.

<sup>2:</sup> The ADC module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is ensured, but not characterized.

<sup>2:</sup> The comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

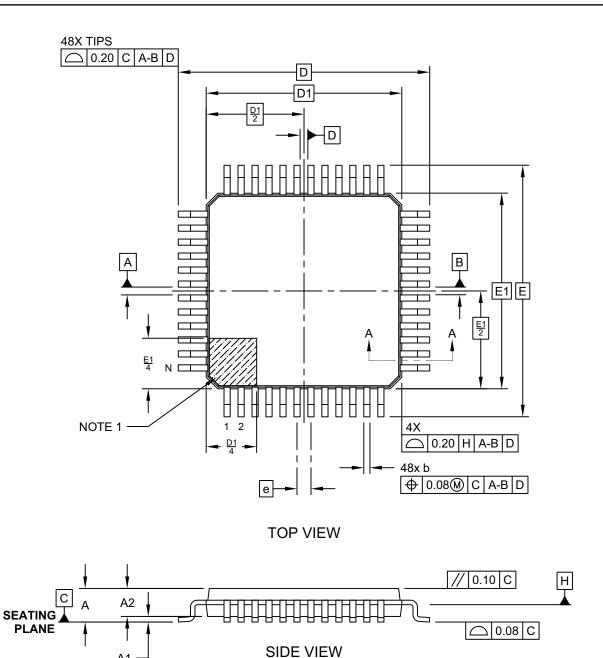

#### 48-Lead Thin Quad Flatpack (PT) - 7x7x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-300-PT Rev A Sheet 1 of 2

| SPIx Slave, Frame Master Connection                                                                                                                                                                                                                                                                         |                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| SPIx Slave, Frame Slave Connection                                                                                                                                                                                                                                                                          |                                                         |

| Suggested Oscillator Circuit Placement                                                                                                                                                                                                                                                                      |                                                         |

| Timerx (x = 2 through 5)                                                                                                                                                                                                                                                                                    |                                                         |

| Type B/Type C Timer Pair (32-Bit Timer)                                                                                                                                                                                                                                                                     |                                                         |

| UARTx Module                                                                                                                                                                                                                                                                                                | 253                                                     |

| Watchdog Timer (WDT)                                                                                                                                                                                                                                                                                        | 356                                                     |

| Brown-out Reset (BOR)                                                                                                                                                                                                                                                                                       | 347, 355                                                |

| •                                                                                                                                                                                                                                                                                                           |                                                         |

| С                                                                                                                                                                                                                                                                                                           |                                                         |

| C Compilers                                                                                                                                                                                                                                                                                                 |                                                         |

| MPLAB XC                                                                                                                                                                                                                                                                                                    | 372                                                     |

| CAN Module                                                                                                                                                                                                                                                                                                  |                                                         |

| Control Registers                                                                                                                                                                                                                                                                                           | 309                                                     |

| Message Buffers                                                                                                                                                                                                                                                                                             | 328                                                     |

| Word 0                                                                                                                                                                                                                                                                                                      | 328                                                     |

| Word 1                                                                                                                                                                                                                                                                                                      | 328                                                     |

| Word 2                                                                                                                                                                                                                                                                                                      | 329                                                     |

| Word 3                                                                                                                                                                                                                                                                                                      | 329                                                     |

| Word 4                                                                                                                                                                                                                                                                                                      | 330                                                     |

| Word 5                                                                                                                                                                                                                                                                                                      | 330                                                     |

| Word 6                                                                                                                                                                                                                                                                                                      | 331                                                     |

| Word 7                                                                                                                                                                                                                                                                                                      | 331                                                     |

| Modes of Operation                                                                                                                                                                                                                                                                                          | 308                                                     |

| Overview                                                                                                                                                                                                                                                                                                    | 307                                                     |

| CAN Module (CAN)                                                                                                                                                                                                                                                                                            | 307                                                     |

| CLC                                                                                                                                                                                                                                                                                                         |                                                         |

| Control Registers                                                                                                                                                                                                                                                                                           | 262                                                     |

| Code Examples                                                                                                                                                                                                                                                                                               |                                                         |

| Port Write/Read                                                                                                                                                                                                                                                                                             | 130                                                     |

| PWM Write-Protected Register                                                                                                                                                                                                                                                                                |                                                         |

| Unlock Sequence                                                                                                                                                                                                                                                                                             | 188                                                     |

|                                                                                                                                                                                                                                                                                                             |                                                         |

|                                                                                                                                                                                                                                                                                                             |                                                         |

| PWRSAV Instruction Syntax                                                                                                                                                                                                                                                                                   | 115                                                     |

| PWRSAV Instruction Syntax  Code Protection                                                                                                                                                                                                                                                                  | 115<br>347, 357                                         |

| PWRSAV Instruction Syntax                                                                                                                                                                                                                                                                                   | 115<br>347, 357<br>347, 357                             |

| PWRSAV Instruction Syntax                                                                                                                                                                                                                                                                                   | 115<br>347, 357<br>347, 357                             |

| PWRSAV Instruction Syntax                                                                                                                                                                                                                                                                                   | 115<br>347, 357<br>347, 357<br>259                      |

| PWRSAV Instruction Syntax                                                                                                                                                                                                                                                                                   |                                                         |

| PWRSAV Instruction Syntax                                                                                                                                                                                                                                                                                   | 115<br>347, 357<br>347, 357<br>259<br>347               |

| PWRSAV Instruction Syntax                                                                                                                                                                                                                                                                                   | 115<br>347, 357<br>347, 357<br>259<br>347<br>349<br>348 |

| PWRSAV Instruction Syntax                                                                                                                                                                                                                                                                                   | 115<br>347, 357<br>347, 357<br>259<br>347<br>349<br>348 |

| PWRSAV Instruction Syntax  Code Protection                                                                                                                                                                                                                                                                  |                                                         |

| PWRSAV Instruction Syntax  Code Protection                                                                                                                                                                                                                                                                  |                                                         |

| PWRSAV Instruction Syntax  Code Protection  CodeGuard Security  Configurable Logic Cell (CLC)  Configurable Logic Cell. See CLC.  Configuration Bits  Description  Configuration Register Map  Constant-Current Source  Control Register  Description  Features Overview                                    |                                                         |

| PWRSAV Instruction Syntax  Code Protection  CodeGuard Security  Configurable Logic Cell (CLC)  Configurable Logic Cell. See CLC.  Configuration Bits  Description  Configuration Register Map  Constant-Current Source  Control Register  Description  Features Overview  Controller Area Network. See CAN. |                                                         |

| PWRSAV Instruction Syntax  Code Protection  CodeGuard Security                                                                                                                                                                                                                                              |                                                         |

| PWRSAV Instruction Syntax  Code Protection  CodeGuard Security                                                                                                                                                                                                                                              |                                                         |

| PWRSAV Instruction Syntax  Code Protection  CodeGuard Security                                                                                                                                                                                                                                              |                                                         |

| PWRSAV Instruction Syntax  Code Protection  CodeGuard Security                                                                                                                                                                                                                                              |                                                         |

| PWRSAV Instruction Syntax  Code Protection                                                                                                                                                                                                                                                                  |                                                         |

| ט                                        |      |

|------------------------------------------|------|

| Data Address Space                       | 3    |

| Memory Map for dsPIC33EP64GS70X/80X      |      |

| Devices                                  | 38   |

| Near Data Space                          |      |

| Organization, Alignment                  |      |

| SFR Space                                |      |

| Width                                    |      |

| Data Space                               |      |

| Extended X                               | 5    |

| Paged Data Memory Space (figure)         |      |

| Paged Memory Scheme                      |      |

|                                          | 4    |

| DC Characteristics                       | 0.01 |

| Brown-out Reset (BOR)                    |      |

| Constant-Current Source Specifications   |      |

| DACx Output (DACOUTx Pin) Specifications |      |

| Doze Current (IDOZE)                     | 38   |

| I/O Pin Input Specifications             |      |

| I/O Pin Output Specifications            |      |

| Idle Current (IIDLE)                     | 379  |

| Operating Current (IDD)                  |      |

| Operating MIPS vs. Voltage               | 376  |

| Power-Down Current (IPD)                 | 380  |

| Program Memory                           | 386  |

| Temperature and Voltage Specifications   | 37   |

| Watchdog Timer Delta Current (ΔIWDT)     |      |

| DC/AC Characteristics                    |      |

| Graphs and Tables                        | 43!  |

| Demo/Development Boards, Evaluation and  |      |

| Starter Kits                             | 374  |

| Development Support                      | 37   |

| Device Calibration                       |      |

| Addresses                                |      |

| and Identification                       |      |

|                                          | 33   |

| Device Programmer                        | 27   |

| MPLAB PM3                                | 37   |

| Direct Memory Access. See DMA.           |      |

| DMA Controller                           |      |

| Channel to Peripheral Associations       |      |

| Control Registers                        |      |

| DMAxCNT                                  |      |

| DMAxCON                                  |      |

| DMAxPAD                                  |      |

| DMAxREQ                                  |      |

| DMAxSTAL/H                               |      |

| DMAxSTBL/H                               | 92   |

| Supported Peripherals                    | 89   |

| Doze Mode                                | 11   |

| DSP Engine                               | 30   |

| _                                        |      |

| E                                        |      |

| Electrical Characteristics               | 37   |

| AC                                       |      |

| Equations                                |      |

| Device Operating Frequency               | 10!  |

| FPLLO Calculation                        |      |

| Fvco Calculation                         |      |

| Relationship Between Device and SPIx     |      |

| Clock Speed                              | 244  |

| Erroto                                   | 24-  |

| USPIC33EPXXXGS/UX/6UX FAIVILT |  |  |  |  |  |  |

|-------------------------------|--|--|--|--|--|--|

| NOTES:                        |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |