Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 51                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| /oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs806t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Pin Diagrams**

| Pin | Pin Function                                       | Pin | Pin Function                      |

|-----|----------------------------------------------------|-----|-----------------------------------|

| 1   | MCLR                                               | 15  | PGEC3/SCL2/RP47/RB15              |

| 2   | AN0/CMP1A/PGA1P1/ <b>RP16</b> /RA0                 | 16  | TDO/AN19/PGA2N2/ <b>RP37</b> /RB5 |

| 3   | AN1/CMP1B/PGA1P2/PGA2P1/ <b>RP17</b> /RA1          | 17  | PGED1/TDI/AN20/SCL1/RP38/RB6      |

| 4   | AN2/CMP1C/CMP2A/PGA1P3/PGA2P2/RP18/RA2             | 18  | PGEC1/AN21/SDA1/RP39/RB7          |

| 5   | AN3/CMP1D/CMP2B/PGA2P3/RP32/RB0                    | 19  | Vss                               |

| 6   | AN4/CMP2C/CMP3A/ISRC4/RP41/RB9                     | 20  | VCAP                              |

| 7   | AVDD                                               | 21  | TMS/PWM3H/ <b>RP43</b> /RB11      |

| 8   | Vss                                                | 22  | TCK/PWM3L/ <b>RP44</b> /RB12      |

| 9   | OSCI/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1           | 23  | PWM2H/ <b>RP45</b> /RB13          |

| 10  | OSC2/CLKO/AN7/CMP3D/CMP4B/PGA1N2/ <b>RP34</b> /RB2 | 24  | PWM2L/ <b>RP46</b> /RB14          |

| 11  | PGED2/DACOUT1/AN18/INT0/RP35/RB3                   | 25  | PWM1H/ <b>RP20</b> /RA4           |

| 12  | PGEC2/ADTRG31/EXTREF1/RP36/RB4                     | 26  | PWM1L/ <b>RP19</b> /RA3           |

| 13  | VDD                                                | 27  | AVss                              |

| 14  | PGED3/SDA2/FLT31/ <b>RP40</b> /RB8                 | 28  | AVDD                              |

**Legend: Shaded pins** are up to 5 VDC tolerant.

RPn represents remappable peripheral functions. See Table 11-12 and Table 11-13 for the complete list of remappable sources.

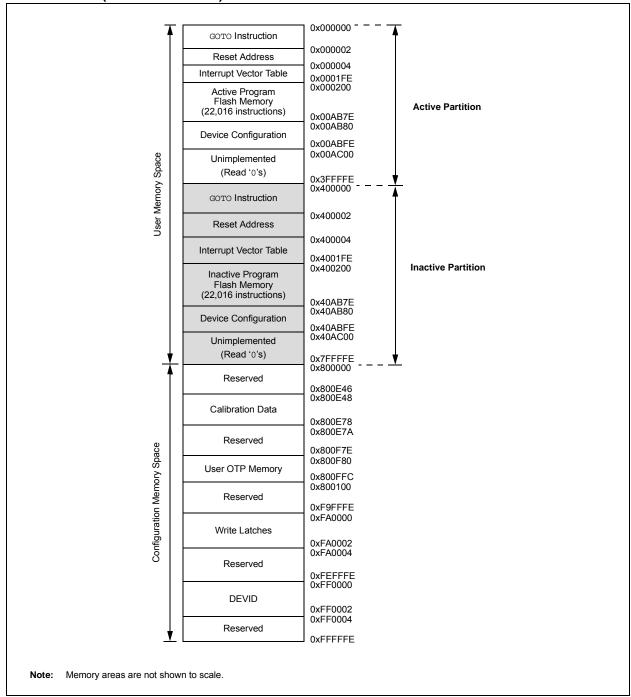

FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP128GS70X/80X DEVICES (DUAL PARTITION)

TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

| Intermed Course                             | Vector  | IRQ     | IVT Address       | In                   | terrupt Bit Lo       | cation                        |

|---------------------------------------------|---------|---------|-------------------|----------------------|----------------------|-------------------------------|

| Interrupt Source                            | #       | #       | IVT Address       | Flag                 | Enable               | Priority                      |

| PSES – PWM Secondary Special<br>Event Match | 81      | 73      | 0x0000A6          | IFS4<9><br>PSESIF    | IEC4<9><br>PSESIE    | IPC18<6:4><br>PSESIP<2:0>     |

| Reserved                                    | 82-97   | 74-89   | 0x0000A8-0x0000C6 | 1                    | _                    | _                             |

| SPI3TX – SPI3 Transfer Done                 | 98      | 90      | 0x0000C8          | IFS5<10><br>SPI3TXIF | IEC5<10><br>SPI3TXIE | IPC22<10:8><br>SPI3TXIP<2:0>  |

| SPI3RX – SPI3 Receive Done                  | 99      | 91      | 0x0000CA          | IFS5<10><br>SPI3RXIF | IEC5<11><br>SPI3RXIE | IPC22<14:12><br>SPI3RXIP<2:0> |

| Reserved                                    | 100-101 | 92-93   | 0x0000CC-0x0000CE | _                    | _                    | _                             |

| PWM1 – PWM1 Interrupt                       | 102     | 94      | 0x0000D0          | IFS5<14><br>PWM1IF   | IEC5<14><br>PWM1IE   | IPC23<10:8><br>PWM1IP<2:0>    |

| PWM2 – PWM2 Interrupt                       | 103     | 95      | 0x0000D2          | IFS5<15><br>PWM2IF   | IEC5<15><br>PWM2IE   | IPC23<14:12><br>PWM2IP<2:0>   |

| PWM3 – PWM3 Interrupt                       | 104     | 96      | 0x0000D4          | IFS6<0><br>PWM3IF    | IEC6<0><br>PWM3IE    | IPC24<2:0><br>PWM3IP<2:0>     |

| PWM4 – PWM4 Interrupt                       | 105     | 97      | 0x0000D6          | IFS6<1><br>PWM4IF    | IEC6<1><br>PWM4IE    | IPC24<6:4><br>PWM4IP<2:0>     |

| PWM5 – PWM5 Interrupt                       | 106     | 98      | 0x0000D8          | IFS6<2><br>PWM5IF    | IEC6<2><br>PWM5IE    | IPC24<10:8><br>PWM5IP<2:0>    |

| PWM6 – PWM6 Interrupt                       | 107     | 99      | 0x0000DA          | IFS6<3><br>PWM6IF    | IEC6<3><br>PWM6IE    | IPC24<14:12><br>PWM6IP<2:0>   |

| PWM7 – PWM7 Interrupt                       | 108     | 100     | 0x0000DC          | IFS6<4><br>PWM7IF    | IEC6<4><br>PWM7IE    | IPC25<2:0><br>PWM7IP<2:0>     |

| PWM8 – PWM8 Interrupt                       | 109     | 101     | 0x0000DE          | IFS6<5><br>PWM8IF    | IEC6<5><br>PWM8IE    | IPC25<6:4><br>PWM8IP<2:0>     |

| Reserved                                    | 110     | 102     | 0x0000E0          | _                    | _                    | _                             |

| AC2 – Analog Comparator 2 Interrupt         | 111     | 103     | 0x0000E2          | IFS6<7><br>AC2IF     | IEC6<7><br>AC2IE     | IPC25<14:12><br>AC2IP<2:0>    |

| AC3 – Analog Comparator 3 Interrupt         | 112     | 104     | 0x0000E4          | IFS6<8><br>AC3IF     | IEC6<8><br>AC3IE     | IPC26<2:0><br>AC3IP<2:0>      |

| AC4 – Analog Comparator 4 Interrupt         | 113     | 105     | 0x0000E6          | IFS6<9><br>AC4IF     | IEC6<9><br>AC4IE     | IPC26<6:4><br>AC4IP<2:0>      |

| Reserved                                    | 114-117 | 106-109 | 0x0000E8-0x0000EE | _                    | _                    | _                             |

| AN0 Conversion Done                         | 118     | 110     | 0x0000F0          | IFS6<14><br>AN0IF    | IEC6<14><br>AN0IE    | IPC27<10:8><br>AN0IP<2:0>     |

| AN1 Conversion Done                         | 119     | 111     | 0x0000F2          | IFS6<15><br>AN1IF    | IEC6<15><br>AN1IE    | IPC27<14:12><br>AN1IP<2:0>    |

| AN2 Conversion Done                         | 120     | 112     | 0x0000F4          | IFS7<0><br>AN2IF     | IEC7<0><br>AN2IE     | IPC28<2:0><br>AN2IP<2:0>      |

| AN3 Conversion Done                         | 121     | 113     | 0x0000F6          | IFS7<1><br>AN3IF     | IEC7<1><br>AN3IE     | IPC28<6:4><br>AN3IP<2:0>      |

| AN4 Conversion Done                         | 122     | 114     | 0x0000F8          | IFS7<2><br>AN4IF     | IEC7<2><br>AN4IE     | IPC28<10:8><br>AN4IP<2:0>     |

| AN5 Conversion Done                         | 123     | 115     | 0x0000FA          | IFS7<3><br>AN5IF     | IEC7<3><br>AN5IE     | IPC28<14:12><br>AN5IP<2:0>    |

| AN6 Conversion Done                         | 124     | 116     | 0x0000FC          | IFS7<4><br>AN6IF     | IEC7<4><br>AN6IE     | IPC29<2:0><br>AN6IP<2:0>      |

| AN7 Conversion Done                         | 125     | 117     | 0x0000FE          | IFS7<5><br>AN7IF     | IEC7<5><br>AN7IE     | IPC29<6:4><br>AN7IP<2:0>      |

| Reserved                                    | 126-131 | 118-123 | 0x000100-0x00010A | _                    | _                    | _                             |

### 9.5 Oscillator Control Registers

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-y                | R/W-y                | R/W-y                |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| _      | COSC2 | COSC1 | COSC0 | _   | NOSC2 <sup>(2)</sup> | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/W-0   | R/W-0  | R-0  | U-0 | R/W-0             | U-0 | U-0 | R/W-0 |

|---------|--------|------|-----|-------------------|-----|-----|-------|

| CLKLOCK | IOLOCK | LOCK | _   | CF <sup>(3)</sup> | _   | _   | OSWEN |

| bit 7   |        |      |     |                   |     |     | bit 0 |

Legend:y = Value set from Configuration bits on PORR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 **COSC<2:0>:** Current Oscillator Selection bits (read-only)

111 = Fast RC Oscillator (FRC) with Divide-by-n

110 = Fast RC Oscillator (FRC) with Divide-by-16

101 = Low-Power RC Oscillator (LPRC)

100 = Reserved

011 = Primary Oscillator (XT, HS, EC) with PLL

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)

000 = Fast RC Oscillator (FRC)

bit 11 **Unimplemented:** Read as '0'

bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(2)</sup>

111 = Fast RC Oscillator (FRC) with Divide-by-n

110 = Fast RC Oscillator (FRC) with Divide-by-16

101 = Low-Power RC Oscillator (LPRC)

100 = Reserved

011 = Primary Oscillator (XT, HS, EC) with PLL

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)

000 = Fast RC Oscillator (FRC)

bit 7 CLKLOCK: Clock Lock Enable bit

1 = If (FCKSM0 = 1), then clock and PLL configurations are locked; if (FCKSM0 = 0), then clock and PLL configurations may be modified

0 = Clock and PLL selections are not locked, configurations may be modified

bit 6 IOLOCK: I/O Lock Enable bit

1 = I/O lock is active

0 = I/O lock is not active

bit 5 LOCK: PLL Lock Status bit (read-only)

1 = Indicates that PLL is in lock or PLL start-up timer is satisfied

0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled

**Note 1:** Writes to this register require an unlock sequence.

2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

3: This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and will trigger an oscillator failure trap.

### 11.0 I/O PORTS

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70000598) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the Parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

### 11.1 Parallel I/O (PIO) Ports

Generally, a Parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in

which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/Os. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device are disabled. This means the corresponding LATx and TRISx registers, and the port pin are read as zeros. Table 11-1 through Table 11-5 show ANSELx bits' availability for device variants.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

**Output Multiplexers Peripheral Module** г Peripheral Input Data Peripheral Module Enable Peripheral Output Enable Output Enable Peripheral Output Data **PIO Module** Output Data Read TRISx 1 Data Bus ח Q I/O Pin WR TRISx TRISx Latch D a WR LATx + WR PORTX Data Latch Read LATx Input Data Read PORTx

FIGURE 11-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

### REGISTER 11-3: LATX: PORTX DATA LATCH REGISTER(1)

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|------------|-------|-------|-------|-------|-------|-------|-------|

| LATx<15:8> |       |       |       |       |       |       |       |

| bit 15     |       |       | bit 8 |       |       |       |       |

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|

| LATx<7:0> |       |       |       |       |       |       |       |

| bit 7 bit |       |       |       |       |       |       |       |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 LATx<15:0>: PORTx Data Latch bits

1 = The latch content is '1' 0 = The latch content is '0'

Note 1: See Table 11-1, Table 11-2, Table 11-3, Table 11-4 and Table 11-5 for individual bit availability in this register.

### REGISTER 11-4: ODCx: PORTx OPEN-DRAIN CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | ODCx  | <15:8> |       |       |       |

| bit 15 |       |       |       |        |       |       |       |

| R/W-0     | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------|-----------|-------|-------|-------|-------|-------|-------|--|--|

|           | ODCx<7:0> |       |       |       |       |       |       |  |  |

| bit 7 bit |           |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **PORTx<15:0>:** PORTx Open-Drain Control bits

1 = The pin acts as an open-drain output pin if TRISx is '0'

0 = The pin acts as a normal pin

Note 1: See Table 11-1, Table 11-2, Table 11-3, Table 11-4 and Table 11-5 for individual bit availability in this register.

TABLE 11-12: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

| Input Name <sup>(1)</sup> | Function Name | Register | Configuration Bits |

|---------------------------|---------------|----------|--------------------|

| External Interrupt 1      | INT1          | RPINR0   | INT1R<7:0>         |

| External Interrupt 2      | INT2          | RPINR1   | INT2R<7:0>         |

| Timer1 External Clock     | T1CK          | RPINR2   | T1CKR<7:0>         |

| Timer2 External Clock     | T2CK          | RPINR3   | T2CKR<7:0>         |

| Timer3 External Clock     | T3CK          | RPINR3   | T3CKR<7:0>         |

| Input Capture 1           | IC1           | RPINR7   | IC1R<7:0>          |

| Input Capture 2           | IC2           | RPINR7   | IC2R<7:0>          |

| Input Capture 3           | IC3           | RPINR8   | IC3R<7:0>          |

| Input Capture 4           | IC4           | RPINR8   | IC4R<7:0>          |

| Output Compare Fault A    | OCFA          | RPINR11  | OCFAR<7:0>         |

| PWM Fault 1               | FLT1          | RPINR12  | FLT1R<7:0>         |

| PWM Fault 2               | FLT2          | RPINR12  | FLT2R<7:0>         |

| PWM Fault 3               | FLT3          | RPINR13  | FLT3R<7:0>         |

| PWM Fault 4               | FLT4          | RPINR13  | FLT4R<7:0>         |

| UART1 Receive             | U1RX          | RPINR18  | U1RXR<7:0>         |

| UART1 Clear-to-Send       | U1CTS         | RPINR18  | U1CTSR<7:0>        |

| UART2 Receive             | U2RX          | RPINR19  | U2RXR<7:0>         |

| UART2 Clear-to-Send       | U2CTS         | RPINR19  | U2CTSR<7:0>        |

| SPI1 Data Input           | SDI1          | RPINR20  | SDI1R<7:0>         |

| SPI1 Clock Input          | SCK1          | RPINR20  | SCK1R<7:0>         |

| SPI1 Slave Select         | SS1           | RPINR21  | SS1R<7:0>          |

| CAN1 Receive              | C1RX          | PRINR26  | C1RXR<7:0>         |

| CAN2 Receive              | C2RX          | PRINR26  | C2RXR<7:0>         |

| SPI3 Data Input           | SDI3          | RPINR29  | SDI3R<7:0>         |

| SPI3 Clock Input          | SCK3          | RPINR29  | SCK3R<7:0>         |

| SPI3 Slave Select         | SS3           | RPINR30  | SS3R<7:0>          |

| SPI2 Data Input           | SDI2          | RPINR22  | SDI2R<7:0>         |

| SPI2 Clock Input          | SCK2          | RPINR22  | SCK2R<7:0>         |

| SPI2 Slave Select         | SS2           | RPINR23  | SS2R<7:0>          |

| PWM Synchronous Input 1   | SYNCI1        | RPINR37  | SYNCI1R<7:0>       |

| PWM Synchronous Input 2   | SYNCI2        | RPINR38  | SYNCI2R<7:0>       |

| PWM Fault 5               | FLT5          | RPINR42  | FLT5R<7:0>         |

| PWM Fault 6               | FLT6          | RPINR42  | FLT6R<7:0>         |

| PWM Fault 7               | FLT7          | RPINR43  | FLT7R<7:0>         |

| PWM Fault 8               | FLT8          | RPINR43  | FLT8R<7:0>         |

| CLC Input A               | CLCINA        | RPINR45  | CLCINA<7:0>        |

| CLC Input B               | CLCINB        | RPINR46  | CLCINB<7:0>        |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

#### 13.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- · Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- · Timer Gate Operation

- · Selectable Prescaler Settings

- · Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note:

For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-2.

#### 13.1 Timer Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 13.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

#### 16.0 HIGH-SPEED PWM

Note:

This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM Module" (DS70000323) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The high-speed PWM on dsPIC33EPXXXGS70X/80X devices supports a wide variety of PWM modes and output formats. This PWM module is ideal for power conversion applications, such as:

- · AC/DC Converters

- · DC/DC Converters

- · Power Factor Correction

- Uninterruptible Power Supply (UPS)

- · Inverters

- · Battery Chargers

- · Digital Lighting

#### 16.1 Features Overview

The high-speed PWM module incorporates the following features:

- Eight PWMx Generators with Two Outputs per Generator

- · Two Master Time Base modules

- Individual Time Base and Duty Cycle for each PWM Output

- Duty Cycle, Dead Time, Phase Shift and a Frequency Resolution of 1.04 ns

- · Independent Fault and Current-Limit Inputs

- · Redundant Output

- True Independent Output

- · Center-Aligned PWM mode

- · Output override control

- Chop mode (also known as Gated mode)

- · Special Event Trigger

- Dual Trigger from PWMx to Analog-to-Digital Converter (ADC)

- · PWMxL and PWMxH Output Pin Swapping

- Independent PWMx Frequency, Duty Cycle and Phase-Shift Changes

- Enhanced Leading-Edge Blanking (LEB) Functionality

- · PWM Capture Functionality

Note:

Duty cycle, dead time, phase shift and frequency resolution is 8.32 ns in Center-Aligned PWM mode.

Figure 16-1 conceptualizes the PWM module in a simplified block diagram. Figure 16-2 illustrates how the module hardware is partitioned for each PWMx output pair for the Complementary PWM mode.

The PWM module contains eight PWM generators. The module has up to 16 PWMx output pins: PWM1H/PWM1L through PWM8H/PWM8L. For complementary outputs, these 16 I/O pins are grouped into high/low pairs. PWM1 through PWM6 can be used to trigger an ADC conversion.

#### 16.2 Feature Description

The PWM module is designed for applications that require:

- · High resolution at high PWM frequencies

- The ability to drive Standard, Edge-Aligned, Center-Aligned Complementary mode and Push-Pull mode outputs

- · The ability to create multiphase PWM outputs

Two common, medium power converter topologies are push-pull and half-bridge. These designs require the PWM output signal to be switched between alternate pins, as provided by the Push-Pull PWM mode.

Phase-shifted PWM describes the situation where each PWM generator provides outputs, but the phase relationship between the generator outputs is specifiable and changeable.

Multiphase PWM is often used to improve DC/DC Converter load transient response, and reduce the size of output filter capacitors and inductors. Multiple DC/DC Converters are often operated in parallel, but phase shifted in time. A single PWM output, operating at 250 kHz, has a period of 4  $\mu s$  but an array of four PWM channels, staggered by 1  $\mu s$  each, yields an effective switching frequency of 1 MHz. Multiphase PWM applications typically use a fixed-phase relationship.

Variable phase PWM is useful in Zero Voltage Transition (ZVT) power converters. Here, the PWM duty cycle is always 50% and the power flow is controlled by varying the relative phase shift between the two PWM generators.

### REGISTER 16-3: PTPER: PWMx PRIMARY MASTER TIME BASE PERIOD REGISTER (1,2)

| R/W-1       | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| PTPER<15:8> |       |       |       |       |       |       |       |

| bit 15      |       |       |       | bit 8 |       |       |       |

| R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | PTPE  | R<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       |       |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 PTPER<15:0>: Primary Master Time Base (PMTMR) Period Value bits

Note 1: The PWMx time base has a minimum value of 0x0010 and a maximum value of 0xFFF8.

2: Any period value that is less than 0x0028 must have the Least Significant 3 bits set to '0', thus yielding a period resolution at 8.32 ns (at fastest auxiliary clock rate).

### REGISTER 16-4: SEVTCMP: PWMx SPECIAL EVENT COMPARE REGISTER<sup>(1)</sup>

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|

| SEVTCMP<12:5> |       |       |       |       |       |       |       |  |

| bit 15        |       |       |       |       |       |       | bit 8 |  |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-------|-----|-----|-------|

|       | _     | _     | _     |       |     |     |       |

| bit 7 |       | _     |       |       |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 **SEVTCMP<12:0>:** Special Event Compare Count Value bits

bit 2-0 **Unimplemented:** Read as '0'

Note 1: One LSB = 1.04 ns (at fastest auxiliary clock rate); therefore, the minimum SEVTCMP resolution is 8.32 ns.

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

# REGISTER 16-24: LEBCONX: PWMX LEADING-EDGE BLANKING (LEB) CONTROL REGISTER (x = 1 to 8)

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0   | U-0 | U-0   |

|--------|-------|-------|-------|----------|---------|-----|-------|

| PHR    | PHF   | PLR   | PLF   | FLTLEBEN | CLLEBEN | _   | _     |

| bit 15 |       |       |       |          |         |     | bit 8 |

| U-0   | U-0 | R/W-0              | R/W-0              | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|--------------------|--------------------|-------|-------|-------|-------|

| _     | _   | BCH <sup>(1)</sup> | BCL <sup>(1)</sup> | BPHH  | BPHL  | BPLH  | BPLL  |

| bit 7 |     |                    |                    |       |       |       | bit 0 |

| bit 15 | PHR: PWMxH Rising Edge Trigger Enable bit                                                                                                                       |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | <ul><li>1 = Rising edge of PWMxH will trigger the Leading-Edge Blanking counter</li><li>0 = Leading-Edge Blanking ignores the rising edge of PWMxH</li></ul>    |

| bit 14 | PHF: PWMxH Falling Edge Trigger Enable bit                                                                                                                      |

|        | <ul><li>1 = Falling edge of PWMxH will trigger the Leading-Edge Blanking counter</li><li>0 = Leading-Edge Blanking ignores the falling edge of PWMxH</li></ul>  |

| bit 13 | PLR: PWMxL Rising Edge Trigger Enable bit                                                                                                                       |

|        | <ul><li>1 = Rising edge of PWMxL will trigger the Leading-Edge Blanking counter</li><li>0 = Leading-Edge Blanking ignores the rising edge of PWMxL</li></ul>    |

| bit 12 | PLF: PWMxL Falling Edge Trigger Enable bit                                                                                                                      |

|        | <ul><li>1 = Falling edge of PWMxL will trigger the Leading-Edge Blanking counter</li><li>0 = Leading-Edge Blanking ignores the falling edge of PWMxL</li></ul>  |

| bit 11 | FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit                                                                                                          |

|        | <ul><li>1 = Leading-Edge Blanking is applied to the selected Fault input</li><li>0 = Leading-Edge Blanking is not applied to the selected Fault input</li></ul> |

| bit 10 | CLLEBEN: Current-Limit Leading-Edge Blanking Enable bit                                                                                                         |

|        | 1 = Leading-Edge Blanking is applied to the selected current-limit input                                                                                        |

**BCH:** Blanking in Selected Blanking Signal High Enable bit<sup>(1)</sup>

1 = State blanking (of current-limit and/or Fault input signals) when the selected blanking signal is high

0 = Leading-Edge Blanking is not applied to the selected current-limit input

0 = No blanking when the selected blanking signal is high

bit 4 BCL: Blanking in Selected Blanking Signal Low Enable bit<sup>(1)</sup>

W = Writable bit

'1' = Bit is set

1 = State blanking (of current-limit and/or Fault input signals) when the selected blanking signal is low

0 = No blanking when the selected blanking signal is low

bit 3 **BPHH:** Blanking in PWMxH High Enable bit

Unimplemented: Read as '0'

${\tt 1}$  = State blanking (of current-limit and/or Fault input signals) when the PWMxH output is high

0 = No blanking when the PWMxH output is high

bit 2 BPHL: Blanking in PWMxH Low Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxH output is low

0 = No blanking when the PWMxH output is low

Note 1: The blanking signal is selected via the BLANKSEL<3:0> bits in the AUXCONx register.

Legend:

bit 9-6

bit 5

R = Readable bit

-n = Value at POR

#### REGISTER 18-6: SPIXIMSKL: SPIX INTERRUPT MASK REGISTER LOW

| U-0          | U-0 | U-0 | R/W-0    | R/W-0  | U-0 | U-0 | R/W-0    |  |

|--------------|-----|-----|----------|--------|-----|-----|----------|--|

| _            | _   | _   | FRMERREN | BUSYEN | _   | _   | SPITUREN |  |

| bit 15 bit 8 |     |     |          |        |     |     |          |  |

| R/W-0       | R/W-0    | R/W-0   | U-0 | R/W-0   | U-0 | R/W-0    | R/W-0    |  |

|-------------|----------|---------|-----|---------|-----|----------|----------|--|

| SRMTEN      | SPIROVEN | SPIRBEN | _   | SPITBEN | _   | SPITBFEN | SPIRBFEN |  |

| bit 7 bit 0 |          |         |     |         |     |          |          |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12 FRMERREN: Enable Interrupt Events via FRMERR bit

1 = Frame error generates an interrupt event

0 = Frame error does not generate an interrupt event

bit 11 BUSYEN: Enable Interrupt Events via SPIBUSY bit

1 = SPIBUSY generates an interrupt event

0 = SPIBUSY does not generate an interrupt event

bit 10-9 **Unimplemented:** Read as '0'

bit 8 SPITUREN: Enable Interrupt Events via SPITUR bit

1 = Transmit Underrun (TUR) generates an interrupt event0 = Transmit Underrun does not generate an interrupt event

bit 7 SRMTEN: Enable Interrupt Events via SRMT bit

1 = Shift Register Empty (SRMT) generates interrupt events0 = Shift Register Empty does not generate interrupt events

bit 6 SPIROVEN: Enable Interrupt Events via SPIROV bit

1 = SPIx Receive Overflow (ROV) generates an interrupt event0 = SPIx Receive Overflow does not generate an interrupt event

bit 5 SPIRBEN: Enable Interrupt Events via SPIRBE bit

1 = SPIx RX buffer empty generates an interrupt event

0 = SPIx RX buffer empty does not generate an interrupt event

bit 4 Unimplemented: Read as '0'

bit 3 SPITBEN: Enable Interrupt Events via SPITBE bit

1 = SPIx transmit buffer empty generates an interrupt event

0 = SPIx transmit buffer empty does not generate an interrupt event

bit 2 Unimplemented: Read as '0'

bit 1 SPITBFEN: Enable Interrupt Events via SPITBF bit

1 = SPIx transmit buffer full generates an interrupt event

0 = SPIx transmit buffer full does not generate an interrupt event

bit 0 SPIRBFEN: Enable Interrupt Events via SPIRBF bit

1 = SPIx receive buffer full generates an interrupt event

0 = SPIx receive buffer full does not generate an interrupt event

### 21.1 Control Registers

The CLCx module is controlled by the following registers:

- CLCxCONL

- CLCxCONH

- CLCxSEL

- CLCxGLSL

- CLCxGLSH

The CLCx Control registers (CLCxCONL and CLCxCONH) are used to enable the module and interrupts, control the output enable bit, select output polarity and select the logic function. The CLCx Control registers also allow the user to control the logic polarity of not only the cell output, but also some intermediate variables.

The CLCx Input MUX Select register (CLCxSEL) allows the user to select up to 4 data input sources using the 4 data input selection multiplexers. Each multiplexer has a list of 8 data sources available.

The CLCx Gate Logic Input Select registers (CLCxGLSL and CLCxGLSH) allow the user to select which outputs from each of the selection MUXes are used as inputs to the input gates of the logic cell. Each data source MUX outputs both a true and a negated version of its output. All of these 8 signals are enabled, ORed together by the logic cell input gates.

### REGISTER 21-1: CLCxCONL: CLCx CONTROL REGISTER (LOW)

| R/W-0  | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | U-0 | U-0   |

|--------|-----|-----|-----|-------|-------|-----|-------|

| LCEN   | _   | _   | _   | INTP  | INTN  | _   | _     |

| bit 15 |     |     |     |       |       |     | bit 8 |

| R-0   | R-0   | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----|-----|-------|-------|-------|

| LCOE  | LCOUT | LCPOL | _   | _   | MODE2 | MODE1 | MODE0 |

| bit 7 |       |       |     |     |       |       | bit 0 |

| L | e | q | el | n | d |  |

|---|---|---|----|---|---|--|

|   |   |   |    |   |   |  |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 LCEN: CLCx Enable bit

1 = CLCx is enabled and mixing input signals0 = CLCx is disabled and has logic zero outputs

bit 14-12 **Unimplemented:** Read as '0'

bit 11 INTP: CLCx Positive Edge Interrupt Enable bit

1 = Interrupt will be generated when a rising edge occurs on LCOUT

0 = Interrupt will not be generated

bit 10 INTN: CLCx Negative Edge Interrupt Enable bit

1 = Interrupt will be generated when a falling edge occurs on LCOUT

0 = Interrupt will not be generated

bit 9-8 **Unimplemented:** Read as '0'

bit 7 LCOE: CLCx Port Enable bit

1 = CLCx port pin output is enabled 0 = CLCx port pin output is disabled

bit 6 LCOUT: CLCx Data Output Status bit

1 = CLCx output high 0 = CLCx output low

bit 5 LCPOL: CLCx Output Polarity Control bit

1 = The output of the module is inverted0 = The output of the module is not inverted

bit 4-3 **Unimplemented:** Read as '0'

#### 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming™ (ICSP™).

### 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

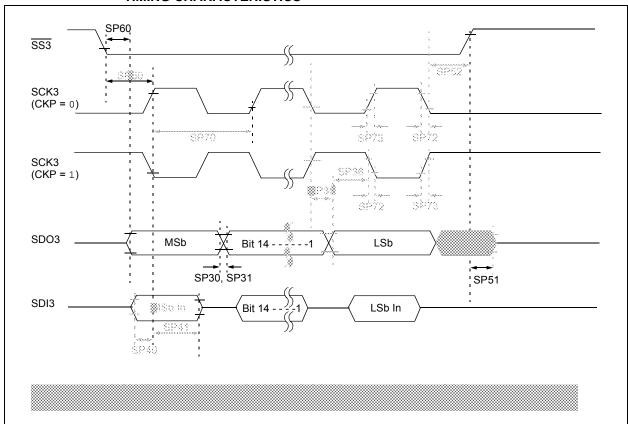

FIGURE 30-24: SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS<sup>(1,2)</sup>

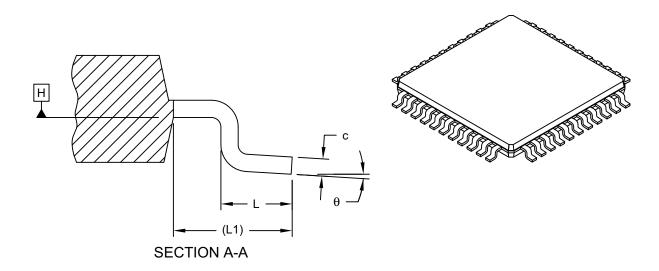

### 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units  |           |           | RS   |  |  |  |

|--------------------------|--------|-----------|-----------|------|--|--|--|

| Dimension                | Limits | MIN       | NOM       | MAX  |  |  |  |

| Number of Leads          | Ν      |           | 44        |      |  |  |  |

| Lead Pitch               | е      |           | 0.80 BSC  |      |  |  |  |

| Overall Height           | Α      | •         | -         | 1.20 |  |  |  |

| Standoff                 | A1     | 0.05      | -         | 0.15 |  |  |  |

| Molded Package Thickness | A2     | 0.95      | 1.00      | 1.05 |  |  |  |

| Overall Width            | Е      | 12.00 BSC |           |      |  |  |  |

| Molded Package Width     | E1     |           | 10.00 BSC |      |  |  |  |

| Overall Length           | D      |           | 12.00 BSC |      |  |  |  |

| Molded Package Length    | D1     |           | 10.00 BSC |      |  |  |  |

| Lead Width               | b      | 0.30      | 0.37      | 0.45 |  |  |  |

| Lead Thickness           | С      | 0.09      | -         | 0.20 |  |  |  |

| Lead Length              | Ĺ      | 0.45      | 0.60      | 0.75 |  |  |  |

| Footprint                | L1     | 1.00 REF  |           |      |  |  |  |

| Foot Angle               | θ      | 0°        | 3.5°      | 7°   |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Exact shape of each corner is optional.

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

$\label{eq:REF:Reference} \textit{REF: Reference Dimension, usually without tolerance, for information purposes only.}$

Microchip Technology Drawing C04-076C Sheet 2 of 2

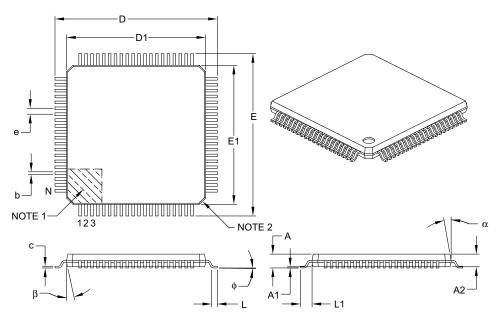

### 80-Lead Plastic Thin Quad Flatpack (PT) - 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          | MILLIMETERS |      |  |  |

|--------------------------|------------------|----------|-------------|------|--|--|

|                          | Dimension Limits | MIN      | NOM         | MAX  |  |  |

| Number of Leads          | N                |          | 80          |      |  |  |

| Lead Pitch               | е                |          | 0.50 BSC    |      |  |  |

| Overall Height           | A                | _        | _           | 1.20 |  |  |

| Molded Package Thickness | A2               | 0.95     | 1.00        | 1.05 |  |  |

| Standoff                 | A1               | 0.05     | _           | 0.15 |  |  |

| Foot Length              | L                | 0.45     | 0.60        | 0.75 |  |  |

| Footprint                | L1               | 1.00 REF |             |      |  |  |

| Foot Angle               | ф                | 0°       | 3.5°        | 7°   |  |  |

| Overall Width            | E                |          | 14.00 BSC   |      |  |  |

| Overall Length           | D                |          | 14.00 BSC   |      |  |  |

| Molded Package Width     | E1               |          | 12.00 BSC   |      |  |  |

| Molded Package Length    | D1               |          | 12.00 BSC   |      |  |  |

| Lead Thickness           | С                | 0.09     | _           | 0.20 |  |  |

| Lead Width               | b                | 0.17     | 0.22        | 0.27 |  |  |

| Mold Draft Angle Top     | α                | 11°      | 12°         | 13°  |  |  |

| Mold Draft Angle Bottom  | β                | 11°      | 12°         | 13°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-092B

| CNPDx (Input Change Notification                  | I2CxMSK (I2Cx Slave Mode Address Mask)     | 252 |

|---------------------------------------------------|--------------------------------------------|-----|

| Pull-Down Enable x)134                            | I2CxSTAT (I2Cx Status)                     |     |

| CNPUx (Input Change Notification                  | ICxCON1 (Input Capture x Control 1)        |     |

| Pull-up Enable x)133                              | ICxCON2 (Input Capture x Control 2)        |     |

| CORCON (Core Control)                             | INTCON1 (Interrupt Control 1)              |     |

| CTXTSTAT (CPU W Register Context Status)29        |                                            |     |

| ,                                                 | INTCON2 (Interrupt Control 2)              |     |

| CxBUFPNT1 (CANx Filters 0-3 Buffer Pointer 1) 318 | INTCON3 (Interrupt Control 3)              |     |

| CxBUFPNT2 (CANx Filters 4-7 Buffer Pointer 2) 319 | INTCON4 (Interrupt Control 4)              |     |

| CxBUFPNT3 (CANx Filters 8-11                      | INTTREG (Interrupt Control and Status)     |     |

| Buffer Pointer 3)319                              | IOCONx (PWMx I/O Control)                  |     |

| CxBUFPNT4 (CANx Filters 12-15                     | ISRCCON (Constant-Current Source Control)  |     |

| Buffer Pointer 4)320                              | LATx (PORTx Data Latch)                    | 132 |

| CxCFG1 (CANx Baud Rate Configuration 1)316        | LEBCONx (PWMx Leading-Edge                 |     |

| CxCFG2 (CANx Baud Rate Configuration 2)           | Blanking Control)                          | 209 |

| CxCTRL1 (CANx Control 1)309                       | LEBDLYx (PWMx Leading-Edge                 |     |

| CxCTRL2 (CANx Control 2)310                       | Blanking Delay)                            | 210 |

| CxEC (CANx Transmit/Receive Error Count) 316      | LFSR (Linear Feedback Shift)               |     |

| CxFCTRL (CANx FIFO Control)312                    | MDC (PWMx Master Duty Cycle)               |     |

| CxFEN1 (CANx Acceptance Filter Enable 1) 318      | NVMADR (Nonvolatile Memory Lower Address)  |     |

| CxFIFO (CANx FIFO Status)                         | NVMADRU (Nonvolatile Memory Upper Address) |     |

| CxFMSKSEL1 (CANx Filters 7-0                      | NVMCON (Nonvolatile Memory (NVM) Control)  |     |

| Mask Selection 1)                                 | NVMKEY (Nonvolatile Memory Key)            |     |

| CxFMSKSEL2 (CANx Filters 15-8                     | NVMSRCADR (NVM Source Data Address)        |     |

| Mask Selection 2)                                 | OCxCON1 (Output Compare x Control 1)       |     |

| CXINTE (CANX Interrupt Enable)315                 | OCxCON1 (Output Compare x Control 1)       |     |

|                                                   |                                            |     |

| CxINTF (CANx Interrupt Flag)                      | ODCx (PORTx Open-Drain Control)            |     |

| CxRXFnEID (CANx Acceptance Filter n               | OSCCON (Oscillator Control)                |     |

| Extended Identifier)                              | OSCTUN (FRC Oscillator Tuning)             |     |

| CxRXFnSID (CANx Acceptance Filter n               | PDCx (PWMx Generator Duty Cycle)           |     |

| Standard Identifier)                              | PGAxCAL (PGAx Calibration)                 |     |

| CxRXFUL1 (CANx Receive Buffer Full 1)325          | PGAxCON (PGAx Control)                     |     |

| CxRXFUL2 (CANx Receive Buffer Full 2)325          | PHASEx (PWMx Primary Phase-Shift)          |     |

| CxRXMnEID (CANx Acceptance Filter Mask n          | PLLFBD (PLL Feedback Divisor)              |     |

| Extended Identifier)324                           | PMD1 (Peripheral Module Disable Control 1) | 118 |

| CxRXMnSID (CANx Acceptance Filter Mask n          | PMD2 (Peripheral Module Disable Control 2) | 120 |

| Standard Identifier) 324                          | PMD3 (Peripheral Module Disable Control 3) | 12  |

| CxRXOVF1 (CANx Receive Buffer Overflow 1) 326     | PMD4 (Peripheral Module Disable Control 4) | 12  |

| CxRXOVF2 (CANx Receive Buffer Overflow 2) 326     | PMD6 (Peripheral Module Disable Control 6) | 122 |

| CxTRmnCON (CANx TX/RX Buffer mn Control) 327      | PMD7 (Peripheral Module Disable Control 7) | 123 |

| CxVEC (CANx Interrupt Code)311                    | PMD8 (Peripheral Module Disable Control 8) | 124 |

| DEVID (Device ID)                                 | PORTx (I/O PORTx)                          | 13  |

| DEVREV (Device Revision)354                       | PTCON (PWMx Time Base Control)             |     |

| DMALCA (DMA Last Channel Active Status) 100       | PTCON2 (PWMx Clock Divider Select)         |     |

| DMAPPS (DMA Ping-Pong Status)                     | PTGADJ (PTG Adjust)                        |     |

| DMAPWC (DMA Peripheral Write                      | PTGBTE (PTG Broadcast Trigger Enable)      |     |

| Collision Status)98                               | PTGC0LIM (PTG Counter 0 Limit)             |     |

| DMARQC (DMA Request Collision Status)99           | PTGC1LIM (PTG Counter 1 Limit)             |     |

| DMAXCNT (DMA Channel x Transfer Count)96          | PTGCON (PTG Control)                       |     |

| ,                                                 | PTGCST (PTG Control/Status)                |     |

| DMAxCON (DMA Channel x Control)                   |                                            |     |

| DMAxPAD (DMA Channel x Peripheral Address) 96     | PTGHOLD (PTG Hold)                         |     |

| DMAxREQ (DMA Channel x IRQ Select)                | PTGL0 (PTG Literal 0)                      |     |

| DMAxSTAH (DMA Channel x                           | PTGQPTR (PTG Step Queue Pointer)           |     |

| Start Address A, High)94                          | PTGQUEx (PTG Step Queue x)                 |     |

| DMAxSTAL (DMA Channel x                           | PTGSDLIM (PTG Step Delay Limit)            |     |

| Start Address A, Low)94                           | PTGT0LIM (PTG Timer0 Limit)                |     |

| DMAxSTBH (DMA Channel x                           | PTGT1LIM (PTG Timer1 Limit)                | 220 |

| Start Address B, High)95                          | PTPER (PWMx Primary Master                 |     |

| DMAxSTBL (DMA Channel x                           | Time Base Period)                          |     |

| Start Address B, Low)95                           | PWMCAPx (PWMx Primary Time Base Capture)   |     |

| DSADRH (DMA Most Recent RAM High Address) 97      | PWMCONx (PWMx Control)                     | 198 |

| DSADRL (DMA Most Recent RAM Low Address)97        | PWMKEY (PWMx Protection Lock/Unlock Key)   | 197 |

| DTRx (PWMx Dead-Time)203                          | RCON (Reset Control)                       |     |

| FCLCONx (PWMx Fault Current-Limit Control) 207    | REFOCON (Reference Oscillator Control)     | 113 |

| I2CxCONH (I2Cx Control High)249                   | RPINR0 (Peripheral Pin Select Input 0)     |     |

| I2CxCONL (I2Cx Control Low)247                    | RPINR1 (Peripheral Pin Select Input 1)     | 142 |

|                                                   |                                            |     |

| RPINR11 (Peripheral Pin Select Input 11) | 145    | STCON2 (PWMx Secondary Clock               |     |

|------------------------------------------|--------|--------------------------------------------|-----|

| RPINR12 (Peripheral Pin Select Input 12) | 145    | Divider Select)                            | 195 |

| RPINR13 (Peripheral Pin Select Input 13) | 146    | STPER (PWMx Secondary Master               |     |

| RPINR18 (Peripheral Pin Select Input 18) |        | Time Base Period)                          | 195 |

| RPINR19 (Peripheral Pin Select Input 19) | 147    | STRIGx (PWMx Secondary Trigger             |     |

| RPINR2 (Peripheral Pin Select Input 2)   |        | Compare Value)                             | 208 |

| RPINR20 (Peripheral Pin Select Input 20) |        | T1CON (Timer1 Control)                     | 171 |

| RPINR21 (Peripheral Pin Select Input 21) | 148    | TRGCONx (PWMx Trigger Control)             |     |

| RPINR22 (Peripheral Pin Select Input 22) |        | TRIGx (PWMx Primary Trigger Compare Value) |     |

| RPINR23 (Peripheral Pin Select Input 23) |        | TRISx (PORTx Data Direction Control)       |     |

| RPINR26 (Peripheral Pin Select Input 26) |        | TxCON (Timer2/4 Control)                   |     |

| RPINR29 (Peripheral Pin Select Input 29) |        | TyCON (Timer3/5 Control)                   |     |

| RPINR3 (Peripheral Pin Select Input 3)   |        | UxMODÈ (UARTx Mode)                        |     |

| RPINR30 (Peripheral Pin Select Input 30) |        | UxSTA (UARTx Status and Control)           |     |

| RPINR37 (Peripheral Pin Select Input 37) |        | Resets                                     |     |

| RPINR38 (Peripheral Pin Select Input 38) |        | Brown-out Reset (BOR)                      |     |

| RPINR42 (Peripheral Pin Select Input 42) |        | Configuration Mismatch Reset (CM)          |     |

| RPINR43 (Peripheral Pin Select Input 43) |        | Illegal Condition Reset (IOPUWR)           |     |

| RPINR45 (Peripheral Pin Select Input 45) |        | Illegal Opcode                             |     |

| RPINR46 (Peripheral Pin Select Input 46) |        | Security                                   |     |

| RPINR7 (Peripheral Pin Select Input 7)   |        | Uninitialized W Register                   |     |

| RPINR8 (Peripheral Pin Select Input 8)   |        | Master Clear (MCLR) Pin Reset              |     |

| RPOR0 (Peripheral Pin Select Output 0)   |        | Power-on Reset (POR)                       |     |

| RPOR1 (Peripheral Pin Select Output 1)   |        | RESET Instruction (SWR)                    |     |

| RPOR10 (Peripheral Pin Select Output 10) |        | Resources                                  |     |

| RPOR11 (Peripheral Pin Select Output 11) |        | Trap Conflict Reset (TRAPR)                |     |

| RPOR12 (Peripheral Pin Select Output 12) |        | Watchdog Timer Time-out Reset (WDTO)       |     |

| RPOR13 (Peripheral Pin Select Output 13) |        | Revision History                           |     |

| RPOR14 (Peripheral Pin Select Output 14) |        |                                            |     |

| RPOR15 (Peripheral Pin Select Output 15) |        | S                                          |     |

| RPOR16 (Peripheral Pin Select Output 16) |        | Serial Peripheral Interface (SPI)          | 229 |

| RPOR17 (Peripheral Pin Select Output 17) |        | Serial Peripheral Interface. See SPI.      |     |

| RPOR18 (Peripheral Pin Select Output 18) |        | SFR Blocks                                 |     |

| RPOR19 (Peripheral Pin Select Output 19) | 163    | 000h                                       | 40  |

| RPOR2 (Peripheral Pin Select Output 2)   |        | 100h                                       | 40  |

| RPOR20 (Peripheral Pin Select Output 20) | 164    | 200h                                       | 41  |

| RPOR21 (Peripheral Pin Select Output 21) | 164    | 300h                                       | 41  |

| RPOR22 (Peripheral Pin Select Output 22) | 165    | 400h                                       | 42  |

| RPOR23 (Peripheral Pin Select Output 23) | 165    | 500h                                       | 42  |

| RPOR24 (Peripheral Pin Select Output 24) | 166    | 600h                                       | 43  |

| RPOR25 (Peripheral Pin Select Output 25) | 166    | 700h                                       |     |

| RPOR26 (Peripheral Pin Select Output 26) | 167    | 800h                                       | 45  |

| RPOR3 (Peripheral Pin Select Output 3)   | 155    | 900h                                       |     |

| RPOR4 (Peripheral Pin Select Output 4)   | 156    | A00h                                       | 46  |

| RPOR5 (Peripheral Pin Select Output 5)   | 156    | B00h                                       | 46  |

| RPOR6 (Peripheral Pin Select Output 6)   | 157    | C00h-D00h                                  |     |

| RPOR7 (Peripheral Pin Select Output 7)   | 157    | E00h-F00h                                  | 48  |

| RPOR8 (Peripheral Pin Select Output 8)   | 158    | Software Simulator                         |     |

| RPOR9 (Peripheral Pin Select Output 9)   | 158    | MPLAB X SIM                                |     |

| SDCx (PWMx Secondary Duty Cycle)         | 200    | Special Features of the CPU                | 347 |

| SEVTCMP (PWMx Special Event Compare)     | 193    | Т                                          |     |

| SPHASEx (PWMx Secondary Phase-Shift)     | 202    | •                                          |     |

| SPIxCON1H (SPIx Control 1 High)          | 234    | Thermal Operating Conditions               |     |

| SPIxCON1L (SPIx Control 1 Low)           | 232    | Thermal Packaging Characteristics          |     |

| SPIxCON2L (SPIx Control 2 Low)           | 236    | Third-Party Development Tools              |     |

| SPIxIMSKH (SPIx Interrupt Mask High)     | 241    | Timer1                                     |     |

| SPIxIMSKL (SPIx Interrupt Mask Low)      | 240    | Control Register                           |     |

| SPIxSTATH (SPIx Status High)             | 239    | Mode Settings                              |     |

| SPIxSTATL (SPIx Status Low)              | 237    | Resources                                  |     |

| SR (CPU STATUS)                          | 26, 82 | Timer2/3 and Timer4/5                      |     |

| SSEVTCMP (PWMx Secondary Special Event   |        | Control Registers                          |     |

| Compare)                                 | 196    | Resources                                  | 173 |

| STCON (PWMx Secondary Master             |        |                                            |     |

| Timo Paco Control)                       | 104    |                                            |     |