Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000.00                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 67                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

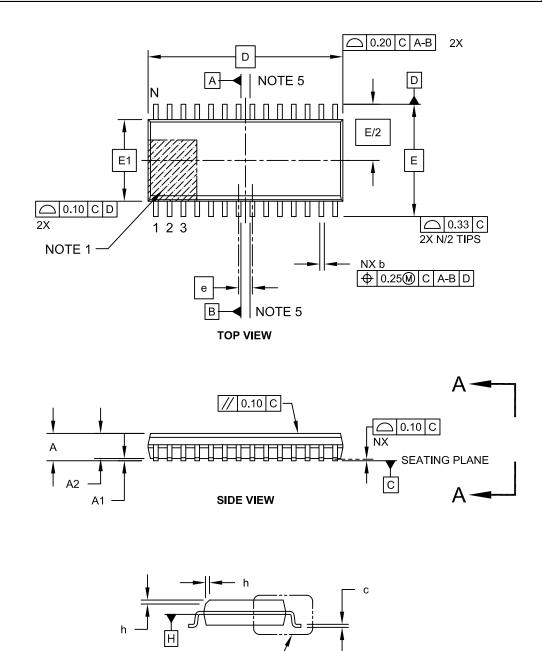

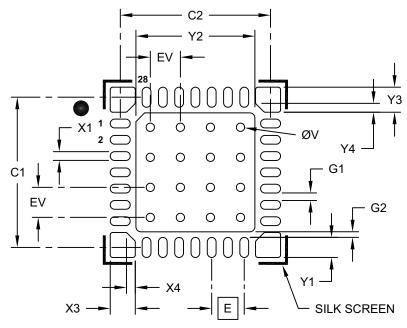

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-TQFP                                                                          |

| Supplier Device Package    | 80-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs808-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| h:+ 7 C | $ \mathbf{p}  \sim 2 \cdot \mathbf{p} \sim C \mathbf{p} $   Interment Driver in Level Contraction hits (1.2) |

|---------|--------------------------------------------------------------------------------------------------------------|

| bit 7-5 | <b>IPL&lt;2:0&gt;:</b> CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                             |

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled                                   |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                                                                 |

|         | 101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)                 |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                                                                 |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                                                                 |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                                                  |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                                                  |

| bit 4   | RA: REPEAT Loop Active bit                                                                                   |

|         | 1 = REPEAT loop is in progress                                                                               |

|         | 0 = REPEAT loop is not in progress                                                                           |

| bit 3   | N: MCU ALU Negative bit                                                                                      |

|         | 1 = Result was negative                                                                                      |

|         | 0 = Result was non-negative (zero or positive)                                                               |

| bit 2   | OV: MCU ALU Overflow bit                                                                                     |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that      |

|         | causes the sign bit to change state.                                                                         |

|         | 1 = Overflow occurred for signed arithmetic (in this arithmetic operation)                                   |

|         | 0 = No overflow occurred                                                                                     |

| bit 1   | Z: MCU ALU Zero bit                                                                                          |

|         | 1 = An operation that affects the Z bit has set it at some time in the past                                  |

|         | 0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)                |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                  |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                         |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                        |

| Note 1: | The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority        |

|         |                                                                                                              |

- Iote 1: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 2: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

#### REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

| U-0          | U-0          | U-0              | U-0             | U-0              | U-0              | U-0             | R/W-0              |  |  |

|--------------|--------------|------------------|-----------------|------------------|------------------|-----------------|--------------------|--|--|

|              | _            | —                | _               | _                | _                | —               | NAE                |  |  |

| bit 15       |              |                  | •               | •                | •                |                 | bit 8              |  |  |

|              |              |                  |                 |                  |                  |                 |                    |  |  |

| U-0          | U-0          | U-0              | R/W-0           | U-0              | U-0              | U-0             | R/W-0              |  |  |

| _            | _            | —                | DOOVR           | —                | _                | —               | APLL               |  |  |

| bit 7        | •            |                  | •               |                  | •                |                 | bit (              |  |  |

|              |              |                  |                 |                  |                  |                 |                    |  |  |

| Legend:      |              |                  |                 |                  |                  |                 |                    |  |  |

| R = Readab   | le bit       | W = Writable     | bit             | U = Unimple      | mented bit, read | as '0'          |                    |  |  |

| -n = Value a | t POR        | '1' = Bit is set | :               | '0' = Bit is cle | eared            | x = Bit is unkr | x = Bit is unknown |  |  |

|              |              |                  |                 |                  |                  |                 |                    |  |  |

| bit 15-9     | Unimpleme    | nted: Read as    | '0'             |                  |                  |                 |                    |  |  |

| bit 8        | NAE: NVM /   | Address Error S  | oft Trap Status | s bit            |                  |                 |                    |  |  |

|              | 1 = NVM ad   | dress error soft | trap has occur  | rred             |                  |                 |                    |  |  |

|              | 0 = NVM ad   | dress error soft | trap has not o  | ccurred          |                  |                 |                    |  |  |

| bit 7-5      | Unimpleme    | nted: Read as    | '0'             |                  |                  |                 |                    |  |  |

| bit 4        | DOOVR: DO    | Stack Overflow   | / Soft Trap Sta | tus bit          |                  |                 |                    |  |  |

|              | 1 = DO stack | overflow soft tr | ap has occurr   | ed               |                  |                 |                    |  |  |

|              | 0 = DO stack | overflow soft tr | ap has not oc   | curred           |                  |                 |                    |  |  |

|              |              |                  |                 |                  |                  |                 |                    |  |  |

- bit 3-1 Unimplemented: Read as '0'

- bit 0 APLL: Auxiliary PLL Loss of Lock Soft Trap Status bit

- 1 = APLL lock soft trap has occurred

- 0 = APLL lock soft trap has not occurred

### REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0                                                                  | U-0 | U-0              | U-0 | U-0                                     | U-0 | U-0 | U-0   |

|----------------------------------------------------------------------|-----|------------------|-----|-----------------------------------------|-----|-----|-------|

| _                                                                    | —   | —                |     | —                                       |     | —   |       |

| bit 15                                                               |     |                  |     |                                         |     |     | bit 8 |

|                                                                      |     |                  |     |                                         |     |     |       |

| U-0                                                                  | U-0 | U-0              | U-0 | U-0                                     | U-0 | U-0 | R/W-0 |

| —                                                                    | —   | —                | —   | —                                       | —   | —   | SGHT  |

| bit 7                                                                |     |                  |     |                                         |     |     | bit 0 |

|                                                                      |     |                  |     |                                         |     |     |       |

| Legend:                                                              |     |                  |     |                                         |     |     |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |                  |     |                                         |     |     |       |

| -n = Value at P                                                      | OR  | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |     | nown  |

bit 15-1 Unimplemented: Read as '0'

SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

bit 0

| U-0          | U-0                                                       | U-0                         | U-0           | U-0               | R/W-0            | U-0              | U-0 |  |  |  |  |

|--------------|-----------------------------------------------------------|-----------------------------|---------------|-------------------|------------------|------------------|-----|--|--|--|--|

| —            | _                                                         |                             | —             |                   | PGA2MD           | _                | _   |  |  |  |  |

| bit 15       | •                                                         |                             |               |                   | •                |                  | bit |  |  |  |  |

|              |                                                           |                             |               |                   |                  |                  |     |  |  |  |  |

| U-0          | U-0                                                       | R/W-0                       | R/W-0         | R/W-0             | R/W-0            | R/W-0            | U-0 |  |  |  |  |

| —            | —                                                         | CLC4MD                      | CLC3MD        | CLC2MD            | CLC1MD           | CCSMD            | —   |  |  |  |  |

| bit 7        |                                                           |                             |               |                   |                  |                  | bit |  |  |  |  |

| Legend:      |                                                           |                             |               |                   |                  |                  |     |  |  |  |  |

| R = Readab   | ole bit                                                   | W = Writable                | oit           | U = Unimpler      | nented bit, read | d as '0'         |     |  |  |  |  |

| -n = Value a | It POR                                                    | '1' = Bit is set            |               | '0' = Bit is clea |                  | x = Bit is unkno | own |  |  |  |  |

|              |                                                           |                             |               |                   |                  |                  |     |  |  |  |  |

| bit 15-11    | Unimplemen                                                | ted: Read as '              | )'            |                   |                  |                  |     |  |  |  |  |

| bit 10       | PGA2MD: PO                                                | ID: PGA2 Module Disable bit |               |                   |                  |                  |     |  |  |  |  |

|              | 1 = PGA2 module is disabled                               |                             |               |                   |                  |                  |     |  |  |  |  |

|              |                                                           | dule is enabled             |               |                   |                  |                  |     |  |  |  |  |

| bit 9-6      | •                                                         | ted: Read as '0             |               |                   |                  |                  |     |  |  |  |  |

| bit 5        |                                                           | C4 Module Dis               |               |                   |                  |                  |     |  |  |  |  |

|              |                                                           | dule is disabled            |               |                   |                  |                  |     |  |  |  |  |

|              | 0 = CLC4 module is enabled                                |                             |               |                   |                  |                  |     |  |  |  |  |

| bit 4        | CLC3MD: CLC3 Module Disable bit                           |                             |               |                   |                  |                  |     |  |  |  |  |

|              | 1 = CLC3 module is disabled<br>0 = CLC3 module is enabled |                             |               |                   |                  |                  |     |  |  |  |  |

| bit 3        |                                                           | C2 Module Dis               |               |                   |                  |                  |     |  |  |  |  |

| bit 0        |                                                           | dule is disabled            |               |                   |                  |                  |     |  |  |  |  |

|              |                                                           | dule is enabled             |               |                   |                  |                  |     |  |  |  |  |

| bit 2        | CLC1MD: CL                                                | C1 Module Dis               | able bit      |                   |                  |                  |     |  |  |  |  |

|              | 1 = CLC1 module is disabled                               |                             |               |                   |                  |                  |     |  |  |  |  |

|              | 0 = CLC1 mo                                               | dule is enabled             |               |                   |                  |                  |     |  |  |  |  |

| bit 1        | CCSMD: Con                                                | stant-Current S             | Source Module | Disable bit       |                  |                  |     |  |  |  |  |

|              |                                                           | current source              |               |                   |                  |                  |     |  |  |  |  |

|              |                                                           | current source              |               | bled              |                  |                  |     |  |  |  |  |

| bit 0        | Unimplemen                                                | ted: Read as '0             | )'            |                   |                  |                  |     |  |  |  |  |

### REGISTER 10-7: PMD8: PERIPHERAL MODULE DISABLE CONTROL REGISTER 8

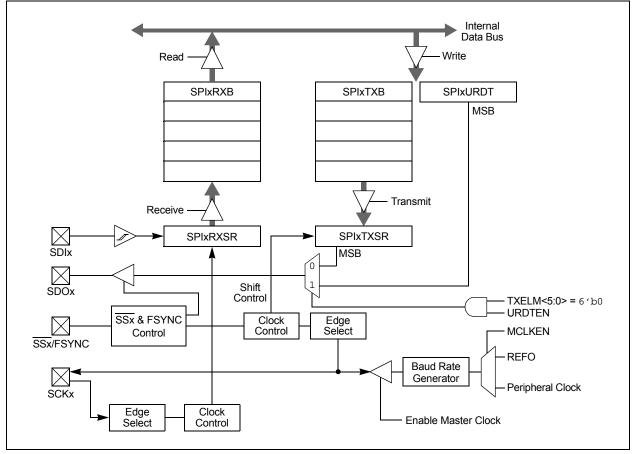

To set up the SPIx module for the Enhanced Buffer Master mode of operation:

- 1. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with MSTEN (SPIxCON1L<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTATL<6>).

- 4. Select Enhanced Buffer mode by setting the ENHBUF bit (SPIxCON1L<0>).

- 5. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

To set up the SPIx module for the Enhanced Buffer Slave mode of operation:

- 1. Clear the SPIxBUFL and SPIxBUFH registers.

- 2. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with the MSTEN bit (SPIxCON1L<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit must be set, thus enabling the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTATL<6>).

- 7. Select Enhanced Buffer mode by setting the ENHBUF bit (SPIxCON1L<0>).

- 8. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

### REGISTER 21-1: CLCxCONL: CLCx CONTROL REGISTER (LOW) (CONTINUED)

- bit 2-0 MODE<2:0>: CLCx Mode bits

- 111 = Single Input Transparent Latch with S and R

- 110 = JK Flip-Flop with R

- 101 = Two-Input D Flip-Flop with R

- 100 = Single Input D Flip-Flop with S and R

- 011 = SR Latch

- 010 = Four-Input AND

- 001 = Four-Input OR-XOR

- 000 = Four-Input AND-OR

### REGISTER 21-2: CLCxCONH: CLCx CONTROL REGISTER (HIGH)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | G4POL | G3POL | G2POL | G1POL |

| bit 7 |     |     |     |       |       |       | bit 0 |

#### Legend:

| Legena.           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                                 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | G4POL: Gate 4 Polarity Control bit                                                                                                         |

|          | <ul><li>1 = Channel 4 logic output is inverted when applied to the logic cell</li><li>0 = Channel 4 logic output is not inverted</li></ul> |

| bit 2    | G3POL: Gate 3 Polarity Control bit                                                                                                         |

|          | <ul><li>1 = Channel 3 logic output is inverted when applied to the logic cell</li><li>0 = Channel 3 logic output is not inverted</li></ul> |

| bit 1    | G2POL: Gate 2 Polarity Control bit                                                                                                         |

|          | <ul><li>1 = Channel 2 logic output is inverted when applied to the logic cell</li><li>0 = Channel 2 logic output is not inverted</li></ul> |

| bit 0    | G1POL: Gate 1 Polarity Control bit                                                                                                         |

|          | <ul><li>1 = Channel 1 logic output is inverted when applied to the logic cell</li><li>0 = Channel 1 logic output is not inverted</li></ul> |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| G4D4T  | G4D4N | G4D3T | G4D3N | G4D2T | G4D2N | G4D1T | G4D1N |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:                                                                                                                                               |          |                                                                |                       |                    |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------|-----------------------|--------------------|--|--|--|

| R = Readable                                                                                                                                          | e bit    | W = Writable bit                                               | U = Unimplemented bit | , read as '0'      |  |  |  |

| -n = Value at                                                                                                                                         | POR      | '1' = Bit is set                                               | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |

| bit 15                                                                                                                                                | G4D4T: ( | Gate 4 Data Source 4 True E                                    | nable bit             |                    |  |  |  |

| <ul> <li>1 = Data Source 4 non-inverted signal is enabled for Gate 4</li> <li>0 = Data Source 4 non-inverted signal is disabled for Gate 4</li> </ul> |          |                                                                |                       |                    |  |  |  |

| bit 14                                                                                                                                                |          | Gate 4 Data Source 4 Negat<br>Source 4 inverted signal is e    |                       |                    |  |  |  |

|                                                                                                                                                       | 0 = Data | Source 4 inverted signal is c                                  | lisabled for Gate 4   |                    |  |  |  |

| bit 13                                                                                                                                                |          | Gate 4 Data Source 3 True E                                    |                       |                    |  |  |  |

|                                                                                                                                                       |          | Source 3 non-inverted signal Source 3 non-inverted signal      |                       |                    |  |  |  |

| bit 12                                                                                                                                                | G4D3N:   | Gate 4 Data Source 3 Negat                                     | ed Enable bit         |                    |  |  |  |

|                                                                                                                                                       |          | Source 3 inverted signal is a Source 3 inverted signal is a    |                       |                    |  |  |  |

| bit 11                                                                                                                                                | G4D2T: ( | G4D2T: Gate 4 Data Source 2 True Enable bit                    |                       |                    |  |  |  |

|                                                                                                                                                       |          | Source 2 non-inverted signal Source 2 non-inverted signal      |                       |                    |  |  |  |

| bit 10                                                                                                                                                | G4D2N:   | Gate 4 Data Source 2 Negat                                     | ed Enable bit         |                    |  |  |  |

|                                                                                                                                                       |          | Source 2 inverted signal is a Source 2 inverted signal is a    |                       |                    |  |  |  |

| bit 9                                                                                                                                                 | G4D1T: ( | Gate 4 Data Source 1 True E                                    | nable bit             |                    |  |  |  |

|                                                                                                                                                       |          | Source 1 non-inverted signal Source 1 non-inverted signal      |                       |                    |  |  |  |

| bit 8                                                                                                                                                 | G4D1N:   | Gate 4 Data Source 1 Negat                                     | ed Enable bit         |                    |  |  |  |

|                                                                                                                                                       |          | Source 1 inverted signal is a Source 1 inverted signal is a    |                       |                    |  |  |  |

| bit 7                                                                                                                                                 | G3D4T: ( | Gate 3 Data Source 4 True E                                    | nable bit             |                    |  |  |  |

|                                                                                                                                                       |          | Source 4 non-inverted signal Source 4 non-inverted signal      |                       |                    |  |  |  |

| bit 6                                                                                                                                                 | G3D4N:   | Gate 3 Data Source 4 Negat                                     | ed Enable bit         |                    |  |  |  |

|                                                                                                                                                       |          | Source 4 inverted signal is e<br>Source 4 inverted signal is o |                       |                    |  |  |  |

| bit 5                                                                                                                                                 | G3D3T: ( | Gate 3 Data Source 3 True E                                    | nable bit             |                    |  |  |  |

|                                                                                                                                                       |          | Source 3 non-inverted signa<br>Source 3 non-inverted signa     |                       |                    |  |  |  |

| bit 4                                                                                                                                                 | G3D3N:   | Gate 3 Data Source 3 Negat                                     | ed Enable bit         |                    |  |  |  |

|                                                                                                                                                       | 1 = Data | Source 3 inverted signal is e                                  | enabled for Gate 3    |                    |  |  |  |

0 = Data Source 3 inverted signal is disabled for Gate 3

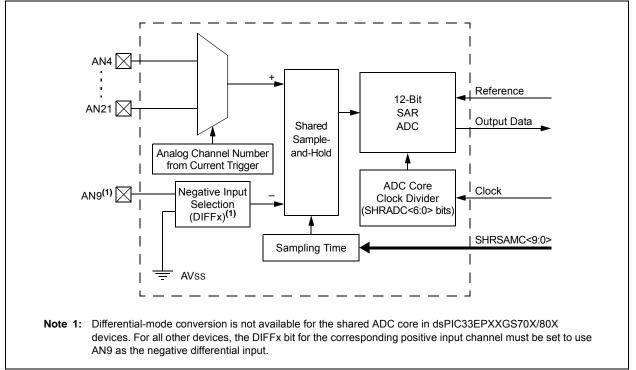

### FIGURE 22-3: SHARED ADC CORE BLOCK DIAGRAM

# REGISTER 22-26: ADTRIGxL: ADC CHANNEL TRIGGER x SELECTION REGISTER LOW (x = 0 to 5) (CONTINUED)

bit 4-0 TRGSRC(4x)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits 11111 = ADTRG31 11110 = PTG Trigger Output 30 11101 = PWM Generator 6 current-limit trigger 11100 = PWM Generator 5 current-limit trigger 11011 = PWM Generator 4 current-limit trigger 11010 = PWM Generator 3 current-limit trigger 11001 = PWM Generator 2 current-limit trigger 11000 = PWM Generator 1 current-limit trigger 10111 = Output Compare 2 trigger 10110 = Output Compare 1 trigger 10101 = CLC2 output 10100 = PWM Generator 6 secondary trigger 10011 = PWM Generator 5 secondary trigger 10010 = PWM Generator 4 secondary trigger 10001 = PWM Generator 3 secondary trigger 10000 = PWM Generator 2 secondary trigger 01111 = PWM Generator 1 secondary trigger 01110 = PWM secondary Special Event Trigger 01101 = Timer2 period match 01100 = Timer1 period match 01011 = CLC1 output 01010 = PWM Generator 6 primary trigger 01001 = PWM Generator 5 primary trigger 01000 = PWM Generator 4 primary trigger 00111 = PWM Generator 3 primary trigger 00110 = PWM Generator 2 primary trigger 00101 = PWM Generator 1 primary trigger 00100 = PWM Special Event Trigger 00011 = Reserved 00010 = Level software trigger 00001 = Common software trigger

00000 = No trigger is enabled

## REGISTER 22-34: ADFLxCON: ADC DIGITAL FILTER x CONTROL REGISTER

| FLEN       MODE1       MODE0       OVRSAM2       OVRSAM1       OVRSAM0       IE       RI         bit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | REGISTER               | 22-34: ADFL<br>(x = 0                                                                                                                                                                                                                                   | _xCON: ADC<br>) or 1)                                                                                                                                                    | DIGITAL FIL                                                                                                                                        | TER x CONT                                                                                                                                       | ROL REGIS                                                                                                   | FER          |           |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------|-----------|--|--|

| FLEN       MODE1       MODE0       OVRSAM2       OVRSAM1       OVRSAM0       IE       RI         bit 15       Image: State                                                                                                                                   | R/W-0                  | R/W-0                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                    | R/W-0                                                                                                                                              | R/W-0                                                                                                                                            | R/W-0                                                                                                       | R/W-0        | R-0, HSC  |  |  |

| U-0       U-0       R/W-0       R/W       R/W       R/W       R/W       R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FLEN                   | MODE1                                                                                                                                                                                                                                                   | MODE0                                                                                                                                                                    | OVRSAM2                                                                                                                                            | OVRSAM1                                                                                                                                          | OVRSAM0                                                                                                     | IE           | RDY       |  |  |

| -       -       FLCHSEL4       FLCHSEL3       FLCHSEL2       FLCHSEL1       FLCHSEL1         bit 7         Legend:       U = Unimplemented bit, read as '0'         R = Readable bit       W = Writable bit       HSC = Hardware Settable/Clearable bit         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       FLEN: Filter Enable bit       -       -       -         0 = Filter is disabled and the RDY bit is cleared       -       -       -       -         bit 14-13       MODE<1:0>: Filter Mode bits       -       -       -       -         1 = Averaging mode       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15                 |                                                                                                                                                                                                                                                         |                                                                                                                                                                          |                                                                                                                                                    |                                                                                                                                                  |                                                                                                             |              | bit 8     |  |  |

| bit 7 Legend: U = Unimplemented bit, read as '0' R = Readable bit W = Writable bit HSC = Hardware Settable/Clearable bit -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 FLEN: Filter Enable bit 1 = Filter is enabled 0 = Filter is disabled and the RDY bit is cleared bit 14-13 MODE<1:0:: Filter Mode bits 11 = Averaging mode 10 = Reserved 00 = Oversampling mode 10 = Reserved 00 = Oversampling mode 11 = 128 (16-bit result in the ADFLxDAT register is in 12.4 format) 110 = 32x (16-bit result in the ADFLxDAT register is in 12.4 format) 101 = 8x (14-bit result in the ADFLxDAT register is in 12.4 format) 101 = 256x (16-bit result in the ADFLxDAT register is in 12.4 format) 011 = 256x (16-bit result in the ADFLxDAT register is in 12.4 format) 010 = 64x (13-bit result in the ADFLxDAT register is in 12.4 format) 011 = 256x (16-bit result in the ADFLxDAT register is in 12.4 format) 011 = 126x 110 = 128. 110 = 128. 110 = 128. 111 = 128 100 = 32. 111 = 128 100 = 32. 111 = 128 100 = 32. 111 = 128 100 = 32. 111 = 128 101 = 4X 100 = 32. 111 = 128 101 = 4X 100 = 32. 111 = 128 101 = 4X 100 = 32. 111 = 128 101 = 4X 100 = 32. 111 = 128 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 100 = 32. 111 = 16X 101 = 4X 101 = 4X 100 = 32. 111 = 16X 101 = 4X | U-0                    | U-0                                                                                                                                                                                                                                                     | U-0                                                                                                                                                                      | R/W-0                                                                                                                                              | R/W-0                                                                                                                                            | R/W-0                                                                                                       | R/W-0        | R/W-0     |  |  |

| Legend:       U = Unimplemented bit, read as '0'         R = Readable bit       W = Writable bit       HSC = Hardware Settable/Clearable bit         .n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       FLEN: Filter Enable bit       1 = Filter is disabled and the RDY bit is cleared       x = Bit is unknown         bit 14.13       MODE<1:0>: Filter Mode bits       1 = Averaging mode       10 = Reserved         00 = Oversampling mode       00 = Oversampling mode       10 = Reserved       11 = 128x (16-bit result in the ADFLxDAT register is in 12.4 format)         110 = 32x (15-bit result in the ADFLxDAT register is in 12.3 format)       101 = 8x (14-bit result in the ADFLxDAT register is in 12.4 format)         101 = 256x (16-bit result in the ADFLxDAT register is in 12.4 format)       010 = 0 = 2x (13-bit result in the ADFLxDAT register is in 12.4 format)         010 = 0 = 32x (15-bit result in the ADFLxDAT register is in 12.4 format)       011 = 256x (16-bit result in the ADFLxDAT register is in 12.4 format)         011 = 128x (13-bit result in the ADFLxDAT register is in 12.4 format)       010 = 64x (13-bit result in the ADFLxDAT register is in 12.1 format)         011 = 128x       101 = 128x       101 = 128x         100 = 128x       101 = 128x       101 = 128x         101 = 128x       101 = 128x       101 = 128x         101 = 128x       101 = 128x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | —                      | —                                                                                                                                                                                                                                                       | —                                                                                                                                                                        | FLCHSEL4                                                                                                                                           | FLCHSEL3                                                                                                                                         | FLCHSEL2                                                                                                    | FLCHSEL1     | FLCHSEL0  |  |  |

| R = Readable bit       W = Writable bit       HSC = Hardware Settable/Clearable bit         .n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       FLEN: Filter Enable bit       1       = Filter is enabled       0         0 = Filter is disabled and the RDY bit is cleared       0 = Filter is disabled and the RDY bit is cleared       0         bit 14-13       MODE-1:0>: Filter Mode bits       1       = Reserved       0         0 = Reserved       00 = Oversampling mode       0       = Coresampling mode         0 = Reserved       00 = Oversampling mode       0       = Norsampling mode         bit 12-10       OVRSAM       = Site result in the ADFLxDAT register is in 12.4 format)       110 = 32x (15-bit result in the ADFLxDAT register is in 12.3 format)         101 = 32x (14-bit result in the ADFLxDAT register is in 12.1 format)       100 = 2x (13-bit result in the ADFLxDAT register is in 12.2 format)       001 = 4x (14-bit result in the ADFLxDAT register is in 12.2 format)         001 = 4x (14-bit result in the ADFLxDAT register is in 12.2 format)       001 = 4x (14-bit result in the ADFLxDAT register is in 12.1 format)         001 = 16x (14-bit result in the ADFLxDAT register is in 12.1 format)       111 = 256x         111 = 256x       111 = 256x       111 = 256x         111 = 256x       111 = 256x       111 = 256x       111 = 256                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 7                  |                                                                                                                                                                                                                                                         |                                                                                                                                                                          |                                                                                                                                                    |                                                                                                                                                  |                                                                                                             |              | bit (     |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       FLEN: Filter Enable bit       1 = Filter is enabled       0 = Filter is disabled and the RDY bit is cleared         bit 14-13       MODE<1:0>: Filter Mode bits       1 = Averaging mode       0 = Reserved         01 = Reserved       00 = Oversampling mode       0 = Reserved       0 = Oversampling mode         bit 12-10       OVRSAM       2:0>: Filter Averaging/Oversampling Ratio bits       If MODE         I11 = 128x (16-bit result in the ADFLxDAT register is in 12.4 format)       10 = 32x (15-bit result in the ADFLxDAT register is in 12.3 format)         100 = 2x (15-bit result in the ADFLxDAT register is in 12.4 format)       100 = 2x (14-bit result in the ADFLxDAT register is in 12.4 format)         101 = 256x (16-bit result in the ADFLxDAT register is in 12.4 format)       000 = 4x (13-bit result in the ADFLxDAT register is in 12.1 format)         010 = 64x (15-bit result in the ADFLxDAT register is in 12.1 format)       000 = 4x (13-bit result in the ADFLxDAT register is in 12.1 format)         011 = 128x       10 = 128x       10 = 64x         100 = 32x       11 = 16x       10 = 8x         010 = 42x       10 = 64x       10 = 2x         101 = 16x       10 = 8x       10 = 8x         010 = 8x       10 = 16x       10 = 16x         010 = 8x       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Legend:                |                                                                                                                                                                                                                                                         | U = Unimpler                                                                                                                                                             | mented bit, read                                                                                                                                   | as '0'                                                                                                                                           |                                                                                                             |              |           |  |  |

| bit 15       FLEN: Filter Enabled         0 = Filter is enabled         0 = Filter is disabled and the RDY bit is cleared         bit 14-13         MODE<1:0>: Filter Mode bits         11 = Averaging mode         10 = Reserved         01 = Reserved         00 = Oversampling mode         bit 12-10       OVRSAM<2:0>: Filter Averaging/Oversampling Ratio bits         If MODE<1:0> = 00;         111 = 128x (16-bit result in the ADFLxDAT register is in 12.4 format)         100 = 32x (15-bit result in the ADFLxDAT register is in 12.4 format)         101 = 8x (14-bit result in the ADFLxDAT register is in 12.4 format)         101 = 2x (13-bit result in the ADFLxDAT register is in 12.4 format)         101 = 2x (14-bit result in the ADFLxDAT register is in 12.4 format)         101 = 25x (16-bit result in the ADFLxDAT register is in 12.4 format)         010 = 64x (15-bit result in the ADFLxDAT register is in 12.1 format)         001 = 64x (15-bit result in the ADFLxDAT register is in 12.1 format)         000 = 4x (13-bit result in the ADFLxDAT register is in 12.1 format)         000 = 4x (13-bit result in the ADFLxDAT register is in 12.1 format)         011 = 128x         101 = 128x         101 = 64x         100 = 4x         001 = 4x         000 = 2x         bit 9       IE: Filte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R = Readab             | le bit                                                                                                                                                                                                                                                  | W = Writable                                                                                                                                                             | bit                                                                                                                                                | HSC = Hardw                                                                                                                                      | /are Settable/C                                                                                             | learable bit |           |  |  |

| <ul> <li>i = Filter is enabled         <ul> <li>i = Filter is disabled and the RDY bit is cleared</li> <li>bit 14-13</li> <li>MODE</li> <li>i = Averaging mode                  10 = Reserved                  01 = Reserved                  00 = Oversampling mode</li> <li>bit 12-10</li> <li>OVRSAM</li> <li>i = Averaging mode</li> <li>i = Reserved                  00 = Oversampling mode</li> <li>bit 12-10</li> <li>OVRSAM</li> <li>i = Reserved</li> <li>i = Reserved</li> <li>i = 128x (16-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 32x (15-bit result in the ADFLxDAT register is in 12.3 format)</li> <li>i = 8x (14-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 8x (14-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 256x (16-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 26x (16-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 64x (14-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 26x (16-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 128x in the ADFLxDAT register is in 12.4 format)</li> <li>i = 128x in the ADFLxDAT register is in 12.1 format)</li> <li>i = 128x in the ADFLxDAT register is in 12.1 format)</li> <li>i = 128x in the ADFLxDAT register is in 12.1 format)</li> <li>i = 10 = 11 (12-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>i = 26x in the ADFLxDAT register is in 12.4 format)</li> <li>i = 28x in the ADFLxDAT register is in 12.4 format)</li> <li>i = 28x in the ADFLxDAT register is in 12.4 format)</li> <li>i = 20mon ADC Interrupt Will be generated when the filter result will be ready in = 8x in the ADFLxDA</li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                             | -n = Value a           | = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown                                                                                                                                                                                 |                                                                                                                                                                          |                                                                                                                                                    |                                                                                                                                                  |                                                                                                             |              |           |  |  |

| bit 14-13 MODE<1:0:: Filter Mode bits<br>11 = Averaging mode<br>10 = Reserved<br>01 = Reserved<br>00 = Oversampling mode<br>bit 12-10 OVRSAM<2:0:: Filter Averaging/Oversampling Ratio bits<br><u>If MODE&lt;1:0&gt; = 00</u> :<br>111 = 128x (16-bit result in the ADFLxDAT register is in 12.4 format)<br>110 = 32x (15-bit result in the ADFLxDAT register is in 12.2 format)<br>101 = 8x (14-bit result in the ADFLxDAT register is in 12.2 format)<br>102 = 2x (13-bit result in the ADFLxDAT register is in 12.4 format)<br>103 = 64x (15-bit result in the ADFLxDAT register is in 12.4 format)<br>104 = 45x (16-bit result in the ADFLxDAT register is in 12.4 format)<br>105 = 64x (15-bit result in the ADFLxDAT register is in 12.2 format)<br>106 = 4x (13-bit result in the ADFLxDAT register is in 12.2 format)<br>107 = 16x (14-bit result in the ADFLxDAT register is in 12.1 format)<br>111 = 256x<br>111 = 256x<br>110 = 128x<br>101 = 64x<br>100 = 32x<br>011 = 16x<br>000 = 2x<br>bit 9 IE: Filter Common ADC Interrupt Enable bit<br>1 = Common ADC interrupt Will be generated when the filter result will be ready<br>0 = Common ADC interrupt will be generated for the filter<br>bit 8 RDY: Oversampling Filter Data Ready Flag bit<br>This bit is cleared by hardware when the result is read from the ADFLxDAT register.<br>1 = Data in the ADFLxDAT register is read from the ADFLxDAT register.<br>1 = Data in the ADFLxDAT register is read from the ADFLxDAT register.<br>1 = Data in the ADFLxDAT register is read from the ADFLxDAT register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15                 | 1 = Filter is e                                                                                                                                                                                                                                         | nabled                                                                                                                                                                   |                                                                                                                                                    |                                                                                                                                                  |                                                                                                             |              |           |  |  |

| <ul> <li>11 = Averaging mode</li> <li>10 = Reserved</li> <li>01 = Reserved</li> <li>00 = Oversampling mode</li> <li>bit 12-10</li> <li>OVRSAM&lt;2:0&gt;: Filter Averaging/Oversampling Ratio bits</li> <li><u>If MODE&lt;1:0&gt; = 00:</u></li> <li>111 = 128x (16-bit result in the ADFLxDAT register is in 12.4 format)</li> <li>101 = 32x (15-bit result in the ADFLxDAT register is in 12.3 format)</li> <li>101 = 8x (14-bit result in the ADFLxDAT register is in 12.1 format)</li> <li>101 = 256x (16-bit result in the ADFLxDAT register is in 12.1 format)</li> <li>011 = 256x (16-bit result in the ADFLxDAT register is in 12.1 format)</li> <li>010 = 64x (15-bit result in the ADFLxDAT register is in 12.3 format)</li> <li>001 = 16x (14-bit result in the ADFLxDAT register is in 12.3 format)</li> <li>000 = 4x (13-bit result in the ADFLxDAT register is in 12.3 format)</li> <li>001 = 16x (14-bit result in the ADFLxDAT register is in 12.1 format)</li> <li>111 = 256x</li> <li>110 = 128x</li> <li>100 = 32x</li> <li>111 = 26ax</li> <li>100 = 32x</li> <li>111 = 26ax</li> <li>100 = 32x</li> <li>111 = 18x</li> <li>100 = 32x</li> <li>111 = 16x</li> <li>110 = 128x</li> <li>111 = 100 = 100000000000000000000000000</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                        | 0 = Filter is d                                                                                                                                                                                                                                         | isabled and the                                                                                                                                                          | e RDY bit is clea                                                                                                                                  | ared                                                                                                                                             |                                                                                                             |              |           |  |  |

| If MODE<1:0> = 00:         111 = 128x (16-bit result in the ADFLxDAT register is in 12.4 format)         100 = 32x (15-bit result in the ADFLxDAT register is in 12.3 format)         101 = 8x (14-bit result in the ADFLxDAT register is in 12.2 format)         100 = 2x (13-bit result in the ADFLxDAT register is in 12.4 format)         011 = 256x (16-bit result in the ADFLxDAT register is in 12.4 format)         011 = 256x (16-bit result in the ADFLxDAT register is in 12.3 format)         001 = 64x (15-bit result in the ADFLxDAT register is in 12.3 format)         001 = 64x (15-bit result in the ADFLxDAT register is in 12.3 format)         001 = 16x (14-bit result in the ADFLxDAT register is in 12.3 format)         000 = 4x (13-bit result in the ADFLxDAT register is in 12.1 format)         If MODE         000 = 4x (13-bit result in the ADFLxDAT register is in 12.1 format)         If MODE         110 = 128x         110 = 128x         111 = 256ax         111 = 16x         100 = 32x         011 = 16x         010 = 8x         001 = 4x         000 = 2x         bit 9         IE: Filter Common ADC Interrupt Enable bit         1 = Common ADC interrupt will be generated when the filter result will be ready         00 = 2x         bit 8       RDY: Oversampling Filter Data Ready Flag bit     <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 1 <del>4</del> -10 | 11 = Averagi<br>10 = Reserve<br>01 = Reserve                                                                                                                                                                                                            | ng mode<br>ed<br>ed                                                                                                                                                      |                                                                                                                                                    |                                                                                                                                                  |                                                                                                             |              |           |  |  |

| 1 = Common ADC interrupt will be generated when the filter result will be ready         0 = Common ADC interrupt will not be generated for the filter         bit 8       RDY: Oversampling Filter Data Ready Flag bit         This bit is cleared by hardware when the result is read from the ADFLxDAT register.         1 = Data in the ADFLxDAT register is ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 12-10              | If MODE<1:0<br>111 = 128x (<br>110 = 32x (1<br>101 = 8x (14<br>100 = 2x (13<br>011 = 256x (<br>010 = 64x (13<br>001 = 16x (14<br>000 = 4x (13<br>If MODE<1:0<br>111 = 256x<br>110 = 128x<br>101 = 64x<br>100 = 32x<br>011 = 16x<br>010 = 8x<br>001 = 4x | $\geq$ = 00:<br>16-bit result in<br>5-bit result in the<br>-bit result in the<br>-bit result in the<br>16-bit result in the<br>5-bit result in the<br>-bit result in the | the ADFLxDAT<br>the ADFLxDAT re-<br>e ADFLxDAT re-<br>e ADFLxDAT re-<br>the ADFLxDAT re-<br>the ADFLxDAT re-<br>the ADFLxDAT re-<br>e ADFLxDAT re- | register is in 1<br>egister is in 12.2<br>gister is in 12.1<br>register is in 12.1<br>register is in 1<br>egister is in 12<br>egister is in 12.1 | 2.4 format)<br>.3 format)<br>2 format)<br>1 format)<br>2.4 format)<br>.3 format)<br>.2 format)<br>1 format) | <u>es):</u>  |           |  |  |

| bit 8 <b>RDY:</b> Oversampling Filter Data Ready Flag bitThis bit is cleared by hardware when the result is read from the ADFLxDAT register.1 = Data in the ADFLxDAT register is ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 9                  | 1 = Common                                                                                                                                                                                                                                              | 1 = Common ADC interrupt will be generated when the filter result will be ready                                                                                          |                                                                                                                                                    |                                                                                                                                                  |                                                                                                             |              |           |  |  |