Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Dectano                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 67                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 80-TQFP                                                                           |

| Supplier Device Package    | 80-TQFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gs808t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

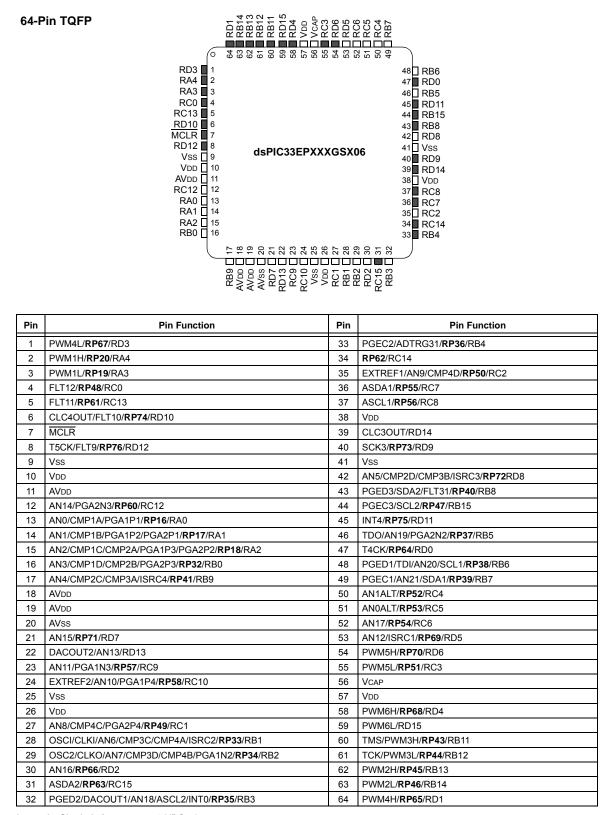

### **Pin Diagrams (Continued)**

Legend: Shaded pins are up to 5 VDC tolerant.

RPn represents remappable peripheral functions. See Table 11-12 and Table 11-13 for the complete list of remappable sources.

| Pin Name <sup>(1)</sup>    | Pin<br>Type | Buffer<br>Type | PPS                | Description                                               |

|----------------------------|-------------|----------------|--------------------|-----------------------------------------------------------|

| U2CTS                      | I           | ST             | Yes                | UART2 Clear-to-Send.                                      |

| U2RTS                      | 0           | —              | Yes                | UART2 Ready-to-Send.                                      |

| U2RX                       |             | ST             | Yes                | UART2 receive.                                            |

| U2TX                       | 0           |                | Yes                | UART2 transmit.                                           |

| BCLK2                      | 0           | ST             | Yes                | UART2 IrDA baud clock output.                             |

| SCK1                       | I/O         | ST             | Yes                | Synchronous serial clock input/output for SPI1.           |

| SDI1                       |             | ST             | Yes                | SPI1 data in.                                             |

| SDO1                       | 0           |                | Yes                | SPI1 data out.                                            |

| SS1                        | I/O         | ST             | Yes                | SPI1 slave synchronization or frame pulse I/O.            |

| SCK2                       | I/O         | ST             | Yes                | Synchronous serial clock input/output for SPI2.           |

| SDI2                       | I           | ST             | Yes                | SPI2 data in.                                             |

| SDO2                       | 0           | —              | Yes                | SPI2 data out.                                            |

| SS2                        | I/O         | ST             | Yes                | SPI2 slave synchronization or frame pulse I/O.            |

| SCK3                       | I/O         | ST             | Yes <sup>(3)</sup> | Synchronous serial clock input/output for SPI3.           |

| SDI3                       | 1           | ST             | Yes                | SPI3 data in.                                             |

| SDO3                       | 0           | —              | Yes                | SPI3 data out.                                            |

| SS3                        | I/O         | ST             | Yes                | SPI3 slave synchronization or frame pulse I/O.            |

| SCL1                       | I/O         | ST             | No                 | Synchronous serial clock input/output for I2C1.           |

| SDA1                       | I/O         | ST             | No                 | Synchronous serial data input/output for I2C1.            |

| ASCL1                      | I/O         | ST             | No                 | Alternate synchronous serial clock input/output for I2C1. |

| ASDA1                      | I/O         | ST             | No                 | Alternate synchronous serial data input/output for I2C1.  |

| SCL2                       | I/O         | ST             | No                 | Synchronous serial clock input/output for I2C2.           |

| SDA2                       | I/O         | ST             | No                 | Synchronous serial data input/output for I2C2.            |

| ASCL2                      | I/O         | ST             | No                 | Alternate synchronous serial clock input/output for I2C2. |

| ASDA2                      | I/O         | ST             | No                 | Alternate synchronous serial data input/output for I2C2.  |

| TMS                        | I           | ST             | No                 | JTAG Test mode select pin.                                |

| ТСК                        | I           | ST             | No                 | JTAG test clock input pin.                                |

| TDI                        | 1           | ST             | No                 | JTAG test data input pin.                                 |

| TDO                        | 0           | —              | No                 | JTAG test data output pin.                                |

| FLT1-FLT8                  | 1           | ST             | Yes                | PWM Fault Inputs 1 through 8.                             |

| FLT9-FLT12                 | I           | ST             | No                 | PWM Fault Inputs 9 through 12.                            |

| PWM1L-PWM3L                | 0           | _              | No                 | PWM Low Outputs 1 through 3.                              |

| PWM1H-PWM3H                | 0           | —              | No                 | PWM High Outputs 1 through 3.                             |

| PWM4L-PWM8L <sup>(2)</sup> | 0           | —              | Yes                | PWM Low Outputs 4 through 8.                              |

| PWM4H-PWM8H <sup>(2)</sup> | 0           | —              | Yes                | PWM High Outputs 4 through 8.                             |

| SYNCI1, SYNCI2             | I.          | ST             | Yes                | PWM Synchronization Inputs 1 and 2.                       |

| SYNCO1, SYNCO2             | 0           |                | Yes                | PWM Synchronization Outputs 1 and 2.                      |

| Legend: CMOS = C           |             |                |                    |                                                           |

| ST = Schm                  | itt Trigg   | jer input      | with CN            | IOS levels O = Output I = Input                           |

#### TABLE 1-1. PINOUT I/O DESCRIPTIONS (CONTINUED)

PPS = Peripheral Pin Select TTL = TTL input buffer 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

2: PWM4H/L through PWM8H/L are fixed on dsPIC33EPXXXGS708/808 devices. PWM4H/L through PWM6H/L are fixed on dsPIC33EPXXXGS706/806 devices.

3: The SCK3 pin is fixed on dsPIC33EPXXXGS706/806 and dsPIC33EPXXXGS708/808 devices.

4: PPS is available on dsPIC33EPXXXGS702 devices only.

| R/W-0          | R/W-0                                     | U-0                                                                                                                                                | U-0            | R/W-0                 | U-0               | R/W-0             | R/W-0        |  |

|----------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------|-------------------|-------------------|--------------|--|

| TRAPF          | R IOPUWR                                  | _                                                                                                                                                  |                | VREGSF                |                   | CM                | VREGS        |  |

| bit 15         | •                                         |                                                                                                                                                    |                |                       |                   |                   | bit          |  |

| <b>D</b> #44.0 | <b>D M U O</b>                            | Date                                                                                                                                               | <b>D</b> 444 0 | <b>D</b> 444 A        | <b>D</b> 444 0    | <b>D</b> 444 4    |              |  |

| R/W-0          |                                           | R/W-0                                                                                                                                              | R/W-0          | R/W-0                 | R/W-0             | R/W-1             | R/W-1        |  |

| EXTR           | SWR                                       | SWDTEN <sup>(2)</sup>                                                                                                                              | WDTO           | SLEEP                 | IDLE              | BOR               | POR          |  |

| bit 7          |                                           |                                                                                                                                                    |                |                       |                   |                   | bit          |  |

| Legend:        |                                           |                                                                                                                                                    |                |                       |                   |                   |              |  |

| R = Reada      | able bit                                  | W = Writable b                                                                                                                                     | bit            | U = Unimpler          | mented bit, read  | d as '0'          |              |  |

| -n = Value     | at POR                                    | '1' = Bit is set                                                                                                                                   |                | '0' = Bit is cle      | ared              | x = Bit is unkı   | nown         |  |

|                |                                           |                                                                                                                                                    |                |                       |                   |                   |              |  |

| bit 15         | TRAPR: Trap                               | Reset Flag bit                                                                                                                                     |                |                       |                   |                   |              |  |

|                |                                           | onflict Reset ha                                                                                                                                   |                |                       |                   |                   |              |  |

|                |                                           | onflict Reset ha                                                                                                                                   |                |                       |                   |                   |              |  |

| bit 14         |                                           | gal Opcode or                                                                                                                                      |                | -                     |                   | -                 |              |  |

|                |                                           | <ul> <li>An illegal opcode detection, an illegal address mode or Uninitialized W register used as an<br/>Address Pointer caused a Reset</li> </ul> |                |                       |                   |                   |              |  |

|                |                                           | l opcode or Uni                                                                                                                                    |                | egister Reset h       | as not occurre    | d                 |              |  |

| bit 13-12      | -                                         | nted: Read as '0                                                                                                                                   |                | - 3                   |                   | -                 |              |  |

| bit 11         | •                                         | ash Voltage Reg                                                                                                                                    |                | by During Slee        | p bit             |                   |              |  |

|                |                                           | Itage regulator i                                                                                                                                  |                |                       |                   |                   |              |  |

|                |                                           | 0 = Flash voltage regulator goes into Standby mode during Sleep                                                                                    |                |                       |                   |                   |              |  |

| bit 10         | Unimplemer                                | nted: Read as 'o                                                                                                                                   | 2              |                       |                   |                   |              |  |

| bit 9          | CM: Configu                               | ration Mismatch                                                                                                                                    | Flag bit       |                       |                   |                   |              |  |

|                | Ų                                         | uration Mismatc<br>uration Mismatc                                                                                                                 |                |                       |                   |                   |              |  |

| bit 8          | VREGS: Volt                               | age Regulator S                                                                                                                                    | Standby Durir  | ng Sleep bit          |                   |                   |              |  |

|                | •                                         | regulator is activ                                                                                                                                 | •              | •                     |                   |                   |              |  |

|                | -                                         | regulator goes in                                                                                                                                  | -              | mode during Sl        | еер               |                   |              |  |

| bit 7          |                                           | nal Reset (MCLI                                                                                                                                    | ,              |                       |                   |                   |              |  |

|                |                                           | Clear (pin) Res<br>Clear (pin) Res                                                                                                                 |                |                       |                   |                   |              |  |

| bit 6          |                                           | are RESET (Instr                                                                                                                                   |                |                       |                   |                   |              |  |

|                |                                           | instruction has                                                                                                                                    |                |                       |                   |                   |              |  |

|                |                                           | instruction has                                                                                                                                    |                |                       |                   |                   |              |  |

| bit 5          | SWDTEN: Se                                | oftware Enable/I                                                                                                                                   | Disable of W   | DT bit <sup>(2)</sup> |                   |                   |              |  |

|                | 1 = WDT is e                              |                                                                                                                                                    |                |                       |                   |                   |              |  |

|                | 0 = WDT is d                              |                                                                                                                                                    |                |                       |                   |                   |              |  |

| bit 4          |                                           | hdog Timer Tim                                                                                                                                     | •              | IT                    |                   |                   |              |  |

|                |                                           | e-out has occurr<br>e-out has not oc                                                                                                               |                |                       |                   |                   |              |  |

| Note 1:        | All of the Reset sta<br>cause a device Re |                                                                                                                                                    | set or cleare  | d in software. S      | Setting one of th | nese bits in soft | ware does no |  |

| 2:             | If the WDTEN<1:0<br>of the SWDTEN b       | se a device Reset.<br>e WDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardle<br>the SWDTEN bit potting       |                |                       |                   |                   |              |  |

### REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

© 2016-2017 Microchip Technology Inc.

### 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70000600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGS70X/80X family devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior, contains the Global Interrupt Enable bit (GIE) and the Alternate Interrupt Vector Table Enable bit (AIVTEN).

INTCON3 contains the status flags for the Auxiliary PLL and DO stack overflow status trap sources.

The INTCON4 register contains the Software Generated Hard Trap Status bit (SGHT).

### 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

### 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of seven priority levels.

### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number of Pending Interrupt bits (VECNUM<7:0>) and New CPU Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP<2:0> bits in the first position of IPC0 (IPC0<2:0>).

### 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers, refer to "dsPIC33E Enhanced CPU" (DS70005158) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

| R/W-1                          | R/W-0                                                                                      | R/W-0                                                                                   | U-0         | U-0             | U-0               | U-0             | R/W-0  |  |  |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------|-----------------|-------------------|-----------------|--------|--|--|--|--|

| GIE                            | DISI                                                                                       | SWTRAP                                                                                  | _           | _               | _                 |                 | AIVTEN |  |  |  |  |

| bit 15                         |                                                                                            |                                                                                         |             |                 | 4                 |                 | bit 8  |  |  |  |  |

|                                |                                                                                            |                                                                                         |             |                 |                   |                 |        |  |  |  |  |

| U-0                            | U-0                                                                                        | U-0                                                                                     | R/W-0       | U-0             | R/W-0             | R/W-0           | R/W-0  |  |  |  |  |

| _                              |                                                                                            |                                                                                         | INT4EP      | —               | INT2EP            | INT1EP          | INT0EP |  |  |  |  |

| bit 7                          |                                                                                            |                                                                                         |             |                 |                   |                 | bit C  |  |  |  |  |

|                                |                                                                                            |                                                                                         |             |                 |                   |                 |        |  |  |  |  |

| Legend:                        |                                                                                            |                                                                                         |             |                 |                   | ( <b>a</b> )    |        |  |  |  |  |

| R = Readable                   |                                                                                            | W = Writable                                                                            |             | -               | emented bit, read |                 |        |  |  |  |  |

| -n = Value at                  | POR                                                                                        | '1' = Bit is set                                                                        |             | '0' = Bit is cl | eared             | x = Bit is unkr | nown   |  |  |  |  |

| bit 15                         | CIE: Clobal                                                                                | Interrupt Enable                                                                        | hit         |                 |                   |                 |        |  |  |  |  |

| DIL 15                         |                                                                                            | Interrupt Enable<br>s and associate                                                     |             | nabled          |                   |                 |        |  |  |  |  |

|                                |                                                                                            | s are disabled,                                                                         |             |                 |                   |                 |        |  |  |  |  |

| bit 14                         | DISI: DISI                                                                                 | nstruction Statu                                                                        | s bit       |                 |                   |                 |        |  |  |  |  |

|                                | 1 = DISI ins                                                                               | struction is activ                                                                      | е           |                 |                   |                 |        |  |  |  |  |

|                                |                                                                                            | struction is not a                                                                      |             |                 |                   |                 |        |  |  |  |  |

| bit 13                         |                                                                                            | Software Trap St                                                                        |             |                 |                   |                 |        |  |  |  |  |

|                                |                                                                                            | e trap is enabled<br>e trap is disabled                                                 |             |                 |                   |                 |        |  |  |  |  |

| bit 12-9                       |                                                                                            | nted: Read as '                                                                         |             |                 |                   |                 |        |  |  |  |  |

| bit 8                          | -                                                                                          | ernate Interrupt                                                                        |             | Enable          |                   |                 |        |  |  |  |  |

|                                |                                                                                            | ernate Interrupt                                                                        |             |                 |                   |                 |        |  |  |  |  |

|                                |                                                                                            | andard Interrupt                                                                        |             |                 |                   |                 |        |  |  |  |  |

| bit 7-5                        | Unimpleme                                                                                  | nted: Read as '                                                                         | 0'          |                 |                   |                 |        |  |  |  |  |

| bit 4                          | INT4EP: Ext                                                                                | ternal Interrupt 4                                                                      | Edge Detect | Polarity Selec  | ct bit            |                 |        |  |  |  |  |

|                                | <ul> <li>1 = Interrupt on negative edge</li> <li>0 = Interrupt on positive edge</li> </ul> |                                                                                         |             |                 |                   |                 |        |  |  |  |  |

| h:+ 0                          | -                                                                                          |                                                                                         |             |                 |                   |                 |        |  |  |  |  |

| bit 3                          | -                                                                                          | nted: Read as '                                                                         |             | Delarity Color  | at bit            |                 |        |  |  |  |  |

| bit 2                          | INT2EP: External Interrupt 2 Edge Detect Polarity Select bit                               |                                                                                         |             |                 |                   |                 |        |  |  |  |  |

|                                |                                                                                            | <ul><li>1 = Interrupt on negative edge</li><li>0 = Interrupt on positive edge</li></ul> |             |                 |                   |                 |        |  |  |  |  |

| bit 1                          | <b>INT1EP:</b> External Interrupt 1 Edge Detect Polarity Select bit                        |                                                                                         |             |                 |                   |                 |        |  |  |  |  |

| 1 = Interrupt on negative edge |                                                                                            |                                                                                         |             |                 |                   |                 |        |  |  |  |  |

|                                | -                                                                                          | on positive edg                                                                         |             |                 |                   |                 |        |  |  |  |  |

| bit 0                          |                                                                                            | ternal Interrupt (                                                                      | -           | Polarity Selec  | ct bit            |                 |        |  |  |  |  |

|                                |                                                                                            | on negative ed                                                                          |             |                 |                   |                 |        |  |  |  |  |

|                                | 0 = interrupt                                                                              | on positive edg                                                                         | e           |                 |                   |                 |        |  |  |  |  |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

### 9.1 CPU Clocking System

The dsPIC33EPXXXGS70X/80X family of devices provides six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase-Locked Loop (FRCPLL)

- FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL (XTPLL, HSPLL, ECPLL)

- Low-Power RC (LPRC) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

### EQUATION 9-1: DEVICE OPERATING FREQUENCY

#### FCY = FOSC/2

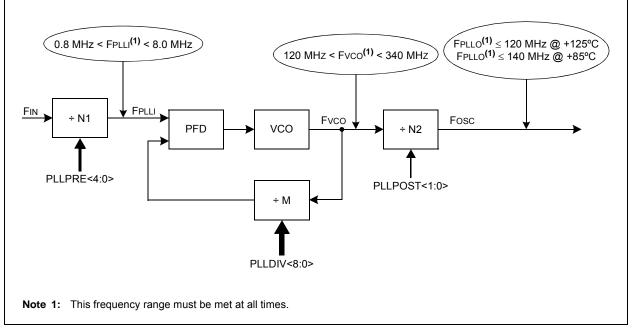

Figure 9-2 is a block diagram of the PLL module. Equation 9-2 provides the relationship between Input Frequency (FIN) and Output Frequency (FPLLO). Equation 9-3 provides the relationship between Input Frequency (FIN) and VCO Frequency (FVCO).

### EQUATION 9-2: FPLLO CALCULATION

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{PLLDIV < 8:0 > + 2}{(PLLPRE < 4:0 > + 2) \times 2(PLLPOST < 1:0 > + 1)}\right)$$

Where:

N1 = PLLPRE < 4:0 > +2

N2 = 2 x (PLLPOST < 1:0 > +1)

M = PLLDIV < 8:0 > +2

### EQUATION 9-3: Fvco CALCULATION

$$F_{VCO} = F_{IN} \times \left(\frac{M}{N1}\right) = F_{IN} \times \left(\frac{PLLDIV < 8:0 > +2}{(PLLPRE < 4:0 > +2)}\right)$$

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input, provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRISx setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRISx settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned.

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select x (ANSELx) registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select x registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

### 11.8 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 11.8.1 KEY RESOURCES

- "I/O Ports" (DS70000598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

### 11.9 Peripheral Pin Select Registers

#### REGISTER 11-9: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|--------|--------|--------|--------|--------|--------|--------|

| INT1R7  | INT1R6 | INT1R5 | INT1R4 | INT1R3 | INT1R2 | INT1R1 | INT1R0 |

| bit 15  |        | •      |        |        |        |        | bit 8  |

|         |        |        |        |        |        |        |        |

| U-0     | U-0    | U-0    | U-0    | U-0    | U-0    | U-0    | U-0    |

| _       | _      | —      | —      | —      | —      | —      | _      |

| bit 7   | ·      | •      | •      | •      |        |        | bit 0  |

|         |        |        |        |        |        |        |        |

| Legend: |        |        |        |        |        |        |        |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8INT1R<7:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits<br/>See Table 11-11 which contains a list of remappable inputs for the index value.bit 7-0Unimplemented: Read as '0'

#### REGISTER 11-10: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| INT2R7 | INT2R6 | INT2R5 | INT2R4 | INT2R3 | INT2R2 | INT2R1 | INT2R0 |

| bit 7  |        |        |        | •      |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **INT2R<7:0>:** Assign External Interrupt 2 (INT2) to the Corresponding RPn Pin bits See Table 11-11 which contains a list of remappable inputs for the index value.

| -n = Value at POR (1' = Bi |       | '1' = Bit is set | '0' = Bit is cleared |              | ared            | x = Bit is unknown |       |

|----------------------------|-------|------------------|----------------------|--------------|-----------------|--------------------|-------|

| R = Readable bit W =       |       | W = Writable     | bit                  | U = Unimplen | nented bit, rea | d as '0'           |       |

| Legend:                    |       |                  |                      |              |                 |                    |       |

|                            |       |                  |                      |              |                 |                    |       |

| bit 7                      | •     | 1                | •                    | •            |                 |                    | bit ( |

| IC1R7                      | IC1R6 | IC1R5            | IC1R4                | IC1R3        | IC1R2           | IC1R1              | IC1R0 |

| R/W-0                      | R/W-0 | R/W-0            | R/W-0                | R/W-0        | R/W-0           | R/W-0              | R/W-0 |

| bit 15                     |       |                  |                      |              |                 |                    | bit 8 |

| IC2R7                      | IC2R6 | IC2R5            | IC2R4                | IC2R3        | IC2R2           | IC2R1              | IC2R0 |

| R/W-0                      | R/W-0 | R/W-0            | R/W-0                | R/W-0        | R/W-0           | R/W-0              | R/W-0 |

| bit 15-8 | IC2R<7:0>: Assign Input Capture 2 (IC2) to the Corresponding RPn Pin bits       |

|----------|---------------------------------------------------------------------------------|

|          | See Table 11-11 which contains a list of remappable inputs for the index value. |

| bit 7-0  | IC1R<7:0>: Assign Input Capture 1 (IC1) to the Corresponding RPn Pin bits       |

|          | See Table 11-11 which contains a list of remappable inputs for the index value. |

### REGISTER 11-14: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| IC4R7  | IC4R6 | IC4R5 | IC4R4 | IC4R3 | IC4R2 | IC4R1 | IC4R0 |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IC3R7 | IC3R6 | IC3R5 | IC3R4 | IC3R3 | IC3R2 | IC3R1 | IC3R0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8IC4R<7:0>: Assign Input Capture 4 (IC4) to the Corresponding RPn Pin bits<br/>See Table 11-11 which contains a list of remappable inputs for the index value.bit 7-0IC3R<7:0>: Assign Input Capture 3 (IC3) to the Corresponding RPn Pin bits<br/>See Table 11-11 which contains a list of remappable inputs for the index value.

### 15.2 Output Compare Control Registers

### REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

|                 | U-0                                                | OCSIDL              | OCTSEL2           | OCTSEL1           | OCTSEL0           |                 |        |  |

|-----------------|----------------------------------------------------|---------------------|-------------------|-------------------|-------------------|-----------------|--------|--|

| R/W-0<br>ENFLTA | U-0                                                |                     |                   |                   | OCISELU           | _               |        |  |

| ENFLTA          | U-0                                                |                     |                   |                   |                   |                 | bit    |  |

| ENFLTA          | 00                                                 | U-0                 | R/W-0, HSC        | R/W-0             | R/W-0             | R/W-0           | R/W-0  |  |

| bit 7           | _                                                  |                     | OCFLTA            | TRIGMODE          | OCM2              | OCM1            | OCM0   |  |

|                 |                                                    |                     |                   |                   |                   |                 | bit    |  |

| Legend:         |                                                    | USC - Hardwa        | are Settable/Cle  | arablo bit        |                   |                 |        |  |

| R = Readab      | lo hit                                             | W = Writable b      |                   |                   | ented bit, read a | ae 'O'          |        |  |

| -n = Value a    |                                                    | '1' = Bit is set    | п                 | '0' = Bit is clea |                   | x = Bit is unkr |        |  |

|                 |                                                    |                     |                   |                   |                   |                 | 101111 |  |

| bit 15-14       | Unimpleme                                          | ented: Read as '0   | ,                 |                   |                   |                 |        |  |

| bit 13          | OCSIDL: 0                                          | utput Compare x     | Stop in Idle Mo   | de Control bit    |                   |                 |        |  |

|                 | 1 = Output                                         | Compare x halts     | in CPU Idle mo    | de                |                   |                 |        |  |

|                 | 0 = Output                                         | Compare x contir    | ues to operate    | in CPU Idle mo    | de                |                 |        |  |

| bit 12-10       | OCTSEL<2                                           | :0>: Output Com     | oare x Clock Se   | lect bits         |                   |                 |        |  |

|                 | 111 = Peripheral clock (FP)                        |                     |                   |                   |                   |                 |        |  |

|                 |                                                    | 110 = Reserved      |                   |                   |                   |                 |        |  |

|                 | 101 = Rese                                         |                     | was of the OCy    |                   |                   |                 |        |  |

|                 |                                                    | K is the clock sou  |                   |                   | Ironous clock is  | supported)      |        |  |

|                 |                                                    | K is the clock sou  |                   |                   |                   |                 |        |  |

|                 |                                                    | K is the clock sou  |                   |                   |                   |                 |        |  |

|                 | 000 = T2CL                                         | K is the clock sou  | urce of the OCx   |                   |                   |                 |        |  |

| bit 9-8         | Unimpleme                                          | ented: Read as '0   | ,                 |                   |                   |                 |        |  |

| bit 7           | ENFLTA: Fa                                         | ault A Input Enabl  | e bit             |                   |                   |                 |        |  |

|                 | 1 = Output Compare Fault A input (OCFA) is enabled |                     |                   |                   |                   |                 |        |  |

|                 | 0 = Output                                         | Compare Fault A     | input (OCFA) is   | s disabled        |                   |                 |        |  |

| bit 6-5         | Unimpleme                                          | ented: Read as '0   | ,                 |                   |                   |                 |        |  |

| bit 4           | OCFLTA: P                                          | WM Fault A Cond     | lition Status bit |                   |                   |                 |        |  |

|                 |                                                    | ault A condition c  |                   |                   |                   |                 |        |  |

|                 | 0 = No PW                                          | M Fault A condition | on on the OCFA    | pin has occurre   | ed                |                 |        |  |

| bit 3           |                                                    | : Trigger Status N  |                   |                   |                   |                 |        |  |

|                 |                                                    | TAT (OCxCON2<       | ,                 | /hen OCxRS = (    | OCxTMR or in s    | oftware         |        |  |

|                 | 0 = TRIGS                                          | TAT is cleared on   | y by software     |                   |                   |                 |        |  |

**Note 1:** OCxR and OCxRS are double-buffered in PWM mode only.

### REGISTER 16-5: STCON: PWMx SECONDARY MASTER TIME BASE CONTROL REGISTER

| U-0           | U-0                                                                                                                                                                                                                      | U-0                                | R-0, HSC          | R/W-0             | R/W-0               | R/W-0           | R/W-0   |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------|-------------------|---------------------|-----------------|---------|--|--|

| _             | _                                                                                                                                                                                                                        | _                                  | SESTAT            | SEIEN             | EIPU <sup>(1)</sup> | SYNCPOL         | SYNCOEN |  |  |

| bit 15        |                                                                                                                                                                                                                          |                                    |                   |                   |                     |                 | bit     |  |  |

|               |                                                                                                                                                                                                                          |                                    |                   |                   |                     |                 |         |  |  |

| R/W-0         | R/W-0                                                                                                                                                                                                                    | R/W-0                              | R/W-0             | R/W-0             | R/W-0               | R/W-0           | R/W-0   |  |  |

| SYNCEN        | SYNCSRC2                                                                                                                                                                                                                 | SYNCSRC1                           | SYNCSRC0          | SEVTPS3           | SEVTPS2             | SEVTPS1         | SEVTPS0 |  |  |

| bit 7         |                                                                                                                                                                                                                          |                                    |                   |                   |                     |                 | bit     |  |  |

|               |                                                                                                                                                                                                                          |                                    |                   |                   |                     |                 |         |  |  |

| Legend:       | . 1. 11                                                                                                                                                                                                                  |                                    | are Settable/Cle  |                   |                     | 1               |         |  |  |

| R = Readable  |                                                                                                                                                                                                                          | W = Writable                       |                   | •                 | nented bit, read    |                 |         |  |  |

| -n = Value at | POR                                                                                                                                                                                                                      | '1' = Bit is set                   |                   | '0' = Bit is clea | ared                | x = Bit is unkr | nown    |  |  |

| bit 15-13     | Unimplomon                                                                                                                                                                                                               | ted: Read as '                     | ``                |                   |                     |                 |         |  |  |

| bit 12        | -                                                                                                                                                                                                                        | cial Event Inter                   |                   |                   |                     |                 |         |  |  |

|               |                                                                                                                                                                                                                          |                                    | interrupt is pen  | dina              |                     |                 |         |  |  |

|               |                                                                                                                                                                                                                          |                                    | interrupt is not  |                   |                     |                 |         |  |  |

| bit 11        | SEIEN: Speci                                                                                                                                                                                                             | ial Event Interru                  | upt Enable bit    |                   |                     |                 |         |  |  |

|               |                                                                                                                                                                                                                          |                                    | interrupt is ena  |                   |                     |                 |         |  |  |

|               |                                                                                                                                                                                                                          | • •                                | interrupt is disa |                   |                     |                 |         |  |  |

| bit 10        | <b>EIPU:</b> Enable Immediate Period Updates bit <sup>(1)</sup><br>1 = Active Secondary Period register is updated immediately                                                                                           |                                    |                   |                   |                     |                 |         |  |  |

|               |                                                                                                                                                                                                                          |                                    |                   |                   |                     | ndaries         |         |  |  |

| bit 9         | <ul> <li>0 = Active Secondary Period register updates occur on PWMx cycle boundaries</li> <li>SYNCPOL: Synchronize Input and Output Polarity bit</li> <li>1 = SYNCIx/SYNCO2 polarity is inverted (active-low)</li> </ul> |                                    |                   |                   |                     |                 |         |  |  |

|               |                                                                                                                                                                                                                          |                                    |                   |                   |                     |                 |         |  |  |

|               | 0 = SYNCIx/S                                                                                                                                                                                                             | SYNCO2 polari                      | ty is active-high |                   |                     |                 |         |  |  |

| bit 8         |                                                                                                                                                                                                                          | -                                  | ter Time Base S   | Synchronizatio    | n Enable bit        |                 |         |  |  |

|               |                                                                                                                                                                                                                          | output is enabl<br>output is disab |                   |                   |                     |                 |         |  |  |

| bit 7         |                                                                                                                                                                                                                          | -                                  | iry Master Time   | Rase Synchro      | nization Enabl      | e hit           |         |  |  |

|               |                                                                                                                                                                                                                          |                                    | of secondary ti   | -                 |                     |                 |         |  |  |

|               |                                                                                                                                                                                                                          |                                    | of secondary ti   |                   |                     |                 |         |  |  |

| bit 6-4       | SYNCSRC<2                                                                                                                                                                                                                | :0>: Secondar                      | y Time Base Sy    | nc Source Sel     | ection bits         |                 |         |  |  |

|               | 111 = Reserv                                                                                                                                                                                                             |                                    |                   |                   |                     |                 |         |  |  |

|               | 101 = Reserved                                                                                                                                                                                                           |                                    |                   |                   |                     |                 |         |  |  |

|               | 100 = Reserved<br>011 = PTG Trigger Output 17                                                                                                                                                                            |                                    |                   |                   |                     |                 |         |  |  |

|               | 010 = PTG Trigger Output 16                                                                                                                                                                                              |                                    |                   |                   |                     |                 |         |  |  |

|               | 001 = SYNCI2                                                                                                                                                                                                             |                                    |                   |                   |                     |                 |         |  |  |

| hit 2 0       | <ul> <li>3-0 SEVTPS&lt;3:0&gt;: PWMx Secondary Special Event Trigger Output Postscaler Select bi</li> </ul>                                                                                                              |                                    |                   |                   |                     |                 |         |  |  |

| bit 3-0       | 1111 = 1:16 p                                                                                                                                                                                                            |                                    | nuary opecial E   |                   |                     |                 |         |  |  |

|               | 0001 = 1:2 pc                                                                                                                                                                                                            |                                    |                   |                   |                     |                 |         |  |  |

|               | •                                                                                                                                                                                                                        |                                    |                   |                   |                     |                 |         |  |  |

|               |                                                                                                                                                                                                                          |                                    |                   |                   |                     |                 |         |  |  |

|               | •                                                                                                                                                                                                                        |                                    |                   |                   |                     |                 |         |  |  |

Note 1: This bit only applies to the secondary master time base period.

| R/W-0                   | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                                                          | U-0                                                                                                                                      | R/W-0                                                                            | R/W-0            | R/W-0           | R/W-0     |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------|-----------------|-----------|

| HRPDIS                  | HRDDIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                              |                                                                                                                                          | BLANKSEL3                                                                        | BLANKSEL2        | BLANKSEL1       | BLANKSELO |

| bit 15                  | TIRDDIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                              |                                                                                                                                          | DEANICOLLU                                                                       | DEANICOLLZ       | DEANINOLLI      | bit 8     |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                          |                                                                                  |                  |                 | 5110      |

| U-0                     | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                                                                                                                        | R/W-0                                                                                                                                    | R/W-0                                                                            | R/W-0            | R/W-0           | R/W-0     |

| —                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CHOPSEL3                                                                                                                                                     | CHOPSEL2                                                                                                                                 | CHOPSEL1                                                                         | CHOPSEL0         | CHOPHEN         | CHOPLEN   |

| bit 7                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                          |                                                                                  | •                |                 | bit 0     |