Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 67                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

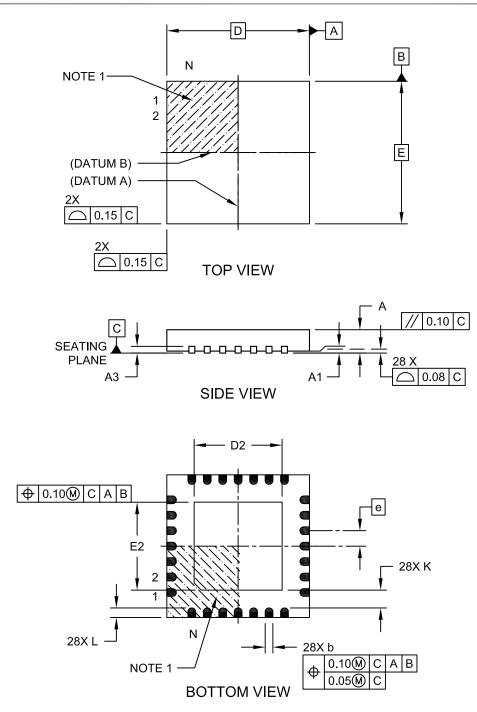

| Package / Case             | 80-TQFP                                                                         |

| Supplier Device Package    | 80-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs708-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

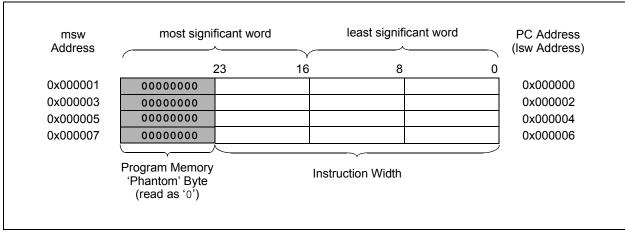

#### 4.2.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-5).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

### 4.2.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGS70X/80X family devices reserve the addresses between 0x000000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1 "Interrupt Vector Table"**.

#### FIGURE 4-5: PROGRAM MEMORY ORGANIZATION

#### 11.2.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control x register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin. See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 30-11 for the maximum VIH specification for each pin.

#### 11.3 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1). Table 11-1 through Table 11-5 show ANSELx bits' availability for device variants.

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin, defined as a digital input (including the ANx pins), can cause the input buffer to consume current that exceeds the device specifications.

#### 11.3.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP, as shown in Example 11-1.

### 11.4 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States, even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the ICN functionality of each I/O port. The CNENx registers contain the ICN interrupt enable control bits for each of the input pins. Setting any of these bits enables an ICN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source, or sink source, connected to the pin, and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

Note: Pull-ups and pull-downs on Input Change Notification pins should always be disabled when the port pin is configured as a digital output.

EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | OxFF00, WO | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

| REGISTER 11-51: RE | <b>RPOR18: PERIPHERAL PIN SELECT OUTPUT REGISTER 18</b> |

|--------------------|---------------------------------------------------------|

|--------------------|---------------------------------------------------------|

| U-0    | R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

|        | RP66R6 | RP66R5 | RP66R4 | RP66R3 | RP66R2 | RP66R1 | RP66R0 |

| bit 15 |        | I      | I      |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| U-0    | R/W-0  |

|        |        |        |        |        |        |        |        |

| —     | RP65R6 | RP65R5 | RP65R4 | RP65R3 | RP65R2 | RP65R1 | RP65R0 |

|-------|--------|--------|--------|--------|--------|--------|--------|

| bit 7 |        |        |        |        |        |        | bit 0  |

|       |        |        |        |        |        |        |        |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15   | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-8 | <b>RP66R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP66 Output Pin bits (see Table 11-13 for peripheral function numbers) |

| bit 7    | Unimplemented: Read as '0'                                                                                                                |

| bit 6-0  | <b>RP65R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP65 Output Pin bits (see Table 11-13 for peripheral function numbers) |

#### REGISTER 11-52: RPOR19: PERIPHERAL PIN SELECT OUTPUT REGISTER 19

| U-0    | R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| —      | RP68R6 | RP68R5 | RP68R4 | RP68R3 | RP68R2 | RP68R1 | RP68R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| U-0   | R/W-0  |

|-------|--------|--------|--------|--------|--------|--------|--------|

| —     | RP67R6 | RP67R5 | RP67R4 | RP67R3 | RP67R2 | RP67R1 | RP67R0 |

| bit 7 |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15 Unimplemented: Read as '0'

bit 14-8**RP68R<6:0>:** Peripheral Output Function is Assigned to RP68 Output Pin bits<br/>(see Table 11-13 for peripheral function numbers)bit 7**Unimplemented:** Read as '0'

bit 6-0 **RP67R<6:0>:** Peripheral Output Function is Assigned to RP67 Output Pin bits (see Table 11-13 for peripheral function numbers)

| U-0                               | R/W-0   | R/W-0                              | R/W-0   | R/W-0                | R/W-0   | R/W-0              | R/W-0   |

|-----------------------------------|---------|------------------------------------|---------|----------------------|---------|--------------------|---------|

| —                                 | RP177R6 | RP177R5                            | RP177R4 | RP177R3              | RP177R2 | RP177R1            | RP177R0 |

| bit 15                            | -       | -<br>-                             |         |                      |         |                    | bit 8   |

|                                   |         |                                    |         |                      |         |                    |         |

| U-0                               | R/W-0   | R/W-0                              | R/W-0   | R/W-0                | R/W-0   | R/W-0              | R/W-0   |

| _                                 | RP176R6 | RP176R5                            | RP176R4 | RP176R3              | RP176R2 | RP176R1            | RP176R0 |

| bit 7                             |         |                                    |         |                      |         | •                  | bit 0   |

|                                   |         |                                    |         |                      |         |                    |         |

| Legend:                           |         |                                    |         |                      |         |                    |         |

| R = Readable bit W = Writable bit |         | U = Unimplemented bit, read as '0' |         |                      |         |                    |         |

| -n = Value at POR                 |         | '1' = Bit is set                   |         | '0' = Bit is cleared |         | x = Bit is unknown |         |

|                                   |         |                                    |         |                      |         |                    |         |

| bit 15   | Unimplemented: Read as '0'                                                                                                                  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-8 | <b>RP177R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP177 Output Pin bits (see Table 11-13 for peripheral function numbers) |

| bit 7    | Unimplemented: Read as '0'                                                                                                                  |

| bit 6-0  | <b>RP176R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP176 Output Pin bits (see Table 11-13 for peripheral function numbers) |

#### REGISTER 11-58: RPOR25: PERIPHERAL PIN SELECT OUTPUT REGISTER 25

| U-0    | R/W-0   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| —      | RP179R6 | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

|        |         |         |         |         |         |         |         |

| U-0    | R/W-0   |

| —      | RP178R6 | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 |

| bit 7  |         |         |         |         |         |         | bit 0   |

|        |         |         |         |         |         |         |         |

| Logond |         |         |         |         |         |         |         |

| Legend.           |                  |                       |                                    |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

bit 15 Unimplemented: Read as '0'

| bit 14-8 | <b>RP179R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP179 Output Pin bits |

|----------|-------------------------------------------------------------------------------------------|

|          | (see Table 11-13 for peripheral function numbers)                                         |

| bit 7    | Unimplemented: Read as '0'                                                                |

bit 6-0 **RP178R<6:0>:** Peripheral Output Function is Assigned to RP178 Output Pin bits (see Table 11-13 for peripheral function numbers)

#### REGISTER 16-5: STCON: PWMx SECONDARY MASTER TIME BASE CONTROL REGISTER

| U-0           | U-0                                                                                                           | U-0                                | R-0, HSC                                | R/W-0             | R/W-0               | R/W-0           | R/W-0   |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------|-------------------|---------------------|-----------------|---------|--|--|

| _             | _                                                                                                             | _                                  | SESTAT                                  | SEIEN             | EIPU <sup>(1)</sup> | SYNCPOL         | SYNCOEN |  |  |

| bit 15        |                                                                                                               |                                    |                                         |                   |                     |                 | bit     |  |  |

|               |                                                                                                               |                                    |                                         |                   |                     |                 |         |  |  |

| R/W-0         | R/W-0                                                                                                         | R/W-0                              | R/W-0                                   | R/W-0             | R/W-0               | R/W-0           | R/W-0   |  |  |

| SYNCEN        | SYNCSRC2                                                                                                      | SYNCSRC1                           | SYNCSRC0                                | SEVTPS3           | SEVTPS2             | SEVTPS1         | SEVTPS0 |  |  |

| bit 7         |                                                                                                               |                                    |                                         |                   |                     |                 | bit     |  |  |

|               |                                                                                                               |                                    |                                         |                   |                     |                 |         |  |  |

| Legend:       | . 1. 11                                                                                                       |                                    | are Settable/Cle                        |                   |                     | 1               |         |  |  |

| R = Readable  |                                                                                                               | W = Writable                       |                                         | •                 | nented bit, read    |                 |         |  |  |

| -n = Value at | POR                                                                                                           | '1' = Bit is set                   |                                         | '0' = Bit is clea | ared                | x = Bit is unkr | nown    |  |  |

| bit 15-13     | Unimplomon                                                                                                    | ted: Read as '                     | ``                                      |                   |                     |                 |         |  |  |

| bit 12        | -                                                                                                             | cial Event Inter                   |                                         |                   |                     |                 |         |  |  |

|               |                                                                                                               |                                    | interrupt is pen                        | dina              |                     |                 |         |  |  |

|               |                                                                                                               |                                    | interrupt is not                        |                   |                     |                 |         |  |  |

| bit 11        | SEIEN: Speci                                                                                                  | ial Event Interru                  | upt Enable bit                          |                   |                     |                 |         |  |  |

|               |                                                                                                               |                                    | interrupt is ena                        |                   |                     |                 |         |  |  |

|               |                                                                                                               | • •                                | interrupt is disa                       |                   |                     |                 |         |  |  |

| bit 10        |                                                                                                               |                                    | riod Updates bit                        |                   | a h i               |                 |         |  |  |

|               |                                                                                                               |                                    | l register is upda<br>l register update |                   |                     | ndaries         |         |  |  |

| bit 9         |                                                                                                               | •                                  | ut and Output F                         |                   |                     |                 |         |  |  |

|               |                                                                                                               |                                    | ty is inverted (ad                      | •                 |                     |                 |         |  |  |

|               | 0 = SYNCIx/S                                                                                                  | SYNCO2 polari                      | ty is active-high                       |                   |                     |                 |         |  |  |

| bit 8         |                                                                                                               | -                                  | ter Time Base S                         | Synchronizatio    | n Enable bit        |                 |         |  |  |

|               |                                                                                                               | output is enabl<br>output is disab |                                         |                   |                     |                 |         |  |  |

| bit 7         |                                                                                                               | -                                  | iry Master Time                         | Rase Synchro      | nization Enabl      | e hit           |         |  |  |

|               |                                                                                                               |                                    | of secondary ti                         | -                 |                     |                 |         |  |  |

|               |                                                                                                               |                                    | of secondary ti                         |                   |                     |                 |         |  |  |

| bit 6-4       | SYNCSRC<2                                                                                                     | :0>: Secondar                      | y Time Base Sy                          | nc Source Sel     | ection bits         |                 |         |  |  |

|               | 111 = Reserv                                                                                                  |                                    |                                         |                   |                     |                 |         |  |  |

|               | 101 = Reserved                                                                                                |                                    |                                         |                   |                     |                 |         |  |  |

|               | 100 = Reserved<br>011 = PTG Trigger Output 17                                                                 |                                    |                                         |                   |                     |                 |         |  |  |

|               | 010 = PTG Trigger Output 16                                                                                   |                                    |                                         |                   |                     |                 |         |  |  |

|               | 001 = SYNCI2                                                                                                  |                                    |                                         |                   |                     |                 |         |  |  |

| hit 2 0       | <ul> <li>3-0 SEVTPS&lt;3:0&gt;: PWMx Secondary Special Event Trigger Output Postscaler Select bits</li> </ul> |                                    |                                         |                   |                     |                 |         |  |  |

| bit 3-0       | 1111 = 1:16 p                                                                                                 |                                    | nuary opecial E                         |                   |                     |                 |         |  |  |

|               | 0001 = 1:2 pc                                                                                                 |                                    |                                         |                   |                     |                 |         |  |  |

|               | •                                                                                                             |                                    |                                         |                   |                     |                 |         |  |  |

|               |                                                                                                               |                                    |                                         |                   |                     |                 |         |  |  |

|               | •                                                                                                             |                                    |                                         |                   |                     |                 |         |  |  |

Note 1: This bit only applies to the secondary master time base period.

#### **REGISTER 17-6: PTGSDLIM: PTG STEP DELAY LIMIT REGISTER**<sup>(1,2)</sup>

| R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0    | R/W-0   | R/W-0   | R/W-0   |

|---------|---------|---------|--------|----------|---------|---------|---------|

| 10,00-0 | 10/00-0 | 10,00-0 | -      | -        | 10/00-0 | 10,00-0 | 10/00-0 |

|         |         |         | PTGSDL | IM<15:8> |         |         |         |

| bit 15  |         |         |        |          |         |         | bit 8   |

|         |         |         |        |          |         |         |         |

| R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0    | R/W-0   | R/W-0   | R/W-0   |

|         |         |         | PTGSDI | _IM<7:0> |         |         |         |

| bit 7   |         |         |        |          |         |         | bit 0   |

|         |         |         |        |          |         |         |         |

|         |         |         |        |          |         |         |         |

| Legend:           |                  |                        |                                    |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |

bit 15-0 **PTGSDLIM<15:0>:** PTG Step Delay Limit Register bits Holds a PTG Step delay value, representing the number of additional PTG clocks, between the start of a Step command and the completion of a Step command.

- **Note 1:** A base Step delay of one PTG clock is added to any value written to the PTGSDLIM register (Step Delay = (PTGSDLIM) + 1).

- 2: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

#### REGISTER 17-7: PTGC0LIM: PTG COUNTER 0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0         R/W-0 <th< th=""><th>R/W-0<br/>bit 8</th></th<> | R/W-0<br>bit 8 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| bit 15<br>R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0<br>PTGC0LIM<7:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 8          |

| R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0<br>PTGC0LIM<7:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 8          |

| PTGC0LIM<7:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

| PTGC0LIM<7:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0          |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 0          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

bit 15-0 **PTGC0LIM<15:0>:** PTG Counter 0 Limit Register bits

'1' = Bit is set

May be used to specify the loop count for the PTGJMPC0 Step command or as a limit register for the General Purpose Counter 0.

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

#### REGISTER 17-12: PTGQPTR: PTG STEP QUEUE POINTER REGISTER<sup>(1)</sup>

| U-0                                                     | U-0 | U-0          | U-0          | U-0                                | U-0   | U-0   | U-0   |  |

|---------------------------------------------------------|-----|--------------|--------------|------------------------------------|-------|-------|-------|--|

| —                                                       | —   | —            | —            | —                                  | —     |       | —     |  |

| bit 15                                                  |     |              |              |                                    | •     |       | bit 8 |  |

|                                                         |     |              |              |                                    |       |       |       |  |

| U-0                                                     | U-0 | U-0          | R/W-0        | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

| —                                                       | —   | —            | PTGQPTR<4:0> |                                    |       |       |       |  |

| bit 7                                                   |     |              |              |                                    |       |       | bit 0 |  |

|                                                         |     |              |              |                                    |       |       |       |  |

| Legend:                                                 |     |              |              |                                    |       |       |       |  |

| R = Readable I                                          | bit | W = Writable | bit          | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared |     |              | ared         | x = Bit is unki                    | nown  |       |       |  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 **PTGQPTR<4:0>:** PTG Step Queue Pointer Register bits This register points to the currently active Step command in the Step queue.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

### **REGISTER 17-13: PTGQUEX: PTG STEP QUEUE REGISTER x (x = 0-15)**<sup>(1,3)</sup>

| R/W-0                        | R/W-0 | R/W-0 | R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 |  |

|------------------------------|-------|-------|-----------|----------------------|-------|-------|-------|--|

|                              |       |       | STEP(2x + | - 1)<7:0> <b>(2)</b> |       |       |       |  |

| bit 15                       |       |       |           |                      |       |       | bit 8 |  |

|                              |       |       |           |                      |       |       |       |  |

| R/W-0                        | R/W-0 | R/W-0 | R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 |  |

| STEP(2x)<7:0> <sup>(2)</sup> |       |       |           |                      |       |       |       |  |

| bit 7                        |       |       |           |                      |       |       | bit ( |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8STEP(2x + 1)<7:0>: PTG Step Queue Pointer Register bits<sup>(2)</sup><br/>A queue location for storage of the STEP(2x +1) command byte.bit 7-0STEP(2x)<7:0>: PTG Step Queue Pointer Register bits<sup>(2)</sup>

A queue location for storage of the STEP(2x) command byte.

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: Refer to Table 17-1 for the Step command encoding.

- 3: The Step registers maintain their values on any type of Reset.

#### 20.1 UART Helpful Tips

- In multi-node, direct connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pullup or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the UxRX pin.

- b) If URXINV = 1, use a pull-down resistor on the UxRX pin.

- 2. The first character received on a wake-up from Sleep mode, caused by activity on the UxRX pin of the UARTx module, will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 20.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 20.2.1 KEY RESOURCES

- "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 21-1: CLCxCONL: CLCx CONTROL REGISTER (LOW) (CONTINUED)

- bit 2-0 MODE<2:0>: CLCx Mode bits

- 111 = Single Input Transparent Latch with S and R

- 110 = JK Flip-Flop with R

- 101 = Two-Input D Flip-Flop with R

- 100 = Single Input D Flip-Flop with S and R

- 011 = SR Latch

- 010 = Four-Input AND

- 001 = Four-Input OR-XOR

- 000 = Four-Input AND-OR

#### REGISTER 21-2: CLCxCONH: CLCx CONTROL REGISTER (HIGH)

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|

| —            | —   | —   | —   | —   |     |     | —   |  |

| bit 15 bit 8 |     |     |     |     |     |     |     |  |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | G4POL | G3POL | G2POL | G1POL |

| bit 7 |     |     |     |       |       |       | bit 0 |

#### Legend:

| Legena.           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                                 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | G4POL: Gate 4 Polarity Control bit                                                                                                         |

|          | <ul><li>1 = Channel 4 logic output is inverted when applied to the logic cell</li><li>0 = Channel 4 logic output is not inverted</li></ul> |

| bit 2    | G3POL: Gate 3 Polarity Control bit                                                                                                         |

|          | <ul><li>1 = Channel 3 logic output is inverted when applied to the logic cell</li><li>0 = Channel 3 logic output is not inverted</li></ul> |

| bit 1    | G2POL: Gate 2 Polarity Control bit                                                                                                         |

|          | <ul><li>1 = Channel 2 logic output is inverted when applied to the logic cell</li><li>0 = Channel 2 logic output is not inverted</li></ul> |

| bit 0    | G1POL: Gate 1 Polarity Control bit                                                                                                         |

|          | <ul><li>1 = Channel 1 logic output is inverted when applied to the logic cell</li><li>0 = Channel 1 logic output is not inverted</li></ul> |

#### REGISTER 22-34: ADFLxCON: ADC DIGITAL FILTER x CONTROL REGISTER (x = 0 or 1) (CONTINUED)

00000 **= AN0**

REGISTER 23-4: CxFCTRL: CANx FIFO CONTROL REGISTER

| R/W-0                                             | R/W-0                                                                                                                                                                                                                                  | R/W-0            | U-0   | U-0              | U-0   | U-0                | U-0   |  |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|------------------|-------|--------------------|-------|--|

| DMABS2                                            | DMABS1                                                                                                                                                                                                                                 | DMABS0           | _     | _                | —     | —                  | _     |  |

| bit 15                                            |                                                                                                                                                                                                                                        |                  |       |                  |       |                    | bit 8 |  |

|                                                   |                                                                                                                                                                                                                                        |                  |       |                  |       |                    |       |  |

| U-0                                               | U-0                                                                                                                                                                                                                                    | U-0              | R/W-0 | R/W-0            | R/W-0 | R/W-0              | R/W-0 |  |

| _                                                 |                                                                                                                                                                                                                                        | —                | FSA4  | FSA3             | FSA2  | FSA1               | FSA0  |  |

| bit 7                                             |                                                                                                                                                                                                                                        |                  |       |                  |       |                    | bit 0 |  |

|                                                   |                                                                                                                                                                                                                                        |                  |       |                  |       |                    |       |  |

| Legend:                                           |                                                                                                                                                                                                                                        |                  |       |                  |       |                    |       |  |

| R = Readable bitW = Writable bitU = Unimplemented |                                                                                                                                                                                                                                        |                  |       |                  |       |                    |       |  |

| -n = Value at                                     | POR                                                                                                                                                                                                                                    | '1' = Bit is set |       | '0' = Bit is cle | ared  | x = Bit is unknown |       |  |

| bit 12-5<br>bit 4-0                               | 111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM<br>100 = 16 buffers in RAM<br>011 = 12 buffers in RAM<br>010 = 8 buffers in RAM<br>001 = 6 buffers in RAM<br>000 = 4 buffers in RAM<br>Unimplemented: Read as '0' |                  |       |                  |       |                    |       |  |

|                                                   | 4-0 FSA<4:0>: FIFO Area Starts with Buffer bits<br>11111 = Receive Buffer RB31<br>11110 = Receive Buffer RB30<br>•<br>•<br>00001 = Transmit/Receive Buffer TRB1<br>00000 = Transmit/Receive Buffer TRB0                                |                  |       |                  |       |                    |       |  |

| Bit Field              | Description                                                                                                                                                                                                                                                                                |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSS<1:0>               | Boot Segment Code-Protect Level bits                                                                                                                                                                                                                                                       |

|                        | <ul> <li>11 = Boot Segment is not code-protected other than BWRP</li> <li>10 = Standard security</li> <li>0x = High security</li> </ul>                                                                                                                                                    |

| BSEN                   | Boot Segment Control bit<br>1 = No Boot Segment is enabled<br>0 = Boot Segment size is determined by the BSLIM<12:0> bits                                                                                                                                                                  |

| BWRP                   | Boot Segment Write-Protect bit                                                                                                                                                                                                                                                             |

| binti                  | 1 = Boot Segment can be written<br>0 = Boot Segment is write-protected                                                                                                                                                                                                                     |

| BSLIM<12:0>            | Boot Segment Flash Page Address Limit bits<br>Contains the last active Boot Segment page. The value to be programmed is the inverted<br>page address, such that programming additional '0's can only increase the Boot Segment<br>size (i.e., 0x1FFD = 2 Pages or 1024 IW).                |

| GSS<1:0>               | General Segment Code-Protect Level bits                                                                                                                                                                                                                                                    |

|                        | <ul> <li>11 = User program memory is not code-protected</li> <li>10 = Standard security</li> <li>0x = High security</li> </ul>                                                                                                                                                             |

| GWRP                   | General Segment Write-Protect bit                                                                                                                                                                                                                                                          |

|                        | <ul> <li>1 = User program memory is not write-protected</li> <li>0 = User program memory is write-protected</li> </ul>                                                                                                                                                                     |

| CWRP                   | Configuration Segment Write-Protect bit<br>1 = Configuration data is not write-protected<br>0 = Configuration data is write-protected                                                                                                                                                      |

| CSS<2:0>               | Configuration Segment Code-Protect Level bits<br>111 = Configuration data is not code-protected<br>110 = Standard security<br>10x = Enhanced security<br>0xx = High security                                                                                                               |

| BTSWP                  | BOOTSWP Instruction Enable/Disable bit<br>1 = BOOTSWP instruction is disabled<br>0 = BOOTSWP instruction is enabled                                                                                                                                                                        |

| BSEQ<11:0>             | Boot Sequence Number bits (Dual Partition modes only)<br>Relative value defining which partition will be active after device Reset; the partition<br>containing a lower boot number will be active.                                                                                        |

| IBSEQ<11:0>            | Inverse Boot Sequence Number bits (Dual Partition modes only)<br>The one's complement of BSEQ<11:0>; must be calculated by the user and written for<br>device programming. If BSEQx and IBSEQx are not complements of each other, the Boot<br>Sequence Number is considered to be invalid. |

| AIVTDIS <sup>(1)</sup> | Alternate Interrupt Vector Table bit<br>1 = Alternate Interrupt Vector Table is disabled<br>0 = Alternate Interrupt Vector Table is enabled if INTCON2<8> = 1                                                                                                                              |

| IESO                   | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Starts up device with FRC, then automatically switches to the user-selected oscillator source when ready</li> <li>0 = Starts up device with the user-selected oscillator source</li> </ul>                                  |

| PWMLOCK                | PWMx Lock Enable bit<br>1 = Certain PWMx registers may only be written after a key sequence<br>0 = PWMx registers may be written without a key sequence                                                                                                                                    |

#### TABLE 27-2: CONFIGURATION BITS DESCRIPTION

Note 1: The Boot Segment must be present to use the Alternate Interrupt Vector Table.

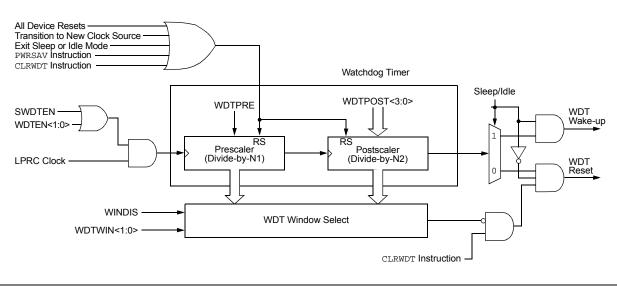

### 27.6 Watchdog Timer (WDT)

For dsPIC33EPXXXGS70X/80X family devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 27.6.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Time-out Period (TWDT), as shown in Parameter SY12 in Table 30-23.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler time-out periods, ranges from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### FIGURE 27-2: WDT BLOCK DIAGRAM

### 27.6.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3:2>) needs to be cleared in software after the device wakes up.

### 27.6.3 ENABLING WDT

The WDT is enabled or disabled by the WDTEN<1:0> Configuration bits in the FWDT Configuration register. When the WDTEN<1:0> Configuration bits have been programmed to '0b11', the WDT is always enabled.

The WDT can be optionally controlled in software when the WDTEN<1:0> Configuration bits have been programmed to '0b10'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disables the WDT during non-critical segments for maximum power savings.

The WDT Time-out flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

#### 27.6.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<7>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

#### TABLE 28-2: INSTRUCTION SET OVERVIEW

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |                | Description                                         | # of<br>Words | # of<br>Cycles <sup>(1)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|-----------------|----------------|-----------------------------------------------------|---------------|-------------------------------|--------------------------|

| 1                  | ADD                  | ADD Acc         |                | Add Accumulators                                    | 1             | 1                             | OA,OB,SA,SB              |

|                    |                      | ADD             | f              | f = f + WREG                                        | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD             | f,WREG         | WREG = f + WREG                                     | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD             | #lit10,Wn      | Wd = lit10 + Wd                                     | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD             | Wb,Ws,Wd       | Wd = Wb + Ws                                        | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD             | Wb,#lit5,Wd    | Wd = Wb + lit5                                      | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD             | Wso,#Slit4,Acc | 16-bit Signed Add to Accumulator                    | 1             | 1                             | OA,OB,SA,SB              |

| 2                  | ADDC                 | ADDC            | f              | f = f + WREG + (C)                                  | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC            | f,WREG         | WREG = f + WREG + (C)                               | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC            | #lit10,Wn      | Wd = lit10 + Wd + (C)                               | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC            | Wb,Ws,Wd       | Wd = Wb + Ws + (C)                                  | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC            | Wb,#lit5,Wd    | Wd = Wb + lit5 + (C)                                | 1             | 1                             | C,DC,N,OV,Z              |

| 3                  | AND                  | AND             | f              | f = f .AND. WREG                                    | 1             | 1                             | N,Z                      |

|                    |                      | AND             | f,WREG         | WREG = f .AND. WREG                                 | 1             | 1                             | N,Z                      |

|                    |                      | AND             | #lit10,Wn      | Wd = lit10 .AND. Wd                                 | 1             | 1                             | N,Z                      |

|                    |                      | AND             | Wb,Ws,Wd       | Wd = Wb .AND. Ws                                    | 1             | 1                             | N,Z                      |

|                    |                      | AND             | Wb,#lit5,Wd    | Wd = Wb .AND. lit5                                  | 1             | 1                             | N,Z                      |

| 4                  | ASR                  | ASR             | f              | f = Arithmetic Right Shift f                        | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | ASR             | f,WREG         | WREG = Arithmetic Right Shift f                     | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | ASR             | Ws,Wd          | Wd = Arithmetic Right Shift Ws                      | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | ASR             | Wb,Wns,Wnd     | Wnd = Arithmetic Right Shift Wb by Wns              | 1             | 1                             | N,Z                      |

|                    |                      | ASR             | Wb,#lit5,Wnd   | Wnd = Arithmetic Right Shift Wb by lit5             | 1             | 1                             | N,Z                      |

| 5                  | BCLR                 | BCLR            | f,#bit4        | Bit Clear f                                         | 1             | 1                             | None                     |

|                    |                      | BCLR            | Ws,#bit4       | Bit Clear Ws                                        | 1             | 1                             | None                     |

| 6                  | BOOTSWP              | BOOTSWP         |                | Swap the active and inactive program<br>Flash Space | 1             | 2                             | None                     |

| 7                  | BRA                  | BRA             | C,Expr         | Branch if Carry                                     | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | GE, Expr       | Branch if greater than or equal                     | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | GEU, Expr      | Branch if unsigned greater than or equal            | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | GT,Expr        | Branch if greater than                              | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | GTU, Expr      | Branch if unsigned greater than                     | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | LE, Expr       | Branch if less than or equal                        | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | LEU, Expr      | Branch if unsigned less than or equal               | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | LT,Expr        | Branch if less than                                 | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | LTU, Expr      | Branch if unsigned less than                        | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | N,Expr         | Branch if Negative                                  | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | NC, Expr       | Branch if Not Carry                                 | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | NN, Expr       | Branch if Not Negative                              | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | NOV, Expr      | Branch if Not Overflow                              | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | NZ, Expr       | Branch if Not Zero                                  | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | OA,Expr        | Branch if Accumulator A overflow                    | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | OB,Expr        | Branch if Accumulator B overflow                    | 1             | 1 (4)                         | None                     |

|                    |                      | BRA             | OV,Expr        | Branch if Overflow                                  | 1             | 1 (4)                         | None                     |