Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 67                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

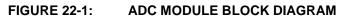

| Data Converters            | A/D 22x12b; D/A 2x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-TQFP                                                                         |

| Supplier Device Package    | 80-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs708-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.6 Instruction Addressing Modes

The addressing modes shown in Table 4-17 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

#### 4.6.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.6.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

#### TABLE 4-17: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

#### REGISTER 5-2: NVMADR: NONVOLATILE MEMORY LOWER ADDRESS REGISTER

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |

|-----------------------------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                                   |       |                  | NVMA  | DR<15:8>                                |       |       |       |

| bit 15                            |       |                  |       |                                         |       |       | bit 8 |

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |

|                                   |       |                  | NVMA  | DR<7:0>                                 |       |       |       |

| bit 7                             |       |                  |       |                                         |       |       | bit 0 |

| Legend:                           |       |                  |       |                                         |       |       |       |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P                   | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 **NVMADR<15:0>:** Nonvolatile Memory Lower Write Address bits Selects the lower 16 bits of the location to program or erase in Program Flash Memory. This register may be read or written to by the user application.

#### REGISTER 5-3: NVMADRU: NONVOLATILE MEMORY UPPER ADDRESS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | —   | —   | —   | —   | —   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-x | R/W-x | R/W-x | R/W-x  | R/W-x    | R/W-x | R/W-x | R/W-x |

|-------|-------|-------|--------|----------|-------|-------|-------|

|       |       |       | NVMADR | U<23:16> |       |       |       |

| bit 7 |       |       |        |          |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMADRU<23:16>: Nonvolatile Memory Upper Write Address bits

Selects the upper 8 bits of the location to program or erase in Program Flash Memory. This register may be read or written to by the user application.

#### 11.6.5 OUTPUT MAPPING

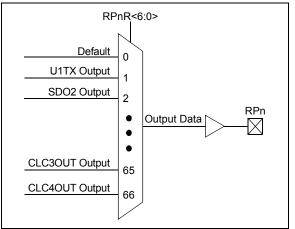

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-33 through Register 11-56). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-13 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUTS FOR RPn

### 11.6.5.1 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings, across any or all of the RPn pins, is possible. This includes both many-to-one and one-to-many mappings of peripheral inputs, and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| T1CKR7 | T1CKR6 | T1CKR5 | T1CKR4 | T1CKR3 | T1CKR2 | T1CKR1 | T1CKR0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| U-0    |

#### REGISTER 11-11: RPINR2: PERIPHERAL PIN SELECT INPUT REGISTER 2

|         | — | _ | _ | — | — | — | —     |

|---------|---|---|---|---|---|---|-------|

| bit 7   |   |   |   |   |   |   | bit 0 |

|         |   |   |   |   |   |   |       |

| Legend: |   |   |   |   |   |   |       |

| Logona.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 **T1CKR<7:0>:** Assign Timer1 External Clock (T1CK) to the Corresponding RPn Pin bits See Table 11-11 which contains a list of remappable inputs for the index value. bit 7-0 **Unimplemented:** Read as '0'

#### REGISTER 11-12: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| T3CKR7 | T3CKR6 | T3CKR5 | T3CKR4 | T3CKR3 | T3CKR2 | T3CKR1 | T3CKR0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-0  |

| bit 7  |        |        |        |        |        |        | bit 0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| T2CKR7 | T2CKR6 | T2CKR5 | T2CKR4 | T2CKR3 | T2CKR2 | T2CKR1 | T2CKR0 |

| R/W-0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8T3CKR<7:0>: Assign Timer3 External Clock (T3CK) to the Corresponding RPn Pin bits<br/>See Table 11-11 which contains a list of remappable inputs for the index value.bit 7-0T2CKR<7:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn Pin bits<br/>See Table 11-11 which contains a list of remappable inputs for the index value.

© 2016-2017 Microchip Technology Inc.

#### REGISTER 16-12: PWMCONx: PWMx CONTROL REGISTER (x = 1 to 8) (CONTINUED)

- bit 7-6 DTC<1:0>: Dead-Time Control bits 11 = Reserved 10 = Dead-time function is disabled 01 = Negative dead time is actively applied for Complementary Output mode 00 = Positive dead time is actively applied for all Output modes bit 5-4 Unimplemented: Read as '0' bit 3 MTBS: Master Time Base Select bit 1 = PWMx generator uses the secondary master time base for synchronization and the clock source for the PWMx generation logic (if secondary time base is available) 0 = PWMx generator uses the primary master time base for synchronization and the clock source for the PWMx generation logic CAM: Center-Aligned Mode Enable bit<sup>(2,3,4)</sup> bit 2 1 = Center-Aligned mode is enabled 0 = Edge-Aligned mode is enabled bit 1 XPRES: External PWMx Reset Control bit<sup>(5)</sup> 1 = Current-limit source resets the time base for this PWMx generator if it is in Independent Time Base mode 0 = External pins do not affect the PWMx time base bit 0 IUE: Immediate Update Enable bit 1 = Updates to the active Duty Cycle, Phase Offset, Dead-Time and local Time Base Period registers are immediate 0 = Updates to the active Duty Cycle, Phase Offset, Dead-Time and local Time Base Period registers are synchronized to the local PWMx time base Note 1: Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller. 2: The Independent Time Base mode (ITB = 1) must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored. 3: These bits should not be changed after the PWMx is enabled by setting PTEN (PTCON<15>) = 1. 4: Center-Aligned mode ignores the Least Significant 3 bits of the Duty Cycle, Phase and Dead-Time

- registers. The highest Center-Aligned mode resolution available is 8.32 ns with the clock prescaler set to the fastest clock.

- 5: Configure CLMOD (FCLCONx<8>) = 0 and ITB (PWMCONx<9>) = 1 to operate in External Period Reset mode.

#### **REGISTER 16-15:** PHASEX: PWMx PRIMARY PHASE-SHIFT REGISTER (x = 1 to 8)<sup>(1,2)</sup>

| R/W-0                             | R/W-0 | R/W-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|-----------------------------------|-------|-------|-------|--------------|------------------|----------|-------|

|                                   |       |       | PHASE | Ex<15:8>     |                  |          |       |

| bit 15                            |       |       |       |              |                  |          | bit 8 |

|                                   |       |       |       |              |                  |          |       |

| R/W-0                             | R/W-0 | R/W-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                                   |       |       | PHAS  | Ex<7:0>      |                  |          |       |

| bit 7                             |       |       |       |              |                  |          | bit 0 |

|                                   |       |       |       |              |                  |          |       |

| Legend:                           |       |       |       |              |                  |          |       |

| R = Readable bit W = Writable bit |       |       |       | U = Unimplen | nented bit, read | l as '0' |       |

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWMx Generator bits

- **Note 1:** If PWMCONx<9> = 0, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Phase-shift value for PWMxH only

- When the PHASEx/SPHASEx registers provide the phase shift with respect to the master time base; therefore, the valid range is 0x0000 through period

- **2:** If PWMCONx<9> = 1, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Independent time base period value for PWMxH only

- When the PHASEx/SPHASEx registers provide the local period, the valid range is 0x0000-0xFFF8

#### REGISTER 16-20: IOCONx: PWMx I/O CONTROL REGISTER (x = 1 to 8) (CONTINUED)

| bit 3-2 | CLDAT<1:0>: State for PWMxH and PWMxL Pins if CLMOD is Enabled bits <sup>(2)</sup>                            |

|---------|---------------------------------------------------------------------------------------------------------------|

|         | IFLTMOD (FCLCONx<15>) = 0: Normal Fault mode:                                                                 |

|         | If current limit is active, then CLDAT1 provides the state for the PWMxH pin.                                 |

|         | If current limit is active, then CLDAT0 provides the state for the PWMxL pin.                                 |

|         | IFLTMOD (FCLCONx<15>) = 1: Independent Fault mode:                                                            |

|         | CLDAT<1:0> bits are ignored.                                                                                  |

| bit 1   | SWAP: SWAP PWMxH and PWMxL Pins bit                                                                           |

|         | 1 = PWMxH output signal is connected to the PWMxL pins; PWMxL output signal is connected to the<br>PWMxH pins |

|         | 0 = PWMxH and PWMxL pins are mapped to their respective pins                                                  |

| bit 0   | OSYNC: Output Override Synchronization bit                                                                    |

|         | 1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWMx time base                          |

|         | 0 = Output overrides via the OVRDAT<1:0> bits occur on the next CPU clock boundary                            |

| Nata A. |                                                                                                               |

- **Note 1:** These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: State represents the active/inactive state of the PWMx depending on the POLH and POLL bits settings.

#### **REGISTER 16-21: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER (x = 1 to 8)**

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|-------------------|-------|-----------------|-------|

|                                   |       |                  | TRGCI                              | MP<12:5>          |       |                 |       |

| bit 15                            |       |                  |                                    |                   |       |                 | bit 8 |

|                                   |       |                  |                                    |                   |       |                 |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0             | U-0   | U-0             | U-0   |

|                                   |       | TRGCMP<4:0>      | •                                  |                   | —     | —               | —     |

| bit 7                             |       |                  |                                    |                   |       |                 | bit 0 |

|                                   |       |                  |                                    |                   |       |                 |       |

| Legend:                           |       |                  |                                    |                   |       |                 |       |

| R = Readable bit W = Writable bit |       |                  | U = Unimplemented bit, read as '0' |                   |       |                 |       |

| -n = Value at POR                 |       | '1' = Bit is set |                                    | '0' = Bit is clea | ared  | x = Bit is unkn | iown  |

|                                   | -     |                  |                                    |                   |       |                 | -     |

bit 15-3 **TRGCMP<12:0>:** Trigger Compare Value bits When the primary PWMx functions in the local time base, this register contains the compare values that can trigger the ADC module.

bit 2-0 Unimplemented: Read as '0'

#### REGISTER 16-22: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER (x = 1 to 8) (CONTINUED)

| bit 7-3 | FLTSRC<4:0>: Fault Control Signal Source Select for PWMx Generator bits<br>11111 = Reserved<br>10001 = Reserved<br>10000 = Analog Comparator 4<br>01111 = Analog Comparator 3<br>01110 = Analog Comparator 2<br>01101 = Analog Comparator 1<br>01100 = Fault 12<br>01011 = Fault 11<br>01010 = Fault 11<br>01010 = Fault 10<br>01001 = Fault 9<br>01000 = Fault 8<br>00111 = Fault 7 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 00110 = Fault 7 $00110 = Fault 6$ $00101 = Fault 5$ $00100 = Fault 4$ $00011 = Fault 3$ $00010 = Fault 2$ $00001 = Fault 1$ $00000 = Reserved$                                                                                                                                                                                                                                       |

| bit 2   | <b>FLTPOL:</b> Fault Polarity for PWMx Generator bit <sup>(1)</sup><br>1 = The selected Fault source is active-low<br>0 = The selected Fault source is active-high                                                                                                                                                                                                                   |

| bit 1-0 | FLTMOD<1:0>: Fault Mode for PWMx Generator bits<br>11 = Fault input is disabled<br>10 = Reserved<br>01 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (cycle)<br>00 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (latched condition)                                                                                       |

Note 1: These bits should be changed only when PTEN = 0 (PTCON<15>).

#### REGISTER 16-23: STRIGX: PWMX SECONDARY TRIGGER COMPARE VALUE REGISTER (x = 1 to 8)<sup>(1)</sup>

| R/W-0        | R/W-0       | R/W-0                                               | R/W-0           | R/W-0                              | R/W-0 | R/W-0              | R/W-0        |  |

|--------------|-------------|-----------------------------------------------------|-----------------|------------------------------------|-------|--------------------|--------------|--|

|              |             |                                                     | STRGC           | MP<12:5>                           |       |                    |              |  |

| bit 15       |             |                                                     |                 |                                    |       |                    | bit 8        |  |

| R/W-0        | R/W-0       | R/W-0                                               | R/W-0           | R/W-0                              | U-0   | U-0                | U-0          |  |

|              |             | STRGCMP<4:0                                         | >               |                                    |       | _                  | _            |  |

| bit 7        |             |                                                     |                 |                                    |       |                    | bit (        |  |

| Legend:      |             |                                                     |                 |                                    |       |                    |              |  |

| R = Readab   | le bit      | W = Writable                                        | bit             | U = Unimplemented bit, read as '0' |       |                    |              |  |

| -n = Value a | t POR       | '1' = Bit is set                                    |                 | '0' = Bit is clea                  | ared  | x = Bit is unknown |              |  |

| bit 15-3     | When the se | <12:0>: Seconda<br>econdary PWMx<br>ger the ADC mod | functions in th | •                                  |       | contains the co    | mpare values |  |

| bit 2-0      |             | nted: Read as '                                     |                 |                                    |       |                    |              |  |

Note 1: STRIGx cannot generate the PWM trigger interrupts.

#### REGISTER 21-4: CLCxGLSL: CLCx GATE LOGIC INPUT SELECT LOW REGISTER (CONTINUED)

| bit 3 | G1D2T: Gate 1 Data Source 2 True Enable bit                                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Data Source 2 non-inverted signal is enabled for Gate 1                                                                                           |

|       | 0 = Data Source 2 non-inverted signal is disabled for Gate 1                                                                                          |

| bit 2 | G1D2N: Gate 1 Data Source 2 Negated Enable bit                                                                                                        |

|       | <ul> <li>1 = Data Source 2 inverted signal is enabled for Gate 1</li> <li>0 = Data Source 2 inverted signal is disabled for Gate 1</li> </ul>         |

| bit 1 | G1D1T: Gate 1 Data Source 1 True Enable bit                                                                                                           |

|       | <ul> <li>1 = Data Source 1 non-inverted signal is enabled for Gate 1</li> <li>0 = Data Source 1 non-inverted signal is disabled for Gate 1</li> </ul> |

| bit 0 | G1D1N: Gate 1 Data Source 1 Negated Enable bit                                                                                                        |

|       | 1 = Data Source 1 inverted signal is enabled for Gate 1                                                                                               |

|       | 0 = Data Source 1 inverted signal is disabled for Gate 1                                                                                              |

| REGISTER 2              | 2-0. ADCC                                                      |                                                                                                                                           | CONTROL RE                                                                                              | EGISTER 3 H       | IGH                         |                                                          |                  |

|-------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------|-----------------------------|----------------------------------------------------------|------------------|

| R/W-0                   | R/W-0                                                          | R/W-0                                                                                                                                     | R/W-0                                                                                                   | R/W-0             | R/W-0                       | R/W-0                                                    | R/W-0            |

| CLKSEL1                 | CLKSEL0                                                        | CLKDIV5                                                                                                                                   | CLKDIV4                                                                                                 | CLKDIV3           | CLKDIV2                     | CLKDIV1                                                  | CLKDIV0          |

| bit 15                  |                                                                |                                                                                                                                           |                                                                                                         |                   |                             |                                                          | bit 8            |

|                         |                                                                |                                                                                                                                           |                                                                                                         |                   |                             |                                                          |                  |

| R/W-0                   | U-0                                                            | U-0                                                                                                                                       | U-0                                                                                                     | R/W-0             | R/W-0                       | R/W-0                                                    | R/W-0            |

| SHREN                   | —                                                              | —                                                                                                                                         | —                                                                                                       | C3EN              | C2EN                        | C1EN                                                     | C0EN             |

| bit 7                   |                                                                |                                                                                                                                           |                                                                                                         |                   |                             |                                                          | bit 0            |

| Lonondi                 |                                                                |                                                                                                                                           |                                                                                                         |                   |                             |                                                          |                  |

| Legend:<br>R = Readable | hit                                                            | W = Writable                                                                                                                              | hit                                                                                                     | II – Unimplon     | anted hit rea               | d oo 'O'                                                 |                  |

| -n = Value at           |                                                                | '1' = Bit is set                                                                                                                          |                                                                                                         | '0' = Bit is clea | nented bit, read            | x = Bit is unkr                                          | 0.000            |

|                         | FUR                                                            | I - DILIS SEL                                                                                                                             |                                                                                                         |                   | areu                        |                                                          | IUWII            |

| bit 15-14               | 11 = APLL<br>10 = FRC<br>01 = Fosc (S                          | >: ADC Module                                                                                                                             |                                                                                                         | Selection bits    |                             |                                                          |                  |

| bit 13-8                | 00 = Fsys(S)                                                   | /stem Clock)<br>>: ADC Module                                                                                                             |                                                                                                         |                   |                             |                                                          |                  |

|                         | module clock<br>TCORESRC clo<br>register or the<br>111111 = 64 | source selecte<br>ock to get a con<br>SHRADCS<6<br>Source Clock P<br>Source Clock P<br>Source Clock P<br>Source Clock P<br>Source Clock P | d by the CLKS<br>re-specific TAD<br>:0> bits in the A<br>Periods<br>eriods<br>eriods<br>eriods<br>eriod | EL<1:0> bits. T   | hen, each AD<br>ng the ADCS | ledicated) from<br>C core individua<br><6:0> bits in the | ally divides the |

| bit 7                   | 1 = Shared Al                                                  | red ADC Core<br>DC core is ena<br>DC core is disa                                                                                         | bled                                                                                                    |                   |                             |                                                          |                  |

| bit 6-4                 | Unimplemen                                                     | ted: Read as '                                                                                                                            | )'                                                                                                      |                   |                             |                                                          |                  |

| bit 3                   | 1 = Dedicated                                                  | ated ADC Core<br>I ADC Core 3 is<br>I ADC Core 3 is                                                                                       | s enabled                                                                                               |                   |                             |                                                          |                  |

| bit 2                   | 1 = Dedicated                                                  | ated ADC Core<br>I ADC Core 2 is<br>I ADC Core 2 is                                                                                       | s enabled                                                                                               |                   |                             |                                                          |                  |

| bit 1                   | 1 = Dedicated                                                  | ated ADC Core<br>I ADC Core 1 is<br>I ADC Core 1 is                                                                                       | s enabled                                                                                               |                   |                             |                                                          |                  |

| bit 0                   | 1 = Dedicated                                                  | ated ADC Core<br>I ADC Core 0 is<br>I ADC Core 0 is                                                                                       | s enabled                                                                                               |                   |                             |                                                          |                  |

#### REGISTER 22-6: ADCON3H: ADC CONTROL REGISTER 3 HIGH

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| DIFF7  | SIGN7 | DIFF6 | SIGN6 | DIFF5 | SIGN5 | DIFF4 | SIGN4 |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| DIFF3  | SIGN3 | DIFF2 | SIGN2 | DIFF1 | SIGN1 | DIFF0 | SIGN0 |

| bit 7  |       | •     | •     | •     | ·     |       | bit 0 |

|        |       |       |       |       |       |       |       |

#### REGISTER 22-19: ADMODOL: ADC INPUT MODE CONTROL REGISTER 0 LOW

| Leaend: |

|---------|

| Logona. |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-1(odd) DIFF<7:0>: Differential-Mode for Corresponding Analog Inputs bits

- 1 = Channel is differential

- 0 = Channel is single-ended

bit 14-0 (even) SIGN<7:0>: Output Data Sign for Corresponding Analog Inputs bits

- 1 = Channel output data is signed

- 0 = Channel output data is unsigned

### REGISTER 22-20: ADMOD0H: ADC INPUT MODE CONTROL REGISTER 0 HIGH

| R/W-0                             | R/W-0  | R/W-0            | R/W-0                              | R/W-0                | R/W-0  | R/W-0              | R/W-0  |

|-----------------------------------|--------|------------------|------------------------------------|----------------------|--------|--------------------|--------|

| DIFF15                            | SIGN15 | DIFF14           | SIGN14                             | DIFF13               | SIGN13 | DIFF12             | SIGN12 |

| bit 15                            |        |                  |                                    |                      |        |                    | bit 8  |

|                                   |        |                  |                                    |                      |        |                    |        |

| R/W-0                             | R/W-0  | R/W-0            | R/W-0                              | R/W-0                | R/W-0  | R/W-0              | R/W-0  |

| DIFF11                            | SIGN11 | DIFF10           | SIGN10                             | DIFF9                | SIGN9  | DIFF8              | SIGN8  |

| bit 7                             |        |                  |                                    | -<br>-               |        | •                  | bit 0  |

|                                   |        |                  |                                    |                      |        |                    |        |

| Legend:                           |        |                  |                                    |                      |        |                    |        |

| R = Readable bit W = Writable bit |        | bit              | U = Unimplemented bit, read as '0' |                      |        |                    |        |

| -n = Value at POR                 |        | '1' = Bit is set |                                    | '0' = Bit is cleared |        | x = Bit is unknown |        |

bit 15-1(odd) DIFF<15:8>: Differential-Mode for Corresponding Analog Inputs bits

1 = Channel is differential

0 = Channel is single-ended

bit 14-0 (even) SIGN<15:8>: Output Data Sign for Corresponding Analog Inputs bits

- 1 = Channel output data is signed

- 0 = Channel output data is unsigned

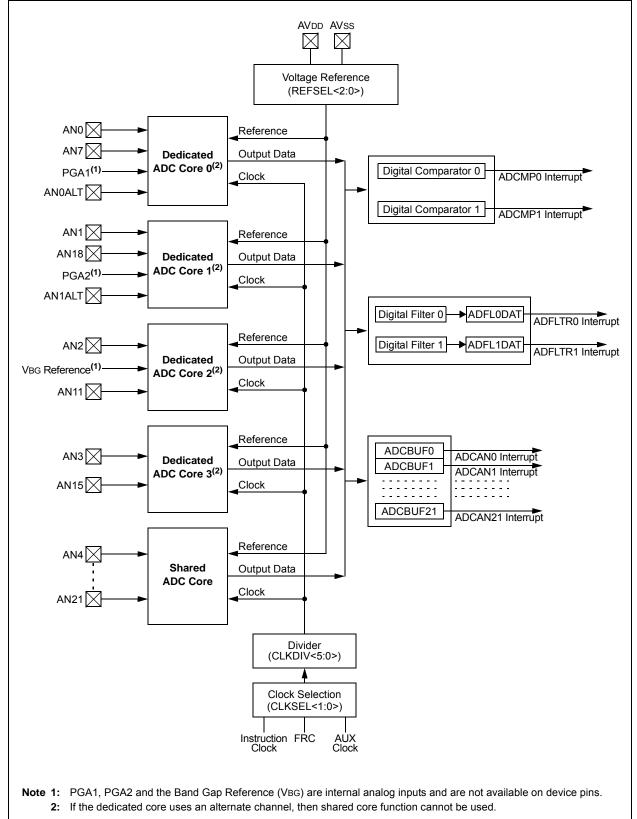

### 25.0 PROGRAMMABLE GAIN AMPLIFIER (PGA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/ 80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Programmable Gain Amplifier (PGA)" (DS70005146) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGS70X/80X family devices have two Programmable Gain Amplifiers (PGA1, PGA2). The PGA is an op amp-based, non-inverting amplifier with user-programmable gains. The output of the PGA can be connected to a number of dedicated Sampleand-Hold inputs of the Analog-to-Digital Converter and/ or to the high-speed analog comparator module. The PGA has five selectable gains and may be used as a ground referenced amplifier (single-ended) or used with an independent ground reference point.

Key features of the PGA module include:

- Single-Ended or Independent Ground Reference

- Selectable Gains: 4x, 8x, 16x, 32x and 64x

- High Gain Bandwidth

- Rail-to-Rail Output Voltage

- Wide Input Voltage Range

#### 25.2 PGA Resources

Many useful resources are provided on the main product page of the Microchip website for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 25.2.1 KEY RESOURCES

- "Programmable Gain Amplifier (PGA)" (DS70005146) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 25-1: PGAxCON: PGAx CONTROL REGISTER

| R/W-0         | R/W-0                                                   | R/W-0                                          | R/W-0  | R/W-0                              | R/W-0            | R/W-0    | R/W-0  |  |  |  |

|---------------|---------------------------------------------------------|------------------------------------------------|--------|------------------------------------|------------------|----------|--------|--|--|--|

| PGAEN         | PGAOEN                                                  | SELPI2                                         | SELPI1 | SELPI0                             | SELNI2           | SELNI1   | SELNI0 |  |  |  |

| bit 15        |                                                         |                                                |        |                                    |                  | <u>.</u> | bit 8  |  |  |  |

|               |                                                         |                                                |        |                                    |                  |          |        |  |  |  |

| U-0           | U-0                                                     | U-0                                            | U-0    | U-0                                | R/W-0            | R/W-0    | R/W-0  |  |  |  |

| _             | _                                                       | _                                              | _      | _                                  | GAIN2            | GAIN1    | GAIN0  |  |  |  |

| bit 7         |                                                         | •                                              |        |                                    |                  | -        | bit C  |  |  |  |

|               |                                                         |                                                |        |                                    |                  |          |        |  |  |  |

| Legend:       |                                                         |                                                |        |                                    |                  |          |        |  |  |  |

| R = Readabl   | e bit                                                   | W = Writable                                   | bit    | U = Unimpler                       | mented bit, read | 1 as '0' |        |  |  |  |

| -n = Value at | t POR                                                   | '1' = Bit is set                               | t      | '0' = Bit is cleared x = Bit is ur |                  |          | nown   |  |  |  |

|               |                                                         |                                                |        |                                    |                  |          |        |  |  |  |

| bit 15        | PGAEN: PGA                                              | PGAEN: PGAx Enable bit                         |        |                                    |                  |          |        |  |  |  |

|               | 1 = PGAx module is enabled                              |                                                |        |                                    |                  |          |        |  |  |  |

|               | 0 = PGAx module is disabled (reduces power consumption) |                                                |        |                                    |                  |          |        |  |  |  |

| bit 14        | PGAOEN: PGAx Output Enable bit                          |                                                |        |                                    |                  |          |        |  |  |  |

|               | 1 = PGAx output is connected to the DACOUTx pin         |                                                |        |                                    |                  |          |        |  |  |  |

|               | 0 = PGAx output is not connected to the DACOUTx pin     |                                                |        |                                    |                  |          |        |  |  |  |

| bit 13-11     | SELPI<2:0>:                                             | SELPI<2:0>: PGAx Positive Input Selection bits |        |                                    |                  |          |        |  |  |  |

|               | 111 = Reserved                                          |                                                |        |                                    |                  |          |        |  |  |  |

|               | 110 = Reserved                                          |                                                |        |                                    |                  |          |        |  |  |  |

|               | 101 = Reserved                                          |                                                |        |                                    |                  |          |        |  |  |  |

|               | 100 = Reserved                                          |                                                |        |                                    |                  |          |        |  |  |  |

|               | 011 = PGAxF                                             | -                                              |        |                                    |                  |          |        |  |  |  |

|               | 010 = PGAxF                                             | >3                                             |        |                                    |                  |          |        |  |  |  |

|               |                                                         | 22                                             |        |                                    |                  |          |        |  |  |  |

001 = PGAxP2 000 = PGAxP1

### bit 10-8 **SELNI<2:0>:** PGAx Negative Input Selection bits

- 111 = Reserved 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = Ground (Single-Ended mode)

- 010 = PGAxN3

- 001 = PGAxN2

- 000 = Ground (Single-Ended mode)

- bit 7-3 Unimplemented: Read as '0'

| DC CHARACTERISTICS |        |                                                             | (unles                          | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |   |                                                                                                                                                                                                   |  |  |

|--------------------|--------|-------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param.             | Symbol | Characteristic                                              | Min. Typ. Max. Units Conditions |                                                                                                                                                                                                                                                                                       |     |   |                                                                                                                                                                                                   |  |  |

| DO10 Vol           |        | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    | -                               | _                                                                                                                                                                                                                                                                                     | 0.4 | V | $V_{DD} = 3.3V$ ,<br>$I_{OL} \le 6 \text{ mA}, -40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C},$<br>$I_{OL} \le 5 \text{ mA}, +85^{\circ}\text{C} < \text{Ta} \le +125^{\circ}\text{C}$ |  |  |

|                    |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | _                               | _                                                                                                                                                                                                                                                                                     | 0.4 | V | $V_{DD} = 3.3V$ ,<br>$I_{OL} \le 12 \text{ mA}, -40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C},$<br>$I_{OL} \le 8 \text{ mA}, +85^{\circ}\text{C} < T_{A} \le +125^{\circ}\text{C}$        |  |  |

| DO20               | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                             |                                                                                                                                                                                                                                                                                       | —   | V | IOH ≥ -10 mA, VDD = 3.3V                                                                                                                                                                          |  |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                             |                                                                                                                                                                                                                                                                                       | —   | V | IOH ≥ -15 mA, VDD = 3.3V                                                                                                                                                                          |  |  |

| DO20A              | Von1   | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 1.5 <sup>(1)</sup>              |                                                                                                                                                                                                                                                                                       |     | V | IOH ≥ -14 mA, VDD = 3.3V                                                                                                                                                                          |  |  |

|                    |        |                                                             | 2.0 <sup>(1)</sup>              | _                                                                                                                                                                                                                                                                                     |     |   | IOH ≥ -12 mA, VDD = 3.3V                                                                                                                                                                          |  |  |

|                    |        |                                                             | 3.0 <sup>(1)</sup>              |                                                                                                                                                                                                                                                                                       |     |   | ІОн ≥ -7 mA, VDD = 3.3V                                                                                                                                                                           |  |  |

|                    |        | Output High Voltage                                         | 1.5 <sup>(1)</sup>              |                                                                                                                                                                                                                                                                                       |     | V | IOH ≥ -22 mA, VDD = 3.3V                                                                                                                                                                          |  |  |

|                    |        | 8x Source Driver Pins <sup>(3)</sup>                        | 2.0 <sup>(1)</sup>              |                                                                                                                                                                                                                                                                                       |     |   | ІОН ≥ -18 mA, VDD = 3.3V                                                                                                                                                                          |  |  |

|                    |        |                                                             | 3.0 <sup>(1)</sup>              | _                                                                                                                                                                                                                                                                                     |     |   | IOH ≥ -10 mA, VDD = 3.3V                                                                                                                                                                          |  |  |

#### TABLE 30-12: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized but not tested.

2: Includes RA0-RA2, RB0-RB1, RB9, RC1-RC2, RC9-RC10, RC12, RD7, RD8, RE4-RE5, RE8-RE9 and RE12-RE13 pins.

3: Includes all I/O pins that are not 4x driver pins (see Note 2).

#### TABLE 30-13: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                            | $ \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array} $ |      |      |       |                     |  |  |

|--------------------|--------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|---------------------|--|--|

| Param<br>No.       | Symbol | Characteristic                             | Min. <sup>(2)</sup>                                                                                                                                                                                                                                                                         | Тур. | Max. | Units | Conditions          |  |  |

| BO10               | VBOR   | BOR Event on VDD Transition<br>High-to-Low | 2.65                                                                                                                                                                                                                                                                                        | _    | 2.95 | V     | VDD (Notes 2 and 3) |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, PGAs and comparators) may have degraded performance.

**2:** Parameters are for design guidance only and are not tested in manufacturing.

**3:** The VBOR specification is relative to VDD.

#### TABLE 30-20: INTERNAL FRC ACCURACY

| АС СНА                      | RACTERISTICS           | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |          |             |       |                                           |                |  |  |  |

|-----------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|-------|-------------------------------------------|----------------|--|--|--|

| Param<br>No. Characteristic |                        | Min.                                                                                                                                                                                                                                                                         | Тур.     | Max.        | Units | Conditions                                |                |  |  |  |

| Internal                    | FRC Accuracy @ FRC Fre | equency =                                                                                                                                                                                                                                                                    | 7.37 MHz | <b>(</b> 1) |       |                                           |                |  |  |  |

| F20a FRC                    |                        | -2                                                                                                                                                                                                                                                                           | 0.5      | +2          | %     | $-40^\circ C \le T A \le -10^\circ C$     | VDD = 3.0-3.6V |  |  |  |

|                             |                        |                                                                                                                                                                                                                                                                              | 0.5      | +0.9        | %     | $-10^{\circ}C \le TA \le +85^{\circ}C$    | VDD = 3.0-3.6V |  |  |  |

| F20b                        | FRC                    | -2                                                                                                                                                                                                                                                                           | 1        | +2          | %     | $+85^{\circ}C \leq TA \leq +125^{\circ}C$ | VDD = 3.0-3.6V |  |  |  |

**Note 1:** Frequency is calibrated at +25°C and 3.3V. TUNx bits can be used to compensate for temperature drift.

### TABLE 30-21: INTERNAL LPRC ACCURACY

| AC CH                       | ARACTERISTICS               | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq T_A \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq T_A \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                                           |                |  |  |  |

|-----------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------------------------------------------|----------------|--|--|--|

| Param<br>No. Characteristic |                             | Min.                                                                                                                                                                                                                                                                           | Тур. | Max. | Units | Conditions                                |                |  |  |  |

| LPRC                        | @ 32.768 kHz <sup>(1)</sup> |                                                                                                                                                                                                                                                                                |      |      |       |                                           |                |  |  |  |

| F21a                        | LPRC                        | -30                                                                                                                                                                                                                                                                            | _    | +30  | %     | $-40^{\circ}C \le TA \le -10^{\circ}C$    | VDD = 3.0-3.6V |  |  |  |

|                             |                             | -20                                                                                                                                                                                                                                                                            | _    | +20  | %     | $-10^{\circ}C \le TA \le +85^{\circ}C$    | VDD = 3.0-3.6V |  |  |  |

| F21b                        | LPRC                        | -30                                                                                                                                                                                                                                                                            | —    | +30  | %     | $+85^{\circ}C \leq TA \leq +125^{\circ}C$ | VDD = 3.0-3.6V |  |  |  |

Note 1: This is the change of the LPRC frequency as VDD changes.

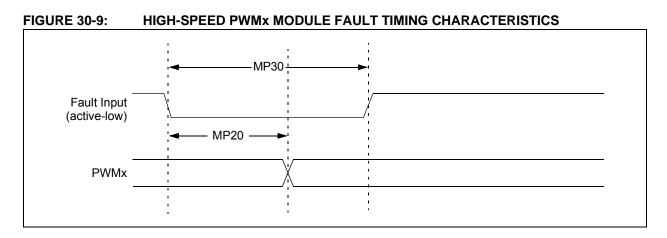

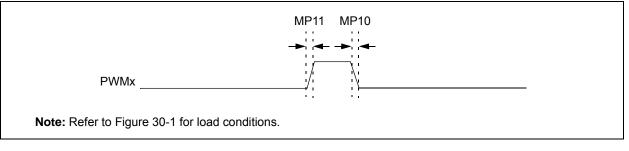

#### FIGURE 30-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 30-30: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |   |    |    |                    |  |

|--------------------|--------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|----|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>       | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                                                     |   |    |    |                    |  |

| MP10               | TFPWM  | PWMx Output Fall Time               | _                                                                                                                                                                                                                                                                                   | _ | —  | ns | See Parameter DO32 |  |

| MP11               | TRPWM  | PWMx Output Rise Time               | —                                                                                                                                                                                                                                                                                   | _ | —  | ns | See Parameter DO31 |  |

| MP20               | Tfd    | Fault Input ↓ to PWMx<br>I/O Change | _                                                                                                                                                                                                                                                                                   | _ | 15 | ns |                    |  |

| MP30               | Tfh    | Fault Input Pulse Width             | 15                                                                                                                                                                                                                                                                                  | — | —  | ns |                    |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

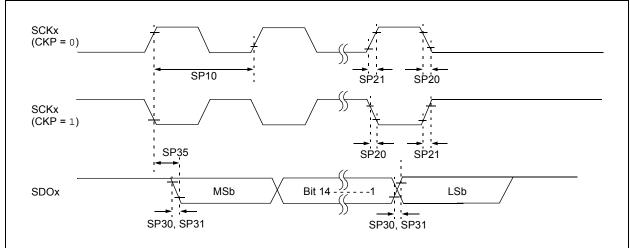

#### TABLE 30-31: SPI1, SPI2 AND SPI3 MAXIMUM DATA/CLOCK RATE SUMMARY<sup>(1)</sup>

| AC CHARA             | CTERISTICS                               |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |  |

| 15 MHz               | Table 30-32                              | _                                           | _                                                     | 0,1 | 0,1 | 0,1 |  |  |

| 9 MHz                | _                                        | Table 30-33                                 | —                                                     | 1   | 0,1 | 1   |  |  |

| 9 MHz                | —                                        | Table 30-34                                 | —                                                     | 0   | 0,1 | 1   |  |  |

| 15 MHz               | —                                        | —                                           | Table 30-35                                           | 1   | 0   | 0   |  |  |

| 11 MHz               | _                                        | —                                           | Table 30-36                                           | 1   | 1   | 0   |  |  |

| 15 MHz               | _                                        | —                                           | Table 30-37                                           | 0   | 1   | 0   |  |  |

| 11 MHz               | —                                        | —                                           | Table 30-38                                           | 0   | 0   | 0   |  |  |

**Note 1:** Pertaining to SPI3: dsPIC33EPXXXGS702, dsPIC33EPXXXGSX04 and dsPIC33EPXXXGSX05 devices with a remappable SCK3 pin.

### FIGURE 30-11: SPI1, SPI2 AND SPI3 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS<sup>(1,2)</sup>

Note 1: Pertaining to SPI3: dsPIC33EPXXXGS702, dsPIC33EPXXXGSX04 and dsPIC33EPXXXGSX05 devices with a remappable SCK3 pin.

**2:** Refer to Figure 30-1 for load conditions.

#### TABLE 30-57: PGAx MODULE SPECIFICATIONS

| AC/DC CHARACTERISTICS |        |                                                |            |            |             |            |        |                                                                |  |  |

|-----------------------|--------|------------------------------------------------|------------|------------|-------------|------------|--------|----------------------------------------------------------------|--|--|

| Param<br>No.          | Symbol | Characteris                                    | tic        | Min.       | Тур.        | Max.       | Units  | Comments                                                       |  |  |

| PA01                  | Vin    | Input Voltage Rang                             | е          | AVss - 0.3 | —           | AVDD + 0.3 | V      |                                                                |  |  |

| PA02                  | Vсм    | Common-Mode Input<br>Voltage Range             |            | AVss       | —           | AVDD - 1.6 | V      |                                                                |  |  |

| PA03                  | Vos    | Input Offset Voltage                           | 9          | -10        | _           | 10         | mV     |                                                                |  |  |

| PA04                  | Vos    | Input Offset Voltage Drift<br>with Temperature |            | _          | ±15         | —          | µV/∘C  |                                                                |  |  |

| PA05                  | Rin+   | Input Impedance of<br>Positive Input           |            | _          | >1M    7 pF | —          | Ω   pF |                                                                |  |  |

| PA06                  | Rin-   | Input Impedance of<br>Negative Input           |            | —          | 10K    7 pF | _          | Ω∥ pF  |                                                                |  |  |

| PA07                  | Gerr   | Gain Error                                     |            | -2         | —           | 2          | %      | Gain = 4x, 8x                                                  |  |  |

|                       |        |                                                |            | -3         | —           | 3          | %      | Gain = 16x                                                     |  |  |

|                       |        |                                                |            | -4         | —           | 4          | %      | Gain = 32x, 64x                                                |  |  |

| PA08                  | Lerr   | Gain Nonlinearity Error                        |            | _          | —           | 0.5        | %      | % of full scale,<br>Gain = 16x                                 |  |  |

| PA09                  | IDD    | Current Consumption                            |            | _          | 2.0         | _          | mA     | Module is enabled with<br>a 2-volt P-P output<br>voltage swing |  |  |

| PA10a                 | BW     | Small Signal                                   | G = 4x     | _          | 10          | _          | MHz    |                                                                |  |  |

| PA10b                 |        | Bandwidth (-3 dB)                              | G = 8x     | _          | 5           | —          | MHz    |                                                                |  |  |

| PA10c                 |        |                                                | G = 16x    | -          | 2.5         | —          | MHz    |                                                                |  |  |

| PA10d                 |        |                                                | G = 32x    | _          | 1.25        | —          | MHz    |                                                                |  |  |

| PA10e                 |        |                                                | G = 64x    | _          | 0.625       | _          | MHz    |                                                                |  |  |

| PA11                  | OST    | Output Settling Time to 1% of Final Value      |            | —          | 0.4         | —          | μs     | Gain = 16x, 100 mV<br>input step change                        |  |  |

| PA12                  | SR     | Output Slew Rate                               |            | _          | 40          | _          | V/µs   | Gain = 16x                                                     |  |  |

| PA13                  | TGSEL  | Gain Selection Tim                             | e          |            | 1           |            | μs     |                                                                |  |  |