Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| roduct Status             | Active                                                                           |

| Core Processor            | dsPIC                                                                            |

| Core Size                 | 16-Bit                                                                           |

| peed                      | 70 MIPs                                                                          |

| onnectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| eripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| lumber of I/O             | 67                                                                               |

| rogram Memory Size        | 64KB (64K x 8)                                                                   |

| ogram Memory Type         | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AM Size                   | 8K x 8                                                                           |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| ata Converters            | A/D 22x12b; D/A 2x12b                                                            |

| scillator Type            | Internal                                                                         |

| perating Temperature      | -40°C ~ 85°C (TA)                                                                |

| ounting Type              | Surface Mount                                                                    |

| ackage / Case             | 80-TQFP                                                                          |

| upplier Device Package    | 80-TQFP (12x12)                                                                  |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs708t-i-pt |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name <sup>(1)</sup>                   | Pin<br>Type | Buffer<br>Type | PPS                | Description                                               |  |

|-------------------------------------------|-------------|----------------|--------------------|-----------------------------------------------------------|--|

| U2CTS                                     | ı           | ST             | Yes                | UART2 Clear-to-Send.                                      |  |

| U2RTS                                     | 0           | _              | Yes                | UART2 Ready-to-Send.                                      |  |

| U2RX                                      | - 1         | ST             | Yes                | UART2 receive.                                            |  |

| U2TX                                      | 0           | _              | Yes                | UART2 transmit.                                           |  |

| BCLK2                                     | 0           | ST             | Yes                | UART2 IrDA baud clock output.                             |  |

| SCK1                                      | I/O         | ST             | Yes                | Synchronous serial clock input/output for SPI1.           |  |

| SDI1                                      | I           | ST             | Yes                | SPI1 data in.                                             |  |

| SDO1                                      | 0           |                | Yes                | SPI1 data out.                                            |  |

| SS1                                       | I/O         | ST             | Yes                | SPI1 slave synchronization or frame pulse I/O.            |  |

| SCK2                                      | I/O         | ST             | Yes                | Synchronous serial clock input/output for SPI2.           |  |

| SDI2                                      |             | ST             | Yes                | SPI2 data in.                                             |  |

| SDO2                                      | 0           | <br>o          | Yes                | SPI2 data out.                                            |  |

| SS2                                       | I/O         | ST             | Yes                | SPI2 slave synchronization or frame pulse I/O.            |  |

| SCK3                                      | I/O         | ST             | Yes <sup>(3)</sup> | Synchronous serial clock input/output for SPI3.           |  |

| SDI3                                      |             | ST             | Yes                | SPI3 data in.                                             |  |

| SDO3                                      | 0           | <br>OT         | Yes                | SPI3 data out.                                            |  |

| SS3                                       | I/O         | ST             | Yes                | SPI3 slave synchronization or frame pulse I/O.            |  |

| SCL1                                      | I/O         | ST             | No                 | Synchronous serial clock input/output for I2C1.           |  |

| SDA1                                      | I/O         | ST             | No                 | Synchronous serial data input/output for I2C1.            |  |

| ASCL1                                     | 1/0         | ST             | No                 | Alternate synchronous serial clock input/output for I2C1. |  |

| ASDA1                                     | I/O         | ST             | No                 | Alternate synchronous serial data input/output for I2C1.  |  |

| SCL2                                      | I/O         | ST             | No                 | Synchronous serial clock input/output for I2C2.           |  |

| SDA2                                      | I/O         | ST             | No                 | Synchronous serial data input/output for I2C2.            |  |

| ASCL2                                     | 1/0         | ST             | No                 | Alternate synchronous serial clock input/output for I2C2. |  |

| ASDA2                                     | I/O         | ST             | No                 | Alternate synchronous serial data input/output for I2C2.  |  |

| TMS                                       | <br>        | ST             | No                 | JTAG Test mode select pin.                                |  |

| TCK                                       |             | ST             | No                 | JTAG test clock input pin.                                |  |

| TDI                                       |             | ST             | No                 | JTAG test data input pin.                                 |  |

| TDO                                       | 0           |                | No                 | JTAG test data output pin.                                |  |

| FLT1-FLT8                                 |             | ST             | Yes                | PWM Fault Inputs 1 through 8.                             |  |

| FLT9-FLT12                                | 1           | ST             | No                 | PWM Fault Inputs 9 through 12.                            |  |

| PWM1L-PWM3L                               | 0           | _              | No                 | PWM Low Outputs 1 through 3.                              |  |

| PWM1H-PWM3H<br>PWM4L-PWM8L <sup>(2)</sup> | 0           |                | No<br>Yes          |                                                           |  |

| PWM4H-PWM8H <sup>(2)</sup>                | 0           | _              | Yes                | PWM High Outputs 4 through 8.                             |  |

| SYNCI1, SYNCI2                            | Ī           | ST             | Yes                | PWM Synchronization Inputs 1 and 2.                       |  |

| SYNCO1, SYNCO2                            | Ó           | _              | Yes                | PWM Synchronization Outputs 1 and 2.                      |  |

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

P = Power

ST = Schmitt Trigger input with CMOS levels

O = Output

I = Input

PPS = Peripheral Pin Select

TTL = TTL input buffer

- 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

- 2: PWM4H/L through PWM8H/L are fixed on dsPIC33EPXXXGS708/808 devices. PWM4H/L through PWM6H/L are fixed on dsPIC33EPXXXGS706/806 devices.

- **3:** The SCK3 pin is fixed on dsPIC33EPXXXGS706/806 and dsPIC33EPXXXGS708/808 devices.

- 4: PPS is available on dsPIC33EPXXXGS702 devices only.

TABLE 4-8: SFR BLOCK 600h

| Register  | Address | All Resets        | Register | Address | All Resets        | Register | Address | All Resets       |

|-----------|---------|-------------------|----------|---------|-------------------|----------|---------|------------------|

| SPI       |         |                   | RPOR8    | 678     | 0000000000000000  | RPINR7   | 6AE     | 0000000000000000 |

| SPI3CON1L | 600     | 00000000000000000 | RPOR9    | 67A     | 00000000000000000 | RPINR8   | 6B0     | 0000000000000000 |

| SPI3CON1H | 602     | 00000000000000000 | RPOR10   | 67C     | 00000000000000000 | RPINR11  | 6B6     | 0000000000000000 |

| SPI3CON2L | 604     | 0000000000000000  | RPOR11   | 67E     | 00000000000000000 | RPINR12  | 6B8     | 0000000000000000 |

| SPI3CON2H | 606     | 00000000000000000 | RPOR12   | 680     | 0000000000000000  | RPINR13  | 6BA     | 0000000000000000 |

| SPI3STATL | 608     | 000000000101000   | RPOR13   | 682     | 0000000000000000  | RPINR18  | 6C4     | 0000000000000000 |

| SPI3STATH | 60A     | 00000000000000000 | RPOR14   | 684     | 0000000000000000  | RPINR19  | 6C6     | 0000000000000000 |

| SPI3BUFL  | 60C     | 00000000000000000 | RPOR15   | 686     | 0000000000000000  | RPINR20  | 6C8     | 0000000000000000 |

| SPI3BUFH  | 60E     | 00000000000000000 | RPOR17   | 68A     | 0000000000000000  | RPINR21  | 6CA     | 0000000000000000 |

| SPI3BRGL  | 610     | 000xxxxxxxxxxxxx  | RPOR18   | 68C     | 0000000000000000  | RPINR22  | 6CC     | 0000000000000000 |

| SPI3BRGH  | 612     | 00000000000000000 | RPOR19   | 68E     | 0000000000000000  | RPINR23  | 6CE     | 0000000000000000 |

| SPI3IMSKL | 614     | 00000000000000000 | RPOR20   | 690     | 00000000000000000 | RPINR26  | 6D4     | 0000000000000000 |

| SPI3IMSKH | 616     | 00000000000000000 | RPOR21   | 692     | 0000000000000000  | RPINR29  | 6DA     | 0000000000000000 |

| SPI3URDTL | 618     | 00000000000000000 | RPOR22   | 694     | 00000000000000000 | RPINR30  | 6DC     | 0000000000000000 |

| SPI3URDTH | 61A     | 00000000000000000 | RPOR23   | 696     | 0000000000000000  | RPINR37  | 6EA     | 0000000000000000 |

| RPOR0     | 668     | 00000000000000000 | RPOR24   | 698     | 0000000000000000  | RPINR38  | 6EC     | 0000000000000000 |

| RPOR1     | 66A     | 00000000000000000 | RPOR25   | 69A     | 0000000000000000  | RPINR42  | 6F4     | 0000000000000000 |

| RPOR2     | 66C     | 00000000000000000 | RPOR26   | 69C     | 0000000000000000  | RPINR43  | 6F6     | 0000000000000000 |

| RPOR3     | 66E     | 00000000000000000 | RPINR0   | 6A0     | 00000000000000000 | RPINR45  | 6FA     | 0000000000000000 |

| RPOR4     | 670     | 00000000000000000 | RPINR1   | 6A2     | 00000000000000000 | RPINR46  | 6FC     | 0000000000000000 |

| RPOR5     | 672     | 00000000000000000 | RPINR2   | 6A4     | 00000000000000000 |          |         |                  |

| RPOR6     | 674     | 00000000000000000 | RPINR3   | 6A6     | 00000000000000000 |          |         |                  |

**Legend:** x = unknown or indeterminate value. Address values are in hexadecimal. Reset values are in binary.

TABLE 4-9: SFR BLOCK 700h

| Register       | Address                        | All Resets        | Register      | Address          | All Resets        | Register   | Address       | All Resets     |

|----------------|--------------------------------|-------------------|---------------|------------------|-------------------|------------|---------------|----------------|

| NVM            |                                |                   | C2INTF        | 78A              | 0000000000000000  | C2RXF1SID  | 7C4           | xxxxxxxxxxxx   |

| NVMCON         | 728                            | 00000000000000000 | C2INTE        | 78C              | 0000000000000000  | C2RXF1EID  | 7C6           | xxxxxxxxxxxxx  |

| NVMADR         | 72A                            | 00000000000000000 | C2EC          | 78E              | 00000000000000000 | C2RXF2SID  | 7C8           | xxxxxxxxxxxxx  |

| NVMADRU        | 72C                            | 00000000000000000 | C2CFG1        | 790              | 00000000000000000 | C2RXF2EID  | 7CA           | xxxxxxxxxxxxx  |

| NVMKEY         | 72E                            | 00000000000000000 | C2CFG2        | 792              | 0x000xxxxxxxxxxx  | C2RXF3SID  | 7CC           | xxxxxxxxxxxxx  |

| NVMSRCADR      | 730                            | 00000000000000000 | C2FEN1        | 794              | 1111111111111111  | C2RXF3EID  | 7CE           | xxxxxxxxxxxxx  |

| NVMSRCADRH     | 732                            | 00000000000000000 | C2FMSKSEL1    | 798              | 00000000000000000 | C2RXF4SID  | 7D0           | xxxxxxxxxxxxx  |

| System Control |                                | C2FMSKSEL2        | 79A           | 0000000000000000 | C2RXF4EID         | 7D2        | xxxxxxxxxxxxx |                |

| RCON           | 740                            | 0x00x0x01x0xxxxx  | CAN (WIN (C1  | CTR1<0>)         | = 0)              | C2RXF5SID  | 7D4           | xxxxxxxxxxxxx  |

| OSCCON         | 742                            | 00000000000000000 | C2RXFUL1      | 7A0              | 00000000000000000 | C2RXF5EID  | 7D6           | xxxxxxxxxxxxx  |

| CLKDIV         | 744                            | 00000000000000000 | C2RXFUL2      | 7A2              | 00000000000000000 | C2RXF6SID  | 7D8           | xxxxxxxxxxxxx  |

| PLLFBD         | 746                            | 00000000000000000 | C2RXOVF1      | 7A8              | 00000000000000000 | C2RXF6EID  | 7DA           | xxxxxxxxxxxxx  |

| OSCTUN         | 748                            | 00000000000000000 | C2RXOVF2      | 7AA              | 00000000000000000 | C2RXF7SID  | 7DC           | xxxxxxxxxxxxx  |

| LFSR           | 74C                            | 00000000000000000 | C2TR01CON     | 7B0              | 00000000000000000 | C2RXF7EID  | 7DE           | xxxxxxxxxxxxx  |

| REFOCON        | 74E                            | 00000000000000000 | C2TR23CON     | 7B2              | 0000000000000000  | C2RXF8SID  | 7E0           | xxxxxxxxxxxxx  |

| ACLKCON        | 750                            | 00000000000000000 | C2TR45CON     | 7B4              | 00000000000000000 | C2RXF8EID  | 7E2           | xxxxxxxxxxxxx  |

| PMD            |                                |                   | C2TR67CON     | 7B6              | xxxxxxxxxxxxx     | C2RXF9SID  | 7E4           | xxxxxxxxxxxxx  |

| PMD1           | 760                            | 00000000000000000 | C2RXD         | 7C0              | xxxxxxxxxxxxx     | C2RXF9EID  | 7E6           | xxxxxxxxxxxxx  |

| PMD2           | 762                            | 00000000000000000 | C2TXD         | 7C2              | xxxxxxxxxxxxx     | C2RXF10SID | 7E8           | xxxxxxxxxxxxx  |

| PMD3           | 764                            | 00000000000000000 | CAN (WIN (C10 | CTR1<0>):        | = 1)              | C2RXF10EID | 7EA           | xxxxxxxxxxxxx  |

| PMD4           | 766                            | 00000000000000000 | C2BUFPNT1     | 7A0              | 00000000000000000 | C2RXF11SID | 7EC           | xxxxxxxxxxxxxx |

| PMD6           | 76A                            | 00000000000000000 | C2BUFPNT2     | 7A2              | 00000000000000000 | C2RXF11EID | 7EE           | xxxxxxxxxxxxxx |

| PMD7           | 76C                            | 0000000000000000  | C2BUFPNT3     | 7A4              | 00000000000000000 | C2RXF12SID | 7F0           | xxxxxxxxxxxxx  |

| PMD8           | 76E                            | 00000000000000000 | C2BUFPNT4     | 7A6              | 00000000000000000 | C2RXF12EID | 7F2           | xxxxxxxxxxxxx  |

| CAN (WIN (C1C  | CAN (WIN (C1CTR1<0>) = 0 or 1) |                   | C2RXM0SID     | 7B0              | xxxxxxxxxxxxx     | C2RXF13SID | 7F4           | xxxxxxxxxxxxx  |

| C2CTRL1        | 780                            | 0000010010000000  | C2RXM0EID     | 7B2              | xxxxxxxxxxxxx     | C2RXF13EID | 7F6           | xxxxxxxxxxxxx  |

| C2CTRL2        | 782                            | 00000000000000000 | C2RXM1SID     | 7B4              | xxxxxxxxxxxxx     | C2RXF14SID | 7F8           | xxxxxxxxxxxxxx |

| C2VEC          | 784                            | 000000001000000   | C2RXM1EID     | 7B6              | xxxxxxxxxxxxx     | C2RXF14EID | 7FA           | xxxxxxxxxxxxx  |

| C2FCTRL        | 786                            | 00000000000000000 | C2RXM2SID     | 7B8              | xxxxxxxxxxxxx     | C2RXF15SID | 7FC           | xxxxxxxxxxxxxx |

| C2FIFO         | 788                            | 00000000000000000 | C2RXM2EID     | 7BA              | xxxxxxxxxxxxx     | C2RXF15EID | 7FE           | xxxxxxxxxxxxx  |

**Legend:** x = unknown or indeterminate value. Address values are in hexadecimal. Reset values are in binary.

### REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   |     | _   | _   | _   | NAE   |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | U-0 | U-0 | U-0 | R/W-0 |

|-------|-----|-----|-------|-----|-----|-----|-------|

| _     | _   | _   | DOOVR | _   | _   | _   | APLL  |

| bit 7 |     |     |       |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-9 **Unimplemented:** Read as '0'

bit 8 NAE: NVM Address Error Soft Trap Status bit

1 = NVM address error soft trap has occurred

0 = NVM address error soft trap has not occurred

bit 7-5 **Unimplemented:** Read as '0'

bit 4 DOOVR: DO Stack Overflow Soft Trap Status bit

1 = DO stack overflow soft trap has occurred

0 = DO stack overflow soft trap has not occurred

bit 3-1 **Unimplemented:** Read as '0'

bit 0 APLL: Auxiliary PLL Loss of Lock Soft Trap Status bit

1 = APLL lock soft trap has occurred

0 = APLL lock soft trap has not occurred

### REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   |       |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     |     |     | -   | _   | -   | _   | SGHT  |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-1 **Unimplemented:** Read as '0'

bit 0 SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

### REGISTER 11-27: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SYNCI1R7 | SYNCI1R6 | SYNCI1R5 | SYNCI1R4 | SYNCI1R3 | SYNCI1R2 | SYNCI1R1 | SYNCI1R0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 SYNCI1R<7:0>: Assign PWM Synchronization Input 1 (SYNCI1) to the Corresponding RPn Pin bits

See Table 11-11 which contains a list of remappable inputs for the index value.

bit 7-0 **Unimplemented:** Read as '0'

### REGISTER 11-28: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SYNCI2R7 | SYNCI2R6 | SYNCI2R5 | SYNCI2R4 | SYNCI2R3 | SYNCI2R2 | SYNCI2R1 | SYNCI2R0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 SYNCI2R<7:0>: Assign PWM Synchronization Input 2 (SYNCI2) to the Corresponding RPn Pin bits

See Table 11-11 which contains a list of remappable inputs for the index value.

### REGISTER 11-39: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| U-0    | R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| _      | RP40R6 | RP40R5 | RP40R4 | RP40R3 | RP40R2 | RP40R1 | RP40R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| U-0   | R/W-0  |

|-------|--------|--------|--------|--------|--------|--------|--------|

| _     | RP39R6 | RP39R5 | RP39R4 | RP39R3 | RP39R2 | RP39R1 | RP39R0 |

| bit 7 |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 RP40R<6:0>: Peripheral Output Function is Assigned to RP40 Output Pin bits

(see Table 11-13 for peripheral function numbers)

bit 7 Unimplemented: Read as '0'

bit 6-0 RP39R<6:0>: Peripheral Output Function is Assigned to RP39 Output Pin bits

(see Table 11-13 for peripheral function numbers)

### REGISTER 11-40: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| _      | RP43R6 | RP43R5 | RP43R4 | RP43R3 | RP43R2 | RP43R1 | RP43R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| U-0   | R/W-0  |

|-------|--------|--------|--------|--------|--------|--------|--------|

| _     | RP41R6 | RP41R5 | RP41R4 | RP41R3 | RP41R2 | RP41R1 | RP41R0 |

| bit 7 |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 RP43R<6:0>: Peripheral Output Function is Assigned to RP43 Output Pin bits

(see Table 11-13 for peripheral function numbers)

bit 7 **Unimplemented:** Read as '0'

bit 6-0 RP41R<6:0>: Peripheral Output Function is Assigned to RP41 Output Pin bits

(see Table 11-13 for peripheral function numbers)

### 12.2 Timer1 Control Register

### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0              | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|-----|-------|-----|-----|-----|-----|-------|

| TON <sup>(1)</sup> | _   | TSIDL | _   | _   | _   | _   | _     |

| bit 15             |     |       |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0  | R/W-0  | U-0 | R/W-0                | R/W-0              | U-0   |

|-------|-------|--------|--------|-----|----------------------|--------------------|-------|

| _     | TGATE | TCKPS1 | TCKPS0 | _   | TSYNC <sup>(1)</sup> | TCS <sup>(1)</sup> | _     |

| bit 7 |       |        |        |     |                      |                    | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **TON:** Timer1 On bit<sup>(1)</sup>

1 = Starts 16-bit Timer1

0 = Stops 16-bit Timer1

bit 14 Unimplemented: Read as '0'

bit 13 TSIDL: Timer1 Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-7 **Unimplemented:** Read as '0'

bit 6 TGATE: Timer1 Gated Time Accumulation Enable bit

When TCS = 1: This bit is ignored. When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

bit 5-4 TCKPS<1:0>: Timer1 Input Clock Prescale Select bits

11 = 1:256

10 = 1:64

01 = 1:8

00 = 1:1

bit 3 Unimplemented: Read as '0'

bit 2 **TSYNC:** Timer1 External Clock Input Synchronization Select bit<sup>(1)</sup>

When TCS = 1:

1 = Synchronizes external clock input

0 = Does not synchronize external clock input

When TCS = 0:

This bit is ignored.

bit 1 TCS: Timer1 Clock Source Select bit<sup>(1)</sup>

1 = External clock is from pin, T1CK (on the rising edge)

0 = Internal clock (FP)

bit 0 **Unimplemented:** Read as '0'

**Note 1:** When Timer1 is enabled in External Synchronous Counter mode (TCS = 1, TSYNC = 1, TON = 1), any attempts by user software to write to the TMR1 register are ignored.

### 15.2 Output Compare Control Registers

### REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | _   | OCSIDL | OCTSEL2 | OCTSEL1 | OCTSEL0 | _   | _     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| R/W-0  | U-0 | U-0 | R/W-0, HSC | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|------------|----------|-------|-------|-------|

| ENFLTA | _   | _   | OCFLTA     | TRIGMODE | OCM2  | OCM1  | OCM0  |

| bit 7  |     |     |            |          |       |       | bit 0 |

**Legend:** HSC = Hardware Settable/Clearable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13 OCSIDL: Output Compare x Stop in Idle Mode Control bit

1 = Output Compare x halts in CPU Idle mode

0 = Output Compare x continues to operate in CPU Idle mode

bit 12-10 OCTSEL<2:0>: Output Compare x Clock Select bits

111 = Peripheral clock (FP)

110 = Reserved

101 = Reserved

100 = T1CLK is the clock source of the OCx (only the synchronous clock is supported)

011 = T5CLK is the clock source of the OCx

010 = T4CLK is the clock source of the OCx

001 = T3CLK is the clock source of the OCx

000 = T2CLK is the clock source of the OCx

bit 9-8 **Unimplemented:** Read as '0'

bit 7 ENFLTA: Fault A Input Enable bit

1 = Output Compare Fault A input (OCFA) is enabled

0 = Output Compare Fault A input (OCFA) is disabled

bit 6-5 **Unimplemented:** Read as '0'

bit 4 OCFLTA: PWM Fault A Condition Status bit

1 = PWM Fault A condition on the OCFA pin has occurred

0 = No PWM Fault A condition on the OCFA pin has occurred

bit 3 TRIGMODE: Trigger Status Mode Select bit

1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

0 = TRIGSTAT is cleared only by software

Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

### REGISTER 16-12: PWMCONx: PWMx CONTROL REGISTER (x = 1 to 8)

| R-0, HSC               | R-0, HSC              | R-0, HSC | R/W-0  | R/W-0 | R/W-0  | R/W-0              | R/W-0               |

|------------------------|-----------------------|----------|--------|-------|--------|--------------------|---------------------|

| FLTSTAT <sup>(1)</sup> | CLSTAT <sup>(1)</sup> | TRGSTAT  | FLTIEN | CLIEN | TRGIEN | ITB <sup>(3)</sup> | MDCS <sup>(3)</sup> |

| bit 15                 |                       |          |        |       |        |                    | bit 8               |

| R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0                  | R/W-0                | R/W-0 |

|-------|-------|-----|-----|-------|------------------------|----------------------|-------|

| DTC1  | DTC0  | _   | _   | MTBS  | CAM <sup>(2,3,4)</sup> | XPRES <sup>(5)</sup> | IUE   |

| bit 7 |       |     |     |       |                        |                      | bit 0 |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15 FLTSTAT: Fault Interrupt Status bit (1)

1 = Fault interrupt is pending

0 = No Fault interrupt is pending

This bit is cleared by setting FLTIEN = 0.

bit 14 CLSTAT: Current-Limit Interrupt Status bit<sup>(1)</sup>

1 = Current-limit interrupt is pending

0 = No current-limit interrupt is pending

This bit is cleared by setting CLIEN = 0.

bit 13 TRGSTAT: Trigger Interrupt Status bit

1 = Trigger interrupt is pending

0 = No trigger interrupt is pending

This bit is cleared by setting TRGIEN = 0.

bit 12 FLTIEN: Fault Interrupt Enable bit

1 = Fault interrupt is enabled

0 = Fault interrupt is disabled and the FLTSTAT bit is cleared

bit 11 CLIEN: Current-Limit Interrupt Enable bit

1 = Current-limit interrupt is enabled

0 = Current-limit interrupt is disabled and the CLSTAT bit is cleared

bit 10 TRGIEN: Trigger Interrupt Enable bit

1 = A trigger event generates an interrupt request

0 = Trigger event interrupts are disabled and the TRGSTAT bit is cleared

bit 9 **ITB:** Independent Time Base Mode bit<sup>(3)</sup>

1 = PHASEx/SPHASEx registers provide the time base period for this PWMx generator

0 = PTPER register provides timing for this PWMx generator

bit 8 MDCS: Master Duty Cycle Register Select bit (3)

1 = MDC register provides duty cycle information for this PWMx generator

0 = PDCx and SDCx registers provide duty cycle information for this PWMx generator

Note 1: Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.

- 2: The Independent Time Base mode (ITB = 1) must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.

- 3: These bits should not be changed after the PWMx is enabled by setting PTEN (PTCON<15>) = 1.

- **4:** Center-Aligned mode ignores the Least Significant 3 bits of the Duty Cycle, Phase and Dead-Time registers. The highest Center-Aligned mode resolution available is 8.32 ns with the clock prescaler set to the fastest clock.

- 5: Configure CLMOD (FCLCONx<8>) = 0 and ITB (PWMCONx<9>) = 1 to operate in External Period Reset mode.

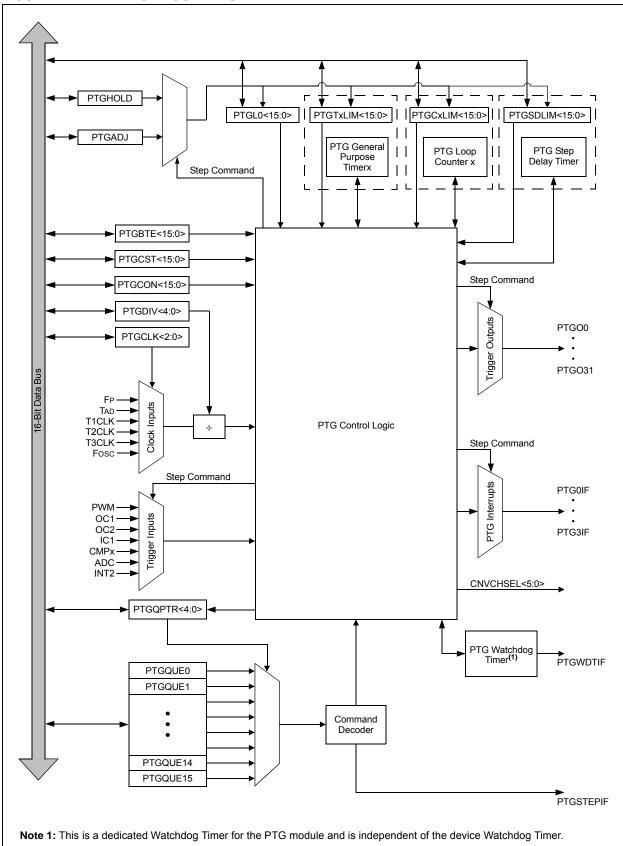

FIGURE 17-1: PTG BLOCK DIAGRAM

To set up the SPIx module for Audio mode:

- 1. Clear the SPIxBUFL and SPIxBUFH registers.

- 2. If using interrupts:

- Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- a) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with AUDEN (SPIxCON1H<15>) = 1.

- 4. Clear the SPIROV bit (SPIxSTATL<6>).

- Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

### REGISTER 18-1: SPIXCON1L: SPIX CONTROL REGISTER 1 LOW

| R/W-0  | U-0 | R/W-0   | R/W-0  | R/W-0                   | R/W-0                   | R/W-0 | R/W-0              |

|--------|-----|---------|--------|-------------------------|-------------------------|-------|--------------------|

| SPIEN  | _   | SPISIDL | DISSDO | MODE32 <sup>(1,4)</sup> | MODE16 <sup>(1,4)</sup> | SMP   | CKE <sup>(1)</sup> |

| bit 15 |     |         |        |                         |                         |       | bit 8              |

| R/W-0               | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0                 | R/W-0 | R/W-0  |

|---------------------|-------|-------|--------|--------|-----------------------|-------|--------|

| SSEN <sup>(2)</sup> | CKP   | MSTEN | DISSDI | DISSCK | MCLKEN <sup>(3)</sup> | SPIFE | ENHBUF |

| bit 7               |       |       |        |        |                       |       | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 SPIEN: SPIx On bit

1 = Enables module

0 = Turns off and resets module, disables clocks, disables interrupt event generation, allows SFR modifications

bit 14 Unimplemented: Read as '0'

bit 13 SPISIDL: SPIx Stop in Idle Mode bit

1 = Halts in CPU Idle mode

0 = Continues to operate in CPU Idle mode

bit 12 DISSDO: Disable SDOx Output Port bit

1 = SDOx pin is not used by the module; pin is controlled by port function

0 = SDOx pin is controlled by the module

bit 11-10 MODE32 and MODE16: Serial Word Length Select bits<sup>(1,4)</sup>

| MODE32 | MODE16 | AUDEN | Communication                                         |

|--------|--------|-------|-------------------------------------------------------|

| 1      | х      |       | 32-Bit                                                |

| 0      | 1      | 0     | 16-Bit                                                |

| 0      | 0      |       | 8-Bit                                                 |

| 1      | 1      |       | 24-Bit Data, 32-Bit FIFO, 32-Bit Channel/64-Bit Frame |

| 1      | 0      | 1     | 32-Bit Data, 32-Bit FIFO, 32-Bit Channel/64-Bit Frame |

| 0      | 1      | ] 1   | 16-Bit Data, 16-Bit FIFO, 32-Bit Channel/64-Bit Frame |

| 0      | 0      |       | 16-Bit FIFO, 16-Bit Channel/32-Bit Frame              |

- Note 1: When AUDEN (SPIxCON1H<15>) = 1, this module functions as if CKE = 0, regardless of its actual value.

- 2: When FRMEN = 1, SSEN is not used.

- 3: MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows FRMSYPW.

### REGISTER 19-2: I2CxCONH: I2Cx CONTROL REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| _     | PCIE  | SCIE  | BOEN  | SDAHT | SBCDE | AHEN  | DHEN  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 Unimplemented: Read as '0'

bit 6 **PCIE:** Stop Condition Interrupt Enable bit (I<sup>2</sup>C Slave mode only)

1 = Enables interrupt on detection of Stop condition

0 = Stop detection interrupts are disabled

bit 5 **SCIE:** Start Condition Interrupt Enable bit (I<sup>2</sup>C Slave mode only)

1 = Enables interrupt on detection of Start or Restart conditions

0 = Start detection interrupts are disabled

bit 4 **BOEN:** Buffer Overwrite Enable bit (I<sup>2</sup>C Slave mode only)

1 = I2CxRCV is updated and ACK is generated for a received address/data byte, ignoring the state of the I2COV only if the RBF bit = 0

0 = I2CxRCV is only updated when I2COV is clear

bit 3 SDAHT: SDAx Hold Time Selection bit

1 = Minimum of 300 ns hold time on SDAx after the falling edge of SCLx

0 = Minimum of 100 ns hold time on SDAx after the falling edge of SCLx

bit 2 **SBCDE:** Slave Mode Bus Collision Detect Enable bit (I<sup>2</sup>C Slave mode only)

1 = Enables slave bus collision interrupts

0 = Slave bus collision interrupts are disabled

If the rising edge of SCLx and SDAx is sampled low when the module is in a high state, the BCL bit is set and the bus goes Idle. This Detection mode is only valid during data and ACK transmit sequences.

bit 1 AHEN: Address Hold Enable bit (I<sup>2</sup>C Slave mode only)

1 = Following the 8th falling edge of SCLx for a matching received address byte, the SCLREL (I2CxCONL<12>) bit will be cleared and SCLx will be held low

0 = Address holding is disabled

bit 0 **DHEN:** Data Hold Enable bit (I<sup>2</sup>C Slave mode only)

1 = Following the 8th falling edge of SCLx for a received data byte, the slave hardware clears the SCLREL (I2CxCONL<12>) bit and SCLx is held low

0 = Data holding is disabled

TABLE 21-1: CLC1 MULTIPLEXER INPUT SOURCES

|          | DSx<2:0> | Signal Source           |  |  |  |  |

|----------|----------|-------------------------|--|--|--|--|

|          | 000      | CLCINA                  |  |  |  |  |

|          | 001      | System Clock            |  |  |  |  |

| Δ        | 010      | Timer1 Match            |  |  |  |  |

| 5:0      | 011      | PWM1H                   |  |  |  |  |

| DS1<2:0> | 100      | PWM5L                   |  |  |  |  |

| Δ        | 101      | High-Speed PWM Clock    |  |  |  |  |

|          | 110      | Timer2 Match            |  |  |  |  |

|          | 111      | Timer3 Match            |  |  |  |  |

|          | 000      | CLCINB                  |  |  |  |  |

|          | 001      | CLC2 Out                |  |  |  |  |

| ۸        | 010      | CMP1 Out                |  |  |  |  |

| DS2<2:0> | 011      | UART1 TX Out            |  |  |  |  |

| S2<      | 100      | ADC End-of-Conversion   |  |  |  |  |

| ă        | 101      | DMA Channel 0 Interrupt |  |  |  |  |

|          | 110      | PWM1L                   |  |  |  |  |

|          | 111      | PWM5H                   |  |  |  |  |

|          | 000      | CLCINA                  |  |  |  |  |

|          | 001      | CLC1 Out                |  |  |  |  |

| ^        | 010      | CMP2 Out                |  |  |  |  |

| 5:0      | 011      | SPI1 SDO Out            |  |  |  |  |

| DS3<2:0> | 100      | UART1 RX                |  |  |  |  |

| ă        | 101      | PWM2H                   |  |  |  |  |

|          | 110      | PWM6L                   |  |  |  |  |

|          | 111      | OCMP2                   |  |  |  |  |

|          | 000      | CLCINB                  |  |  |  |  |

|          | 001      | CLC2 Out                |  |  |  |  |

| ^        | 010      | CMP3 Out                |  |  |  |  |

| DS4<2:0> | 011      | SDI1                    |  |  |  |  |

| 84       | 100      | PTG                     |  |  |  |  |

| ă        | 101      | ECAN1                   |  |  |  |  |

|          | 110      | PWM2L                   |  |  |  |  |

|          | 111      | PWM6H                   |  |  |  |  |

### REGISTER 22-8: ADCON4H: ADC CONTROL REGISTER 4 HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| C3CHS1 | C3CHS0 | C2CHS1 | C2CHS0 | C1CHS1 | C1CHS0 | C0CHS1 | C0CHS0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-6 C3CHS<1:0>: Dedicated ADC Core 3 Input Channel Selection bits

1x = Reserved

01 = AN15 (differential negative input when DIFF3 (ADMOD0L<7>) = 1)

00 = AN3

bit 5-4 C2CHS<1:0>: Dedicated ADC Core 2 Input Channel Selection bits

11 = Reserved

10 = VREF band gap

01 = AN11 (differential negative input when DIFF2 (ADMOD0L<5>) = 1)

00 = AN2

bit 3-2 C1CHS<1:0>: Dedicated ADC Core 1 Input Channel Selection bits

11 = AN1ALT

10 = PGA2

01 = AN18 (differential negative input when DIFF1 (ADMOD0L<3>) = 1)

00 = AN1

bit 1-0 **COCHS<1:0>:** Dedicated ADC Core 0 Input Channel Selection bits

11 = AN0ALT

10 = PGA1

01 = AN7 (differential negative input when DIFF0 (ADMOD0L<1>) = 1)

00 **= ANO**

### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

### 30.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the dsPIC33EPXXXGS70X/80X family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXXGS70X/80X family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                    | 40°C to +125°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                                | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | -0.3V to +3.6V       |

| Maximum current out of Vss pin                                                    | 300 mA               |

| Maximum current into VDD pin <sup>(2)</sup>                                       | 300 mA               |

| Maximum current sunk/sourced by any 4x I/O pin                                    | 15 mA                |

| Maximum current sunk/sourced by any 8x I/O pin                                    | 25 mA                |

| Maximum current sunk by all ports <sup>(2)</sup>                                  | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those, or any other conditions above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

TABLE 30-12: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                             | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |      |      |       |                                                                                                                                                                                                                                                     |

|--------------------|--------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.             | Symbol | Characteristic                                              | Min.                                                                                                                                                                                                                                             | Тур. | Max. | Units | Conditions                                                                                                                                                                                                                                          |

| DO10               | Vol    | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    | _                                                                                                                                                                                                                                                | _    | 0.4  | V     | $\begin{aligned} &\text{VDD} = 3.3\text{V}, \\ &\text{IOL} \le 6 \text{ mA}, -40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}, \\ &\text{IOL} \le 5 \text{ mA}, +85^{\circ}\text{C} < \text{Ta} \le +125^{\circ}\text{C} \end{aligned}$    |

|                    |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | _                                                                                                                                                                                                                                                | _    | 0.4  | V     | $\begin{split} \text{VDD} &= 3.3 \text{V}, \\ \text{IOL} &\leq 12 \text{ mA}, -40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}, \\ \text{IOL} &\leq 8 \text{ mA}, +85^{\circ}\text{C} < \text{TA} \leq +125^{\circ}\text{C} \end{split}$ |

| DO20               | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                                                                                                                                                                                                                                              | _    | _    | V     | IOH ≥ -10 mA, VDD = 3.3V                                                                                                                                                                                                                            |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                                                                                                                                                                                                                                              | _    | _    | V     | IOH ≥ -15 mA, VDD = 3.3V                                                                                                                                                                                                                            |

| DO20A              | Vон1   | Output High Voltage                                         | 1.5 <sup>(1)</sup>                                                                                                                                                                                                                               | _    | _    | V     | IOH ≥ -14 mA, VDD = 3.3V                                                                                                                                                                                                                            |

|                    |        | 4x Source Driver Pins <sup>(2)</sup>                        | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                               | _    | _    |       | IOH ≥ -12 mA, VDD = 3.3V                                                                                                                                                                                                                            |

|                    |        |                                                             | 3.0 <sup>(1)</sup>                                                                                                                                                                                                                               | _    | _    |       | IOH ≥ -7 mA, VDD = 3.3V                                                                                                                                                                                                                             |

|                    |        | Output High Voltage                                         | 1.5 <sup>(1)</sup>                                                                                                                                                                                                                               | _    | _    | V     | IOH ≥ -22 mA, VDD = 3.3V                                                                                                                                                                                                                            |

|                    |        | 8x Source Driver Pins <sup>(3)</sup>                        | 2.0(1)                                                                                                                                                                                                                                           | _    | _    |       | IOH ≥ -18 mA, VDD = 3.3V                                                                                                                                                                                                                            |

|                    |        |                                                             | 3.0 <sup>(1)</sup>                                                                                                                                                                                                                               | _    | _    |       | IOH ≥ -10 mA, VDD = 3.3V                                                                                                                                                                                                                            |

- Note 1: Parameters are characterized but not tested.

- **2:** Includes RA0-RA2, RB0-RB1, RB9, RC1-RC2, RC9-RC10, RC12, RD7, RD8, RE4-RE5, RE8-RE9 and RE12-RE13 pins.

- 3: Includes all I/O pins that are not 4x driver pins (see Note 2).

### **TABLE 30-13: ELECTRICAL CHARACTERISTICS: BOR**

| DC CHAR      | ACTERIST | ICS                                     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) <sup>(1)</sup> Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |   |      |   |                     |  |

|--------------|----------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|---|---------------------|--|

| Param<br>No. | Symbol   | Characteristic                          | Min. <sup>(2)</sup> Typ. Max. Units Conditions                                                                                                                                                                                                                  |   |      |   | Conditions          |  |

| BO10         | VBOR     | BOR Event on VDD Transition High-to-Low | 2.65                                                                                                                                                                                                                                                            | ı | 2.95 | V | VDD (Notes 2 and 3) |  |

- **Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, PGAs and comparators) may have degraded performance.

- 2: Parameters are for design guidance only and are not tested in manufacturing.

- **3:** The VBOR specification is relative to VDD.

TABLE 30-37: SPI1, SPI2 AND SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING REQUIREMENTS<sup>(5)</sup>

| AC CHA | AC CHARACTERISTICS    |                                            |              | oerating<br>erwise st<br>mperatur | t <b>ated)</b><br>re -40° | C ≤ Ta ≤ | +85°C for Industrial<br>+125°C for Extended |

|--------|-----------------------|--------------------------------------------|--------------|-----------------------------------|---------------------------|----------|---------------------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>              | Min.         | Typ. <sup>(2)</sup>               | Max.                      | Units    | Conditions                                  |

| SP70   | FscP                  | Maximum SCKx Input Frequency               | _            | _                                 | 15                        | MHz      | (Note 3)                                    |

| SP72   | TscF                  | SCKx Input Fall Time                       | _            | _                                 | _                         | ns       | See Parameter DO32 (Note 4)                 |

| SP73   | TscR                  | SCKx Input Rise Time                       | _            | _                                 | _                         | ns       | See Parameter DO31 (Note 4                  |

| SP30   | TdoF                  | SDOx Data Output Fall Time                 | _            | _                                 | _                         | ns       | See Parameter DO32 (Note 4)                 |

| SP31   | TdoR                  | SDOx Data Output Rise Time                 | _            | _                                 | _                         | ns       | See Parameter DO31 (Note 4)                 |

| SP35   | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge  | _            | 6                                 | 20                        | ns       |                                             |

| SP36   | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to First SCKx Edge  | 30           | _                                 | _                         | ns       |                                             |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge | 30           | _                                 | _                         | ns       |                                             |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge  | 30           | _                                 | _                         | ns       |                                             |

| SP50   | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↑ or SCKx ↓ Input            | 120          | _                                 | _                         | ns       |                                             |

| SP51   | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance     | 10           | _                                 | 50                        | ns       | (Note 4)                                    |

| SP52   | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                      | 1.5 Tcy + 40 | _                                 | _                         | ns       | (Note 4)                                    |

- **Note 1:** These parameters are characterized, but are not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

- **5:** Pertaining to SPI3: dsPIC33EPXXXGS702, dsPIC33EPXXXGSX04 and dsPIC33EPXXXGSX05 devices with a remappable SCK3 pin.

| F                                                    |     | Input Change Notification (ICN)                    | 130  |

|------------------------------------------------------|-----|----------------------------------------------------|------|

| Filter Capacitor (CEFC) Specifications               | 377 | Instruction Addressing Modes                       | 53   |

| Flash Program Memory                                 |     | File Register Instructions                         | 53   |

| and Table Instructions                               |     | Fundamental Modes Supported                        | 53   |

| Control Registers                                    |     | MAC Instructions                                   | 54   |

| Dual Partition Flash Configuration                   |     | MCU Instructions                                   |      |

| Operations                                           |     | Move and Accumulator Instructions                  | 54   |

| Resources                                            |     | Other Instructions                                 | 54   |

| RTSP Operation                                       |     | Instruction Set Summary                            | 361  |

| Flexible Configuration                               |     | Overview                                           | 364  |

| Tiexible Corniguration                               | 547 | Symbols Used in Opcode Descriptions                | 362  |

| G                                                    |     | Instruction-Based Power-Saving Modes               | 115  |

| Getting Started Guidelines                           | 15  | Idle                                               | 116  |

| Connection Requirements                              |     | Sleep                                              | 116  |

| CPU Logic Filter Capacitor Connection (VCAP)         |     | Inter-Integrated Circuit (I <sup>2</sup> C)        | 245  |

| Decoupling Capacitors                                |     | Control Registers                                  | 247  |

| External Oscillator Pins                             |     | Resources                                          |      |

| ICSP Pins                                            |     | Inter-Integrated Circuit. See I <sup>2</sup> C.    |      |

|                                                      |     | Internet Address                                   | 474  |

| Master Clear (MCLR) Pin                              |     | Interrupt Controller                               |      |

| Oscillator Value Conditions on Start-up              |     | Alternate Interrupt Vector Table (AIVT)            | 73   |

| Targeted Applications                                |     | Control and Status Registers                       |      |

| Unused I/Os                                          | 18  | INTCON1                                            |      |

| H                                                    |     | INTCON2                                            |      |

|                                                      |     | INTCON3                                            |      |

| High-Speed Analog Comparator                         | 005 | INTCON4                                            |      |

| Applications                                         |     | INTTREG                                            |      |

| Description                                          |     | Interrupt Vector Details                           |      |

| Digital-to-Analog Comparator (DAC)                   |     | •                                                  |      |

| Features Overview                                    |     | Interrupt Vector Table (IVT)                       |      |

| Hysteresis                                           |     | Reset Sequence                                     |      |

| Pulse Stretcher and Digital Logic                    | 335 | Resources                                          |      |

| Resources                                            | 336 | Interrupts Coincident with Power Save Instructions | 116  |

| High-Speed PWM                                       |     | J                                                  |      |

| Features                                             | 187 |                                                    | 0.47 |

| Resources                                            | 188 | JTAG Boundary Scan Interface                       |      |

| Write-Protected Registers                            | 188 | JTAG Interface                                     | 357  |

| High-Speed, 12-Bit Analog-to-Digital Converter (ADC) | 273 | 1                                                  |      |

| Control Registers                                    | 276 | Landing Edge Blanking (LEB)                        | 407  |

| Features Overview                                    | 273 | Leading-Edge Blanking (LEB)                        | 187  |

| Resources                                            | 276 | LPRC Oscillator                                    |      |

|                                                      |     | Use with WDT                                       | 356  |

| l                                                    |     | M                                                  |      |

| I/O Ports                                            | 125 |                                                    | 0.4  |

| Configuring Analog/Digital Port Pins                 | 130 | Memory Organization                                |      |

| Control Registers                                    | 131 | Resources                                          |      |

| Helpful Tips                                         | 140 | Special Function Register Maps                     |      |

| Open-Drain Configuration                             | 130 | Microchip Internet Web Site                        |      |

| Parallel I/O (PIO)                                   |     | Modulo Addressing                                  |      |

| Register Maps                                        | 127 | Applicability                                      |      |

| PORTA                                                |     | Operation Example                                  |      |

| PORTB                                                |     | Start and End Address                              |      |

| PORTC                                                | 128 | W Address Register Selection                       |      |

| PORTD                                                |     | MPLAB REAL ICE In-Circuit Emulator System          | 373  |

| PORTE                                                |     | MPLAB X Integrated Development                     |      |

| Resources                                            |     | Environment Software                               | 371  |

| Write/Read Timing                                    |     | MPLINK Object Linker/MPLIB Object Librarian        | 372  |

| In-Circuit Debugger                                  |     | Multiplexer Input Sources                          |      |

| MPLAB ICD 3                                          |     | CLC1                                               | 265  |

|                                                      |     | CLC2                                               | 266  |

| PICkit 3 Programmer                                  |     | CLC3                                               | 267  |

| In-Circuit Emulation                                 |     | CLC4                                               |      |

| In-Circuit Serial Programming (ICSP)                 |     |                                                    |      |

| Input Capture                                        |     |                                                    |      |

| Control Registers                                    | 1/ŏ |                                                    |      |

| Timing Diagrams                               |     |

|-----------------------------------------------|-----|

| BOR and Master Clear Reset Characteristics    | 391 |

| CANx I/O                                      | 426 |

| External Clock                                | 388 |

| High-Speed PWMx Fault Characteristics         | 397 |

| High-Speed PWMx Module Characteristics        | 397 |

| I/O Characteristics                           |     |

| I2Cx Bus Data (Master Mode)                   | 422 |

| I2Cx Bus Data (Slave Mode)                    |     |

| I2Cx Bus Start/Stop Bits (Master Mode)        |     |

| I2Cx Bus Start/Stop Bits (Slave Mode)         |     |

| Input Capture x (ICx) Characteristics         |     |

| OCx/PWMx Characteristics                      |     |

| Output Compare x (OCx) Characteristics        | 396 |

| SPI1, SPI2 and SPI3 Master Mode (Full-Duplex, |     |

| CKE = 0, CKP = x, SMP = 1)                    | 401 |

| SPI1, SPI2 and SPI3 Master Mode (Full-Duplex, |     |

| CKE = 1, CKP = x, SMP = 1)                    | 400 |

| SPI1, SPI2 and SPI3 Master Mode (Half-Duplex, |     |

| Transmit Only, CKE = 0)                       | 398 |

| SPI1, SPI2 and SPI3 Master Mode (Half-Duplex, |     |

| Transmit Only, CKE = 1)                       | 399 |

| SPI1, SPI2 and SPI3 Slave Mode (Full-Duplex,  |     |

| CKE = 0, CKP = 0, SMP = 0)                    | 408 |

| SPI1, SPI2 and SPI3 Slave Mode (Full-Duplex,  |     |

| CKE = 0, CKP = 1, SMP = 0)                    | 406 |

| SPI1, SPI2 and SPI3 Slave Mode (Full-Duplex,  |     |

| CKE = 1, CKP = 0, SMP = 0)                    | 402 |

| SPI1, SPI2 and SPI3 Slave Mode (Full-Duplex,  |     |

| CKE = 1, CKP = 1, SMP = 0)                    | 404 |

| SPI3 Master Mode (Full-Duplex, CKE = 0,       |     |

| CKP = x, SMP = 1)                             | 413 |

| SPI3 Master Mode (Full-Duplex, CKE = 1,       |     |

| CKP = x, SMP = 1)                             | 412 |

| SPI3 Master Mode (Half-Duplex, Transmit Only, |     |

| CKE = 0)                                      | 410 |

| SPI3 Master Mode (Half-Duplex, Transmit Only, |     |

| CKE = 1)                                      | 411 |

| SPI3 Slave Mode (Full-Duplex, CKE = 0,        |     |

| CKP = 0, SMP = 0)                             | 420 |

| SPI3 Slave Mode (Full-Duplex, CKE = 0,        |     |

| CKP = 1, SMP = 0)                             | 418 |

| SPI3 Slave Mode (Full-Duplex, CKE = 1,        |     |

| CKP = 0, SMP = 0)                             | 414 |

| SPI3 Slave Mode (Full-Duplex, CKE = 1,        |     |

| CKP = 1, SMP = 0)                             | 416 |

| Timer1-Timer5 External Clock Characteristics  |     |

| UARTx I/O Characteristics                     |     |

|                                               |     |

# U UART Unique Device Identifier (UDID) 32 Universal Asynchronous Receiver Transmitter (UART) 253 Control Registers 255 Helpful Tips 254 Resources 254 Universal Asynchronous Receiver Transmitter. See UART. User OTP Memory 355 V Voltage Regulator (On-Chip) 355 W Watchdog Timer (WDT) 347, 356 Programming Considerations 356 WWW Address 474 WWW, On-Line Support 10