Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 33                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 17x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

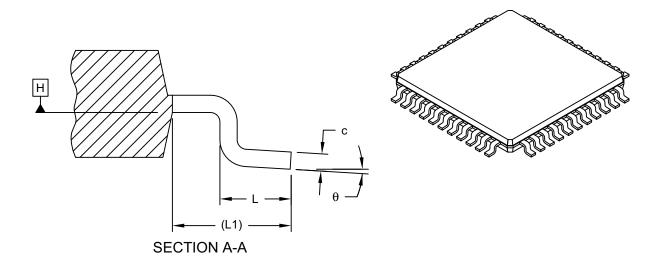

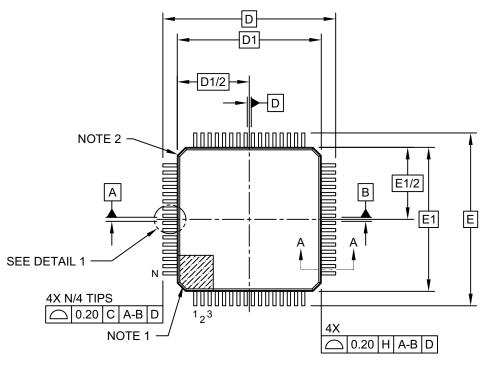

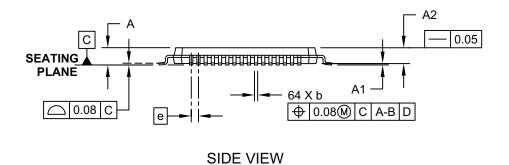

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs804-e-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 5.6 Control Registers

Five SFRs are used to write and erase the Program Flash Memory: NVMCON, NVMKEY, NVMADR, NVMADRU and NVMSRCADR/H.

The NVMCON register (Register 5-1) selects the operation to be performed (page erase, word/row program, Inactive Partition erase), initiates the program or erase cycle and is used to determine the Active Partition in Dual Partition modes.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. There are two NVM Address registers: NVMADRU and NVMADR. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word/row for programming operations, or the selected page for erase operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA.

For row programming operation, data to be written to Program Flash Memory is written into data memory space (RAM) at an address defined by the NVMSRCADR register (location of first element in row programming data).

#### REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-0 | U-0    | U-0   |

|---------|-----|-----|-----|-----|-------|--------|-------|

| _       |     | —   | —   | —   | CMPMD | —      | _     |

| bit 15  |     | •   |     |     |       |        | bit 8 |

|         |     |     |     |     |       |        |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0   | R/W-0  | U-0   |

|         | —   | —   | —   | —   | —     | I2C2MD | —     |

| bit 7   |     |     |     |     |       |        | bit 0 |

|         |     |     |     |     |       |        |       |

| Legend: |     |     |     |     |       |        |       |

| Legenu.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-11 | Unimplemented: Read as '0'                                                                      |

|-----------|-------------------------------------------------------------------------------------------------|

| bit 10    | CMPMD: Comparator Module Disable bit                                                            |

|           | <ol> <li>1 = Comparator module is disabled</li> <li>0 = Comparator module is enabled</li> </ol> |

| bit 9-2   | Unimplemented: Read as '0'                                                                      |

| bit 1     | I2C2MD: I2C2 Module Disable bit                                                                 |

|           | <ul><li>1 = I2C2 module is disabled</li><li>0 = I2C2 module is enabled</li></ul>                |

| bit 0     | Unimplemented: Read as '0'                                                                      |

#### REGISTER 10-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|--------|-----|-----|-------|

| —     | —   | —   | —   | REFOMD | —   | —   | —     |

| bit 7 |     |     |     |        |     |     | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-4 Unimplemented: I    | Read as '0'                 |

|------------------------------|-----------------------------|

| bit 3 <b>REFOMD:</b> Referen | ce Clock Module Disable bit |

| 1 = Reference cloc           | k module is disabled        |

| 0 = Reference cloc           | k module is enabled         |

| bit 2-0 Unimplemented:       | Read as '0'                 |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| U2CTSR7 | U2CTSR6 | U2CTSR5 | U2CTSR4 | U2CTSR3 | U2CTSR2 | U2CTSR1 | U2CTSR0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

#### REGISTER 11-19: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| U2RXR7 | U2RXR6 | U2RXR5 | U2RXR4 | U2RXR3 | U2RXR2 | U2RXR1 | U2RXR0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-8 **U2CTSR<7:0>:** Assign UART2 Clear-to-Send (U2CTS) to the Corresponding RPn Pin bits See Table 11-11 which contains a list of remappable inputs for the index value.

bit 7-0 **U2RXR<7:0>:** Assign UART2 Receive (U2RX) to the Corresponding RPn Pin bits See Table 11-11 which contains a list of remappable inputs for the index value.

#### REGISTER 11-20: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SCK1INR7 | SCK1INR6 | SCK1INR5 | SCK1INR4 | SCK1INR3 | SCK1INR2 | SCK1INR1 | SCK1INR0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| SDI1R7 | SDI1R6 | SDI1R5 | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 **SCK1INR<7:0>:** Assign SPI1 Clock Input (SCK1) to the Corresponding RPn Pin bits See Table 11-11 which contains a list of remappable inputs for the index value.

bit 7-0 **SDI1R<7:0>:** Assign SPI1 Data Input (SDI1) to the Corresponding RPn Pin bits See Table 11-11 which contains a list of remappable inputs for the index value.

#### REGISTER 11-37: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| bit 15 bit 15<br>U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0<br>— RP35R6 RP35R5 RP35R4 RP35R3 RP35R2 RP35R1 RP35R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |                            |                |        |              |                  |          |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------|----------------|--------|--------------|------------------|----------|--------|

| bit 15       Image: constraint of the second constraint | U-0                                                                        | R/W-0                      | R/W-0          | R/W-0  | R/W-0        | R/W-0            | R/W-0    | R/W-0  |

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            | RP36R6                     | RP36R5         | RP36R4 | RP36R3       | RP36R2           | RP36R1   | RP36R0 |

| —       RP35R6       RP35R5       RP35R4       RP35R3       RP35R2       RP35R1       RP35R0         bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 15                                                                     |                            | ·              |        |              |                  |          | bit 8  |

| —       RP35R6       RP35R5       RP35R4       RP35R3       RP35R2       RP35R1       RP35R0         bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                            |                            |                |        |              |                  |          |        |

| bit 7       bit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'       bit 14-8       RP36R<6:0>: Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U-0                                                                        | R/W-0                      | R/W-0          | R/W-0  | R/W-0        | R/W-0            | R/W-0    | R/W-0  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'         bit 14-8       RP36R<6:0>: Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            | RP35R6                     | RP35R5         | RP35R4 | RP35R3       | RP35R2           | RP35R1   | RP35R0 |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'         bit 14-8       RP36R<6:0>: Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 7                                                                      | •                          |                |        |              |                  |          | bit 0  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'         bit 14-8       RP36R<6:0>: Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |                            |                |        |              |                  |          |        |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'       x = Bit is unknown         bit 14-8       RP36R<6:0>: Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Legend:                                                                    |                            |                |        |              |                  |          |        |

| bit 15       Unimplemented: Read as '0'         bit 14-8       RP36R<6:0>: Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R = Readable                                                               | bit                        | W = Writable   | bit    | U = Unimpler | nented bit, read | l as '0' |        |

| bit 14-8 <b>RP36R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                            |                |        |              | nown             |          |        |

| bit 14-8 <b>RP36R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                            |                            |                |        |              |                  |          |        |

| (see Table 11-13 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15                                                                     | Unimplemen                 | ted: Read as ' | 0'     |              |                  |          |        |

| bit 7 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 14-8                                                                   |                            |                | •      | •            | RP36 Output F    | Pin bits |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 7                                                                      | Unimplemented: Read as '0' |                |        |              |                  |          |        |

bit 6-0 **RP35R<6:0>:** Peripheral Output Function is Assigned to RP35 Output Pin bits (see Table 11-13 for peripheral function numbers)

#### **REGISTER 11-38: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5**

| U-0             | R/W-0      | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|-----------------|------------|------------------|--------|------------------|------------------|-----------------|--------|

| —               | RP38R6     | RP38R5           | RP38R4 | RP38R3           | RP38R2           | RP38R1          | RP38R0 |

| bit 15          |            |                  |        |                  |                  |                 | bit 8  |

|                 |            |                  |        |                  |                  |                 |        |

| U-0             | R/W-0      | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| —               | RP37R6     | RP37R5           | RP37R4 | RP37R3           | RP37R2           | RP37R1          | RP37R0 |

| bit 7           |            |                  |        |                  |                  |                 | bit 0  |

|                 |            |                  |        |                  |                  |                 |        |

| Legend:         |            |                  |        |                  |                  |                 |        |

| R = Readable    | bit        | W = Writable     | bit    | U = Unimpler     | nented bit, read | as '0'          |        |

| -n = Value at P | OR         | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

|                 |            |                  |        |                  |                  |                 |        |

| bit 15          | Unimplemen | ted: Read as '   | כי     |                  |                  |                 |        |

| bit 14-8        |            |                  |        |                  | RP38 Output P    |                 |        |

- (see Table 11-13 for peripheral function numbers)

- bit 7 Unimplemented: Read as '0'

- bit 6-0 **RP37R<6:0>:** Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 11-13 for peripheral function numbers)

| U-0    | R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| —      | RP40R6 | RP40R5 | RP40R4 | RP40R3 | RP40R2 | RP40R1 | RP40R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| U-0    | R/W-0  |

| —      | RP39R6 | RP39R5 | RP39R4 | RP39R3 | RP39R2 | RP39R1 | RP39R0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

#### REGISTER 11-39: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15   | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-8 | <b>RP40R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-13 for peripheral function numbers) |

| bit 7    | Unimplemented: Read as '0'                                                                                                                |

| bit 6-0  | <b>RP39R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP39 Output Pin bits (see Table 11-13 for peripheral function numbers) |

#### REGISTER 11-40: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0          | R/W-0  | R/W-0         | R/W-0  | R/W-0         | R/W-0           | R/W-0  | R/W-0  |

|--------------|--------|---------------|--------|---------------|-----------------|--------|--------|

| _            | RP43R6 | RP43R5        | RP43R4 | RP43R3        | RP43R2          | RP43R1 | RP43R0 |

| bit 15       |        |               |        |               |                 |        | bit 8  |

|              |        |               |        |               |                 |        |        |

| U-0          | R/W-0  | R/W-0         | R/W-0  | R/W-0         | R/W-0           | R/W-0  | R/W-0  |

| _            | RP41R6 | RP41R5        | RP41R4 | RP41R3        | RP41R2          | RP41R1 | RP41R0 |

| bit 7        |        | •             | •      | •             |                 | •      | bit 0  |

|              |        |               |        |               |                 |        |        |

| Legend:      |        |               |        |               |                 |        |        |

| D - Doodable | hit    | M = M/ritable | hit    | II – Unimplor | monted hit read | aa '0' |        |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15 Unimplemented: Read as '0'

bit 14-8 **RP43R<6:0>:** Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-13 for peripheral function numbers)

bit 7 Unimplemented: Read as '0'

bit 6-0 **RP41R<6:0>:** Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 11-13 for peripheral function numbers)

### 15.2 Output Compare Control Registers

#### REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

|                 | U-0         | OCSIDL              | OCTSEL2           | OCTSEL1           | OCTSEL0           |                 |        |

|-----------------|-------------|---------------------|-------------------|-------------------|-------------------|-----------------|--------|

| R/W-0<br>ENFLTA | U-0         |                     |                   |                   | OCISELU           |                 |        |

| ENFLTA          | U-0         |                     |                   |                   |                   |                 | bit    |

| ENFLTA          | 00          | U-0                 | R/W-0, HSC        | R/W-0             | R/W-0             | R/W-0           | R/W-0  |

| bit 7           | _           |                     | OCFLTA            | TRIGMODE          | OCM2              | OCM1            | OCM0   |

|                 |             |                     |                   |                   |                   |                 | bit    |

| Legend:         |             | USC - Hardwa        | are Settable/Cle  | arablo bit        |                   |                 |        |

| R = Readab      | lo hit      | W = Writable b      |                   |                   | ented bit, read a | ae 'O'          |        |

| -n = Value a    |             | '1' = Bit is set    | п                 | '0' = Bit is clea |                   | x = Bit is unkr |        |

|                 |             |                     |                   |                   |                   |                 | 101111 |

| bit 15-14       | Unimpleme   | ented: Read as '0   | ,                 |                   |                   |                 |        |

| bit 13          | OCSIDL: 0   | utput Compare x     | Stop in Idle Mo   | de Control bit    |                   |                 |        |

|                 | 1 = Output  | Compare x halts     | in CPU Idle mo    | de                |                   |                 |        |

|                 | 0 = Output  | Compare x contir    | ues to operate    | in CPU Idle mo    | de                |                 |        |

| bit 12-10       | OCTSEL<2    | :0>: Output Com     | oare x Clock Se   | lect bits         |                   |                 |        |

|                 | 111 = Perip | heral clock (FP)    |                   |                   |                   |                 |        |

|                 | 110 = Rese  |                     |                   |                   |                   |                 |        |

|                 | 101 = Rese  |                     | was of the OCy    |                   |                   |                 |        |

|                 |             | K is the clock sou  |                   |                   | Ironous clock is  | supported)      |        |

|                 |             | K is the clock sou  |                   |                   |                   |                 |        |

|                 |             | K is the clock sou  |                   |                   |                   |                 |        |

|                 | 000 = T2CL  | K is the clock sou  | urce of the OCx   |                   |                   |                 |        |

| bit 9-8         | Unimpleme   | ented: Read as '0   | ,                 |                   |                   |                 |        |

| bit 7           | ENFLTA: Fa  | ault A Input Enabl  | e bit             |                   |                   |                 |        |

|                 | 1 = Output  | Compare Fault A     | input (OCFA) is   | s enabled         |                   |                 |        |

|                 | 0 = Output  | Compare Fault A     | input (OCFA) is   | s disabled        |                   |                 |        |

| bit 6-5         | Unimpleme   | ented: Read as '0   | ,                 |                   |                   |                 |        |

| bit 4           | OCFLTA: P   | WM Fault A Cond     | lition Status bit |                   |                   |                 |        |

|                 |             | ault A condition c  |                   |                   |                   |                 |        |

|                 | 0 = No PW   | M Fault A condition | on on the OCFA    | pin has occurre   | ed                |                 |        |

| bit 3           |             | : Trigger Status N  |                   |                   |                   |                 |        |

|                 |             | TAT (OCxCON2<       | ,                 | /hen OCxRS = (    | OCxTMR or in s    | oftware         |        |

|                 | 0 = TRIGS   | TAT is cleared on   | y by software     |                   |                   |                 |        |

**Note 1:** OCxR and OCxRS are double-buffered in PWM mode only.

#### REGISTER 16-8: SSEVTCMP: PWMx SECONDARY SPECIAL EVENT COMPARE REGISTER<sup>(1)</sup>

| R/W-0   | R/W-0 | R/W-0       | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|---------|-------|-------------|--------|----------|-------|-------|-------|

|         |       |             | SSEVTC | MP<12:5> |       |       |       |

| bit 15  |       |             |        |          |       |       | bit 8 |

|         |       |             |        |          |       |       |       |

| R/W-0   | R/W-0 | R/W-0       | R/W-0  | R/W-0    | U-0   | U-0   | U-0   |

|         | S     | SEVTCMP<4:0 | )>     |          | —     | —     | —     |

| bit 7   |       |             |        |          |       |       | bit 0 |

|         |       |             |        |          |       |       |       |

| Legend: |       |             |        |          |       |       |       |

| _ogona.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-3 SSEVTCMP<12:0>: Special Event Compare Count Value bits

bit 2-0 Unimplemented: Read as '0'

Note 1: One LSB = 1.04 ns (at fastest auxiliary clock rate); therefore, the minimum SSEVTCMP resolution is 8.32 ns.

#### **REGISTER 16-9:** CHOP: PWMx CHOP CLOCK GENERATOR REGISTER<sup>(1)</sup>

| R/W-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    |  |

|----------|-----|-----|-----|-----|-----|----------|----------|--|

| CHPCLKEN | _   | —   | —   | —   | —   | CHOPCLK6 | CHOPCLK5 |  |

| bit 15 b |     |     |     |     |     |          |          |  |

| R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | U-0 | U-0 | U-0   |

|----------|----------|----------|----------|----------|-----|-----|-------|

| CHOPCLK4 | CHOPCLK3 | CHOPCLK2 | CHOPCLK1 | CHOPCLK0 | —   | —   | —     |

| bit 7    |          |          |          |          |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15

CHPCLKEN: Enable Chop Clock Generator bit

1 = Chop clock generator is enabled

0 = Chop clock generator is disabled

bit 14-10

Unimplemented: Read as '0'

bit 9-3

CHOPCLK<6:0>: Chop Clock Divider bits

Value is in 8.32 ns increments. The frequency of the chop clock signal is given by:

Chop Frequency = 1/(16.64 \* (CHOP<7:3> + 1) \* Primary Master PWM Input Clock Period)

bit 2-0 Unimplemented: Read as '0'

**Note 1:** The chop clock generator operates with the primary PWMx clock prescaler (PCLKDIV<2:0>) in the PTCON2 register (Register 16-2).

#### REGISTER 16-22: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER (x = 1 to 8) (CONTINUED)

| bit 7-3 | FLTSRC<4:0>: Fault Control Signal Source Select for PWMx Generator bits<br>11111 = Reserved<br>10001 = Reserved<br>10000 = Analog Comparator 4<br>01111 = Analog Comparator 3<br>01110 = Analog Comparator 2<br>01101 = Analog Comparator 1<br>01100 = Fault 12<br>01011 = Fault 11<br>01010 = Fault 11<br>01010 = Fault 10<br>01001 = Fault 9<br>01000 = Fault 8<br>00111 = Fault 7 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 00110 = Fault 7 $00110 = Fault 6$ $00101 = Fault 5$ $00100 = Fault 4$ $00011 = Fault 3$ $00010 = Fault 2$ $00001 = Fault 1$ $00000 = Reserved$                                                                                                                                                                                                                                       |

| bit 2   | <b>FLTPOL:</b> Fault Polarity for PWMx Generator bit <sup>(1)</sup><br>1 = The selected Fault source is active-low<br>0 = The selected Fault source is active-high                                                                                                                                                                                                                   |

| bit 1-0 | FLTMOD<1:0>: Fault Mode for PWMx Generator bits<br>11 = Fault input is disabled<br>10 = Reserved<br>01 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (cycle)<br>00 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (latched condition)                                                                                       |

Note 1: These bits should be changed only when PTEN = 0 (PTCON<15>).

#### REGISTER 16-23: STRIGX: PWMX SECONDARY TRIGGER COMPARE VALUE REGISTER (x = 1 to 8)<sup>(1)</sup>

| R/W-0             | R/W-0       | R/W-0                                               | R/W-0           | R/W-0                              | R/W-0 | R/W-0              | R/W-0        |  |

|-------------------|-------------|-----------------------------------------------------|-----------------|------------------------------------|-------|--------------------|--------------|--|

|                   |             |                                                     | STRGC           | MP<12:5>                           |       |                    |              |  |

| bit 15            |             |                                                     |                 |                                    |       |                    | bit 8        |  |

| R/W-0             | R/W-0       | R/W-0                                               | R/W-0           | R/W-0                              | U-0   | U-0                | U-0          |  |

|                   |             | STRGCMP<4:0                                         | >               |                                    |       | _                  | _            |  |

| bit 7             |             |                                                     |                 |                                    |       |                    | bit (        |  |

| Legend:           |             |                                                     |                 |                                    |       |                    |              |  |

| R = Readab        | le bit      | W = Writable                                        | bit             | U = Unimplemented bit, read as '0' |       |                    |              |  |

| -n = Value at POR |             | '1' = Bit is set                                    |                 | '0' = Bit is cleared               |       | x = Bit is unknown |              |  |

| bit 15-3          | When the se | <12:0>: Seconda<br>econdary PWMx<br>ger the ADC mod | functions in th | •                                  |       | contains the co    | mpare values |  |

| bit 2-0           |             | nted: Read as '                                     |                 |                                    |       |                    |              |  |

Note 1: STRIGx cannot generate the PWM trigger interrupts.

| Step<br>Command       | OPTION<3:0> | Option Description                                                                            |

|-----------------------|-------------|-----------------------------------------------------------------------------------------------|

| PTGCTRL(1)            | 0000        | Reserved                                                                                      |

|                       | 0001        | Reserved                                                                                      |

|                       | 0010        | Disable PTG Step Delay Timer (PTGSD)                                                          |

|                       | 0011        | Reserved                                                                                      |

|                       | 0100        | Reserved                                                                                      |

|                       | 0101        | Reserved                                                                                      |

|                       | 0110        | Enable PTG Step Delay Timer (PTGSD)                                                           |

|                       | 0111        | Reserved                                                                                      |

|                       | 1000        | Start and wait for the PTG Timer0 to match the PTG Timer0 Limit register                      |

|                       | 1001        | Start and wait for the PTG Timer1 to match the PTG Timer1 Limit register                      |

|                       | 1010        | Reserved                                                                                      |

|                       | 1011        | Wait for software trigger bit transition from low-to-high before continuing (PTGSWT = 0 to 1) |

|                       | 1100        | Copy contents of the PTG Counter 0 register to the CNVCHSEL<5:0> bits (ADCON3L<5:0>)          |

|                       | 1101        | Copy contents of the PTG Counter 1 register to the CNVCHSEL<5:0> bits (ADCON3L<5:0>)          |

|                       | 1110        | Copy contents of the PTG Literal 0 register to the CNVCHSEL<5:0> bits (ADCON3L<5:0>)          |

|                       | 1111        | Generate the triggers indicated in the PTG Broadcast Trigger Enable register (PTGBTE)         |

| PTGADD <sup>(1)</sup> | 0000        | Add contents of PTGADJ register to the PTG Counter 0 Limit register (PTGC0LIM                 |

|                       | 0001        | Add contents of PTGADJ register to the PTG Counter 1 Limit register (PTGC1LIN                 |

|                       | 0010        | Add contents of PTGADJ register to the PTG Timer0 Limit register (PTGT0LIM)                   |

|                       | 0011        | Add contents of PTGADJ register to the PTG Timer1 Limit register (PTGT1LIM)                   |

|                       | 0100        | Add contents of PTGADJ register to the PTG Step Delay Limit register (PTGSDLIM)               |

|                       | 0101        | Add contents of PTGADJ register to the PTG Literal 0 register (PTGL0)                         |

|                       | 0110        | Reserved                                                                                      |

|                       | 0111        | Reserved                                                                                      |

| PTGCOPY(1)            | 1000        | Copy contents of PTGHOLD register to the PTG Counter 0 Limit register (PTGC0LIM)              |

|                       | 1001        | Copy contents of PTGHOLD register to the PTG Counter 1 Limit register (PTGC1LIM)              |

|                       | 1010        | Copy contents of PTGHOLD register to the PTG Timer0 Limit register (PTGT0LIM                  |

|                       | 1011        | Copy contents of PTGHOLD register to the PTG Timer1 Limit register (PTGT1LIM                  |

|                       | 1100        | Copy contents of PTGHOLD register to the PTG Step Delay Limit register (PTGSDLIM)             |

|                       | 1101        | Copy contents of PTGHOLD register to the PTG Literal 0 register (PTGL0)                       |

|                       | 1110        | Reserved                                                                                      |

|                       | 1111        | Reserved                                                                                      |

### TABLE 17-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 17-2 for the trigger output descriptions.

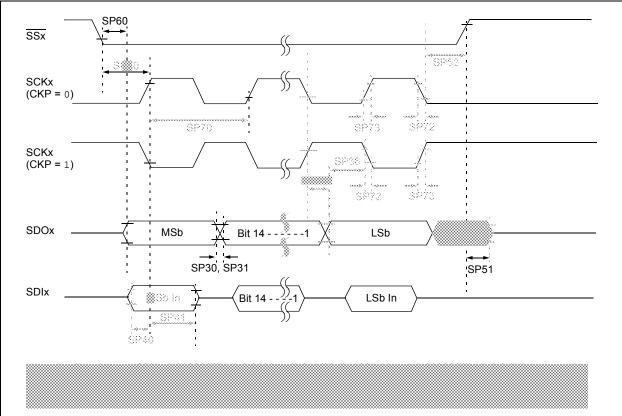

#### REGISTER 18-1: SPIx CONTROL REGISTER 1 LOW (CONTINUED)

| bit 9         | SMP: SPIx Data Input Sample Phase bit                                                                                                                                                                                            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | <u>Master Mode:</u><br>1 = Input data is sampled at the end of data output time                                                                                                                                                  |

|               | 0 = Input data is sampled at the middle of data output time                                                                                                                                                                      |

|               | Slave Mode:                                                                                                                                                                                                                      |

|               | Input data is always sampled at the middle of data output time, regardless of the SMP setting.                                                                                                                                   |

| bit 8         | CKE: SPIx Clock Edge Select bit <sup>(1)</sup>                                                                                                                                                                                   |

|               | <ul> <li>1 = Transmit happens on transition from active clock state to Idle clock state</li> <li>0 = Transmit happens on transition from Idle clock state to active clock state</li> </ul>                                       |

| bit 7         | SSEN: Slave Select Enable bit (Slave mode) <sup>(2)</sup>                                                                                                                                                                        |

|               | 1 = $\overline{SSx}$ pin is used by the macro in Slave mode; $\overline{SSx}$ pin is used as the slave select input 0 = $\overline{SSx}$ pin is not used by the macro ( $\overline{SSx}$ pin will be controlled by the port I/O) |

| bit 6         | CKP: Clock Polarity Select bit                                                                                                                                                                                                   |

|               | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                         |

| bit 5         | MSTEN: Master Mode Enable bit                                                                                                                                                                                                    |

|               | 1 = Master mode<br>0 = Slave mode                                                                                                                                                                                                |

| bit 4         | DISSDI: Disable SDIx Input Port bit                                                                                                                                                                                              |

|               | <ul> <li>1 = SDIx pin is not used by the module; pin is controlled by port function</li> <li>0 = SDIx pin is controlled by the module</li> </ul>                                                                                 |

| bit 3         | DISSCK: Disable SCKx Output Port bit                                                                                                                                                                                             |

|               | <ul> <li>1 = SCKx pin is not used by the module; pin is controlled by port function</li> <li>0 = SCKx pin is controlled by the module</li> </ul>                                                                                 |

| bit 2         | MCLKEN: Master Clock Enable bit <sup>(3)</sup>                                                                                                                                                                                   |

|               | <ul> <li>1 = REFO is used by the Baud Rate Generator (BRG)</li> <li>0 = Peripheral clock is used by the BRG</li> </ul>                                                                                                           |

| bit 1         | SPIFE: Frame Sync Pulse Edge Select bit                                                                                                                                                                                          |

|               | <ul> <li>1 = Frame Sync pulse (Idle-to-active edge) coincides with the first bit clock</li> <li>0 = Frame Sync pulse (Idle-to-active edge) precedes the first bit clock</li> </ul>                                               |

| bit 0         | ENHBUF: Enhanced Buffer Enable bit                                                                                                                                                                                               |

|               | <ul> <li>1 = Enhanced Buffer mode is enabled</li> <li>0 = Enhanced Buffer mode is disabled</li> </ul>                                                                                                                            |

| Note 1:<br>2: | When AUDEN (SPIxCON1H<15>) = 1, this module functions as if CKE = 0, regardless of its actual value.<br>When $FRMEN = 1$ SSEN is not used                                                                                        |

- **2:** When FRMEN = 1, SSEN is not used.

- **3:** MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows FRMSYPW.

| U-0          | U-0                                                                                                                                                           | U-0                                                                                                              | U-0             | U-0                       | U-0               | U-0             | U-0            |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------|-------------------|-----------------|----------------|--|--|--|

| _            | _                                                                                                                                                             | —                                                                                                                | _               |                           |                   | _               | _              |  |  |  |

| bit 15       |                                                                                                                                                               |                                                                                                                  |                 |                           |                   |                 | bit 8          |  |  |  |

|              |                                                                                                                                                               | <b>5</b> .444.6                                                                                                  | 54446           | 5444.6                    | -                 | <b>D</b> 444 A  |                |  |  |  |

| U-0          | R/W-0                                                                                                                                                         | R/W-0                                                                                                            | R/W-0           | R/W-0                     | R/W-0             | R/W-0           | R/W-0          |  |  |  |

|              | PCIE                                                                                                                                                          | SCIE                                                                                                             | BOEN            | SDAHT                     | SBCDE             | AHEN            | DHEN           |  |  |  |

| bit 7        |                                                                                                                                                               |                                                                                                                  |                 |                           |                   |                 | bit 0          |  |  |  |

| Legend:      |                                                                                                                                                               |                                                                                                                  |                 |                           |                   |                 |                |  |  |  |