Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betano                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 33                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

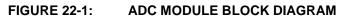

| Data Converters            | A/D 17x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs804-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.3 Data Address Space

The dsPIC33EPXXXGS70X/80X family CPU has a separate 16-bit wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory map is shown in Figure 4-6.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes or 32K words.

The lower half of the data memory space (i.e., when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV).

dsPIC33EPXXXGS70X/80X family devices implement up to 12 Kbytes of data memory. If an EA points to a location outside of this area, an all-zero word or byte is returned.

### 4.3.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.3.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGS70X/80X family instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB; the MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

### 4.3.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGS70X/80X family core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

### 4.3.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a Working register as an Address Pointer.

### 4.7 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a Bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.7.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-2).

Note: Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.7.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags, as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W (XWM) register, to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-2). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W (YWM) register, to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit (MODCON<14>) is set.

#### FIGURE 4-10: MODULO ADDRESSING OPERATION EXAMPLE

| Byte<br>Address<br>0x1100 |                                                                   | MOV<br>MOV<br>MOV | #0x1100, W0<br>W0, XMODSRT<br>#0x1163, W0 | ;set modulo start address                             |

|---------------------------|-------------------------------------------------------------------|-------------------|-------------------------------------------|-------------------------------------------------------|

| 0x1100                    |                                                                   | MOV               | W0, MODEND<br>#0x8001, W0                 | ;set modulo end address                               |

|                           |                                                                   | MOV               | W0, MODCON                                | ;enable W1, X AGU for modulo                          |

|                           | ♥ ( )                                                             | MOV               |                                           |                                                       |

| 0x1163                    | $\square$                                                         | MOV               | #0x1110, W1                               | ;point W1 to buffer                                   |

|                           |                                                                   | DO<br>MOV         | AGAIN, #0x31<br>W0, [W1++]                | ;fill the 50 buffer locations ;fill the next location |

|                           | Start Addr = 0x1100<br>End Addr = 0x1163<br>Length = 0x0032 words | AGAIN:            | INC WO, WO                                | ;increment the fill value                             |

| U-0                                     | U-0                                                                                                         | U-0                                | U-0              | R/W-0             | R/W-0           | R/W-0           | R/W-0          |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------|------------------|-------------------|-----------------|-----------------|----------------|

| —                                       | -                                                                                                           | —                                  | —                | IC4MD             | IC3MD           | IC2MD           | IC1MD          |

| bit 15                                  |                                                                                                             |                                    |                  |                   |                 | ·               | bit 8          |

|                                         |                                                                                                             |                                    |                  | <b>D</b> 444 0    | <b>D</b> 444 0  | <b>D</b> 444 0  | <b>D</b> 444 0 |

| U-0                                     | U-0                                                                                                         | U-0                                | U-0              | R/W-0<br>OC4MD    | R/W-0<br>OC3MD  | R/W-0<br>OC2MD  | R/W-0<br>OC1MD |

| <br>bit 7                               | _                                                                                                           |                                    |                  | 004MD             | OCSIVID         | OCZIVID         | bit 0          |

|                                         |                                                                                                             |                                    |                  |                   |                 |                 |                |

| Legend:                                 |                                                                                                             |                                    |                  |                   |                 |                 |                |

| R = Readab                              | ole bit                                                                                                     | W = Writable I                     | oit              | U = Unimplem      | nented bit, rea | d as '0'        |                |

| -n = Value a                            | at POR                                                                                                      | '1' = Bit is set                   |                  | '0' = Bit is clea | ared            | x = Bit is unkn | iown           |

| bit 15-12                               | Unimplomon                                                                                                  | ted: Read as 'o                    | <b>)</b> ,       |                   |                 |                 |                |

| bit 13-12                               | -                                                                                                           | Capture 4 Mod                      |                  |                   |                 |                 |                |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | •                                                                                                           | ture 4 module i                    |                  |                   |                 |                 |                |

|                                         |                                                                                                             | ture 4 module i                    |                  |                   |                 |                 |                |

| oit 10                                  | IC3MD: Input                                                                                                | Capture 3 Mod                      | lule Disable bit |                   |                 |                 |                |

|                                         |                                                                                                             | ture 3 module i                    |                  |                   |                 |                 |                |

|                                         |                                                                                                             | ture 3 module i                    |                  |                   |                 |                 |                |

| bit 9                                   |                                                                                                             | Capture 2 Moc                      |                  |                   |                 |                 |                |

|                                         |                                                                                                             | ture 2 module i<br>ture 2 module i |                  |                   |                 |                 |                |

| bit 8                                   |                                                                                                             | Capture 1 Mod                      |                  |                   |                 |                 |                |

|                                         | 1 = Input Cap                                                                                               | ture 1 module i<br>ture 1 module i | s disabled       |                   |                 |                 |                |

| bit 7-4                                 |                                                                                                             | ted: Read as 'd                    |                  |                   |                 |                 |                |

| bit 3                                   | OC4MD: Outp                                                                                                 | out Compare 4                      | Module Disable   | e bit             |                 |                 |                |

|                                         | 1 = Output Compare 4 module is disabled                                                                     |                                    |                  |                   |                 |                 |                |

|                                         | 0 = Output Compare 4 module is enabled                                                                      |                                    |                  |                   |                 |                 |                |

| bit 2                                   | OC3MD: Output Compare 3 Module Disable bit                                                                  |                                    |                  |                   |                 |                 |                |

|                                         | <ul> <li>1 = Output Compare 3 module is disabled</li> <li>0 = Output Compare 3 module is enabled</li> </ul> |                                    |                  |                   |                 |                 |                |

| bit 1                                   | OC2MD: Output Compare 2 Module Disable bit                                                                  |                                    |                  |                   |                 |                 |                |

|                                         | <ul> <li>1 = Output Compare 2 module is disabled</li> <li>0 = Output Compare 2 module is enabled</li> </ul> |                                    |                  |                   |                 |                 |                |

| bit 0                                   | OC1MD: Outp                                                                                                 | out Compare 1                      | Module Disable   | e bit             |                 |                 |                |

|                                         |                                                                                                             |                                    |                  |                   |                 |                 |                |

### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

| U-0          | U-0                             | U-0                                 | U-0           | U-0               | R/W-0            | U-0              | U-0 |  |  |

|--------------|---------------------------------|-------------------------------------|---------------|-------------------|------------------|------------------|-----|--|--|

| —            | _                               |                                     | —             |                   | PGA2MD           | _                | _   |  |  |

| bit 15       | •                               |                                     |               |                   | •                |                  | bit |  |  |

|              |                                 |                                     |               |                   |                  |                  |     |  |  |

| U-0          | U-0                             | R/W-0                               | R/W-0         | R/W-0             | R/W-0            | R/W-0            | U-0 |  |  |

| —            | —                               | CLC4MD                              | CLC3MD        | CLC2MD            | CLC1MD           | CCSMD            | —   |  |  |

| bit 7        |                                 |                                     |               |                   |                  |                  | bit |  |  |

| Legend:      |                                 |                                     |               |                   |                  |                  |     |  |  |

| R = Readab   | ole bit                         | W = Writable                        | oit           | U = Unimpler      | nented bit, read | d as '0'         |     |  |  |

| -n = Value a | It POR                          | '1' = Bit is set                    |               | '0' = Bit is clea |                  | x = Bit is unkno | own |  |  |

|              |                                 |                                     |               |                   |                  |                  |     |  |  |

| bit 15-11    | Unimplemen                      | ted: Read as '                      | )'            |                   |                  |                  |     |  |  |

| bit 10       | PGA2MD: PO                      | GA2 Module Dis                      | able bit      |                   |                  |                  |     |  |  |

|              |                                 | dule is disable                     | -             |                   |                  |                  |     |  |  |

|              |                                 | dule is enabled                     |               |                   |                  |                  |     |  |  |

| bit 9-6      | •                               | ted: Read as '0                     |               |                   |                  |                  |     |  |  |

| bit 5        |                                 | C4 Module Dis                       |               |                   |                  |                  |     |  |  |

|              |                                 | dule is disabled                    |               |                   |                  |                  |     |  |  |

|              |                                 | dule is enabled                     |               |                   |                  |                  |     |  |  |

| bit 4        |                                 | C3 Module Dis                       |               |                   |                  |                  |     |  |  |

|              |                                 | dule is disableo<br>dule is enabled |               |                   |                  |                  |     |  |  |

| bit 3        |                                 | C2 Module Dis                       |               |                   |                  |                  |     |  |  |

| bit 0        |                                 | dule is disabled                    |               |                   |                  |                  |     |  |  |

|              | 0 = CLC2 module is enabled      |                                     |               |                   |                  |                  |     |  |  |

| bit 2        | CLC1MD: CLC1 Module Disable bit |                                     |               |                   |                  |                  |     |  |  |

|              | 1 = CLC1 mo                     | 1 = CLC1 module is disabled         |               |                   |                  |                  |     |  |  |

|              | 0 = CLC1 mo                     | dule is enabled                     |               |                   |                  |                  |     |  |  |

| bit 1        | CCSMD: Con                      | stant-Current S                     | Source Module | Disable bit       |                  |                  |     |  |  |

|              |                                 | current source                      |               |                   |                  |                  |     |  |  |

|              |                                 | current source                      |               | bled              |                  |                  |     |  |  |

| bit 0        | Unimplemen                      | ted: Read as '0                     | )'            |                   |                  |                  |     |  |  |

### REGISTER 10-7: PMD8: PERIPHERAL MODULE DISABLE CONTROL REGISTER 8

#### REGISTER 11-21: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|-------|-------|-------|-------|

| —      | —     | —     | —     | —     | —     | —     | —     |

| bit 15 |       |       |       | •     |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| SS1R7  | SS1R6 | SS1R5 | SS1R4 | SS1R3 | SS1R2 | SS1R1 | SS1R0 |

| bit 7  |       |       | ·     |       | ·     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **SS1R<7:0>:** Assign SPI1 Slave Select (SS1) to the Corresponding RPn Pin bits See Table 11-11 which contains a list of remappable inputs for the index value.

#### REGISTER 11-22: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| R/W-0             | R/W-0    | R/W-0            | R/W-0    | R/W-0                              | R/W-0    | R/W-0              | R/W-0    |

|-------------------|----------|------------------|----------|------------------------------------|----------|--------------------|----------|

| SCK2INR7          | SCK2INR6 | SCK2INR5         | SCK2INR4 | SCK2INR3                           | SCK2INR2 | SCK2INR1           | SCK2INR0 |

| bit 15            |          |                  |          |                                    |          | •                  | bit 8    |

|                   |          |                  |          |                                    |          |                    |          |

| R/W-0             | R/W-0    | R/W-0            | R/W-0    | R/W-0                              | R/W-0    | R/W-0              | R/W-0    |

| SDI2R7            | SDI2R6   | SDI2R5           | SDI2R4   | SDI2R3                             | SDI2R2   | SDI2R1             | SDI2R0   |

| bit 7             |          |                  |          |                                    |          |                    | bit 0    |

|                   |          |                  |          |                                    |          |                    |          |

| Legend:           |          |                  |          |                                    |          |                    |          |

| R = Readable bit  |          | W = Writable bit |          | U = Unimplemented bit, read as '0' |          |                    |          |

| -n = Value at POR |          | '1' = Bit is set |          | '0' = Bit is cleared               |          | x = Bit is unknown |          |

bit 15-8SCK2INR<7:0>: Assign SPI2 Clock Input (SCK2) to the Corresponding RPn Pin bits<br/>See Table 11-11 which contains a list of remappable inputs for the index value.bit 7-0SDI2R<7:0>: Assign SPI2 Data Input (SDI2) to the Corresponding RPn Pin bits

See Table 11-11 which contains a list of remappable inputs for the index value.

### 14.2 Input Capture Registers

### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0   | R/W-0  | R/W-0       | R/W-0       | R/W-0   | U-0   | U-0   |

|--------|-------|--------|-------------|-------------|---------|-------|-------|

| _      | —     | ICSIDL | ICTSEL2     | ICTSEL1     | ICTSEL0 |       | —     |

| bit 15 |       |        |             |             |         |       | bit 8 |

|        |       |        |             |             |         |       |       |

| U-0    | R/W-0 | R/W-0  | R-0, HC, HS | R-0, HC, HS | R/W-0   | R/W-0 | R/W-0 |

| _      | ICI1  | ICI0   | ICOV        | ICBNE       | ICM2    | ICM1  | ICM0  |

| bit 7  |       |        |             |             |         |       | bit 0 |

| Legend:HC = Hardware Clearable bit |                  | HS = Hardware Settable bit         |                    |  |

|------------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit                   | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                  | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                       |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture x Stop in Idle Control bit                                                                                                                                                                                                                                 |

|           | 1 = Input capture will halt in CPU Idle mode                                                                                                                                                                                                                                     |

|           | <ul><li>Input capture will continue to operate in CPU Idle mode</li></ul>                                                                                                                                                                                                        |

| bit 12-10 | ICTSEL<2:0>: Input Capture x Timer Select bits                                                                                                                                                                                                                                   |

|           | <ul> <li>111 = Peripheral clock (FP) is the clock source of the ICx</li> <li>110 = Reserved</li> <li>101 = Reserved</li> <li>100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)</li> <li>011 = T5CLK is the clock source of the ICx</li> </ul> |

|           | 010 = T4CLK is the clock source of the ICx<br>001 = T2CLK is the clock source of the ICx                                                                                                                                                                                         |

|           | 000 = T3CLK is the clock source of the ICx                                                                                                                                                                                                                                       |

| bit 9-7   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                       |

| bit 6-5   | ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)                                                                                                                                                                         |

|           | <ul> <li>11 = Interrupt on every fourth capture event</li> <li>10 = Interrupt on every third capture event</li> <li>01 = Interrupt on every second capture event</li> <li>00 = Interrupt on every capture event</li> </ul>                                                       |

| bit 4     | ICOV: Input Capture x Overflow Status Flag bit (read-only)                                                                                                                                                                                                                       |

|           | <ul> <li>1 = Input capture buffer overflow has occurred</li> <li>0 = No input capture buffer overflow has occurred</li> </ul>                                                                                                                                                    |

| bit 3     | ICBNE: Input Capture x Buffer Not Empty Status bit (read-only)                                                                                                                                                                                                                   |

|           | <ul> <li>1 = Input capture buffer is not empty, at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                                                                                                                |

| bit 2-0   | ICM<2:0>: Input Capture x Mode Select bits                                                                                                                                                                                                                                       |

|           | <ul> <li>111 = Input Capture x functions as an interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)</li> <li>110 = Unused (module is disabled)</li> </ul>                                                         |

|           | 101 = Capture mode, every 16th rising edge (Prescaler Capture mode)                                                                                                                                                                                                              |

|           | 100 = Capture mode, every 4th rising edge (Prescaler Capture mode)                                                                                                                                                                                                               |

|           | <ul> <li>011 = Capture mode, every rising edge (Simple Capture mode)</li> <li>010 = Capture mode, every falling edge (Simple Capture mode)</li> </ul>                                                                                                                            |

|           | 001 = Capture mode, every raining edge (Simple Capture mode)<br>001 = Capture mode, every rising and falling edge (Edge Detect mode, ICI<1:0>, is not used in this mode)<br>000 = Input Capture x is turned off                                                                  |

### 15.2 Output Compare Control Registers

### REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

|                 | U-0                                      | OCSIDL              | OCTSEL2          | OCTSEL1           | OCTSEL0           |                 |        |

|-----------------|------------------------------------------|---------------------|------------------|-------------------|-------------------|-----------------|--------|

| R/W-0<br>ENFLTA | U-0                                      |                     |                  |                   | OCISELU           |                 |        |

| ENFLTA          | U-0                                      |                     |                  |                   |                   |                 | bit    |

| ENFLTA          | 00                                       | U-0                 | R/W-0, HSC       | R/W-0             | R/W-0             | R/W-0           | R/W-0  |

| bit 7           | _                                        |                     | OCFLTA           | TRIGMODE          | OCM2              | OCM1            | OCM0   |

|                 |                                          |                     |                  |                   |                   |                 | bit    |

| Legend:         |                                          | USC - Hardwa        | are Settable/Cle | arablo bit        |                   |                 |        |

| R = Readab      | lo hit                                   | W = Writable b      |                  |                   | ented bit, read a | ae 'O'          |        |

| -n = Value a    |                                          | '1' = Bit is set    | п                | '0' = Bit is clea |                   | x = Bit is unkr |        |

|                 |                                          |                     |                  |                   |                   |                 | 101111 |

| bit 15-14       | Unimpleme                                | ented: Read as '0   | ,                |                   |                   |                 |        |

| bit 13          | OCSIDL: 0                                | utput Compare x     | Stop in Idle Mo  | de Control bit    |                   |                 |        |

|                 | 1 = Output                               | Compare x halts     | in CPU Idle mo   | de                |                   |                 |        |

|                 | 0 = Output                               | Compare x contir    | ues to operate   | in CPU Idle mo    | de                |                 |        |

| bit 12-10       | OCTSEL<2                                 | :0>: Output Com     | oare x Clock Se  | lect bits         |                   |                 |        |

|                 | 111 = Perip                              | heral clock (FP)    |                  |                   |                   |                 |        |

|                 | 110 = Rese                               |                     |                  |                   |                   |                 |        |

|                 | 101 = Rese                               |                     | was of the OCy   |                   |                   |                 |        |

|                 |                                          | K is the clock sou  |                  |                   | Ironous clock is  | supported)      |        |

|                 |                                          | K is the clock sou  |                  |                   |                   |                 |        |

|                 |                                          | K is the clock sou  |                  |                   |                   |                 |        |

|                 | 000 = T2CL                               | K is the clock sou  | urce of the OCx  |                   |                   |                 |        |

| bit 9-8         | Unimpleme                                | ented: Read as '0   | ,                |                   |                   |                 |        |

| bit 7           | ENFLTA: Fa                               | ault A Input Enabl  | e bit            |                   |                   |                 |        |

|                 | 1 = Output                               | Compare Fault A     | input (OCFA) is  | s enabled         |                   |                 |        |

|                 | 0 = Output                               | Compare Fault A     | input (OCFA) is  | s disabled        |                   |                 |        |

| bit 6-5         | Unimpleme                                | ented: Read as '0   | ,                |                   |                   |                 |        |

| bit 4           | OCFLTA: PWM Fault A Condition Status bit |                     |                  |                   |                   |                 |        |

|                 |                                          | ault A condition c  |                  |                   |                   |                 |        |

|                 | 0 = No PW                                | M Fault A condition | on on the OCFA   | pin has occurre   | ed                |                 |        |

| bit 3           |                                          | : Trigger Status N  |                  |                   |                   |                 |        |

|                 |                                          | TAT (OCxCON2<       | ,                | /hen OCxRS = (    | OCxTMR or in s    | oftware         |        |

|                 | 0 = TRIGS                                | TAT is cleared on   | y by software    |                   |                   |                 |        |

**Note 1:** OCxR and OCxRS are double-buffered in PWM mode only.

| REGISTER 21-3: | CLCxSEL: CLCx INPUT MUX SELECT REGISTER |

|----------------|-----------------------------------------|

|----------------|-----------------------------------------|

| U-0          | R/W-0        | R/W-0                                                | R/W-0          | U-0               | R/W-0           | R/W-0            | R/W-0   |  |  |

|--------------|--------------|------------------------------------------------------|----------------|-------------------|-----------------|------------------|---------|--|--|

| —            |              | DS4<2:0>                                             |                | —                 |                 | DS3<2:0>         |         |  |  |

| bit 15       |              |                                                      |                |                   |                 |                  | bit 8   |  |  |

| U-0          | R/W-0        | R/W-0                                                | R/W-0          | U-0               | R/W-0           | R/W-0            | R/W-0   |  |  |

| 0-0          | 17/10-0      | DS2<2:0>                                             | FV VV-U        | 0-0               | 1.000-0         | DS1<2:0>         | N/ VV-U |  |  |

| bit 7        |              | D32~2.0>                                             |                | —                 |                 | D31~2.02         | bit 0   |  |  |

| Dit 7        |              |                                                      |                |                   |                 |                  | bit 0   |  |  |

| Legend:      |              |                                                      |                |                   |                 |                  |         |  |  |

| R = Readab   | ole bit      | W = Writable t                                       | oit            | U = Unimplen      | nented bit, rea | d as '0'         |         |  |  |

| -n = Value a | at POR       | '1' = Bit is set                                     |                | '0' = Bit is clea | ared            | x = Bit is unkno | own     |  |  |

|              |              |                                                      |                |                   |                 |                  |         |  |  |

| bit 15       | Unimpleme    | nted: Read as '0                                     | )'             |                   |                 |                  |         |  |  |

| bit 14-12    | DS4<2:0>: [  | Data Selection M                                     | UX 4 Signal S  | Selection bits    |                 |                  |         |  |  |

|              | See Table Ta | able 21-1 for inpu                                   | ut selections. |                   |                 |                  |         |  |  |

| bit 11       | Unimpleme    | nted: Read as '0                                     | )'             |                   |                 |                  |         |  |  |

| bit 10-8     | DS3<2:0>: [  | Data Selection M                                     | UX 3 Signal S  | Selection bits    |                 |                  |         |  |  |

|              | See Table Ta | able 21-1 for inpu                                   | ut selections. |                   |                 |                  |         |  |  |

| bit 7        | Unimpleme    | nted: Read as '0                                     | )'             |                   |                 |                  |         |  |  |

| bit 6-4      | DS2<2:0>: [  | DS2<2:0>: Data Selection MUX 2 Signal Selection bits |                |                   |                 |                  |         |  |  |

|              | See Table Ta | able 21-1 for inpu                                   | ut selections. |                   |                 |                  |         |  |  |

| bit 3        | Unimpleme    | nted: Read as 'o                                     | )'             |                   |                 |                  |         |  |  |

| bit 2-0      | DS1<2:0>: [  | Data Selection M                                     | UX 1 Signal S  | Selection bits    |                 |                  |         |  |  |

|              | See Table Ta | ble 21-1 for inpu                                    | ut selections. |                   |                 |                  |         |  |  |

|              |              |                                                      |                |                   |                 |                  |         |  |  |

| R/W-0, HS           | U-0                                                                                                                                                                                                                                                                                                                                                               | U-0              | U-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|-------------------|------------------|-----------------|---------|--|

| CSHRRDY             |                                                                                                                                                                                                                                                                                                                                                                   |                  |                | CSHRSKIP          | CSHRDIFF         | CSHREN          | CSHRRUN |  |

| bit 15              |                                                                                                                                                                                                                                                                                                                                                                   |                  |                |                   | •                |                 | bit 8   |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                   |                  |                |                   |                  |                 |         |  |

| U-0                 | U-0                                                                                                                                                                                                                                                                                                                                                               | U-0              | U-0            | U-0               | U-0              | U-0             | U-0     |  |

| —                   | _                                                                                                                                                                                                                                                                                                                                                                 | _                | —              | _                 | —                | —               |         |  |

| bit 7               |                                                                                                                                                                                                                                                                                                                                                                   |                  |                |                   |                  |                 | bit (   |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                   |                  |                |                   |                  |                 |         |  |

| Legend:             |                                                                                                                                                                                                                                                                                                                                                                   | HS = Hardwar     | e Settable bit |                   |                  |                 |         |  |

| R = Readable        | e bit                                                                                                                                                                                                                                                                                                                                                             | W = Writable I   | oit            | U = Unimplem      | nented bit, read | l as '0'        |         |  |

| -n = Value at       | POR                                                                                                                                                                                                                                                                                                                                                               | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |

| bit 14-12<br>bit 11 | <ul> <li>1 = Shared ADC core calibration is finished</li> <li>0 = Shared ADC core calibration is in progress</li> <li>Unimplemented: Read as '0'</li> <li>CSHRSKIP: Shared ADC Core Calibration Bypass bit</li> <li>1 = After power-up, the shared ADC core will not be calibrated</li> <li>0 = After power-up, the shared ADC core will be calibrated</li> </ul> |                  |                |                   |                  |                 |         |  |

| bit 10              | <b>CSHRDIFF:</b> Shared ADC Core Differential-Mode Calibration bit<br>1 = Shared ADC core will be calibrated in Differential Input mode<br>0 = Shared ADC core will be calibrated in Single-Ended Input mode                                                                                                                                                      |                  |                |                   |                  |                 |         |  |

| bit 9               | <ul> <li>CSHREN: Shared ADC Core Calibration Enable bit</li> <li>1 = Shared ADC core calibration bits (CSHRRDY, CSHRSKIP, CSHRDIFF and CSHRRUN) can be accessed by software</li> <li>0 = Shared ADC core calibration bits are disabled</li> </ul>                                                                                                                 |                  |                |                   |                  |                 |         |  |

| bit 8               | <ul> <li>Shared ADC core calibration bits are disabled</li> <li>CSHRRUN: Shared ADC Core Calibration Start bit</li> <li>1 = If this bit is set by software, the shared ADC core calibration cycle is started; this bit is cleare automatically by hardware</li> </ul>                                                                                             |                  |                |                   |                  |                 |         |  |

- 0 = Software can start the next calibration cycle

- bit 7-0 Unimplemented: Read as '0'

### 24.0 HIGH-SPEED ANALOG COMPARATOR

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/ 80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed Analog Comparator Module" (DS70005128) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The high-speed analog comparator module monitors current and/or voltage transients that may be too fast for the CPU and ADC to capture.

### 24.1 Features Overview

The Switch Mode Power Supply (SMPS) comparator module offers the following major features:

- Four Rail-to-Rail Analog Comparators

- Dedicated 12-Bit DAC for each Analog Comparator

- Up to Six Selectable Input Sources per Comparator:

- Four external inputs

- Two internal inputs from the PGAx module

- Programmable Comparator Hysteresis

- Programmable Output Polarity

- Up to Two DAC Outputs to Device Pins

- Multiple Voltage References for the DAC:

External References (EXTREF1 or EXTREF2)

- AVDD

- Interrupt Generation Capability

- Functional Support for PWMx:

- PWMx duty cycle control

- PWMx period control

- PWMx Fault detected

### TABLE 30-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS |                           |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |       |                     |  |  |

|--------------------|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|---------------------|--|--|

| Parameter<br>No.   | Тур.                      | Max. | Units                                                                                                                                                                                                                                                                                   | Conditions |       |                     |  |  |

| Operating Cur      | rent (IDD) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                         |            |       |                     |  |  |

| DC20d              | 8                         | 13   | mA                                                                                                                                                                                                                                                                                      | -40°C      |       |                     |  |  |

| DC20a              | 8                         | 13   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 2 2)/ | 10 MIPS             |  |  |

| DC20b              | 8                         | 13   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V  | TO MIPS             |  |  |

| DC20c              | 8                         | 13   | mA                                                                                                                                                                                                                                                                                      | +125°C     |       |                     |  |  |

| DC22d              | 12                        | 20   | mA                                                                                                                                                                                                                                                                                      | -40°C      |       | 20 MIPS             |  |  |

| DC22a              | 12                        | 20   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 2.01/ |                     |  |  |

| DC22b              | 12                        | 20   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V  | 20 MIPS             |  |  |

| DC22c              | 12                        | 20   | mA                                                                                                                                                                                                                                                                                      | +125°C     |       |                     |  |  |

| DC24d              | 19                        | 30   | mA                                                                                                                                                                                                                                                                                      | -40°C      |       |                     |  |  |

| DC24a              | 19                        | 30   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3∨  | 40 MIPS             |  |  |

| DC24b              | 19                        | 30   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V  | 40 IVIIPS           |  |  |

| DC24c              | 19                        | 30   | mA                                                                                                                                                                                                                                                                                      | +125°C     |       |                     |  |  |

| DC25d              | 27                        | 42   | mA                                                                                                                                                                                                                                                                                      | -40°C      |       |                     |  |  |

| DC25a              | 27                        | 42   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 2.01/ |                     |  |  |

| DC25b              | 27                        | 42   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V  | 60 MIPS             |  |  |

| DC25c              | 27                        | 42   | mA                                                                                                                                                                                                                                                                                      | +125°C     |       |                     |  |  |

| DC26d              | 30                        | 46   | mA                                                                                                                                                                                                                                                                                      | -40°C      |       |                     |  |  |

| DC26a              | 30                        | 46   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V  | 70 MIPS             |  |  |

| DC26b              | 30                        | 46   | mA                                                                                                                                                                                                                                                                                      | +85°C      |       |                     |  |  |

| DC27d              | 57                        | 75   | mA                                                                                                                                                                                                                                                                                      | -40°C      |       | 70.14120            |  |  |

| DC27a              | 57                        | 75   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V  | 70 MIPS<br>(Note 2) |  |  |

| DC27b              | 57                        | 75   | mA                                                                                                                                                                                                                                                                                      | +85°C      |       |                     |  |  |

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- · CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating or being clocked (all defined PMDx bits are set)

- CPU is executing while(1) statement

- JTAG is disabled

- **2:** For this specification, the following test conditions apply:

- · APLL clock is enabled

- All 8 PWMs enabled and operating at maximum speed (PTCON2<2:0> = 000), PTPER = 1000h, 50% duty cycle

- All other peripherals are disabled (corresponding PMDx bits are set)

| DC CHARACTERISTICS |        |                                                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq T_A \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq T_A \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                                                                                                                                                                                     |

|--------------------|--------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                | Min.                                                                                                                                                                                                                                                                                      | Тур. <sup>(1)</sup> | Max. | Units | Conditions                                                                                                                                                                                          |

| DI50               | lıL    | Input Leakage Current <sup>(2,3)</sup><br>I/O Pins 5V Tolerant <sup>(4)</sup> | -1                                                                                                                                                                                                                                                                                        | _                   | +1   | μΑ    | $Vss \leq VPIN \leq VDD,$ pin at high-impedance                                                                                                                                                     |

| DI51               |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                       | -1                                                                                                                                                                                                                                                                                        | —                   | +1   | μΑ    | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ pin \text{ at high-impedance}, \\ -40^\circC \leq TA \leq +85^\circC \end{array}$                                                       |

| DI51a              |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                       | -1                                                                                                                                                                                                                                                                                        | —                   | +1   | μΑ    | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +85^{\circ}C$                                                                                                       |

| DI51b              |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                       | -1                                                                                                                                                                                                                                                                                        | —                   | +1   | μA    | $\label{eq:VSS} \begin{array}{l} \forall \text{VSS} \leq \text{VPIN} \leq \text{VDD}, \\ \text{pin at high-impedance}, \\ -40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C} \end{array}$ |

| DI51c              |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                       | -1                                                                                                                                                                                                                                                                                        | —                   | +1   | μA    | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +125^{\circ}C$                                                                                                      |

| DI55               |        | MCLR                                                                          | -5                                                                                                                                                                                                                                                                                        | —                   | +5   | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                                                                            |

| DI56               |        | OSC1                                                                          | -5                                                                                                                                                                                                                                                                                        | —                   | +5   | μA    | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$                                                                                           |

### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

Note 1: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

5: VIL Source < (Vss – 0.3). Characterized but not tested.

**6:** VIH Source > (VDD + 0.3) for pins that are not 5V tolerant only.

7: Digital 5V tolerant pins do not have internal high-side diodes to VDD and cannot tolerate any "positive" input injection current.

8: Injection Currents > | 0 | can affect the ADC results by approximately 4-6 counts.

**9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

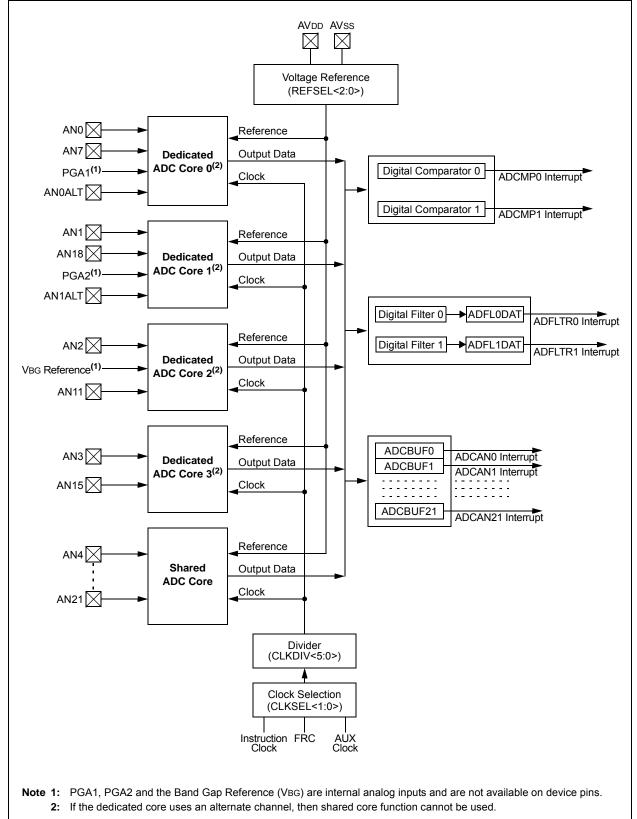

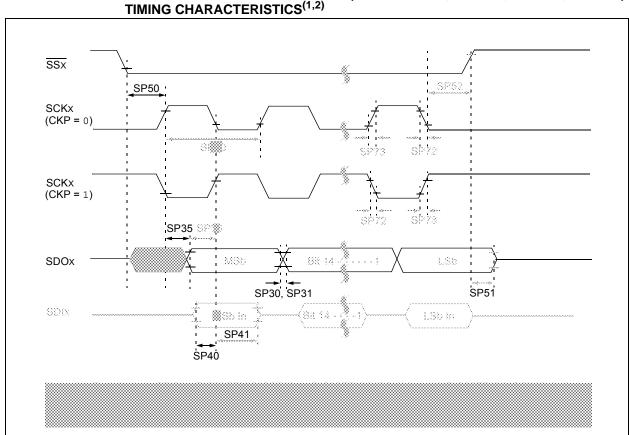

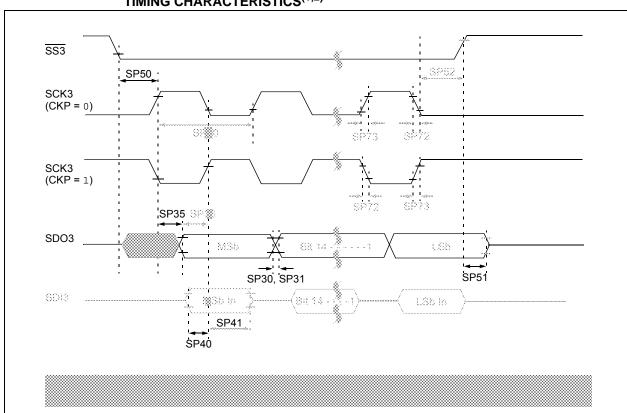

### TABLE 30-31: SPI1, SPI2 AND SPI3 MAXIMUM DATA/CLOCK RATE SUMMARY<sup>(1)</sup>

| AC CHARA             | CTERISTICS                               |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |

| 15 MHz               | Table 30-32                              | _                                           | _                                                     | 0,1 | 0,1 | 0,1 |  |

| 9 MHz                | _                                        | Table 30-33                                 | —                                                     | 1   | 0,1 | 1   |  |

| 9 MHz                | —                                        | Table 30-34                                 | —                                                     | 0   | 0,1 | 1   |  |

| 15 MHz               | —                                        | —                                           | Table 30-35                                           | 1   | 0   | 0   |  |