Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Becano                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 33                                                                              |

| Program Memory Size        | 64KB (64K × 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 17x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

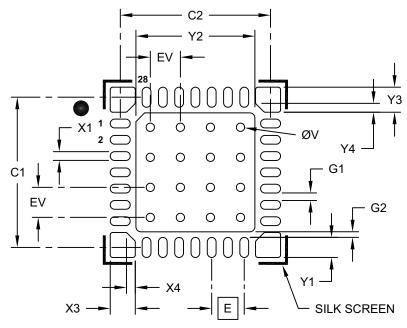

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs804-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz < FIN < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings, after a POR with an oscillator frequency outside this range, will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

### 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

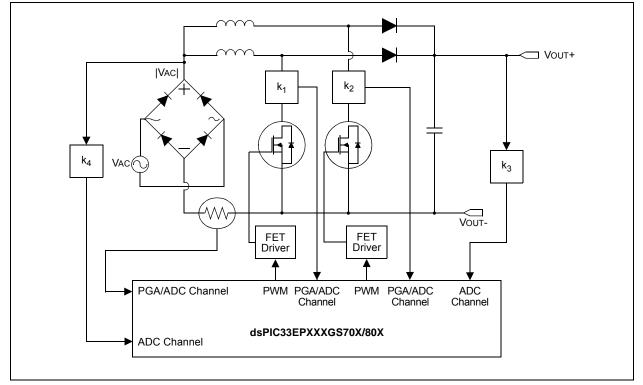

# Power Factor Correction (PFC)

- Interleaved PFC

- Interneaved FFC

- Critical Conduction PFC

- Bridgeless PFC

- DC/DC Converters

- Buck, Boost, Forward, Flyback, Push-Pull

**Targeted Applications**

- Half/Full-Bridge

- Phase-Shift Full-Bridge

- Resonant Converters

- DC/AC

2.9

- Half/Full-Bridge Inverter

- Resonant Inverter

Examples of typical application connections are shown in Figure 2-4 through Figure 2-6.

#### FIGURE 2-4: INTERLEAVED PFC

### REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

| U-0          | U-0                 | U-0                                  | U-0            | U-0                                | U-0     | U-0                | U-0   |  |

|--------------|---------------------|--------------------------------------|----------------|------------------------------------|---------|--------------------|-------|--|

| —            | —                   | —                                    | —              | —                                  | —       | —                  | —     |  |

| bit 15       |                     |                                      |                |                                    |         | bit 8              |       |  |

|              |                     |                                      |                |                                    |         |                    |       |  |

| U-0          | U-0                 | U-0                                  | U-0            | R-1                                | R-1     | R-1                | R-1   |  |

| _            | —                   |                                      | —              |                                    | LSTCH   | 1<3:0>             |       |  |

| bit 7        |                     |                                      |                |                                    |         |                    | bit 0 |  |

|              |                     |                                      |                |                                    |         |                    |       |  |

| Legend:      |                     |                                      |                |                                    |         |                    |       |  |

| R = Readab   | le bit              | W = Writable                         | bit            | U = Unimplemented bit, read as '0' |         |                    |       |  |

| -n = Value a | It POR              | '1' = Bit is set                     |                | '0' = Bit is cleared               |         | x = Bit is unknown |       |  |

|              |                     |                                      |                |                                    |         |                    |       |  |

| bit 15-4     | Unimplemen          | ted: Read as '                       | 0'             |                                    |         |                    |       |  |

| bit 3-0      | LSTCH<3:0>          | : Last DMA Co                        | ntroller Chanr | nel Active Statu                   | us bits |                    |       |  |

|              | 1111 <b>= No Di</b> | MA transfer ha                       | s occurred sin | ce system Res                      | set     |                    |       |  |

|              | 1110 <b>= Rese</b>  | rved                                 |                |                                    |         |                    |       |  |

|              | •                   |                                      |                |                                    |         |                    |       |  |

|              | •                   |                                      |                |                                    |         |                    |       |  |

|              | •                   |                                      |                |                                    |         |                    |       |  |

|              | 0100 = Reser        |                                      |                | Observal 0                         |         |                    |       |  |

|              |                     | lata transfer wa                     |                |                                    |         |                    |       |  |

|              |                     | data transfer wa                     |                |                                    |         |                    |       |  |

|              |                     | data transfer wa<br>data transfer wa |                |                                    |         |                    |       |  |

|              |                     |                                      | as nanuleu by  |                                    |         |                    |       |  |

| U-0                         | R/W-0      | R/W-0                                                        | R/W-0         | R/W-0                | R/W-0            | R/W-0              | R/W-0  |

|-----------------------------|------------|--------------------------------------------------------------|---------------|----------------------|------------------|--------------------|--------|

| —                           | RP17R6     | RP17R5                                                       | RP17R4        | RP17R3               | RP17R2           | RP17R1             | RP17R0 |

| bit 15                      |            |                                                              |               |                      |                  |                    | bit 8  |

|                             |            |                                                              |               |                      |                  |                    |        |

| U-0                         | R/W-0      | R/W-0                                                        | R/W-0         | R/W-0                | R/W-0            | R/W-0              | R/W-0  |

| —                           | RP16R6     | RP16R5                                                       | RP16R4        | RP16R3               | RP16R2           | RP16R1             | RP16R0 |

| bit 7                       |            |                                                              |               |                      |                  |                    | bit (  |

| Legend:                     |            |                                                              |               |                      |                  |                    |        |

| R = Readable                | e bit      | W = Writable                                                 | bit           | U = Unimpler         | nented bit, read | l as '0'           |        |

| -n = Value at POR '1' = Bit |            | '1' = Bit is set                                             |               | '0' = Bit is cleared |                  | x = Bit is unknown |        |

| bit 15<br>bit 14-8          | RP17R<6:0> | <b>ited:</b> Read as '<br>: Peripheral Ou<br>-13 for periphe | tput Function | •                    | RP17 Output F    | Pin bits           |        |

bit 7 Unimplemented: Read as '0'

| bit 6-0 | <b>RP16R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP16 Output Pin bits |

|---------|-----------------------------------------------------------------------------------------|

|         | (see Table 11-13 for peripheral function numbers)                                       |

#### REGISTER 11-34: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0                                | R/W-0                                                                                                                                     | R/W-0          | R/W-0                | R/W-0                              | R/W-0              | R/W-0  | R/W-0  |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------|------------------------------------|--------------------|--------|--------|

| _                                  | RP19R6                                                                                                                                    | RP19R5         | RP19R4               | RP19R3                             | RP19R2             | RP19R1 | RP19R0 |

| bit 15                             |                                                                                                                                           |                |                      |                                    |                    |        | bit 8  |

|                                    |                                                                                                                                           |                |                      |                                    |                    |        |        |

| U-0                                | R/W-0                                                                                                                                     | R/W-0          | R/W-0                | R/W-0                              | R/W-0              | R/W-0  | R/W-0  |

| —                                  | RP18R6                                                                                                                                    | RP18R5         | RP18R4               | RP18R3                             | RP18R2             | RP18R1 | RP18R0 |

| bit 7                              |                                                                                                                                           |                |                      |                                    |                    |        | bit 0  |

|                                    |                                                                                                                                           |                |                      |                                    |                    |        |        |

| Legend:                            |                                                                                                                                           |                |                      |                                    |                    |        |        |

| R = Readable bit W = Writable bit  |                                                                                                                                           |                | bit                  | U = Unimplemented bit, read as '0' |                    |        |        |

| -n = Value at POR '1' = Bit is set |                                                                                                                                           |                | '0' = Bit is cleared |                                    | x = Bit is unknown |        |        |

|                                    |                                                                                                                                           |                |                      |                                    |                    |        |        |

| bit 15                             | Unimplemen                                                                                                                                | ted: Read as ' | 0'                   |                                    |                    |        |        |

| bit 14-8                           | <b>RP19R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP19 Output Pin bits (see Table 11-13 for peripheral function numbers) |                |                      |                                    |                    |        |        |

bit 7 Unimplemented: Read as '0'

bit 6-0 **RP18R<6:0>:** Peripheral Output Function is Assigned to RP18 Output Pin bits (see Table 11-13 for peripheral function numbers)

## REGISTER 16-10: MDC: PWMx MASTER DUTY CYCLE REGISTER<sup>(1,2)</sup>

| R/W-0                                                                   | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|-------------------------------------------------------------------------|-------|-------|-------|------------------------------------|-------|-------|-------|

|                                                                         |       |       | MDC   | C<15:8>                            |       |       |       |

| bit 15                                                                  |       |       |       |                                    |       |       | bit 8 |

|                                                                         |       |       |       |                                    |       |       |       |

| R/W-0                                                                   | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                                                         |       |       | MD    | C<7:0>                             |       |       |       |

| bit 7                                                                   |       |       |       |                                    |       |       | bit 0 |

|                                                                         |       |       |       |                                    |       |       |       |

| Legend:                                                                 |       |       |       |                                    |       |       |       |

| R = Readable bit W = Writable bit                                       |       |       | oit   | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkn |       |       |       | nown                               |       |       |       |

bit 15-0 MDC<15:0>: PWMx Master Duty Cycle Value bits

**Note 1:** The smallest pulse width that can be generated on the PWMx output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period – 0x0008.

2: As the duty cycle gets closer to 0% or 100% of the PWMx period (0 to 40 ns, depending on the mode of operation), PWMx duty cycle resolution will increase from 1 to 3 LSBs.

#### REGISTER 16-11: PWMKEY: PWMx PROTECTION LOCK/UNLOCK KEY REGISTER

| bit  |

|------|

|      |

| 'W-0 |

|      |

| bit  |

|      |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PWMKEY<15:0>:** PWMx Protection Lock/Unlock Key Value bits

|                 | R/W-1                                                                                              | R/W-0                                | R/W-0                             | R/W-0                 | R/W-0                 | R/W-0           | R/W-0  |  |

|-----------------|----------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------|-----------------------|-----------------------|-----------------|--------|--|

| PENH            | PENL                                                                                               | POLH                                 | POLL                              | PMOD1 <sup>(1)</sup>  | PMOD0 <sup>(1)</sup>  | OVRENH          | OVRENL |  |

| bit 15          |                                                                                                    |                                      |                                   |                       |                       |                 | bit    |  |

|                 |                                                                                                    |                                      |                                   |                       |                       |                 |        |  |

| R/W-0           | R/W-0                                                                                              | R/W-0                                | R/W-0                             | R/W-0                 | R/W-0                 | R/W-0           | R/W-0  |  |

| OVRDAT1         | OVRDAT0                                                                                            | FLTDAT1 <sup>(2)</sup>               | FLTDAT0 <sup>(2)</sup>            | CLDAT1 <sup>(2)</sup> | CLDAT0 <sup>(2)</sup> | SWAP            | OSYNC  |  |

| bit 7           |                                                                                                    |                                      |                                   |                       |                       |                 | bit    |  |

|                 |                                                                                                    |                                      |                                   |                       |                       |                 |        |  |

| Legend:         |                                                                                                    |                                      |                                   |                       |                       |                 |        |  |

| R = Readable    |                                                                                                    | W = Writable                         |                                   | •                     | nented bit, read      |                 |        |  |

| -n = Value at F | POR                                                                                                | '1' = Bit is set                     |                                   | '0' = Bit is clea     | ared                  | x = Bit is unkr | nown   |  |

| bit 15          |                                                                                                    | xH Output Pin                        | Ownorship hit                     |                       |                       |                 |        |  |

| 511 15          |                                                                                                    | •                                    | he PWMxH pin                      |                       |                       |                 |        |  |

|                 |                                                                                                    | dule controls th                     |                                   |                       |                       |                 |        |  |

| bit 14          |                                                                                                    | L Output Pin C                       | -                                 |                       |                       |                 |        |  |

|                 |                                                                                                    | •                                    | he PWMxL pin                      |                       |                       |                 |        |  |

|                 |                                                                                                    | dule controls th                     |                                   |                       |                       |                 |        |  |

| bit 13          | POLH: PWM                                                                                          | xH Output Pin I                      | Polarity bit                      |                       |                       |                 |        |  |

|                 | 1 = PWMxH p                                                                                        | oin is active-low                    | /                                 |                       |                       |                 |        |  |

|                 |                                                                                                    | oin is active-hig                    |                                   |                       |                       |                 |        |  |

| bit 12          | POLL: PWMx                                                                                         | L Output Pin F                       | olarity bit                       |                       |                       |                 |        |  |

|                 |                                                                                                    | in is active-low<br>in is active-hig |                                   |                       |                       |                 |        |  |

| bit 11-10       | PMOD<1:0>:                                                                                         | PWMx I/O Pin                         | Mode bits <sup>(1)</sup>          |                       |                       |                 |        |  |

|                 | 11 = PWMx I/                                                                                       | /O pin pair is in                    | the True Indep                    | endent Output         | mode                  |                 |        |  |

|                 |                                                                                                    |                                      | the Push-Pull (                   | •                     |                       |                 |        |  |

|                 |                                                                                                    |                                      | the Redundant                     |                       |                       |                 |        |  |

|                 |                                                                                                    | · ·                                  | the Compleme                      |                       | node                  |                 |        |  |

| bit 9           |                                                                                                    |                                      | for PWMxH Pin                     |                       |                       |                 |        |  |

|                 |                                                                                                    |                                      | for output on the F               |                       | 1                     |                 |        |  |

| bit 8           | -                                                                                                  | -                                    |                                   | -                     |                       |                 |        |  |

| JILO            | OVRENL: Override Enable for PWMxL Pin bit<br>1 = OVRDAT0 provides data for output on the PWMxL pin |                                      |                                   |                       |                       |                 |        |  |

|                 |                                                                                                    | -                                    | es data for the F                 |                       |                       |                 |        |  |

| bit 7-6         | •                                                                                                  | •                                    | /MxH, PWMxL                       |                       | e is Enabled bi       | its             |        |  |

|                 |                                                                                                    |                                      | provides data fo                  |                       |                       |                 |        |  |

|                 |                                                                                                    |                                      | provides data fo                  |                       |                       |                 |        |  |

| bit 5-4         |                                                                                                    | -                                    | MxH and PWM                       | -                     |                       | Enabled bits(2) |        |  |

|                 |                                                                                                    |                                      | = 0: Normal Fa                    |                       |                       |                 |        |  |

|                 |                                                                                                    |                                      | AT1 provides the                  |                       | PWMxH pin.            |                 |        |  |

|                 | If Fault is activ                                                                                  | ve, then FLTDA                       | AT0 provides the                  | e state for the       | PWMxL pin.            |                 |        |  |

|                 |                                                                                                    |                                      |                                   |                       |                       |                 |        |  |

|                 | IFLTMOD (FC                                                                                        |                                      |                                   |                       |                       |                 |        |  |

|                 | If current limit                                                                                   | is active, then                      | FLTDAT1 provi<br>AT0 provides the | ides the state f      | for the PWMxH         | l pin.          |        |  |

#### REGISTER 16-20: IOCONX: PWMx I/O CONTROL REGISTER (x = 1 to 8)

2: State represents the active/inactive state of the PWMx depending on the POLH and POLL bits settings.

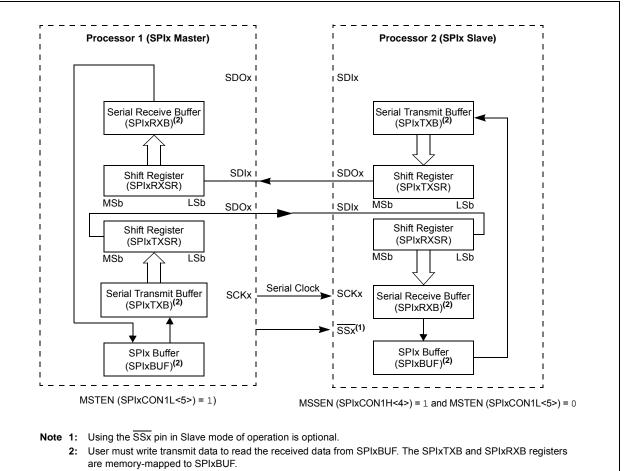

To set up the SPIx module for Audio mode:

- 1. Clear the SPIxBUFL and SPIxBUFH registers.

- 2. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- a) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with AUDEN (SPIxCON1H<15>) = 1.

- 4. Clear the SPIROV bit (SPIxSTATL<6>).

- Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- 6. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

#### REGISTER 18-1: SPIxCON1L: SPIx CONTROL REGISTER 1 LOW

| Legend:<br>R = Readable |       | W = Writable |        |                         | ented bit read          | (0)   |                    |

|-------------------------|-------|--------------|--------|-------------------------|-------------------------|-------|--------------------|

| bit 7                   |       |              |        |                         |                         |       | bit 0              |

| SSEN <sup>(2)</sup>     | CKP   | MSTEN        | DISSDI | DISSCK                  | MCLKEN <sup>(3)</sup>   | SPIFE | ENHBUF             |

| R/W-0                   | R/W-0 | R/W-0        | R/W-0  | R/W-0                   | R/W-0                   | R/W-0 | R/W-0              |

| bit 15                  |       |              |        |                         |                         |       | bit 8              |

| SPIEN                   | _     | SPISIDL      | DISSDO | MODE32 <sup>(1,4)</sup> | MODE16 <sup>(1,4)</sup> | SMP   | CKE <sup>(1)</sup> |

| R/W-0                   | U-0   | R/W-0        | R/W-0  | R/W-0                   | R/W-0                   | R/W-0 | R/W-0              |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 15 SPIEN: SPIx On bit

- 1 = Enables module

- 0 = Turns off and resets module, disables clocks, disables interrupt event generation, allows SFR modifications

#### bit 14 Unimplemented: Read as '0'

- bit 13 SPISIDL: SPIx Stop in Idle Mode bit

- 1 = Halts in CPU Idle mode

- 0 = Continues to operate in CPU Idle mode

#### bit 12 DISSDO: Disable SDOx Output Port bit

1 = SDOx pin is not used by the module; pin is controlled by port function

#### 0 = SDOx pin is controlled by the module

#### bit 11-10 MODE32 and MODE16: Serial Word Length Select bits<sup>(1,4)</sup>

| MODE32 | MODE16 | AUDEN | Communication                                         |

|--------|--------|-------|-------------------------------------------------------|

| 1      | x      |       | 32-Bit                                                |

| 0      | 1      | 0     | 16-Bit                                                |

| 0      | 0      |       | 8-Bit                                                 |

| 1      | 1      |       | 24-Bit Data, 32-Bit FIFO, 32-Bit Channel/64-Bit Frame |

| 1      | 0      | 1     | 32-Bit Data, 32-Bit FIFO, 32-Bit Channel/64-Bit Frame |

| 0      | 1      | T     | 16-Bit Data, 16-Bit FIFO, 32-Bit Channel/64-Bit Frame |

| 0      | 0      |       | 16-Bit FIFO, 16-Bit Channel/32-Bit Frame              |

#### **Note 1:** When AUDEN (SPIxCON1H<15>) = 1, this module functions as if CKE = 0, regardless of its actual value.

- 2: When FRMEN = 1, SSEN is not used.

- 3: MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows FRMSYPW.

| REGISTER 18-4: SPIxS | TATL: SPIX STATUS REGISTER LOW |

|----------------------|--------------------------------|

|----------------------|--------------------------------|

| U-0           | U-0                            | U-0                                         | R/C-0, HS      | R-0, HSC          | U-0           | U-0             | R-0, HSC              |

|---------------|--------------------------------|---------------------------------------------|----------------|-------------------|---------------|-----------------|-----------------------|

| _             | _                              | —                                           | FRMERR         | SPIBUSY           |               | —               | SPITUR <sup>(1)</sup> |

| bit 15        |                                |                                             |                |                   |               | ·               | bit 8                 |

|               |                                |                                             |                |                   |               |                 |                       |

| R-0, HSC      | R/C-0, HS                      | R-1, HSC                                    | U-0            | R-1, HSC          | U-0           | R-0, HSC        | R-0, HSC              |

| SRMT          | SPIROV                         | SPIRBE                                      | —              | SPITBE            | —             | SPITBF          | SPIRBF                |

| bit 7         |                                |                                             |                |                   |               |                 | bit                   |

| Legend:       |                                | C = Clearable                               | hit            | U = Unimplerr     | ented read as | : 'O'           |                       |

| R = Readabl   | e hit                          | W = Writable b                              |                | HSC = Hardw       |               |                 |                       |

| -n = Value at |                                | '1' = Bit is set                            | it.            | '0' = Bit is clea |               | HS = Hardwar    | e Settable bit        |

|               |                                | 1 Dicio Cot                                 |                | Bit lo biod       |               |                 |                       |

| bit 15-13     | Unimplemen                     | ted: Read as '0                             | )'             |                   |               |                 |                       |

| bit 12        | FRMERR: SF                     | Plx Frame Error                             | Status bit     |                   |               |                 |                       |

|               | 1 = Frame er                   | ror is detected                             |                |                   |               |                 |                       |

|               | 0 = No frame                   | error is detecte                            | d              |                   |               |                 |                       |

| bit 11        |                                | Plx Activity State                          |                |                   |               |                 |                       |

|               |                                | currently busy                              |                |                   |               |                 |                       |

| bit 10-9      | •                              | ng transactions<br>i <b>ted:</b> Read as '0 |                | d)                |               |                 |                       |

|               | •                              | x Transmit Und                              |                | (1)               |               |                 |                       |

| bit 8         |                                | buffer has enco                             |                |                   | condition     |                 |                       |

|               |                                | buffer does not                             |                |                   |               |                 |                       |

| bit 7         | SRMT: Shift F                  | Register Empty                              | Status bit     |                   |               |                 |                       |

|               |                                |                                             |                | , neither SPIxT   | XB or SPIxT>  | (SR contains da | ta to transmit)       |

|               |                                | r pending trans                             |                |                   |               |                 |                       |

| bit 6         |                                | x Receive Over                              |                |                   |               |                 |                       |

|               | 1 = A new by<br>0 = No overflo |                                             | rd has been co | ompletely recei   | ved when the  | SPIxRXB was f   | ull                   |

| bit 5         | SPIRBE: SPI                    | x RX Buffer Em                              | pty Status bit |                   |               |                 |                       |

|               | 1 = RX buffer                  |                                             |                |                   |               |                 |                       |

|               | 0 = RX buffer                  |                                             |                |                   |               |                 |                       |

|               | Standard Buff                  |                                             |                | IC is read from   |               | RXB. Automatio  | ally alcored i        |

|               |                                | en SPIx transfe                             |                |                   |               |                 |                       |

|               | Enhanced Bu                    |                                             |                |                   |               |                 |                       |

|               | Indicates RXE                  |                                             | 0000.          |                   |               |                 |                       |

|               |                                |                                             |                |                   |               |                 |                       |

**Note 1:** SPITUR is cleared when SPIEN = 0. When IGNTUR = 1, SPITUR provides dynamic status of the Transmit Underrun condition, but does not stop RX/TX operation and does not need to be cleared by software.

# REGISTER 22-32: ADCMPxENL: ADC DIGITAL COMPARATOR x CHANNEL ENABLE REGISTER LOW (x = 0 or 1)

| bit 15      | R/W/0  | R/W-0 |

|-------------|--------|-------|-------|-------|-------|-------|-------|-------|

| bit 15      |        |       |       |       |       |       |       |       |

|             | bit 15 |       |       |       |       |       |       | bit   |

| CMPEN<15:8> | _      | R/W-0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **CMPEN<15:0>:** Comparator Enable for Corresponding Input Channels bits

0 = Conversion result for corresponding channel is not used by the comparator

# REGISTER 22-33: ADCMPxENH: ADC DIGITAL COMPARATOR x CHANNEL ENABLE REGISTER HIGH (x = 0 or 1)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|---------|-------|-------|

| —     | _   |       |       | CMPEN | <21:16> |       |       |

| bit 7 |     |       |       |       |         |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0

CMPEN<21:16>: Comparator Enable for Corresponding Input Channels bits

1 = Conversion result for corresponding channel is used by the comparator

0 = Conversion result for corresponding channel is not used by the comparator

<sup>1 =</sup> Conversion result for corresponding channel is used by the comparator

| R/W-0         | R/W-0                                                   | R/W-0                                                                                          | R/W-0                                     | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |

|---------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------|-------|--------------------|-------|--|

| F7BP3         | F7BP2                                                   | F7BP1                                                                                          | F7BP0                                     | F6BP3                              | F6BP2 | F6BP1              | F6BP0 |  |

| bit 15        | •                                                       |                                                                                                |                                           |                                    | ·     |                    | bit 8 |  |

|               |                                                         |                                                                                                |                                           |                                    |       |                    |       |  |

| R/W-0         | R/W-0                                                   | R/W-0                                                                                          | R/W-0                                     | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |

| F5BP3         | F5BP2                                                   | F5BP1                                                                                          | F5BP0                                     | F4BP3                              | F4BP2 | F4BP1              | F4BP0 |  |

| bit 7         | ·                                                       |                                                                                                |                                           | ·                                  | •     |                    | bit 0 |  |

|               |                                                         |                                                                                                |                                           |                                    |       |                    |       |  |

| Legend:       |                                                         |                                                                                                |                                           |                                    |       |                    |       |  |

| R = Readable  | e bit                                                   | W = Writable bit                                                                               |                                           | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value at | POR                                                     | '1' = Bit is set                                                                               |                                           | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |

| bit 15-12     | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>•<br>• | RX Buffer Mash<br>hits received ir<br>hits received ir<br>hits received ir<br>hits received ir | RX FIFO bu<br>RX Buffer 14<br>RX Buffer 1 | ffer                               |       |                    |       |  |

#### REGISTER 23-13: CxBUFPNT2: CANx FILTERS 4-7 BUFFER POINTER REGISTER 2

| bit 11-8 | F6BP<3:0>: RX Buffer Mask for Filter 6 bits | (same values as bits 15-12) |

|----------|---------------------------------------------|-----------------------------|

|          |                                             |                             |

| bit 7-4 <b>F5BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 5 bits (same values as bits 15-12) |

|----------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------|

| bit 3-0 | F4BP<3:0>: RX Buffer Mask for Filter 4 bits | (same values as bits 15-12) |

|---------|---------------------------------------------|-----------------------------|

|         |                                             |                             |

#### REGISTER 23-14: CxBUFPNT3: CANx FILTERS 8-11 BUFFER POINTER REGISTER 3

| R/W-0  |  |

|--------|--------|--------|--------|--------|--------|--------|--------|--|

| F11BP3 | F11BP2 | F11BP1 | F11BP0 | F10BP3 | F10BP2 | F10BP1 | F10BP0 |  |

| bit 15 |        |        |        |        |        |        |        |  |

|        |        |        |        |        |        |        |        |  |

| R/W-0  |  |

| F9BP3  | F9BP2  | F9BP1  | F9BP0  | F8BP3  | F8BP2  | F8BP1  | F8BP0  |  |

| bit 7  |        |        | •      | •      |        | •      | bit 0  |  |

|        |        |        |        |        |        |        |        |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

© 2016-2017 Microchip Technology Inc.

#### 23.4 CAN Message Buffers

CAN Message Buffers are part of RAM memory. They are not CAN Special Function Registers. The user application must directly write into the RAM area that is configured for CAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: CANx MESSAGE BUFFER WORD 0

| U-0                                                                                                                           | U-0          | U-0                                          | R/W-x     | R/W-x                              | R/W-x | R/W-x | R/W-x |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------|-----------|------------------------------------|-------|-------|-------|--|--|--|--|--|--|--|--|

| _                                                                                                                             | _            | _                                            | SID10     | SID9                               | SID8  | SID7  | SID6  |  |  |  |  |  |  |  |  |

| bit 15                                                                                                                        |              |                                              |           | •<br>•                             |       |       | bit 8 |  |  |  |  |  |  |  |  |

|                                                                                                                               |              |                                              |           |                                    |       |       |       |  |  |  |  |  |  |  |  |

| R/W-x                                                                                                                         | R/W-x        | R/W-x                                        | R/W-x     | R/W-x                              | R/W-x | R/W-x | R/W-x |  |  |  |  |  |  |  |  |

| SID5                                                                                                                          | SID4         | SID3                                         | SID2      | SID1                               | SID0  | SRR   | IDE   |  |  |  |  |  |  |  |  |

| bit 7                                                                                                                         |              |                                              |           |                                    |       |       | bit 0 |  |  |  |  |  |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'                              |              |                                              |           |                                    |       |       |       |  |  |  |  |  |  |  |  |

| -n = Value at                                                                                                                 | t POR        | '1' = Bit is set                             |           | '0' = Bit is cleared x = Bit is un |       |       | known |  |  |  |  |  |  |  |  |

|                                                                                                                               |              |                                              |           |                                    |       |       |       |  |  |  |  |  |  |  |  |

| bit 15-13                                                                                                                     | Unimplemen   | ted: Read as '                               | 0'        |                                    |       |       |       |  |  |  |  |  |  |  |  |

| bit 12-2                                                                                                                      | SID<10:0>: S | Standard Identif                             | ier bits  |                                    |       |       |       |  |  |  |  |  |  |  |  |

| bit 1                                                                                                                         | SRR: Substit | ute Remote Re                                | quest bit |                                    |       |       |       |  |  |  |  |  |  |  |  |

|                                                                                                                               | When IDE =   | 0:                                           |           |                                    |       |       |       |  |  |  |  |  |  |  |  |

|                                                                                                                               | 1 = Message  | 1 = Message will request remote transmission |           |                                    |       |       |       |  |  |  |  |  |  |  |  |

|                                                                                                                               | 0 = Normal m | 0 = Normal message                           |           |                                    |       |       |       |  |  |  |  |  |  |  |  |

|                                                                                                                               | When IDE =   | When IDE = 1:                                |           |                                    |       |       |       |  |  |  |  |  |  |  |  |

|                                                                                                                               | The SRR bit  | must be set to '                             | 1'.       |                                    |       |       |       |  |  |  |  |  |  |  |  |

| bit 0                                                                                                                         | IDE: Extende | d Identifier bit                             |           |                                    |       |       |       |  |  |  |  |  |  |  |  |

| <ul> <li>1 = Message will transmit an Extended Identifier</li> <li>0 = Message will transmit a Standard Identifier</li> </ul> |              |                                              |           |                                    |       |       |       |  |  |  |  |  |  |  |  |

|                                                                                                                               |              |                                              |           |                                    |       |       |       |  |  |  |  |  |  |  |  |

#### BUFFER 21-2: CANx MESSAGE BUFFER WORD 1

| U-0                              | U-0   | U-0              | U-0          | R/W-x                               | R/W-x | R/W-x   | R/W-x |

|----------------------------------|-------|------------------|--------------|-------------------------------------|-------|---------|-------|

| _                                |       | —                |              |                                     | EID   | <17:14> |       |

| bit 15                           |       |                  |              |                                     |       |         | bit 8 |

|                                  |       |                  |              |                                     |       |         |       |

| R/W-x                            | R/W-x | R/W-x            | R/W-x        | R/W-x                               | R/W-x | R/W-x   | R/W-x |

|                                  |       |                  | EID          | <13:6>                              |       |         |       |

| bit 7                            |       |                  |              |                                     |       |         | bit ( |

| Legend:                          |       |                  |              |                                     |       |         |       |

| R = Readable bit W = Writable bi |       | bit              | U = Unimplen | U = Unimplemented bit, read as '0'  |       |         |       |

| -n = Value at POR                |       | '1' = Bit is set |              | '0' = Bit is cleared x = Bit is unk |       | nown    |       |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

#### BUFFER 21-5: CANx MESSAGE BUFFER WORD 4

| R/W-x                              | R/W-x | R/W-x | R/W-x | R/W-x                                             | R/W-x | R/W-x | R/W-x |

|------------------------------------|-------|-------|-------|---------------------------------------------------|-------|-------|-------|

|                                    |       |       | Byte  | 3<15:8>                                           |       |       |       |

| bit 15                             |       |       | -     |                                                   |       |       | bit 8 |

|                                    |       |       |       |                                                   |       |       |       |

| R/W-x                              | R/W-x | R/W-x | R/W-x | R/W-x                                             | R/W-x | R/W-x | R/W-x |

|                                    |       |       | Byte  | 2<7:0>                                            |       |       |       |

| bit 7                              |       |       |       |                                                   |       |       | bit 0 |

| Legend:                            |       |       |       |                                                   |       |       |       |

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplemented bit, read as '0'                |       |       |       |

| -n = Value at POR (1' = Bit is set |       |       |       | $0^{\circ}$ = Bit is cleared $x = Bit is unknown$ |       |       |       |

bit 15-8 Byte 3<15:8>: CANx Message Byte 3 bits

bit 7-0 Byte 2<7:0>: CANx Message Byte 2 bits

#### BUFFER 21-6: CANx MESSAGE BUFFER WORD 5

| R/W-x                              | R/W-x | R/W-x            | R/W-x | R/W-x                | R/W-x           | R/W-x              | R/W-x |

|------------------------------------|-------|------------------|-------|----------------------|-----------------|--------------------|-------|

|                                    |       |                  | Byte  | 5<15:8>              |                 |                    |       |

| bit 15                             |       |                  |       |                      |                 |                    | bit 8 |

| R/W-x                              | R/W-x | R/W-x            | R/W-x | R/W-x                | R/W-x           | R/W-x              | R/W-x |

|                                    |       |                  | Byte  | 4<7:0>               |                 |                    |       |

| bit 7                              |       |                  |       |                      |                 |                    | bit 0 |

| Legend:                            |       |                  |       |                      |                 |                    |       |

| R = Readable                       | bit   | W = Writable b   | it    | U = Unimplen         | nented bit, rea | ad as '0'          |       |

| -n = Value at POR '1' = Bit is set |       | '1' = Bit is set |       | '0' = Bit is cleared |                 | x = Bit is unknown |       |

bit 7-0 Byte 4<7:0>: CANx Message Byte 4 bits

### 25.1 Module Description

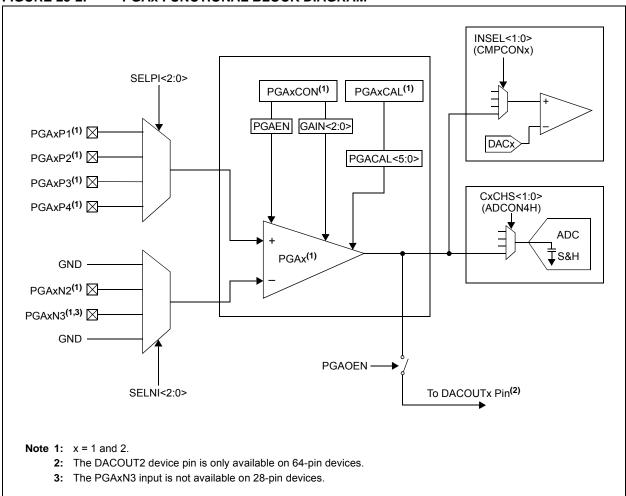

The Programmable Gain Amplifiers are used to amplify small voltages (i.e., voltages across burden/shunt resistors) to improve the signal-to-noise ratio of the measured signal. The PGAx output voltage can be read by any of the four dedicated Sample-and-Hold circuits on the ADC module. The output voltage can also be fed to the comparator module for overcurrent/ voltage protection. Figure 25-2 shows a functional block diagram of the PGAx module. Refer to **Section 22.0 "High-Speed, 12-Bit Analog-to-Digital Converter (ADC)"** and **Section 24.0 "High-Speed Analog Comparator"** for more interconnection details.

The gain of the PGAx module is selectable via the GAIN<2:0> bits in the PGAxCON register. There are five selectable gains, ranging from 4x to 64x. The SELPI<2:0> and SELNI<2:0> bits in the PGAxCON register select one of four positive/negative inputs to the PGAx module. For single-ended applications, the SELNI<2:0> bits will select the ground as the negative

input source. To provide an independent ground reference, the PGAxN2 and PGAxN3 pins are available as the negative input source to the PGAx module.

Note 1: Not all PGA positive/negative inputs are available on all devices. Refer to the specific device pinout for available input source pins.

The output voltage of the PGAx module can be connected to the DACOUTx pin by setting the PGAOEN bit in the PGAxCON register. When the PGAOEN bit is enabled, the output voltage of PGA1 is connected to DACOUT1 and PGA2 is connected to DACOUT2. For devices with a single DACOUTx pin, the output voltage of PGA2 can be connected to DACOUT1 by configuring the DBCC Configuration bit in the FDEVOPT register (FDEVOPT<6>).

If both the DACx output voltage and PGAx output voltage are connected to the DACOUTx pin, the resulting output voltage would be a combination of signals. There is no assigned priority between the PGAx module and the DACx module.

#### FIGURE 25-2: PGAx FUNCTIONAL BLOCK DIAGRAM

# 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Device Configuration" (DS70000618), "Watchdog Timer and Power-Saving Modes" (DS70615) and "CodeGuard™ Intermediate Security" (DS70005182) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGS70X/80X family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

- Brown-out Reset (BOR)

## 27.1 Configuration Bits

In dsPIC33EPXXXGS70X/80X family devices, the Configuration Words are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored at the end of the on-chip program memory space, known as the Flash Configuration Words. Their specific locations are shown in Table 27-1 with detailed descriptions in Table 27-2. The configuration data is automatically loaded from the Flash Configuration Words to the proper Configuration Shadow registers during device Resets.

For devices operating in Dual Partition Flash modes, the BSEQx bits (FBTSEQ<11:0>) determine which panel is the Active Partition at start-up and the Configuration Words from that panel are loaded into the Configuration Shadow registers.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration Words for configuration data in their code for the compiler. This is to make certain that program code is not stored in this address when the code is compiled. Program code executing out of configuration space will cause a device Reset.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration Words.

#### TABLE 27-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

| Bit Field   | Description                                                                 |

|-------------|-----------------------------------------------------------------------------|

| CTXT4<2:0>  | Alternate Working Register Set 4 Interrupt Priority Level (IPL) Select bits |

|             | 111 = Reserved                                                              |

|             | 110 = Assigned to IPL of 7                                                  |

|             | 101 = Assigned to IPL of 6                                                  |

|             | 100 = Assigned to IPL of 5                                                  |

|             | 011 = Assigned to IPL of 4                                                  |

|             | 010 = Assigned to IPL of 3                                                  |

|             | 001 = Assigned to IPL of 2                                                  |

|             | 000 = Assigned to IPL of 1                                                  |

| BTMODE<1:0> | Boot Mode Configuration bits                                                |

|             | 11 = Single Partition mode                                                  |

|             | 10 = Dual Partition mode                                                    |

|             | 01 = Protected Dual Partition mode                                          |

|             | 00 = Privileged Dual Partition mode                                         |

Note 1: The Boot Segment must be present to use the Alternate Interrupt Vector Table.

### 27.7 JTAG Interface

The dsPIC33EPXXXGS70X/80X family devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface is provided in future revisions of the document.

| Note: | Refer to "Programming and Diagnostics"       |  |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|--|

|       | (DS70608) in the "dsPIC33/PIC24 Family       |  |  |  |  |  |  |  |

|       | Reference Manual" for further information on |  |  |  |  |  |  |  |

|       | usage, configuration and operation of the    |  |  |  |  |  |  |  |

|       | JTAG interface.                              |  |  |  |  |  |  |  |

### 27.8 In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

The dsPIC33EPXXXGS70X/80X family devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for details about In-Circuit Serial Programming  $\mathbb{C}(\mathsf{LSP}^{\mathsf{TM}})$ .

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

## 27.9 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or REAL ICE<sup>™</sup> emulator is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/ Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{\text{MCLR}}$ , VDD, VSS and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

### 27.10 Code Protection and CodeGuard™ Security

dsPIC33EPXXXGS70X/80X devices offer multiple levels of security for protecting individual intellectual property. The program Flash protection can be broken up into three segments: Boot Segment (BS), General Segment (GS) and Configuration Segment (CS). Boot Segment has the highest security privilege and can be thought to have limited restrictions when accessing other segments. General Segment has the least security and is intended for the end user system code. Configuration Segment contains only the device user configuration data which is located at the end of the program memory space.

The code protection features are controlled by the Configuration registers, FSEC and FBSLIM. The FSEC register controls the code-protect level for each segment and if that segment is write-protected. The size of BS and GS will depend on the BSLIM<12:0> bits setting and if the Alternate Interrupt Vector Table (AIVT) is enabled. The BSLIM<12:0> bits define the number of pages for BS with each page containing 512 IW. The smallest BS size is one page, which will consist of the Interrupt Vector Table (IVT) and 256 IW of code protection.

If the AIVT is enabled, the last page of BS will contain the AIVT and will not contain any BS code. With AIVT enabled, the smallest BS size is now two pages (1024 IW), with one page for the IVT and BS code, and the other page for the AIVT. Write protection of the BS does not cover the AIVT. The last page of BS can always be programmed or erased by BS code. The General Segment will start at the next page and will consume the rest of program Flash except for the Flash Configuration Words. The IVT will assume GS security only if BS is not enabled. The IVT is protected from being programmed or page erased when either security segment has enabled write protection.

Note: Refer to "CodeGuard™ Intermediate Security" (DS70005182) in the "dsPIC33/ PIC24 Family Reference Manual" for further information on usage, configuration and operation of CodeGuard Security.

# TABLE 30-36:SPI1, SPI2 AND SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)TIMING REQUIREMENTS<sup>(5)</sup>

| AC CHARACTERISTICS |                       |                                                                                  | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                                |  |

|--------------------|-----------------------|----------------------------------------------------------------------------------|-------------------------------------------------------|---------------------|------|-------|--------------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                                                    | Min.                                                  | Тур. <sup>(2)</sup> | Max. | Units | Conditions                     |  |

| SP70               | FscP                  | Maximum SCKx Input Frequency                                                     |                                                       |                     | 11   | MHz   | (Note 3)                       |  |

| SP72               | TscF                  | SCKx Input Fall Time                                                             |                                                       |                     |      | ns    | See Parameter DO32<br>(Note 4) |  |

| SP73               | TscR                  | SCKx Input Rise Time                                                             | —                                                     | _                   | _    | ns    | See Parameter DO31<br>(Note 4  |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                                       | —                                                     | _                   | _    | ns    | See Parameter DO32<br>(Note 4) |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                                       | —                                                     | _                   | _    | ns    | See Parameter DO31<br>(Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                        | —                                                     | 6                   | 20   | ns    |                                |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                                     | 30                                                    | _                   | _    | ns    |                                |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                       | 30                                                    | _                   | _    | ns    |                                |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                        | 30                                                    | —                   |      | ns    |                                |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{\text{SSx}} \downarrow$ to SCKx $\uparrow$ or SCKx $\downarrow$ Input | 120                                                   | —                   | _    | ns    |                                |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                           | 10                                                    | —                   | 50   | ns    | (Note 4)                       |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                                                            | 1.5 Tcy + 40                                          | _                   | _    | ns    | (Note 4)                       |  |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                                         | —                                                     | —                   | 50   | ns    |                                |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the master must not violate this specification.