Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 33                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 17x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

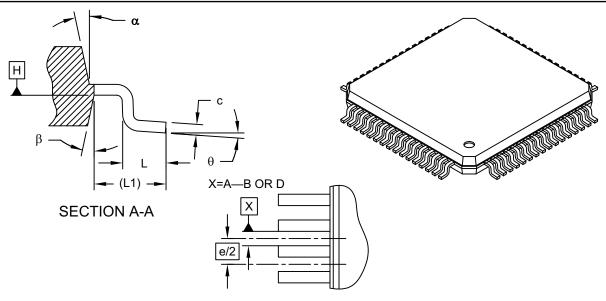

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs804t-i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| RW-0       RW-1       RW-0       R/C-0       R-0       R/W-0       R/W-0         SATA       SATB       SATDW       ACCSAT       IPL3 <sup>(2)</sup> SFA       RND       IF         bit       C       = Clearable bit       C = Clearable bit       U = Unimplemented bit, read as '0'       bit         R Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       n = Value at POR       1' = Bit is set       0' = Bit is cleared       x = Bit is unknown         bit 15       VAR: Variable Exception Processing is enabled       0 = Fixed exception processing is enabled       0 = Fixed exception processing is enabled       0 = DSP engine multiplies are signed       00 = DSP engine multiplies are unsigned       00 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed       0 = No effect       00 = D Do loop sare active       00 = D D loop sare active       00 = D D loops are active       00 = D D loops are active       00 = Accumulator A saturation is enabled       0 = Dat Space write saturation is disabled       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | REGISTER      | 3-2: CORC     | ON: CORE (       | SONTROL RI       | EGISTER            |                |                 |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|------------------|------------------|--------------------|----------------|-----------------|-------|

| RW-0       RW-0       R/W-1       RW-0       R/C-0       R-0       R/W-0       R/W-0         SATA       SATB       SATDW       ACCSAT       IPL3 <sup>(2)</sup> SFA       RND       IF         bit 7       SFA       RND       IF       bit       U       Unimplemented bit, read as '0'         enderstand       W= Writable bit       U = Unimplemented bit, read as '0'       in       v       w         of 15       VAR: Variable Exception Processing is enabled       0 = Fixed exception processing is enabled       is cleared       x = Bit is unknown         bit 15       VAR: Variable Exception Processing is enabled       0 = DSP engine multiplies are insigned       0 = DSP engine multiplies are insigned       0 = DSP engine multiplies are signed       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0         | U-0           | R/W-0            | R/W-0            | R/W-0              | R-0            | R-0             | R-0   |

| RW-0       RW-1       RW-0       R/C-0       R-0       R/W-0       R/W-0         SATA       SATB       SATDW       ACCSAT       IPL3 <sup>(2)</sup> SFA       RND       IF         bit       C       = Clearable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       VAR: Variable Exception Processing Latency Control bit       1 = Variable exception processing is enabled       0' = Bit is cleared       x = Bit is unknown         bit 15       VAR: Variable Exception processing is enabled       0' = Bit is cleared       x = Bit is unknown         bit 15       VAR: Variable exception processing is enabled       0 = BSP engine multiplies are unsigned       0' = Bit is cleared       x = Bit is unknown         bit 13-12       US       US       DSP engine multiplies are signed       0' = DSP engine multiplies are unsigned       0' = DSP engine multiplies are signed       0' = DSP engine active       0' = Tor loop Nesting Level Status bits       1' = Terminates executing DO loop at the end of current loop iteration       0 = Accumulator A saturation is en                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VAR           |               | US1              | US0              | EDT <sup>(1)</sup> | DL2            | DL1             | DL0   |

| SATA       SATB       SATDW       ACCSAT       IPL3 <sup>(2)</sup> SFA       RND       IF         bit 7       bit       bit       C = Clearable bit       bit       U = Unimplemented bit, read as '0'         cn = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       VAR: Variable Exception Processing Latency Control bit       1 = Variable exception processing is enabled       x = Bit is unknown         bit 13       VAR: Variable Exception processing is enabled       0 = Fixed exception processing is enabled       0 = DSP engine multiplies are unsigned         bit 13       US-10s: DSP Multiply Unsigned/Signed Control bits       11 = Reserved       10 = DSP engine multiplies are unsigned         10 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed       00 = DSP engine multiplies are unsigned         01 = DSP engine multiplies are signed       10 = DSP engine multiplies are signed       11 = Terminates executing Do loop at the end of current loop iteration         0 = DSP engine multiplies are signed       11 = Terminates executing Do loop statuse bits       111 = 7 DO loop is active         001 = 1 DO loop is active       000 = 0 DD loops are active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 15        | ·             |                  | ·                |                    |                | ·               | bit   |

| SATA       SATB       SATDW       ACCSAT       IPL3 <sup>(2)</sup> SFA       RND       IF         bit 7       bit       bit       C = Clearable bit       bit       U = Unimplemented bit, read as '0'         cn = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       VAR: Variable Exception Processing Latency Control bit       1 = Variable exception processing is enabled       x = Bit is unknown         bit 13       VAR: Variable Exception processing is enabled       0 = Fixed exception processing is enabled       0 = DSP engine multiplies are unsigned         bit 13       US-10s: DSP Multiply Unsigned/Signed Control bits       11 = Reserved       10 = DSP engine multiplies are unsigned         10 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed       00 = DSP engine multiplies are unsigned         01 = DSP engine multiplies are signed       10 = DSP engine multiplies are signed       11 = Terminates executing Do loop at the end of current loop iteration         0 = DSP engine multiplies are signed       11 = Terminates executing Do loop statuse bits       111 = 7 DO loop is active         001 = 1 DO loop is active       000 = 0 DD loops are active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0         | R/W-0         | R/W-1            | R/W-0            | R/C-0              | R-0            | R/W-0           | R/W-0 |

| bit 7       bit         C = Clearable bit       C = Clearable bit         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       0' = Bit is cleared       x = Bit is unknown         bit 15       VAR: Variable Exception processing is enabled       0 = Fixed exception processing is enabled       0 = Fixed exception processing is enabled         0 = Fixed exception processing is enabled       0 = Fixed exception processing is enabled       0 = DSP engine multiples are mixed-sign         01 = DSP engine multiples are mixed-sign       0 = DSP engine multiples are unsigned       0 = DSP engine multiples are unsigned         00 = DSP engine multiples are unsigned       0 = No effect       0 = No effect         01 = 1 Do loop is active       00 = 0 loop are active       00 = 0 cloops are active         00 = 0 Do loops are active       00 = Accumulator A saturation is enabled       0 = Accumulator A saturation is enabled         0 = Accumulator A saturation is enabled       0 = Accumulator B saturation is enabled       0 = Data Space write saturation is enabled         0 = Data Space write saturation is enabled       0 = Data Space write saturation is enabled       0 = Data Space write saturation is enabled         0 = Data Space write saturation is enabled       0 = Data Space write saturation is disabled       0 = Data Space write saturation is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -             |               |                  | 1                |                    |                |                 |       |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       VAR: Variable Exception Processing Latency Control bit       1 = Variable exception processing is enabled       0 = Fixed exception processing is enabled         0 = Fixed exception processing is enabled       0 = Fixed exception processing is enabled       0 = Fixed exception processing is enabled         0 = Fixed exception processing is enabled       0 = Fixed exception processing is enabled       0 = Fixed exception processing is enabled         0 = DSP engine multiplies are mixed-sign       0 = DSP engine multiplies are mixed-sign       0 = DSP engine multiplies are signed         0 = DSP engine multiplies are signed       0 = DSP engine multiplies are signed       0 = DSP engine fire         0 = DSP engine multiplies are signed       0 = No effect       0 = No effect         0 = 1 Do loop is active       0 = 0 boo pas are active       0 = Accumulator A saturation is enabled         0 = Accumulator A saturation is enabled       0 = Accumulator A saturation is enabled       0 = Accumulator A saturation is enabled         0 = Accumulator A saturation is enabled       0 = Data Space Write saturation is disabled       0 = Data Space Write saturation is disabled         bit 5       SATDW: Data Space Write saturation is disabled       0 = Data Space write saturation is dis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 7         | 0/110         | 0,11211          | //000///         | 11 20              | GIA            | TUD             | bit   |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       VAR: Variable Exception Processing Latency Control bit       1 = Variable exception processing is enabled       0 = Fixed exception processing is enabled         0 = Fixed exception processing is enabled       0 = Fixed exception processing is enabled       0 = Fixed exception processing is enabled         0 = Fixed exception processing is enabled       0 = Fixed exception processing is enabled       0 = Fixed exception processing is enabled         0 = DSP engine multiplies are mixed-sign       0 = DSP engine multiplies are mixed-sign       0 = DSP engine multiplies are signed         0 = DSP engine multiplies are signed       0 = DSP engine multiplies are signed       0 = DSP engine fire         0 = DSP engine multiplies are signed       0 = No effect       0 = No effect         0 = 1 Do loop is active       0 = 0 boo pas are active       0 = Accumulator A saturation is enabled         0 = Accumulator A saturation is enabled       0 = Accumulator A saturation is enabled       0 = Accumulator A saturation is enabled         0 = Accumulator A saturation is enabled       0 = Data Space Write saturation is disabled       0 = Data Space Write saturation is disabled         bit 5       SATDW: Data Space Write saturation is disabled       0 = Data Space write saturation is dis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Logondu       |               | C = Clearabl     | o bit            |                    |                |                 |       |

| In = Value at POR       '1' = Bit is set       0' = Bit is cleared       x = Bit is unknown         poit 15       VAR: Variable Exception Processing is enabled       0 = Fixed exception processing is enabled         0 = Fixed exception processing is enabled       0 = Fixed exception processing is enabled       0 = Difference         bit 14       Unimplemented: Read as '0'       00 = DSP engine multiplies are unsigned       0 = DSP engine multiplies are unsigned         0 = DSP engine multiplies are unsigned       00 = DSP engine multiplies are unsigned       00 = DSP engine multiplies are unsigned         0 = DSP engine multiplies are unsigned       00 = DSP engine multiplies are unsigned       00 = DSP engine multiplies are unsigned         0 = DSP engine multiplies are unsigned       00 = DSP engine multiplies are unsigned       00 = DSP engine multiplies are unsigned         0 = DSP engine multiplies are unsigned       00 = DSP engine multiplies are unsigned       00 = DSP engine multiplies are unsigned         0 = No effect       0 = No effect       00 = No opps are active       00 = No effect         0 = No effect       0 = Accumulator A saturation is enabled       0 = Accumulator A saturation is disabled         0 = Accumulator A saturation is enabled       0 = Accumulator A saturation is disabled       0 = Accumulator B saturation is disabled         0 = Accumulator B saturation is enabled       0 = Accumulator Saturation is disabled       0 = Data Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -             | , hit         |                  |                  |                    | onted hit read | d ac 'O'        |       |

| <ul> <li>VAR: Variable Exception Processing Latency Control bit <ol> <li>VAR: Variable exception processing is enabled</li> <li>Fixed exception processing is enabled</li> </ol> </li> <li>bit 14 <ul> <li>Unimplemented: Read as '0'</li> </ul> </li> <li>bit 13-12</li> <li>US-1:0-: DSP Multiply Unsigned/Signed Control bits <ol> <li>Reserved</li> <li>DSP engine multiplies are mixed-sign</li> <li>DSP engine multiplies are unsigned</li> <li>DSP engine multiplies are signed</li> <li>DSP engine are active and the end of current loop iteration</li> <li>No effect</li> </ol></li></ul> <li>11 = Tominates executing Do loop at the end of current loop iteration</li> <li>No effect</li> <li>NO elfect</li> <li>DL-2:0-: Do loops are active</li> <li>OO1 = 1 DO loop is active</li> <li>OO1 = 1 DO loop is active</li> <li>OO1 = 1 DO loops are active</li> <li>ACCUMULATOR A saturation is enabled</li> <li>Accumulator A saturation is enabled</li> <li>Accumulator A saturation is enabled</li> <li>Accumulator B saturation is enabled</li> <li>Accumulator B saturation is enabled</li> <li>D = Accumulator Saturation is enabled</li> <li>D = Data Space write saturation is disabled</li> <li>bit 4</li> <li>ACCSAT: Accumulator Saturation Mode Select bit</li> <li>1 = 0:31 saturation (super saturation)</li> <li>0 = 1.31 saturation (normal saturation)</li> <li>0 = 1.31 saturation (normal saturation)</li> <li>0 = CPU Interrupt Priority Level Status bit 3<sup>(2)</sup></li> <li>1 = CPU Interr</li> |               |               |                  |                  | •                  | -              |                 | 0000  |

| 1 = Variable exception processing is enabled         0 = Fixed exception processing is enabled         bit 14       Unimplemented: Read as '0'         bit 13-12       US-1:0:: DSP Multiply Unsigned/Signed Control bits         11 = Reserved       10 = DSP engine multiplies are mixed-sign         01 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed         02 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed         03 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed         04 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed         05 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed         05 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed         05 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed         05 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed         05 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed         05 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed         05 = DSP engine multiplies are signed       00 = DSP engine multiplies are signed         05 = DL-22:0s: Do Loop Nesting Level Status bits       111 = 7 DO loops are active         05 = Accumulator A saturation is enabled       0 = A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -n = value at | PUR           | I = Bit is se    | l                |                    | ared           | x = Bit is unkn | IOWN  |

| <ul> <li>b = Fixed exception processing is enabled</li> <li>bit 13</li> <li>Uis</li> <li>Dit 13-12</li> <li>Uis</li> <li>Cite Composition (Composition of the structure)</li> <li>DSP engine multiplies are mixed-sign</li> <li>D = DSP engine multiplies are mixed-sign</li> <li>D = DSP engine multiplies are unsigned</li> <li>DSP engine multiplies are signed</li> <li>DSP engine multiplies are unsigned</li> <li>DSP engine multiplies are signed</li> <li>DSP engine multiplies are unsigned</li> <li>DSP engine multiplies are signed</li> <li>DSP engine multiplies are signed</li> <li>DSP engine endition (Control bit<sup>(1)</sup>)</li> <li>T = Terminates executing Do loop at the end of current loop iteration</li> <li>D = No effect</li> <li>D = Do loops are active</li> <li>Int = 7 Do loops are active</li> <li>Int = 7 Do loops are active</li> <li>Int = 7 Do loops are active</li> <li>Int = Accumulator A saturation is enabled</li> <li>Accumulator A saturation is disabled</li> <li>SATEW: DAta Space Write from DSP Engine Saturation Enable bit</li> <li>I = Data Space write saturation is disabled</li> <li>O = Data Space write saturation (Composition Strutton)</li> <li>I = Data Space write saturation (Strutton Strutton)<td>bit 15</td><td>VAR: Variable</td><td>e Exception Pr</td><td>ocessing Later</td><td>ncy Control bit</td><td></td><td></td><td></td></li></ul>                                         | bit 15        | VAR: Variable | e Exception Pr   | ocessing Later   | ncy Control bit    |                |                 |       |

| bit 13-12       US<1:0-: DSP Multiply Unsigned/Signed Control bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |               |                  |                  |                    |                |                 |       |

| <pre>11 = Reserved<br/>10 = DSP engine multiplies are mixed-sign<br/>01 = DSP engine multiplies are unsigned<br/>00 = DSP engine multiplies are signed<br/>bit 11 EDT: Early Do Loop Termination Control bit<sup>(1)</sup><br/>1 = Terminates executing Do loop at the end of current loop iteration<br/>0 = No effect<br/>bit 10-8 DL-2:0-: Do Loop Nesting Level Status bits<br/>111 = 7 Do loops are active<br/>001 = 1 Do loop is active<br/>000 = 0 Do loops are active<br/>001 = 1 Do loop is active<br/>000 = 0 Do loops are active<br/>bit 7 SATA: ACCA Saturation Enable bit<br/>1 = Accumulator A saturation is enabled<br/>0 = Accumulator A saturation is enabled<br/>0 = Accumulator A saturation is enabled<br/>0 = Accumulator B saturation is enabled<br/>0 = Accumulator B saturation is disabled<br/>bit 5 SATDW: Data Space Write from DSP Engine Saturation Enable bit<br/>1 = Data Space write saturation is disabled<br/>bit 4 ACCSAT: Accumulator Saturation Mode Select bit<br/>1 = 9.31 saturation (super saturation)<br/>0 = 1.31 saturation (normal saturation)<br/>bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup><br/>1 = CPU Interrupt Priority Level is greater than 7<br/>0 = CPU Interrupt Priority Level is 7 or less</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 14        |               | • •              | •                |                    |                |                 |       |

| <ul> <li>10 = DSP engine multiplies are mixed-sign</li> <li>01 = DSP engine multiplies are unsigned</li> <li>00 = DSP engine multiplies are signed</li> <li>00 = DSP engine multiplies are signed</li> <li>01 = DT: Early Do Loop Termination Control bit<sup>(1)</sup></li> <li>1 = Terminates executing Do loop at the end of current loop iteration</li> <li>0 = No effect</li> <li>01 = 1 Do loop Nesting Level Status bits</li> <li>111 = 7 Do loops are active</li> <li>000 = 0 Do loops are active</li> <li>001 = 1 Do loop is active</li> <li>000 = 0 Do loops are active</li> <li>11 = Accumulator A saturation is enabled</li> <li>0 = Accumulator A saturation is disabled</li> <li>0 = Accumulator B saturation is disabled</li> <li>0 = Accumulator B saturation is disabled</li> <li>0 = Accumulator B saturation is enabled</li> <li>0 = Accumulator B saturation is enabled</li> <li>0 = Data Space Write from DSP Engine Saturation Enable bit</li> <li>1 = Data Space write saturation is disabled</li> <li>0 = Data Space write saturation is disabled</li> <li>0 = Data Space write saturation is disabled</li> <li>0 = 1.31 saturation (super saturation)</li> <li>0 = 1.31 saturation (normal saturation)</li> <li>0 = 1.31 saturation (normal saturation)</li> <li>0 = 1.31 saturation (super saturation)</li> <li>0 = 0.131 saturation (super saturation)</li> <li>0 = 0.131 saturation (normal saturation)</li> <li>0 = CPU Interrupt Priority Level Status bit 3<sup>(2)</sup></li> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 13-12     | US<1:0>: DS   | P Multiply Uns   | igned/Signed     | Control bits       |                |                 |       |

| 01 = DSP engine multiplies are unsigned         00 = DSP engine multiplies are signed         00 = DSP engine multiplies are signed         01 = Terminates executing Do loop at the end of current loop iteration         0 = No effect         bit 10-8         DL<2:0>: Do Loop Nesting Level Status bits         111 = 7 Do loops are active         •         •         001 = 1 Do loop is active         000 = 0 Do loops are active         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |               |                  |                  |                    |                |                 |       |

| bit 11       EDT: Early po Loop Termination Control bit <sup>(1)</sup> 1 = Terminates executing po loop at the end of current loop iteration         0 = No effect         DL<2:0:: Do Loop Nesting Level Status bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               | 01 = DSP en   | gine multiplies  | are unsigned     | ו                  |                |                 |       |

| 1 = Terminates executing D0 loop at the end of current loop iteration         0 = No effect         bit 10-8         DL<2:D>: D0 Loop Nesting Level Status bits         111 = 7 D0 loops are active         .         001 = 1 D0 loop is active         000 = 0 D0 loops are active         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 11        |               |                  | -                | :+(1)              |                |                 |       |

| bit 10-8       DL<2:0>: DO Loop Nesting Level Status bits         111 = 7 DO loops are active         001 = 1 DO loop is active         000 = 0 DO loops are active         bit 7         SATA: ACCA Saturation Enable bit         1 = Accumulator A saturation is enabled         0 = Accumulator A saturation is enabled         0 = Accumulator B saturation is enabled         0 = Data Space write saturation is enabled         0 = Data Space write saturation is disabled         bit 4       ACCSAT: Accumulator Saturation Mode Select bit         1 = 9.31 saturation (super saturation)         0 = 1.31 saturation (normal saturation)         0 = 1.31 saturation (normal saturation)         0 = CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7         0 = CPU Interrupt Priority Level is 7 or less                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | 1 = Terminate | es executing D   |                  |                    | op iteration   |                 |       |

| <ul> <li>111 = 7 Do loops are active</li> <li>001 = 1 Do loop is active</li> <li>000 = 0 Do loops are active</li> <li>bit 7</li> <li>SATA: ACCA Saturation Enable bit</li> <li>1 = Accumulator A saturation is enabled</li> <li>0 = Accumulator A saturation is disabled</li> <li>bit 6</li> <li>SATB: ACCB Saturation Enable bit</li> <li>1 = Accumulator B saturation is enabled</li> <li>0 = Accumulator B saturation is disabled</li> <li>bit 5</li> <li>SATDW: Data Space Write from DSP Engine Saturation Enable bit</li> <li>1 = Data Space write saturation is enabled</li> <li>0 = Data Space write saturation is disabled</li> <li>bit 4</li> <li>ACCSAT: Accumulator Saturation Mode Select bit</li> <li>1 = 9.31 saturation (super saturation)</li> <li>0 = 1.31 saturation (normal saturation)</li> <li>bit 3</li> <li>IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup></li> <li>1 = CPU Interrupt Priority Level is 7 or less</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | hit 10 9      |               |                  | l aval Statua bi | to                 |                |                 |       |

| 001 = 1 D0 loop is active         000 = 0 D0 loops are active         bit 7       SATA: ACCA Saturation Enable bit         1 = Accumulator A saturation is enabled         0 = Accumulator A saturation is enabled         0 = Accumulator A saturation is enabled         0 = Accumulator B saturation is enabled         0 = Data Space write from DSP Engine Saturation Enable bit         1 = Data Space write saturation is enabled         0 = Data Space write saturation is disabled         bit 4       ACCSAT: Accumulator Saturation Mode Select bit         1 = 9.31 saturation (super saturation)       0 = 1.31 saturation (normal saturation)         0 = TL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7         0 = CPU Interrupt Priority Level is 7 or less                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DIL 10-0      |               | -                |                  | lS                 |                |                 |       |

| 000 = 0 D0 loops are active         bit 7       SATA: ACCA Saturation Enable bit         1 = Accumulator A saturation is enabled         0 = Accumulator A saturation is disabled         bit 6       SATB: ACCB Saturation Enable bit         1 = Accumulator B saturation is enabled         0 = Accumulator B saturation is enabled         0 = Accumulator B saturation is disabled         bit 5       SATDW: Data Space Write from DSP Engine Saturation Enable bit         1 = Data Space write saturation is enabled         0 = Data Space write saturation is disabled         bit 4       ACCSAT: Accumulator Saturation Mode Select bit         1 = 9.31 saturation (super saturation)         0 = 1.31 saturation (normal saturation)         0 = 1.31 saturation (normal saturation)         bit 3       IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7         0 = CPU Interrupt Priority Level is 7 or less                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | •             |                  |                  |                    |                |                 |       |

| 000 = 0 D0 loops are active         bit 7       SATA: ACCA Saturation Enable bit         1 = Accumulator A saturation is enabled         0 = Accumulator A saturation is disabled         bit 6       SATB: ACCB Saturation Enable bit         1 = Accumulator B saturation is enabled         0 = Accumulator B saturation is enabled         0 = Accumulator B saturation is disabled         bit 5       SATDW: Data Space Write from DSP Engine Saturation Enable bit         1 = Data Space write saturation is enabled         0 = Data Space write saturation is disabled         bit 4       ACCSAT: Accumulator Saturation Mode Select bit         1 = 9.31 saturation (super saturation)         0 = 1.31 saturation (normal saturation)         0 = 1.31 saturation (normal saturation)         bit 3       IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7         0 = CPU Interrupt Priority Level is 7 or less                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | •             |                  |                  |                    |                |                 |       |

| 000 = 0 D0 loops are active         bit 7       SATA: ACCA Saturation Enable bit         1 = Accumulator A saturation is enabled         0 = Accumulator A saturation is disabled         bit 6       SATB: ACCB Saturation Enable bit         1 = Accumulator B saturation is enabled         0 = Accumulator B saturation is enabled         0 = Accumulator B saturation is disabled         bit 5       SATDW: Data Space Write from DSP Engine Saturation Enable bit         1 = Data Space write saturation is enabled         0 = Data Space write saturation is disabled         bit 4       ACCSAT: Accumulator Saturation Mode Select bit         1 = 9.31 saturation (super saturation)         0 = 1.31 saturation (normal saturation)         0 = 1.31 saturation (normal saturation)         bit 3       IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7         0 = CPU Interrupt Priority Level is 7 or less                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | •             | on is activo     |                  |                    |                |                 |       |

| 1 = Accumulator A saturation is enabled         0 = Accumulator A saturation is disabled         bit 6       SATB: ACCB Saturation Enable bit         1 = Accumulator B saturation is enabled         0 = Accumulator B saturation is enabled         0 = Accumulator B saturation is disabled         bit 5       SATDW: Data Space Write from DSP Engine Saturation Enable bit         1 = Data Space write saturation is enabled         0 = Data Space write saturation is disabled         bit 4       ACCSAT: Accumulator Saturation Mode Select bit         1 = 9.31 saturation (super saturation)         0 = 1.31 saturation (normal saturation)         bit 3       IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7         0 = CPU Interrupt Priority Level is 7 or less                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |               |                  |                  |                    |                |                 |       |

| 0 = Accumulator A saturation is disabledbit 6SATB: ACCB Saturation Enable bit<br>1 = Accumulator B saturation is enabled<br>0 = Accumulator B saturation is disabledbit 5SATDW: Data Space Write from DSP Engine Saturation Enable bit<br>1 = Data Space write saturation is enabled<br>0 = Data Space write saturation is disabledbit 4ACCSAT: Accumulator Saturation Mode Select bit<br>1 = 9.31 saturation (super saturation)<br>0 = 1.31 saturation (normal saturation)bit 3IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup><br>1 = CPU Interrupt Priority Level is greater than 7<br>0 = CPU Interrupt Priority Level is 7 or less                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 7         | SATA: ACCA    | Saturation En    | able bit         |                    |                |                 |       |

| <ul> <li>1 = Accumulator B saturation is enabled</li> <li>0 = Accumulator B saturation is disabled</li> <li>bit 5 SATDW: Data Space Write from DSP Engine Saturation Enable bit</li> <li>1 = Data Space write saturation is enabled</li> <li>0 = Data Space write saturation is disabled</li> <li>bit 4 ACCSAT: Accumulator Saturation Mode Select bit</li> <li>1 = 9.31 saturation (super saturation)</li> <li>0 = 1.31 saturation (normal saturation)</li> <li>0 = 1.31 cPU Interrupt Priority Level Status bit 3<sup>(2)</sup></li> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |               |                  |                  |                    |                |                 |       |

| <ul> <li>a Accumulator B saturation is disabled</li> <li>bit 5</li> <li>SATDW: Data Space Write from DSP Engine Saturation Enable bit</li> <li>1 = Data Space write saturation is enabled</li> <li>0 = Data Space write saturation is disabled</li> <li>bit 4</li> <li>ACCSAT: Accumulator Saturation Mode Select bit</li> <li>1 = 9.31 saturation (super saturation)</li> <li>0 = 1.31 saturation (normal saturation)</li> <li>0 = 1.31 crupt Priority Level Status bit 3<sup>(2)</sup></li> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 6         | SATB: ACCB    | 3 Saturation Er  | able bit         |                    |                |                 |       |

| <ul> <li>1 = Data Space write saturation is enabled</li> <li>0 = Data Space write saturation is disabled</li> <li>bit 4 ACCSAT: Accumulator Saturation Mode Select bit</li> <li>1 = 9.31 saturation (super saturation)</li> <li>0 = 1.31 saturation (normal saturation)</li> <li>0 = 1.31 cPU Interrupt Priority Level Status bit 3<sup>(2)</sup></li> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |               |                  |                  |                    |                |                 |       |

| <ul> <li>1 = Data Space write saturation is enabled</li> <li>0 = Data Space write saturation is disabled</li> <li>bit 4 ACCSAT: Accumulator Saturation Mode Select bit</li> <li>1 = 9.31 saturation (super saturation)</li> <li>0 = 1.31 saturation (normal saturation)</li> <li>0 = 1.31 cPU Interrupt Priority Level Status bit 3<sup>(2)</sup></li> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 5         | SATDW: Data   | a Space Write    | from DSP Eng     | ine Saturation     | Enable bit     |                 |       |

| bit 4       ACCSAT: Accumulator Saturation Mode Select bit         1 = 9.31 saturation (super saturation)         0 = 1.31 saturation (normal saturation)         bit 3         IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7         0 = CPU Interrupt Priority Level is 7 or less                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |               |                  |                  |                    |                |                 |       |

| <ul> <li>0 = 1.31 saturation (normal saturation)</li> <li>bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup></li> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 4         | -             |                  |                  |                    |                |                 |       |

| bit 3 IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup><br>1 = CPU Interrupt Priority Level is greater than 7<br>0 = CPU Interrupt Priority Level is 7 or less                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |               |                  |                  |                    |                |                 |       |

| <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 3         |               | -                | -                | oit 3 <b>(2)</b>   |                |                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               | 1 = CPU Inter | rrupt Priority L | evel is greater  | than 7             |                |                 |       |