Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 33                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 17x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

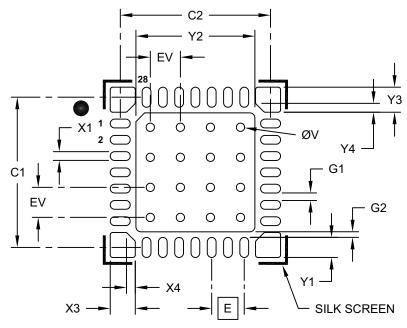

| Package / Case             | 48-TQFP                                                                         |

| Supplier Device Package    | 48-TQFP (7x7)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs805-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(1)</sup> | Pin<br>Type | Buffer<br>Type | PPS               | Description                                                                                                                                                                        |

|-------------------------|-------------|----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN21                |             | Analog         | No                | Analog input channels.                                                                                                                                                             |

| AN0ALT-AN1ALT           | I           | Analog         | No                | Alternate analog input channels.                                                                                                                                                   |

| C1RXR                   | I           | ST             | Yes               | CAN1 receive.                                                                                                                                                                      |

| C2RXR                   | I           | ST             | Yes               | CAN2 receive.                                                                                                                                                                      |

| C1TX                    | 0           | ST             | Yes               | CAN1 transmit.                                                                                                                                                                     |

| C2TX                    | 0           | ST             | Yes               | CAN2 transmit.                                                                                                                                                                     |

| CLKI                    | I           | ST/            | No                | External clock source input. Always associated with OSC1 pin                                                                                                                       |

|                         |             | CMOS           |                   | function.                                                                                                                                                                          |

| CLKO                    | 0           | _              | No                | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                    | I           | ST/<br>CMOS    | No                | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                    |

| OSC2                    | I/O         |                | No                | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                           |

| CLC1OUT                 | 0           | DIG            | Yes               | CLC1 output.                                                                                                                                                                       |

| CLC2OUT                 | 0           | DIG            | Yes               | CLC2 output.                                                                                                                                                                       |

| CLC3OUT                 | 0           | DIG            | No <sup>(4)</sup> | CLC3 output.                                                                                                                                                                       |

| CLC4OUT                 | 0           | DIG            | No <sup>(4)</sup> | CLC4 output.                                                                                                                                                                       |

| REFCLKO                 | 0           | —              | Yes               | Reference clock output.                                                                                                                                                            |

| IC1-IC4                 | I           | ST             | Yes               | Capture Inputs 1 through 4.                                                                                                                                                        |

| OCFA                    | I           | ST             | Yes               | Compare Fault A input (for compare channels).                                                                                                                                      |

| OC1-OC4                 | 0           |                | Yes               | Compare Outputs 1 through 4.                                                                                                                                                       |

| INT0                    | I           | ST             | No                | External Interrupt 0.                                                                                                                                                              |

| INT1                    | I           | ST             | Yes               | External Interrupt 1.                                                                                                                                                              |

| INT2                    | I           | ST             | Yes               | External Interrupt 2.                                                                                                                                                              |

| INT4                    | I           | ST             | Yes               | External Interrupt 4.                                                                                                                                                              |

| RA0-RA4                 | I/O         | ST             | No                | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                | I/O         | ST             | No                | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC15                | I/O         | ST             | No                | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD0-RD15                | I/O         | ST             | No                | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE0-RE15                | I/O         | ST             | No                | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                    | I           | ST             | Yes               | Timer1 external clock input.                                                                                                                                                       |

| T2CK                    | I           | ST             | Yes               | Timer2 external clock input.                                                                                                                                                       |

| T3CK                    | I           | ST             | Yes               | Timer3 external clock input.                                                                                                                                                       |

| T4CK                    |             | ST             | No                | Timer4 external clock input.                                                                                                                                                       |

| T5CK                    |             | ST             | No                | Timer5 external clock input.                                                                                                                                                       |

| U1CTS                   | I           | ST             | Yes               | UART1 Clear-to-Send.                                                                                                                                                               |

| U1RTS                   | 0           | _              | Yes               | UART1 Ready-to-Send.                                                                                                                                                               |

| U1RX                    |             | ST             | Yes               | UART1 receive.                                                                                                                                                                     |

| U1TX                    | 0           |                | Yes               | UART1 transmit.                                                                                                                                                                    |

| BCLK1                   | 0           | ST             | Yes               | UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                                         |

| Legend: CMOS = C        |             |                |                   |                                                                                                                                                                                    |

|                         |             |                |                   | IOS levels O = Output I = Input                                                                                                                                                    |

| PPS = Per               | ripneral    | Pin Selec      | л<br>Л            | TTL = TTL input buffer                                                                                                                                                             |

1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

**2:** PWM4H/L through PWM8H/L are fixed on dsPIC33EPXXXGS708/808 devices. PWM4H/L through PWM6H/L are fixed on dsPIC33EPXXXGS706/806 devices.

3: The SCK3 pin is fixed on dsPIC33EPXXXGS706/806 and dsPIC33EPXXXGS708/808 devices.

4: PPS is available on dsPIC33EPXXXGS702 devices only.

### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| -             |                          |                  |               |                   |                 |                 |       |

|---------------|--------------------------|------------------|---------------|-------------------|-----------------|-----------------|-------|

| U-0           | U-0                      | U-0              | U-0           | U-0               | U-0             | U-0             | U-0   |

| —             | —                        | —                | —             | —                 |                 | —               |       |

| bit 15        |                          |                  |               |                   |                 |                 | bit 8 |

|               |                          |                  |               | =                 |                 | =               |       |

| U-0           | U-0                      | R/W-0            | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|               | —                        |                  |               | TUN               | <5:0>           |                 |       |

| bit 7         |                          |                  |               |                   |                 |                 | bit 0 |

|               |                          |                  |               |                   |                 |                 |       |

| Legend:       |                          |                  |               |                   |                 |                 |       |

| R = Readable  | e bit                    | W = Writable b   | bit           | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value at | POR                      | '1' = Bit is set |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|               |                          |                  |               |                   |                 |                 |       |

| bit 15-6      | Unimplemen               | ted: Read as '0  | ,             |                   |                 |                 |       |

| bit 5-0       | <b>TUN&lt;5:0&gt;:</b> F | RC Oscillator To | uning bits    |                   |                 |                 |       |

|               |                          | ximum frequen    |               |                   | 7 MHz)          |                 |       |

|               | 011110 <b>= Ce</b>       | nter frequency   | + 1.41% (7.47 | 4 MHz)            |                 |                 |       |

|               | •                        |                  |               |                   |                 |                 |       |

|               | •                        |                  |               |                   |                 |                 |       |

|               | 000001 <b>= Ce</b>       | nter frequency   | + 0.047% (7.3 | 73 MHz)           |                 |                 |       |

|               | 000000 <b>= Ce</b>       | nter frequency   | (7.37 MHz noi | minal)            |                 |                 |       |

|               | 111111 <b>= Ce</b>       | nter frequency   | - 0.047% (7.3 | 67 MHz)           |                 |                 |       |

|               | •                        |                  |               |                   |                 |                 |       |

|               | •                        |                  |               |                   |                 |                 |       |

|               | 100001 <b>= Ce</b>       | nter frequency   | - 1.457% (7.2 | 63 MHz)           |                 |                 |       |

|               |                          | nimum frequenc   | •             | ,                 | /IHz)           |                 |       |

|               |                          |                  |               |                   |                 |                 |       |

### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

- bit 1 C1MD: CAN1 Module Disable bit

- 1 = CAN1 module is disabled

- 0 = CAN1 module is enabled

- bit 0 ADCMD: ADC Module Disable bit

- 1 = ADC module is disabled 0 = ADC module is enabled

NOTES:

### REGISTER 16-24: LEBCONX: PWMx LEADING-EDGE BLANKING (LEB) CONTROL REGISTER (x = 1 to 8) (CONTINUED)

- bit 1

BPLH: Blanking in PWMxL High Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is high

bit 0

BPLL: Blanking in PWMxL Low Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is low

0 = No blanking when the PWMxL low Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is low

0 = No blanking when the PWMxL output is low

- **Note 1:** The blanking signal is selected via the BLANKSEL<3:0> bits in the AUXCONx register.

### **REGISTER 16-25: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER (x = 1 to 8)**

| U-0                                                             | U-0   | U-0                                | U-0             | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------------------------------------------------------------|-------|------------------------------------|-----------------|-------|-------|-------|-------|

| —                                                               | —     | —                                  | _               |       | LEB   | <8:5> |       |

| bit 15                                                          |       |                                    |                 |       |       |       | bit 8 |

|                                                                 |       |                                    |                 |       |       |       |       |

| R/W-0                                                           | R/W-0 | R/W-0                              | R/W-0           | R/W-0 | U-0   | U-0   | U-0   |

|                                                                 |       | LEB<4:0>                           |                 |       | —     | —     | —     |

| bit 7                                                           |       |                                    |                 |       |       |       | bit 0 |

|                                                                 |       |                                    |                 |       |       |       |       |

| Legend:                                                         |       |                                    |                 |       |       |       |       |

| R = Readable bit W = Writable bit                               |       | U = Unimplemented bit, read as '0' |                 |       |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit |       |                                    | x = Bit is unkr | nown  |       |       |       |

bit 15-12 Unimplemented: Read as '0'

bit 11-3 **LEB<8:0>:** Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits The value is in 8.32 ns increments.

bit 2-0 Unimplemented: Read as '0'

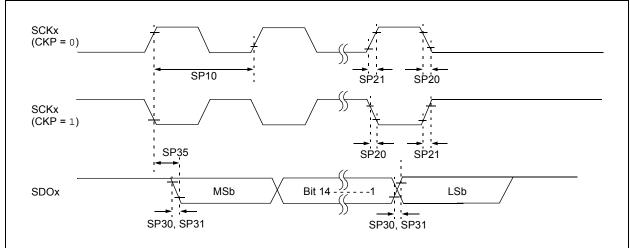

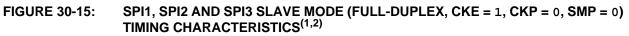

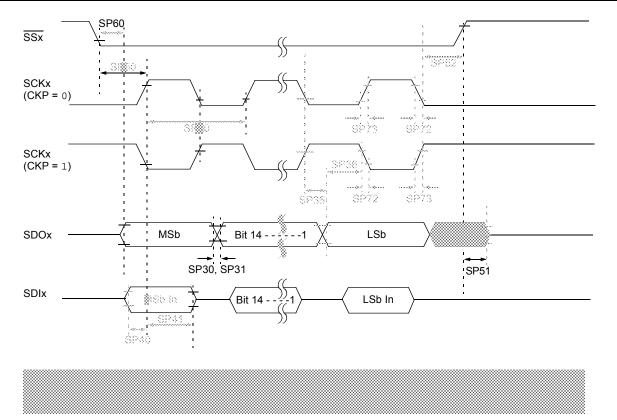

### 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the dsPIC33EPXXXGS70X/80X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI) with Audio Codec Support" (DS70005136) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the Motorola<sup>®</sup> SPI and SIOP interfaces. All devices in the dsPIC33EPXXXGS70X/80X family include three SPI modules.

The module supports operation in two buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through a FIFO buffer. The FIFO level depends on the configured mode.

Variable length data can be transmitted and received, from 2 to 32 bits.

| Note: | Do not perform Read-Modify-Write opera-      |

|-------|----------------------------------------------|

|       | tions (such as bit-oriented instructions) on |

|       | the SPIxBUF register in either Standard or   |

|       | Enhanced Buffer mode.                        |

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

SPI3 also supports Audio modes. Four different Audio modes are available.

- I<sup>2</sup>S

- · Left Justified

- Right Justified

- PCM/DSP

In each of these modes, the serial clock is free-running and audio data is always transferred.

If an audio protocol data transfer takes place between two devices, then usually one device is the master and the other is the slave. However, audio data can be transferred between two slaves. Because the audio protocols require free-running clocks, the master can be a third party controller. In either case, the master generates two free-running clocks: SCKx and LRC (Left, Right Channel Clock/SSx/FSYNC). The SPI serial interface consists of four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SSx}$  is not used. In the 2-pin mode, both SDOx and  $\overline{SSx}$  are not used.

The SPI module has the ability to generate three interrupts, reflecting the events that occur during the data communication. The following types of interrupts can be generated:

- 1. Receive interrupts are signalled by SPIxRXIF. This event occurs when:

- RX watermark interrupt

- SPIROV = 1

- SPIRBF = 1

- SPIRBE = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

- 2. Transmit interrupts are signalled by SPIxTXIF. This event occurs when:

- TX watermark interrupt

- SPITUR = 1

- SPITBF = 1

- SPITBE = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

- 3. General interrupts are signalled by SPIxIF. This event occurs when

- FRMERR = 1

- SPIBUSY = 1

- SRMT = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

Block diagrams of the module in Standard and Enhanced modes are shown in Figure 18-1 and Figure 18-2.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1, SPI2 or SPI3. Special Function Registers will follow a similar notation. For example, SPIxCON1 and SPIxCON2 refer to the control registers for any of the three SPI modules.

### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5     | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4     | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|           | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3     | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|           | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1   | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|           | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0     | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|           | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

| Note 1: F | Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the                                                                                                                                                         |

"dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.

2: This feature is only available for the 16x BRG mode (BRGH = 0).

### REGISTER 21-4: CLCxGLSL: CLCx GATE LOGIC INPUT SELECT LOW REGISTER

| R/W-0         | R/W-0                                                                                                                                                 | R/W-0                                | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|-------------------|------------------|-----------------|-------|--|--|--|

| G2D4T         | G2D4N                                                                                                                                                 | G2D3T                                | G2D3N           | G2D2T             | G2D2N            | G2D1T           | G2D1N |  |  |  |

| bit 15        | •                                                                                                                                                     |                                      |                 |                   |                  |                 | bit 8 |  |  |  |

| R/W-0         | R/W-0                                                                                                                                                 | R/W-0                                | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |

| G1D4T         | G1D4N                                                                                                                                                 | G1D3T                                | G1D3N           | G1D2T             | G1D2N            | G1D1T           | G1D1N |  |  |  |

| bit 7         | GIDHN                                                                                                                                                 | GIBOI                                | GIDSN           | 01021             | GIDZIN           | 01011           | bit 0 |  |  |  |

| Legend:       |                                                                                                                                                       |                                      |                 |                   |                  |                 |       |  |  |  |

| R = Readable  | e bit                                                                                                                                                 | W = Writable I                       | oit             | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |  |

| -n = Value at |                                                                                                                                                       | '1' = Bit is set                     |                 | '0' = Bit is clea |                  | x = Bit is unkr | nown  |  |  |  |

|               |                                                                                                                                                       | 2.1.0 001                            |                 | 0 2000 0.00       |                  |                 |       |  |  |  |

| bit 15        | G2D4T: Gate                                                                                                                                           | 2 Data Source                        | 4 True Enable   | e bit             |                  |                 |       |  |  |  |

|               | 1 = Data Sour                                                                                                                                         | rce 4 non-inver                      | ed signal is er | nabled for Gate   | 2                |                 |       |  |  |  |

|               | 0 = Data Sour                                                                                                                                         | rce 4 non-inver                      | ed signal is di | sabled for Gate   | e 2              |                 |       |  |  |  |

| bit 14        |                                                                                                                                                       | 2 Data Source                        | •               |                   |                  |                 |       |  |  |  |

|               |                                                                                                                                                       | rce 4 inverted s<br>rce 4 inverted s |                 |                   |                  |                 |       |  |  |  |

| bit 13        |                                                                                                                                                       | 2 Data Source                        | •               |                   |                  |                 |       |  |  |  |

|               | 1 = Data Sour                                                                                                                                         | rce 3 non-inver                      | ed signal is er | nabled for Gate   |                  |                 |       |  |  |  |

| bit 12        | <ul> <li>0 = Data Source 3 non-inverted signal is disabled for Gate 2</li> <li>G2D3N: Gate 2 Data Source 3 Negated Enable bit</li> </ul>              |                                      |                 |                   |                  |                 |       |  |  |  |

| 511 12        | 1 = Data Sour                                                                                                                                         | rce 3 inverted s                     | ignal is enable | ed for Gate 2     |                  |                 |       |  |  |  |

| bit 11        | <ul> <li>0 = Data Source 3 inverted signal is disabled for Gate 2</li> <li>G2D2T: Gate 2 Data Source 2 True Enable bit</li> </ul>                     |                                      |                 |                   |                  |                 |       |  |  |  |

|               | <ul> <li>1 = Data Source 2 non-inverted signal is enabled for Gate 2</li> <li>0 = Data Source 2 non-inverted signal is disabled for Gate 2</li> </ul> |                                      |                 |                   |                  |                 |       |  |  |  |

| bit 10        |                                                                                                                                                       | 2 Data Source                        | •               |                   |                  |                 |       |  |  |  |

|               | <ul> <li>1 = Data Source 2 inverted signal is enabled for Gate 2</li> <li>0 = Data Source 2 inverted signal is disabled for Gate 2</li> </ul>         |                                      |                 |                   |                  |                 |       |  |  |  |

| bit 9         |                                                                                                                                                       | 2 Data Source                        | •               |                   |                  |                 |       |  |  |  |

|               |                                                                                                                                                       | rce 1 non-inver<br>rce 1 non-inver   | •               |                   |                  |                 |       |  |  |  |

| bit 8         |                                                                                                                                                       | 2 Data Source                        | -               |                   |                  |                 |       |  |  |  |

|               |                                                                                                                                                       | rce 1 inverted s<br>rce 1 inverted s |                 |                   |                  |                 |       |  |  |  |

| bit 7         |                                                                                                                                                       | 1 Data Source                        | -               |                   |                  |                 |       |  |  |  |

|               |                                                                                                                                                       | rce 4 non-inver<br>rce 4 non-inver   |                 |                   |                  |                 |       |  |  |  |

| bit 6         | <ul> <li>0 = Data Source 4 non-inverted signal is disabled for Gate 1</li> <li>G1D4N: Gate 1 Data Source 4 Negated Enable bit</li> </ul>              |                                      |                 |                   |                  |                 |       |  |  |  |

|               | <ul> <li>1 = Data Source 4 inverted signal is enabled for Gate 1</li> <li>0 = Data Source 4 inverted signal is disabled for Gate 1</li> </ul>         |                                      |                 |                   |                  |                 |       |  |  |  |

| bit 5         |                                                                                                                                                       | 1 Data Source                        | -               |                   |                  |                 |       |  |  |  |

|               | 1 = Data Sour                                                                                                                                         | rce 3 non-inver<br>rce 3 non-inver   | ed signal is er | nabled for Gate   |                  |                 |       |  |  |  |

| bit 4         |                                                                                                                                                       | 1 Data Source                        | -               |                   |                  |                 |       |  |  |  |

|               | 1 = Data Sour                                                                                                                                         | rce 3 inverted s<br>rce 3 inverted s | ignal is enable | ed for Gate 1     |                  |                 |       |  |  |  |

### REGISTER 22-26: ADTRIGXL: ADC CHANNEL TRIGGER x SELECTION REGISTER LOW

(x = 0 to 5)

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0          | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|----------------|-------|-------|

|        | _   | _   |       | TRO   | GSRC(4x+1)<4:0 | )>    |       |

| bit 15 |     |     |       |       |                |       | bit 8 |

|        |     |     |       |       |                |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0          | R/W-0 | R/W-0 |

| —      | —   | _   |       | TR    | GSRC(4x)<4:0   | >     |       |

| bit 7  |     |     |       |       |                |       | bit 0 |

|        |     |     |       |       |                |       |       |

### Legend:

bit

bit

| 3                 |                  |                               |                    |

|-------------------|------------------|-------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read a | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |

#### bit 15-13 Unimplemented: Read as '0'

| t 12-8 | TRGSRC(4x+1)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits |

|--------|----------------------------------------------------------------------------------|

|        | 11111 = ADTRG31                                                                  |

|        | 11110 = PTG Trigger Output 12                                                    |

|        | 11101 = PWM Generator 6 current-limit trigger                                    |

|        | 11100 = PWM Generator 5 current-limit trigger                                    |

|        | 11011 = PWM Generator 4 current-limit trigger                                    |

|        | 11010 = PWM Generator 3 current-limit trigger                                    |

|        | 11001 = PWM Generator 2 current-limit trigger                                    |

|        | 11000 = PWM Generator 1 current-limit trigger                                    |

|        | 10111 = Output Compare 2 trigger                                                 |

|        | 10110 = Output Compare 1 trigger                                                 |

|        | 10101 = CLC2 output                                                              |

|        | 10100 = PWM Generator 6 secondary trigger                                        |

|        | 10011 = PWM Generator 5 secondary trigger                                        |

|        | 10010 = PWM Generator 4 secondary trigger                                        |

|        | 10001 = PWM Generator 3 secondary trigger                                        |

|        | 10000 = PWM Generator 2 secondary trigger                                        |

|        | 01111 = PWM Generator 1 secondary trigger                                        |

|        | 01110 = PWM secondary Special Event Trigger                                      |

|        | 01101 = Timer2 period match                                                      |

|        | 01100 = Timer1 period match                                                      |

|        | 01011 = CLC1 output                                                              |

|        | 01010 = PWM Generator 6 primary trigger                                          |

|        | 01001 = PWM Generator 5 primary trigger                                          |

|        | 01000 = PWM Generator 4 primary trigger                                          |

|        | 00111 = PWM Generator 3 primary trigger                                          |

|        | 00110 = PWM Generator 2 primary trigger                                          |

|        | 00101 = PWM Generator 1 primary trigger                                          |

|        | 00100 = PWM Special Event Trigger<br>00011 = Reserved                            |

|        | 00011 – Reserved                                                                 |

|        | 000001 = Common software trigger                                                 |

|        | 00000 = No trigger is enabled                                                    |

|        |                                                                                  |

| t 7-5  | Unimplemented: Read as '0'                                                       |

|        |                                                                                  |

### REGISTER 22-27: ADTRIGXH: ADC CHANNEL TRIGGER x SELECTION REGISTER HIGH (x = 0 to 5) (CONTINUED)

| bit 4-0 | TRGSRC(4x+2)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits |

|---------|----------------------------------------------------------------------------------|

|         | 11111 = ADTRG31                                                                  |

|         | 11110 = PTG Trigger Output 30                                                    |

|         | 11101 = PWM Generator 6 current-limit trigger                                    |

|         | 11100 = PWM Generator 5 current-limit trigger                                    |

|         | 11011 = PWM Generator 4 current-limit trigger                                    |

|         | 11010 = PWM Generator 3 current-limit trigger                                    |

|         | 11001 = PWM Generator 2 current-limit trigger                                    |

|         | 11000 = PWM Generator 1 current-limit trigger                                    |

|         | 10111 = Output Compare 2 trigger                                                 |

|         | 10110 = Output Compare 1 trigger                                                 |

|         | 10101 = CLC2 output                                                              |

|         | 10100 = PWM Generator 6 secondary trigger                                        |

|         | 10011 = PWM Generator 5 secondary trigger                                        |

|         | 10010 = PWM Generator 4 secondary trigger                                        |

|         | 10001 = PWM Generator 3 secondary trigger                                        |

|         | 10000 = PWM Generator 2 secondary trigger                                        |

|         | 01111 = PWM Generator 1 secondary trigger                                        |

|         | 01110 = PWM secondary Special Event Trigger                                      |

|         | 01101 = Timer2 period match                                                      |

|         | 01100 = Timer1 period match                                                      |

|         | 01011 = CLC1 output                                                              |

|         | 01010 = PWM Generator 6 primary trigger                                          |

|         | 01001 = PWM Generator 5 primary trigger                                          |

|         | 01000 = PWM Generator 4 primary trigger                                          |

|         | 00111 = PWM Generator 3 primary trigger                                          |

|         | 00110 = PWM Generator 2 primary trigger                                          |

|         | 00101 = PWM Generator 1 primary trigger<br>00100 = PWM Special Event Trigger     |

|         | 00010 = P Win Special Event Higger                                               |

|         | 00011 – Reserved<br>00010 = Level software trigger                               |

|         |                                                                                  |

00001 = Common software trigger

00000 = No trigger is enabled

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter is changed as a result of the instruction, or a PSV or Table Read is performed. In these cases, the execution takes multiple instruction cycles, with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

**Note:** For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

| Field           | Description                                                                          |

|-----------------|--------------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                      |

| (text)          | Means "content of text"                                                              |

| [text]          | Means "the location addressed by text"                                               |

| {}              | Optional field or operation                                                          |

| a ∈ {b, c, d}   | a is selected from the set of values b, c, d                                         |

| <n:m></n:m>     | Register bit field                                                                   |

| .b              | Byte mode selection                                                                  |

| .d              | Double-Word mode selection                                                           |

| .S              | Shadow register select                                                               |

| .W              | Word mode selection (default)                                                        |

| Acc             | One of two accumulators {A, B}                                                       |

| AWB             | Accumulator Write-Back Destination Address register ∈ {W13, [W13]+ = 2}              |

| bit4            | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$        |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |

| Expr            | Absolute address, label or expression (resolved by the linker)                       |

| f               | File register address ∈ {0x00000x1FFF}                                               |

| lit1            | 1-bit unsigned literal $\in \{0,1\}$                                                 |

| lit4            | 4-bit unsigned literal $\in \{015\}$                                                 |

| lit5            | 5-bit unsigned literal $\in \{031\}$                                                 |

| lit8            | 8-bit unsigned literal $\in \{0255\}$                                                |

| lit10           | 10-bit unsigned literal $\in$ {0255} for Byte mode, {0:1023} for Word mode           |

| lit14           | 14-bit unsigned literal $\in \{016384\}$                                             |

| lit16           | 16-bit unsigned literal $\in$ {065535}                                               |

| lit23           | 23-bit unsigned literal $\in$ {08388608}; LSb must be '0'                            |

| None            | Field does not require an entry, can be blank                                        |

| OA, OB, SA, SB  | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate          |

| PC              | Program Counter                                                                      |

| Slit10          | 10-bit signed literal $\in$ {-512511}                                                |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                       |

| Wb              | Base W register ∈ {W0W15}                                                            |

| Wd              | Destination W register $\in$ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                |

| Wdo             | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

| Wm,Wn           | Dividend, Divisor Working register pair (Direct Addressing)                          |

### TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

### TABLE 30-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACT          | ERISTICS                     |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |  |  |  |

|---------------------|------------------------------|------|-------------------------------------------------------|---------------------|--|--|--|

| Parameter Typ. Max. |                              |      | Units                                                 | Units Conditions    |  |  |  |

| Power-Down          | Current (IPD) <sup>(1)</sup> |      |                                                       |                     |  |  |  |

| DC60d               | 15                           | 110  | μA                                                    | -40°C               |  |  |  |

| DC60a               | 20                           | 150  | μA                                                    | +25°C<br>+85°C 3.3V |  |  |  |

| DC60b               | 150                          | 500  | μA                                                    |                     |  |  |  |

| DC60c               | 500                          | 1200 | μA                                                    | +125°C              |  |  |  |

Note 1: IPD (Sleep) current is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all set)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

### TABLE 30-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT $(\triangle IwDT)^{(1)}$

| DC CHARACTERISTICS |      |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |        |      |  |  |  |

|--------------------|------|------|-------------------------------------------------------|--------|------|--|--|--|

| Parameter No.      | Тур. | Max. | Units Conditions                                      |        |      |  |  |  |

| DC61d              | 1    | 10   | μΑ                                                    | -40°C  |      |  |  |  |

| DC61a              | 1    | 10   | μA                                                    | +25°C  |      |  |  |  |

| DC61b              | 2    | 17   | μA                                                    | +85°C  | 3.3V |  |  |  |

| DC61c              | 2    | 20   | μA                                                    | +125°C |      |  |  |  |

**Note 1:** The  $\triangle$ IWDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

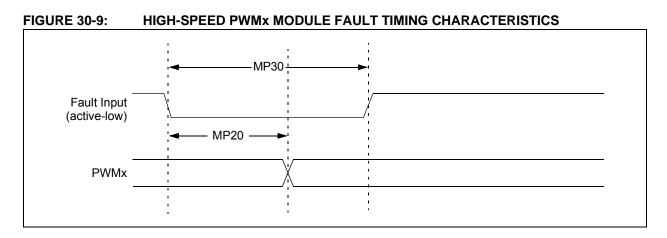

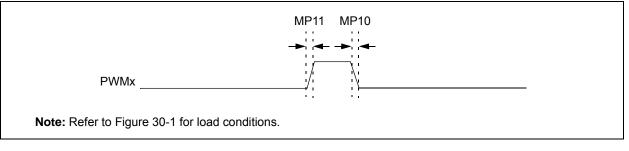

### FIGURE 30-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS

### TABLE 30-30: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |   |    |    |                    |

|--------------------|--------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|----|--------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>       | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                                                       |   |    |    |                    |

| MP10               | TFPWM  | PWMx Output Fall Time               | _                                                                                                                                                                                                                                                                                     | _ | —  | ns | See Parameter DO32 |

| MP11               | TRPWM  | PWMx Output Rise Time               | —                                                                                                                                                                                                                                                                                     | _ | —  | ns | See Parameter DO31 |

| MP20               | Tfd    | Fault Input ↓ to PWMx<br>I/O Change | _                                                                                                                                                                                                                                                                                     | _ | 15 | ns |                    |

| MP30               | Tfh    | Fault Input Pulse Width             | 15                                                                                                                                                                                                                                                                                    | — | —  | ns |                    |

**Note 1:** These parameters are characterized but not tested in manufacturing.

### TABLE 30-31: SPI1, SPI2 AND SPI3 MAXIMUM DATA/CLOCK RATE SUMMARY<sup>(1)</sup>

| AC CHARA             | CTERISTICS                               |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |  |

| 15 MHz               | Table 30-32                              | _                                           | _                                                     | 0,1 | 0,1 | 0,1 |  |  |

| 9 MHz                | _                                        | Table 30-33                                 | —                                                     | 1   | 0,1 | 1   |  |  |

| 9 MHz                | —                                        | Table 30-34                                 | —                                                     | 0   | 0,1 | 1   |  |  |

| 15 MHz               | —                                        | —                                           | Table 30-35                                           | 1   | 0   | 0   |  |  |

| 11 MHz               | _                                        | —                                           | Table 30-36                                           | 1   | 1   | 0   |  |  |

| 15 MHz               | _                                        | —                                           | Table 30-37                                           | 0   | 1   | 0   |  |  |

| 11 MHz               | —                                        | —                                           | Table 30-38                                           | 0   | 0   | 0   |  |  |

**Note 1:** Pertaining to SPI3: dsPIC33EPXXXGS702, dsPIC33EPXXXGSX04 and dsPIC33EPXXXGSX05 devices with a remappable SCK3 pin.

### FIGURE 30-11: SPI1, SPI2 AND SPI3 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS<sup>(1,2)</sup>

Note 1: Pertaining to SPI3: dsPIC33EPXXXGS702, dsPIC33EPXXXGSX04 and dsPIC33EPXXXGSX05 devices with a remappable SCK3 pin.

**2:** Refer to Figure 30-1 for load conditions.

| AC CHARACTERISTICS |        |                                   | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)(5)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |            |         |       |                                    |  |

|--------------------|--------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|-------|------------------------------------|--|

| Param<br>No.       | Symbol | Characteristics                   | Min.                                                                                                                                                                                                    | Typical    | Max.    | Units | Conditions                         |  |

|                    |        | ADC                               | Accuracy: S                                                                                                                                                                                             | ingle-Ende | d Input |       | ·                                  |  |

| AD20b              | Nr     | Resolution                        |                                                                                                                                                                                                         | 12         |         | bits  |                                    |  |

| AD21b              | INL    | Integral Nonlinearity             | > 5                                                                                                                                                                                                     |            | < 5     | LSb   | AVss = 0V, AVDD = 3.3V             |  |

| AD22b              | DNL    | Differential Nonlinearity         | > -1                                                                                                                                                                                                    | —          | < 1     | LSb   | AVss = 0V, AVDD = 3.3V<br>(Note 2) |  |

| AD23b              | Gerr   | Gain Error<br>(Dedicated Core)    | > 0                                                                                                                                                                                                     | 8          | < 15    | LSb   | AVss = 0V, AVdd = 3.3V             |  |

|                    |        | Gain Error<br>(Shared Core)       | > 5                                                                                                                                                                                                     | 15         | < 22    | LSb   |                                    |  |

| AD24b              | Eoff   | Offset Error<br>(Dedicated Core)  | > 2                                                                                                                                                                                                     | 9          | < 15    | LSb   | AVss = 0V, AVdd = 3.3V             |  |

|                    |        | Offset Error<br>(Shared Core)     | > 5                                                                                                                                                                                                     | 17         | < 22    | LSb   |                                    |  |

| AD25b              | _      | Monotonicity                      | _                                                                                                                                                                                                       | _          | _       | _     | Guaranteed                         |  |

|                    |        |                                   | Dynamic P                                                                                                                                                                                               | erformanc  | e       |       |                                    |  |

| AD31b              | SINAD  | Signal-to-Noise and<br>Distortion | 63                                                                                                                                                                                                      | _          | > 65    | dB    | (Notes 3, 4)                       |  |

| AD34b              | ENOB   | Effective Number of Bits          | 10.3                                                                                                                                                                                                    |            | _       | bits  | (Notes 3, 4)                       |  |

### TABLE 30-52: ADC MODULE SPECIFICATIONS (CONTINUED)

**Note 1:** These parameters are not characterized or tested in manufacturing.

2: No missing codes, limits based on characterization results.

3: These parameters are characterized but not tested in manufacturing.

4: Characterized with a 15 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is ensured, but not characterized.

### TABLE 30-55: DACx MODULE SPECIFICATIONS

|              |        | $ \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(2)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array} $ |                               |      |      |      |                                                                             |

|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------|------|------|-----------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                                                                                                                                                                                                                                                                              | Min. Typ. Max. Units Comments |      |      |      | Comments                                                                    |

| DA01         | EXTREF | External Voltage Reference <sup>(1)</sup>                                                                                                                                                                                                                                                   | 1                             | _    | AVdd | V    |                                                                             |

| DA02         | CVRES  | Resolution                                                                                                                                                                                                                                                                                  |                               | 12   |      | bits |                                                                             |

| DA03         | INL    | Integral Nonlinearity Error                                                                                                                                                                                                                                                                 | -16                           | -12  | 0    | LSB  |                                                                             |

| DA04         | DNL    | Differential Nonlinearity Error                                                                                                                                                                                                                                                             | -1.8                          | ±1   | 1.8  | LSB  |                                                                             |

| DA05         | EOFF   | Offset Error                                                                                                                                                                                                                                                                                | -8                            | 3    | 15   | LSB  |                                                                             |

| DA06         | EG     | Gain Error                                                                                                                                                                                                                                                                                  | -1.2                          | -0.5 | 0    | %    |                                                                             |

| DA07         | TSET   | Settling Time <sup>(1)</sup>                                                                                                                                                                                                                                                                | —                             | 700  | _    | ns   | Output with 2% of desired<br>output voltage with a<br>10-90% or 90-10% step |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

2: The DACx module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

| DC CHARACTERISTICS |         |                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                      |               |     |                                                                                              |  |

|--------------------|---------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------|-----|----------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol  | Characteristic                                                     | Min.                                                                                                                                                                                                                                                                                          | Min. Typ. Max. Units |               |     |                                                                                              |  |

| DA11               | RLOAD   | Resistive Output Load<br>Impedance                                 | 10K                                                                                                                                                                                                                                                                                           |                      | —             | Ohm |                                                                                              |  |

| DA11a              | CLOAD   | Output Load<br>Capacitance                                         | _                                                                                                                                                                                                                                                                                             |                      | 35            | pF  | Including output pin<br>capacitance                                                          |  |

| DA12               | Ιουτ    | Output Current Drive<br>Strength                                   | _                                                                                                                                                                                                                                                                                             | 300                  | —             | μA  | Sink and source                                                                              |  |

| DA13               | VRANGE  | Output Drive Voltage<br>Range at Current<br>Drive of 300 µA        | AVss + 250 mV                                                                                                                                                                                                                                                                                 |                      | AVDD – 900 mV | V   |                                                                                              |  |

| DA14               | VLRANGE | Output Drive Voltage<br>Range at Reduced<br>Current Drive of 50 µA | AVss + 50 mV                                                                                                                                                                                                                                                                                  | _                    | AVDD – 500 mV | V   |                                                                                              |  |

| DA15               | IDD     | Current Consumed<br>when Module is<br>Enabled                      |                                                                                                                                                                                                                                                                                               | _                    | 1.3 x IOUT    | μA  | Module will always<br>consume this current,<br>even if no load is<br>connected to the output |  |