Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 33                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · ·                                                                              |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 17x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-TQFP                                                                          |

| Supplier Device Package    | 48-TQFP (7x7)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs805t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

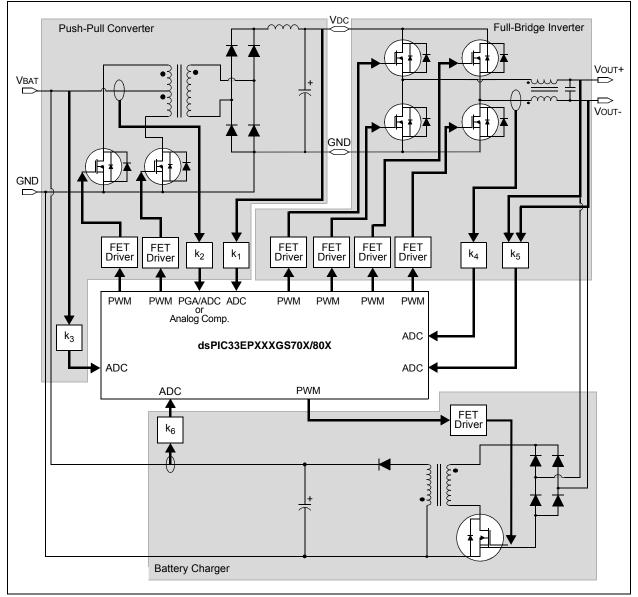

## FIGURE 2-6: OFF-LINE UPS

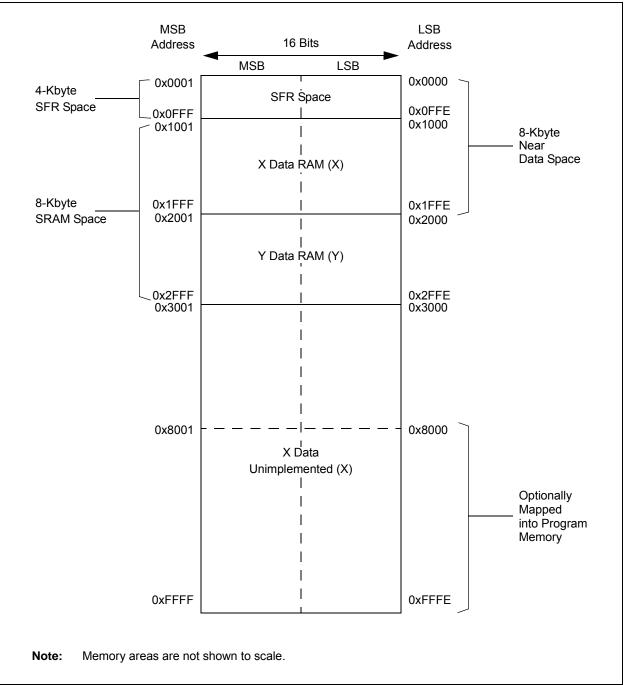

#### FIGURE 4-6: DATA MEMORY MAP FOR dsPIC33EP64GS70X/80X DEVICES

| Register       | Address  | All Resets                              | Register      | Address   | All Resets                              | Register   | Address | All Resets |

|----------------|----------|-----------------------------------------|---------------|-----------|-----------------------------------------|------------|---------|------------|

| NVM            |          |                                         | C2INTF        | 78A       | 000000000000000000000000000000000000000 | C2RXF1SID  | 7C4     | *****      |

| NVMCON         | 728      | 000000000000000000000000000000000000000 | C2INTE        | 78C       | 000000000000000000000000000000000000000 | C2RXF1EID  | 7C6     | *****      |

| NVMADR         | 72A      | 000000000000000000000000000000000000000 | C2EC          | 78E       | 000000000000000000000000000000000000000 | C2RXF2SID  | 7C8     | *****      |

| NVMADRU        | 72C      | 000000000000000000000000000000000000000 | C2CFG1        | 790       | 000000000000000000000000000000000000000 | C2RXF2EID  | 7CA     | *****      |

| NVMKEY         | 72E      | 000000000000000000000000000000000000000 | C2CFG2        | 792       | 0x000xxxxxxxxxx                         | C2RXF3SID  | 7CC     | *****      |

| NVMSRCADR      | 730      | 000000000000000000000000000000000000000 | C2FEN1        | 794       | 11111111111111111                       | C2RXF3EID  | 7CE     | *****      |

| NVMSRCADRH     | 732      | 000000000000000000000000000000000000000 | C2FMSKSEL1    | 798       | 000000000000000000000000000000000000000 | C2RXF4SID  | 7D0     | *****      |

| System Control |          |                                         | C2FMSKSEL2    | 79A       | 0000000000000000000                     | C2RXF4EID  | 7D2     | *****      |

| RCON           | 740      | 0x00x0x01x0xxxxx                        | CAN (WIN (C1  | CTR1<0>)  | = 0)                                    | C2RXF5SID  | 7D4     | *****      |

| OSCCON         | 742      | 0000000000000000000                     | C2RXFUL1      | 7A0       | 0000000000000000000                     | C2RXF5EID  | 7D6     | *****      |

| CLKDIV         | 744      | 0000000000000000000                     | C2RXFUL2      | 7A2       | 0000000000000000000                     | C2RXF6SID  | 7D8     | *****      |

| PLLFBD         | 746      | 000000000000000000000000000000000000000 | C2RXOVF1      | 7A8       | 000000000000000000000000000000000000000 | C2RXF6EID  | 7DA     | *****      |

| OSCTUN         | 748      | 000000000000000000000000000000000000000 | C2RXOVF2      | 7AA       | 000000000000000000000000000000000000000 | C2RXF7SID  | 7DC     | *****      |

| LFSR           | 74C      | 000000000000000000000000000000000000000 | C2TR01CON     | 7B0       | 000000000000000000000000000000000000000 | C2RXF7EID  | 7DE     | *****      |

| REFOCON        | 74E      | 0000000000000000000                     | C2TR23CON     | 7B2       | 0000000000000000000                     | C2RXF8SID  | 7E0     | *****      |

| ACLKCON        | 750      | 0000000000000000000                     | C2TR45CON     | 7B4       | 0000000000000000000                     | C2RXF8EID  | 7E2     | *****      |

| PMD            |          |                                         | C2TR67CON     | 7B6       | *****                                   | C2RXF9SID  | 7E4     | *****      |

| PMD1           | 760      | 0000000000000000000                     | C2RXD         | 7C0       | *****                                   | C2RXF9EID  | 7E6     | *****      |

| PMD2           | 762      | 000000000000000000000000000000000000000 | C2TXD         | 7C2       | *****                                   | C2RXF10SID | 7E8     | *****      |

| PMD3           | 764      | 000000000000000000000000000000000000000 | CAN (WIN (C10 | CTR1<0>): | = 1)                                    | C2RXF10EID | 7EA     | *****      |

| PMD4           | 766      | 000000000000000000000000000000000000000 | C2BUFPNT1     | 7A0       | 000000000000000000000000000000000000000 | C2RXF11SID | 7EC     | *****      |

| PMD6           | 76A      | 000000000000000000000000000000000000000 | C2BUFPNT2     | 7A2       | 000000000000000000000000000000000000000 | C2RXF11EID | 7EE     | *****      |

| PMD7           | 76C      | 000000000000000000000000000000000000000 | C2BUFPNT3     | 7A4       | 000000000000000000000000000000000000000 | C2RXF12SID | 7F0     | *****      |

| PMD8           | 76E      | 000000000000000000000000000000000000000 | C2BUFPNT4     | 7A6       | 000000000000000000000000000000000000000 | C2RXF12EID | 7F2     | *****      |

| CAN (WIN (C1CT | R1<0>) = | 0 or 1)                                 | C2RXM0SID     | 7B0       | *****                                   | C2RXF13SID | 7F4     | *****      |

| C2CTRL1        | 780      | 0000010010000000                        | C2RXM0EID     | 7B2       | *****                                   | C2RXF13EID | 7F6     | *****      |

| C2CTRL2        | 782      | 000000000000000000000000000000000000000 | C2RXM1SID     | 7B4       | *****                                   | C2RXF14SID | 7F8     | *****      |

| C2VEC          | 784      | 000000001000000                         | C2RXM1EID     | 7B6       | *****                                   | C2RXF14EID | 7FA     | *****      |

| C2FCTRL        | 786      | 000000000000000000000000000000000000000 | C2RXM2SID     | 7B8       | *****                                   | C2RXF15SID | 7FC     | *****      |

| C2FIFO         | 788      | 000000000000000000000000000000000000000 | C2RXM2EID     | 7BA       | *****                                   | C2RXF15EID | 7FE     | *****      |

### TABLE 4-9:SFR BLOCK 700h

Legend: x = unknown or indeterminate value. Address values are in hexadecimal. Reset values are in binary.

### TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

|                                   | Vector  | IRQ     |                   | In                    | terrupt Bit Lo        | cation                         |

|-----------------------------------|---------|---------|-------------------|-----------------------|-----------------------|--------------------------------|

| Interrupt Source                  | #       | #       | IVT Address       | Flag                  | Enable                | Priority                       |

| AN17 Conversion Done              | 168     | 160     | 0x000154          | IFS10<0><br>AN17IF    | IEC10<0><br>AN17IE    | IPC40<2:0><br>AN17IP<2:0>      |

| AN18 Conversion Done              | 169     | 161     | 0x000156          | IFS10<1><br>AN18IF    | IEC10<1><br>AN18IE    | IPC40<6:4><br>AN18IP<2:0>      |

| AN19 Conversion Done              | 170     | 162     | 0x000158          | IFS10<2><br>AN19IF    | IEC10<2><br>AN19IE    | IPC40<10:8><br>AN19IP<2:0>     |

| AN20 Conversion Done              | 171     | 163     | 0x00015A          | IFS10<3><br>AN20IF    | IEC10<3><br>AN20IE    | IPC40<14:12><br>AN20IP<2:0>    |

| AN21 Conversion Done              | 172     | 164     | 0x00015C          | IFS10<4><br>AN21IF    | IEC10<4><br>AN21IE    | IPC41<2:0><br>AN21IP<2:0>      |

| Reserved                          | 173-180 | 165-172 | 0x00015C-0x00016C | _                     | —                     | —                              |

| I2C1 – I2C1 Bus Collision         | 181     | 173     | 0x00016E          | IFS10<13><br>I2C1IF   | IEC10<13><br>I2C1IE   | IPC43<6:4><br>I2C1IP<2:0>      |

| I2C2 – I2C2 Bus Collision         | 182     | 174     | 0x000170          | IFS10<14><br>I2C2IF   | IEC10<14><br>I2C2IE   | IPC43<10:8><br>I2C2IP<2:0>     |

| Reserved                          | 183-184 | 175-176 | 0x000172-0x000174 | —                     | _                     | —                              |

| ADCMP0 – ADC Digital Comparator 0 | 185     | 177     | 0x000176          | IFS11<1><br>ADCMP0IF  | IEC11<1><br>ADCMP0IE  | IPC44<6:4><br>ADCMP0IP<2:0>    |

| ADCMP1 – ADC Digital Comparator 1 | 186     | 178     | 0x000178          | IFS11<2><br>ADCMP1IF  | IEC11<2><br>ADCMP1IE  | IPC44<10:8><br>ADCMP1IP<2:0>   |

| ADFLTR0 – ADC Filter 0            | 187     | 179     | 0x00017A          | IFS11<3><br>ADFLTR0IF | IEC11<3><br>ADFLTR0IE | IPC44<14:12><br>ADFLTR0IP<2:0> |

| ADFLTR1 – ADC Filter 1            | 188     | 180     | 0x00017C          | IFS11<4><br>ADFLTR1IF | IEC11<4><br>ADFLTR1IE | IPC45<2:0><br>ADFLTR1IP<2:0>   |

| Reserved                          | 189-253 | 181-245 | 0x00017E-0x000192 | —                     | —                     | _                              |

#### REGISTER 8-5: DMAxSTBH: DMA CHANNEL x START ADDRESS REGISTER B (HIGH)

| U-0    | U-0   | U-0   | U-0   | R/W-0  | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        | _     |       |       |        | —     |       | _     |

| bit 15 |       |       |       |        |       |       | bit 8 |

|        |       |       |       |        |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | STB<  | 23:16> |       |       |       |

| bit 7  |       |       |       |        |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: DMA Secondary Start Address bits (source or destination)

### REGISTER 8-6: DMAxSTBL: DMA CHANNEL x START ADDRESS REGISTER B (LOW)

| R/W-0                                                                 | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|-----------------------------------------------------------------------|-------|-------|-------|------------------------------------|-------|-------|-------|

|                                                                       |       |       | STB   | <15:8>                             |       |       |       |

| bit 15                                                                |       |       |       |                                    |       |       | bit 8 |

|                                                                       |       |       |       |                                    |       |       |       |

| R/W-0                                                                 | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                                                       |       |       | STE   | 3<7:0>                             |       |       |       |

| bit 7                                                                 |       |       |       |                                    |       |       | bit 0 |

|                                                                       |       |       |       |                                    |       |       |       |

| Legend:                                                               |       |       |       |                                    |       |       |       |

| R = Readable bit W = Writable bit                                     |       |       | oit   | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is un |       |       |       | x = Bit is unkr                    | nown  |       |       |

bit 15-0 STB<15:0>: DMA Secondary Start Address bits (source or destination)

## REGISTER 8-7: DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                                                         | R/W-0 | R/W-0 | R/W-0                              | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|---------------------------------------------------------------|-------|-------|------------------------------------|--------|-------|-------|-------|

|                                                               |       |       | PAD                                | <15:8> |       |       |       |

| bit 15                                                        |       |       |                                    |        |       |       | bit 8 |

|                                                               |       |       |                                    |        |       |       |       |

| R/W-0                                                         | R/W-0 | R/W-0 | R/W-0                              | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|                                                               |       |       | PAI                                | )<7:0> |       |       |       |

| bit 7                                                         |       |       |                                    |        |       |       | bit 0 |

|                                                               |       |       |                                    |        |       |       |       |

| Legend:                                                       |       |       |                                    |        |       |       |       |

| R = Readable bit W = Writable bit                             |       | bit   | U = Unimplemented bit, read as '0' |        |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = E |       |       | x = Bit is unkı                    | nown   |       |       |       |

bit 15-0 PAD<15:0>: DMA Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

# REGISTER 8-8: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0             | U-0   | R/W-0            | R/W-0                                               | R/W-0             | R/W-0 | R/W-0           | R/W-0 |  |

|-----------------|-------|------------------|-----------------------------------------------------|-------------------|-------|-----------------|-------|--|

| —               | _     |                  | CNT<13:8> <sup>(2)</sup>                            |                   |       |                 |       |  |

| bit 15          |       |                  |                                                     |                   |       |                 | bit 8 |  |

|                 |       |                  |                                                     |                   |       |                 |       |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                               | R/W-0             | R/W-0 | R/W-0           | R/W-0 |  |

|                 |       |                  | CNT<                                                | <7:0> <b>(2)</b>  |       |                 |       |  |

| bit 7           |       |                  |                                                     |                   |       |                 | bit 0 |  |

|                 |       |                  |                                                     |                   |       |                 |       |  |

| Legend:         |       |                  |                                                     |                   |       |                 |       |  |

| R = Readable    | bit   | W = Writable b   | W = Writable bit U = Unimplemented bit, read as '0' |                   |       | 1 as '0'        |       |  |

| -n = Value at F | POR   | '1' = Bit is set |                                                     | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

### REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

| U-0                               | U-0                 | U-0                                  | U-0            | U-0              | U-0     | U-0             | U-0   |

|-----------------------------------|---------------------|--------------------------------------|----------------|------------------|---------|-----------------|-------|

| —                                 | —                   | —                                    | —              | —                | —       | —               | —     |

| bit 15                            |                     |                                      |                |                  |         |                 | bit 8 |

|                                   |                     |                                      |                |                  |         |                 |       |

| U-0                               | U-0                 | U-0                                  | U-0            | R-1              | R-1     | R-1             | R-1   |

| _                                 | —                   |                                      | —              |                  | LSTCH   | 1<3:0>          |       |

| bit 7                             |                     |                                      |                |                  |         |                 | bit 0 |

|                                   |                     |                                      |                |                  |         |                 |       |

| Legend:                           |                     |                                      |                |                  |         |                 |       |

| R = Readable bit W = Writable bit |                     | bit                                  | U = Unimpler   | mented bit, read | as '0'  |                 |       |

| -n = Value a                      | It POR              | '1' = Bit is set                     |                | '0' = Bit is cle | ared    | x = Bit is unkr | nown  |

|                                   |                     |                                      |                |                  |         |                 |       |

| bit 15-4                          | Unimplemen          | ted: Read as '                       | 0'             |                  |         |                 |       |

| bit 3-0                           | LSTCH<3:0>          | : Last DMA Co                        | ntroller Chanr | nel Active Statu | us bits |                 |       |

|                                   | 1111 <b>= No Di</b> | MA transfer ha                       | s occurred sin | ce system Res    | set     |                 |       |

|                                   | 1110 <b>= Rese</b>  | rved                                 |                |                  |         |                 |       |

|                                   | •                   |                                      |                |                  |         |                 |       |

|                                   | •                   |                                      |                |                  |         |                 |       |

|                                   | •                   |                                      |                |                  |         |                 |       |

|                                   | 0100 = Reser        |                                      |                | Observal 0       |         |                 |       |

|                                   |                     | lata transfer wa                     |                |                  |         |                 |       |

|                                   |                     | data transfer wa                     |                |                  |         |                 |       |

|                                   |                     | lata transfer wa<br>lata transfer wa |                |                  |         |                 |       |

|                                   |                     |                                      | as nanuleu by  |                  |         |                 |       |

### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

bit 4-0

**PLLPRE<4:0>:** PLL Phase Detector Input Divider Select bits (also denoted as 'N1', PLL prescaler) 11111 = Input divided by 33

•

00001 = Input divided by 3

00000 = Input divided by 2 (default)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- **2:** This bit is cleared when the ROI bit is set and an interrupt occurs.

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

#### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0   |

|--------|-----|-----|-----|-----|-----|-----|---------|

| —      | —   | —   | —   | —   | —   | —   | PLLDIV8 |

| bit 15 |     |     |     |     |     |     | bit 8   |

| R/W-0 | R/W-0 | R/W-1 | R/W-1 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | PLLDI | V<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-9 Unimplemented: Read as '0'

### REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| -                                 |                          |                  |               |                                   |                 |          |       |

|-----------------------------------|--------------------------|------------------|---------------|-----------------------------------|-----------------|----------|-------|

| U-0                               | U-0                      | U-0              | U-0           | U-0                               | U-0             | U-0      | U-0   |

| —                                 | —                        | —                | —             | —                                 |                 | —        |       |

| bit 15                            |                          |                  |               |                                   |                 |          | bit 8 |

|                                   |                          |                  |               | =                                 |                 | =        |       |

| U-0                               | U-0                      | R/W-0            | R/W-0         | R/W-0                             | R/W-0           | R/W-0    | R/W-0 |

|                                   | —                        |                  |               | TUN                               | <5:0>           |          |       |

| bit 7                             |                          |                  |               |                                   |                 |          | bit 0 |

|                                   |                          |                  |               |                                   |                 |          |       |

| Legend:                           |                          |                  |               |                                   |                 |          |       |

| R = Readable bit W = Writable bit |                          |                  |               | U = Unimplen                      | nented bit, rea | d as '0' |       |

| -n = Value at                     | POR                      | '1' = Bit is set |               | '0' = Bit is cleared x = Bit is u |                 |          | nown  |

|                                   |                          |                  |               |                                   |                 |          |       |

| bit 15-6                          | Unimplemen               | ted: Read as '0  | ,             |                                   |                 |          |       |

| bit 5-0                           | <b>TUN&lt;5:0&gt;:</b> F | RC Oscillator To | uning bits    |                                   |                 |          |       |

|                                   |                          | ximum frequen    |               |                                   | 7 MHz)          |          |       |

|                                   | 011110 <b>= Ce</b>       | nter frequency   | + 1.41% (7.47 | 4 MHz)                            |                 |          |       |

|                                   | •                        |                  |               |                                   |                 |          |       |

|                                   | •                        |                  |               |                                   |                 |          |       |

|                                   | 000001 <b>= Ce</b>       | nter frequency   | + 0.047% (7.3 | 73 MHz)                           |                 |          |       |

|                                   | 000000 <b>= Ce</b>       | nter frequency   | (7.37 MHz noi | minal)                            |                 |          |       |

|                                   | 111111 <b>= Ce</b>       | nter frequency   | - 0.047% (7.3 | 67 MHz)                           |                 |          |       |

|                                   | •                        |                  |               |                                   |                 |          |       |

|                                   | •                        |                  |               |                                   |                 |          |       |

|                                   | 100001 <b>= Ce</b>       | nter frequency   | - 1.457% (7.2 | 63 MHz)                           |                 |          |       |

|                                   |                          | nimum frequenc   | •             | ,                                 | /IHz)           |          |       |

|                                   |                          |                  |               |                                   |                 |          |       |

### REGISTER 11-27: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SYNCI1R7 | SYNCI1R6 | SYNCI1R5 | SYNCI1R4 | SYNCI1R3 | SYNCI1R2 | SYNCI1R1 | SYNCI1R0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | —   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 SYNCI1R<7:0>: Assign PWM Synchronization Input 1 (SYNCI1) to the Corresponding RPn Pin bits See Table 11-11 which contains a list of remappable inputs for the index value.

bit 7-0 Unimplemented: Read as '0'

### REGISTER 11-28: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SYNCI2R7 | SYNCI2R6 | SYNCI2R5 | SYNCI2R4 | SYNCI2R3 | SYNCI2R2 | SYNCI2R1 | SYNCI2R0 |

| bit 7    | •        |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **SYNCI2R<7:0>:** Assign PWM Synchronization Input 2 (SYNCI2) to the Corresponding RPn Pin bits See Table 11-11 which contains a list of remappable inputs for the index value.

# 13.2 Timer2/3 and Timer4/5 Control Registers

### REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

| R/W-0                   | U-0                                                                                                                   | R/W-0                                           | U-0           | U-0              | U-0              | U-0                | U-0   |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------|------------------|------------------|--------------------|-------|

| TON                     |                                                                                                                       | TSIDL                                           | —             |                  |                  | _                  | —     |

| bit 15                  |                                                                                                                       | I                                               |               |                  |                  | •                  | bit 8 |

|                         |                                                                                                                       |                                                 |               |                  |                  |                    |       |

| U-0                     | R/W-0                                                                                                                 | R/W-0                                           | R/W-0         | R/W-0            | U-0              | R/W-0              | U-0   |

| _                       | TGATE                                                                                                                 | TCKPS1                                          | TCKPS0        | T32              | _                | TCS <sup>(1)</sup> |       |

| bit 7                   |                                                                                                                       |                                                 |               |                  |                  |                    | bit ( |

|                         |                                                                                                                       |                                                 |               |                  |                  |                    |       |

| Legend:<br>R = Readable | hit                                                                                                                   | W = Writable                                    | bit           |                  | nonted hit read  | d as 'O'           |       |

| -n = Value at l         |                                                                                                                       | '1' = Bit is set                                |               | '0' = Bit is cle | nented bit, read | x = Bit is unkn    | 014/0 |

|                         |                                                                                                                       |                                                 |               |                  | areu             |                    | 0001  |

| bit 15                  | <b>TON:</b> Timerx<br><u>When T32 = 1</u><br>1 = Starts 32-<br>0 = Stops 32-<br><u>When T32 = 0</u><br>1 = Starts 16- | L:<br>bit Timerx/y<br>bit Timerx/y<br><u>):</u> |               |                  |                  |                    |       |

|                         | 0 = Stops 16-                                                                                                         |                                                 |               |                  |                  |                    |       |

| bit 14                  | Unimplemented: Read as '0'                                                                                            |                                                 |               |                  |                  |                    |       |

| bit 13                  | TSIDL: Timer                                                                                                          | x Stop in Idle N                                | lode bit      |                  |                  |                    |       |

|                         |                                                                                                                       | ues module op<br>s module opera                 |               |                  | dle mode         |                    |       |

| bit 12-7                | Unimplemen                                                                                                            | ted: Read as '                                  | 0'            |                  |                  |                    |       |

| bit 6                   | When TCS =<br>This bit is igno<br>When TCS =<br>1 = Gated tim                                                         | ored.                                           | n is enabled  | Enable bit       |                  |                    |       |

| bit 5-4                 | TCKPS<1:0>                                                                                                            | : Timerx Input                                  | Clock Prescal | e Select bits    |                  |                    |       |

|                         | 11 = 1:256<br>10 = 1:64<br>01 = 1:8<br>00 = 1:1                                                                       |                                                 |               |                  |                  |                    |       |

| bit 3                   | T32: 32-Bit Ti                                                                                                        | mer Mode Sele                                   | ect bit       |                  |                  |                    |       |

|                         |                                                                                                                       | d Timery form<br>d Timery act a                 |               |                  |                  |                    |       |

| bit 2                   | Unimplemen                                                                                                            | ted: Read as '                                  | 0'            |                  |                  |                    |       |

| bit 1                   |                                                                                                                       | Clock Source S<br>clock is from pi              |               | e rising edge)   |                  |                    |       |

|                         | 0 = Internal cl                                                                                                       | ock (FP)                                        | ·             | · · ·            |                  |                    |       |

| bit 0                   | Unimplemen                                                                                                            | ' se heag <b>' Roat</b>                         | 0 <i>1</i>    |                  |                  |                    |       |

### REGISTER 18-4: SPIx STATL: SPIx STATUS REGISTER LOW (CONTINUED)

- bit 3 SPITBE: SPIx Transmit Buffer Empty Status bit 1 = SPIxTXB is empty 0 = SPIxTXB is not empty Standard Buffer mode: Automatically set in hardware when SPIx transfers data from SPIxTXB to SPIxTXSR. Automatically cleared in hardware when SPIxBUF is written, loading SPIxTXB. Enhanced Buffer mode: Indicates TXELM<5:0> = 000000. bit 2 Unimplemented: Read as '0' bit 1 SPITBF: SPIx Transmit Buffer Full Status bit 1 = SPIxTXB is full 0 = SPIxTXB not full Standard Buffer mode: Automatically set in hardware when SPIxBUF is written, loading SPIxTXB. Automatically cleared in hardware when SPIx transfers data from SPIxTXB to SPIxTXSR. Enhanced Buffer mode: Indicates TXELM<5:0> = 111111. SPIRBF: SPIx Receive Buffer Full Status bit bit 0 1 = SPIxRXB is full 0 = SPIxRXB is not full Standard Buffer mode: Automatically set in hardware when SPIx transfers data from SPIxRXSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB. Enhanced Buffer mode: Indicates RXELM<5:0> = 111111.

- **Note 1:** SPITUR is cleared when SPIEN = 0. When IGNTUR = 1, SPITUR provides dynamic status of the Transmit Underrun condition, but does not stop RX/TX operation and does not need to be cleared by software.

### REGISTER 22-4: ADCON2H: ADC CONTROL REGISTER 2 HIGH

| R-0, HSC | R-0, HSC | r-0 | r-0 | r-0 | r-0 | R/W-0    | R/W-0    |

|----------|----------|-----|-----|-----|-----|----------|----------|

| REFRDY   | REFERR   | —   | —   | —   | —   | SHRSAMC9 | SHRSAMC8 |

| bit 15   |          |     |     |     |     |          | bit 8    |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SHRSAMC7 | SHRSAMC6 | SHRSAMC5 | SHRSAMC4 | SHRSAMC3 | SHRSAMC2 | SHRSAMC1 | SHRSAMC0 |

| bit 7    | ·        |          |          |          |          |          | bit 0    |

| Legend:           | r = Reserved bit | U = Unimplemented bit, read as '0'      |  |

|-------------------|------------------|-----------------------------------------|--|

| R = Readable bit  | W = Writable bit | HSC = Hardware Settable/Clearable bit   |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |

| bit 15    | <b>REFRDY:</b> Band Gap and Reference Voltage Ready Flag bit<br>1 = Band gap is ready<br>0 = Band gap is not ready                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14    | <b>REFERR:</b> Band Gap or Reference Voltage Error Flag bit<br>1 = Band gap was removed after the ADC module was enabled (ADON = 1)<br>0 = No band gap error was detected                                        |

| bit 13-10 | Reserved: Maintain as '0'                                                                                                                                                                                        |

| bit 9-0   | <pre>SHRSAMC&lt;9:0&gt;: Shared ADC Core Sample Time Selection bits These bits specify the number of shared ADC Core Clock Periods (TADCORE) for the shared ADC core sample time. 111111111 = 1025 TADCORE</pre> |

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R-0, HSC | R/W-0   | R-0, HSC |

|---------|---------|---------|---------|---------|----------|---------|----------|

| REFSEL2 | REFSEL1 | REFSEL0 | SUSPEND | SUSPCIE | SUSPRDY  | SHRSAMP | CNVRTCH  |

| bit 15  |         |         |         |         |          |         | bit 8    |

| R/W-0       | R/W-0, HSC | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     |

|-------------|------------|-----------|-----------|-----------|-----------|-----------|-----------|

| SWLCTRG     | SWCTRG     | CNVCHSEL5 | CNVCHSEL4 | CNVCHSEL3 | CNVCHSEL2 | CNVCHSEL1 | CNVCHSEL0 |

| bit 7 bit 0 |            |           |           |           |           |           |           |

| Legend:           | U = Unimplemented bit, read as '0' |                                       |                    |  |  |  |

|-------------------|------------------------------------|---------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                   | HSC = Hardware Settable/Clearable bit |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |

bit 15-13 REFSEL<2:0>: ADC Reference Voltage Selection bits

| Value | VREFH | VREFL |

|-------|-------|-------|

| 000   | AVDD  | AVss  |

001-111 = Unimplemented: Do not use

| bit 12  | SUSPEND: All ADC Cores Triggers Disable bit                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = All new trigger events for all ADC cores are disabled                                                                                                                                                                                                                                                                                                                                                                                            |

|         | 0 = All ADC cores can be triggered                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 11  | SUSPCIE: Suspend All ADC Cores Common Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = Common interrupt will be generated when ADC core triggers are suspended (SUSPEND bit = 1) and all previous conversions are finished (SUSPRDY bit becomes set)</li> <li>0 = Common interrupt is not generated for suspend ADC cores event</li> </ul>                                                                                                                                                                                     |

| bit 10  | SUSPRDY: All ADC Cores Suspended Flag bit                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = All ADC cores are suspended (SUSPEND bit = 1) and have no conversions in progress</li> <li>0 = ADC cores have previous conversions in progress</li> </ul>                                                                                                                                                                                                                                                                               |

| bit 9   | SHRSAMP: Shared ADC Core Sampling Direct Control bit                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | This bit should be used with the individual channel conversion trigger controlled by the CNVRTCH bit.<br>It connects an analog input, specified by the CNVCHSEL<5:0> bits, to the shared ADC core and allows<br>extending the sampling time. This bit is not controlled by hardware and must be cleared before the<br>conversion starts (setting CNVRTCH to '1').<br>1 = Shared ADC core samples an analog input specified by the CNVCHSEL<5:0> bits |

|         | 0 = Sampling is controlled by the shared ADC core hardware                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 8   | CNVRTCH: Software Individual Channel Conversion Trigger bit                                                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>1 = Single trigger is generated for an analog input specified by the CNVCHSEL&lt;5:0&gt; bits; when the bit is set, it is automatically cleared by hardware on the next instruction cycle</li> <li>0 = Next individual channel conversion trigger can be generated</li> </ul>                                                                                                                                                               |

| bit 7   | SWLCTRG: Software Level-Sensitive Common Trigger bit                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = Triggers are continuously generated for all channels with the software, level-sensitive common trigger selected as a source in the ADTRIGxL and ADTRIGxH registers</li> <li>0 = No software, level-sensitive common triggers are generated</li> </ul>                                                                                                                                                                                   |

| bit 6   | SWCTRG: Software Common Trigger bit                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = Single trigger is generated for all channels with the software, common trigger selected as a source<br/>in the ADTRIGxL and ADTRIGxH registers; when the bit is set, it is automatically cleared by<br/>hardware on the next instruction cycle</li> <li>2 = Deadly to generate the next offware common trigger</li> </ul>                                                                                                               |

|         | 0 = Ready to generate the next software common trigger                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 5-0 | <b>CNVCHSEL &lt;5:0&gt;:</b> Channel Number Selection for Software Individual Channel Conversion Trigger bits<br>These bits define a channel to be converted when the CNVRTCH bit is set.                                                                                                                                                                                                                                                            |

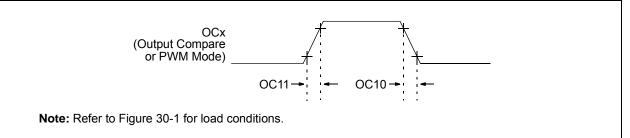

## FIGURE 30-7: OUTPUT COMPARE x MODULE (OCx) TIMING CHARACTERISTICS

### TABLE 30-28: OUTPUT COMPARE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40 \ ^\circ C \leq TA \leq +85 \ ^\circ C \ for \ Industrial \\ -40 \ ^\circ C \leq TA \leq +125 \ ^\circ C \ for \ Extended \end{array}$ |      |      |       |                    |  |

|--------------------|--------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max. | Units | Conditions         |  |

| OC10               | TccF   | OCx Output Fall Time          | _                                                                                                                                                                                                                                                                                     | _    | _    | ns    | See Parameter DO32 |  |

| OC11               | TccR   | OCx Output Rise Time          |                                                                                                                                                                                                                                                                                       | _    | _    | ns    | See Parameter DO31 |  |

Note 1: These parameters are characterized but not tested in manufacturing.

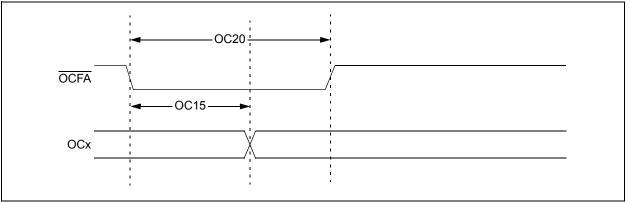

### FIGURE 30-8: OCx/PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 30-29: OCx/PWMx MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |          |       |            |

|--------------------|--------|-----------------------------------|------------------------------------------------------|------|----------|-------|------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>     | Min.                                                 | Тур. | Max.     | Units | Conditions |

| OC15               | TFD    | Fault Input to PWMx I/O<br>Change | _                                                    | _    | Tcy + 20 | ns    |            |

| OC20               | TFLT   | Fault Input Pulse Width           | Tcy + 20                                             | _    | —        | ns    |            |

Note 1: These parameters are characterized but not tested in manufacturing.

# TABLE 30-36:SPI1, SPI2 AND SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)TIMING REQUIREMENTS<sup>(5)</sup>

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                |  |

|--------------------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                    | Тур. <sup>(2)</sup> | Max. | Units | Conditions                     |  |

| SP70               | FscP                  | Maximum SCKx Input Frequency                 |                                                                                                                                                                                                                                                                                         |                     | 11   | MHz   | (Note 3)                       |  |

| SP72               | TscF                  | SCKx Input Fall Time                         |                                                                                                                                                                                                                                                                                         |                     |      | ns    | See Parameter DO32<br>(Note 4) |  |

| SP73               | TscR                  | SCKx Input Rise Time                         | —                                                                                                                                                                                                                                                                                       | _                   | _    | ns    | See Parameter DO31<br>(Note 4  |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                   | —                                                                                                                                                                                                                                                                                       | _                   | _    | ns    | See Parameter DO32<br>(Note 4) |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                       | _                   | _    | ns    | See Parameter DO31 (Note 4)    |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    | —                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                                |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge | 30                                                                                                                                                                                                                                                                                      | _                   | _    | ns    |                                |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge   | 30                                                                                                                                                                                                                                                                                      | _                   | _    | ns    |                                |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge    | 30                                                                                                                                                                                                                                                                                      | —                   |      | ns    |                                |  |

| SP50               | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↑ or SCKx ↓<br>Input           | 120                                                                                                                                                                                                                                                                                     | —                   | _    | ns    |                                |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance       | 10                                                                                                                                                                                                                                                                                      | —                   | 50   | ns    | (Note 4)                       |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                        | 1.5 Tcy + 40                                                                                                                                                                                                                                                                            | _                   | _    | ns    | (Note 4)                       |  |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge     | —                                                                                                                                                                                                                                                                                       | —                   | 50   | ns    |                                |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

5: Pertaining to SPI3: dsPIC33EPXXXGS702, dsPIC33EPXXXGSX04 and dsPIC33EPXXXGSX05 devices with a remappable SCK3 pin.

# TABLE 30-37:SPI1, SPI2 AND SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS<sup>(5)</sup>

| AC CHARACTERISTICS |                       |                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                             |  |

|--------------------|-----------------------|----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP70               | FscP                  | Maximum SCKx Input Frequency                 | —                                                     |                     | 15   | MHz   | (Note 3)                    |  |

| SP72               | TscF                  | SCKx Input Fall Time                         | —                                                     | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP73               | TscR                  | SCKx Input Rise Time                         | —                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4  |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                   | —                                                     | _                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                   | —                                                     | _                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    | —                                                     | 6                   | 20   | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge | 30                                                    | _                   | _    | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge   | 30                                                    | —                   | _    | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge    | 30                                                    | —                   | —    | ns    |                             |  |

| SP50               | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↑ or SCKx ↓<br>Input           | 120                                                   | —                   | _    | ns    |                             |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance       | 10                                                    | —                   | 50   | ns    | (Note 4)                    |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                        | 1.5 Tcy + 40                                          | —                   |      | ns    | (Note 4)                    |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

5: Pertaining to SPI3: dsPIC33EPXXXGS702, dsPIC33EPXXXGSX04 and dsPIC33EPXXXGSX05 devices with a remappable SCK3 pin.

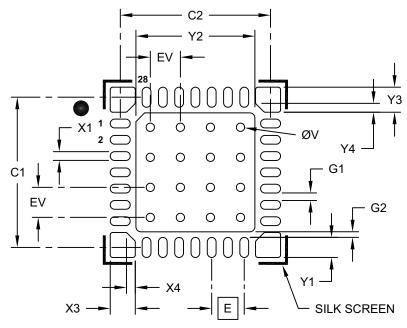

# 28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (2N) - 6x6x0.55 mm Body [UQFN] With 4.65x4.65 mm Exposed Pad and Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                                 | MILLIMETERS |      |          |      |

|---------------------------------|-------------|------|----------|------|

| Dimension                       | MIN         | NOM  | MAX      |      |

| Contact Pitch                   | E           |      | 0.65 BSC |      |

| Optional Center Pad Width       | X2          |      |          | 4.75 |

| Optional Center Pad Length      | Y2          |      |          | 4.75 |

| Contact Pad Spacing             | C1          |      | 6.00     |      |

| Contact Pad Spacing             | C2          |      | 6.00     |      |

| Contact Pad Width (X28)         | X1          |      |          | 0.35 |

| Contact Pad Length (X28)        | Y1          |      |          | 0.80 |

| Corner Anchor (X4)              | X3          |      |          | 1.00 |

| Corner Anchor (X4)              | Y3          |      |          | 1.00 |

| Corner Anchor Chamfer (X4)      | X4          |      |          | 0.35 |

| Corner Anchor Chamfer (X4)      | Y4          |      |          | 0.35 |

| Contact Pad to Pad (X28)        | G1          | 0.20 |          |      |

| Contact Pad to Center Pad (X28) | G2          | 0.20 |          |      |

| Thermal Via Diameter            | V           |      | 0.33     |      |

| Thermal Via Pitch               | EV          |      | 1.20     |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2385B

**Note:** Corner anchor pads are not connected internally and are designed as mechanical features when the package is soldered to the PCB.

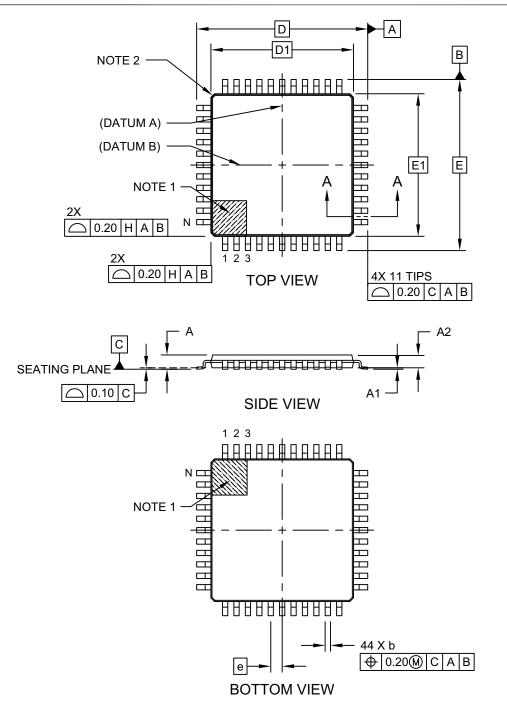

# 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-076C Sheet 1 of 2