Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 67                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-TQFP                                                                         |

| Supplier Device Package    | 80-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs808-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Communication Interfaces**

- Two UART modules (15 Mbps):

- Supports LIN/J2602 protocols and IrDA®

- Three Variable Width SPI modules with Operating modes:

- 3-wire SPI

- 8x16 or 8x8 FIFO mode

- I<sup>2</sup>S mode

- Two I<sup>2</sup>C modules (up to 1 Mbaud) with SMBus Support

- Up to Two CAN modules

- Four-Channel DMA

### Input/Output

- Constant-Current Source (10 µA nominal)

- Sink/Source up to 12 mA/15 mA, respectively; Pin-Specific for Standard VOH/VOL

- 5V Tolerant Pins

- · Selectable, Open-Drain Pull-ups and Pull-Downs

- External Interrupts on all I/O Pins

- Peripheral Pin Select (PPS) to allow Function Remap with Six Virtual I/Os

### **Qualification and Class B Support**

- AEC-Q100 REVG (Grade 1, -40°C to +125°C)

- Class B Safety Library, IEC 60730

- The 6x6x0.55 mm UQFN Package is Designed and Optimized to ease IPC9592B 2nd Level Temperature Cycle Qualification

### **Debugger Development Support**

- In-Circuit and In-Application Programming

- Five Program and Three Complex Data Breakpoints

- IEEE 1149.2 Compatible (JTAG) Boundary Scan

- Trace and Run-Time Watch

### **Digital Peripherals**

- Four Configurable Logic Cells

- Peripheral Trigger Generator

|                   |      | rtes                 |             | (GPIO)                |                       | Re            | ma             | ppal | ole F | Perip              | hera                               | als |                 |                  |     |     | 12-<br>A[     | -            |     |     | r                 |            | Source               |                         |

|-------------------|------|----------------------|-------------|-----------------------|-----------------------|---------------|----------------|------|-------|--------------------|------------------------------------|-----|-----------------|------------------|-----|-----|---------------|--------------|-----|-----|-------------------|------------|----------------------|-------------------------|

| Device            | Pins | Program Memory Bytes | RAM (Bytes) | General Purpose I/O ( | Timers <sup>(1)</sup> | Input Capture | Output Compare | UART | IdS   | PWM <sup>(2)</sup> | External Interrupts <sup>(3)</sup> | CAN | Reference Clock | 1 <sup>2</sup> C | CLC | ÐLd | Analog Inputs | S&H Circuits | V9d | AMA | Analog Comparator | DAC Output | Constant-Current Sou | Packages                |

| dsPIC33EP128GS702 | 28   | 128K                 | 8K          | 20                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 11            | 5            | 2   | 0   | 4                 | 1          | 1                    | SOIC,<br>QFN-S,<br>UQFN |

| dsPIC33EP64GS804  | 44   | 64K                  | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 4   | 4                 | 1          | 1                    |                         |

| dsPIC33EP128GS704 | 44   | 128K                 | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 0   | 4                 | 1          | 1                    | 1 QFN,<br>1 TQFP        |

| dsPIC33EP128GS804 | 44   | 128K                 | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 4   | 4                 | 1          | 1                    | i Qi i                  |

| dsPIC33EP64GS805  | 48   | 64K                  | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 4   | 4                 | 1          | 1                    |                         |

| dsPIC33EP128GS705 | 48   | 128K                 | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 0   | 4                 | 1          | 1                    | TQFP                    |

| dsPIC33EP128GS805 | 48   | 128K                 | 8K          | 33                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 17            | 5            | 2   | 4   | 4                 | 1          | 1                    |                         |

| dsPIC33EP64GS806  | 64   | 64K                  | 8K          | 51                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 4   | 4                 | 2          | 1                    |                         |

| dsPIC33EP128GS706 | 64   | 128K                 | 8K          | 51                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 0   | 4                 | 2          | 1                    |                         |

| dsPIC33EP128GS806 | 64   | 128K                 | 8K          | 51                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 4   | 4                 | 2          | 1                    |                         |

| dsPIC33EP64GS708  | 80   | 64K                  | 8K          | 67                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 0   | 4                 | 2          | 1                    |                         |

| dsPIC33EP64GS808  | 80   | 64K                  | 8K          | 67                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 4   | 4                 | 2          | 1                    | TQFP                    |

| dsPIC33EP128GS708 | 80   | 128K                 | 8K          | 67                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 0   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 0   | 4                 | 2          | 1                    |                         |

| dsPIC33EP128GS808 | 80   | 128K                 | 8K          | 67                    | 5                     | 4             | 4              | 2    | 3     | 8x2                | 4                                  | 2   | 1               | 2                | 4   | 1   | 22            | 5            | 2   | 4   | 4                 | 2          | 1                    |                         |

Note 1: The external clock for Timer1, Timer2 and Timer3 is remappable.

2: PWM4 through PWM8 are remappable on 28/44/48-pin devices; on 64-pin devices, only PWM7/PWM8 are remappable.

**3:** External interrupts, INT0 and INT4, are not remappable.

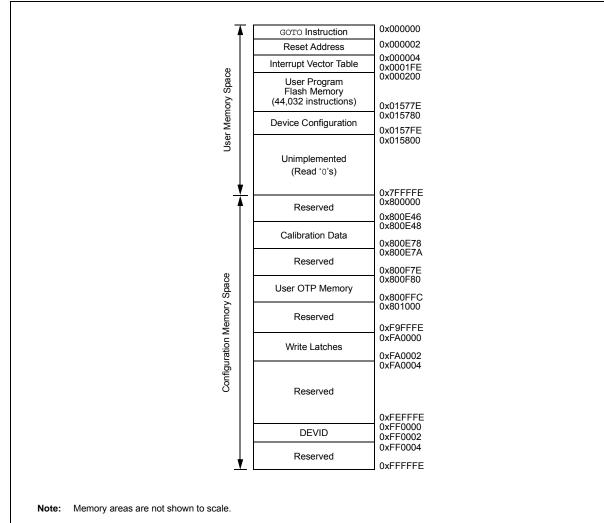

#### FIGURE 4-2: PROGRAM MEMORY MAP FOR dsPIC33EP128GS70X/80X DEVICES

#### 4.5.1 PAGED MEMORY SCHEME

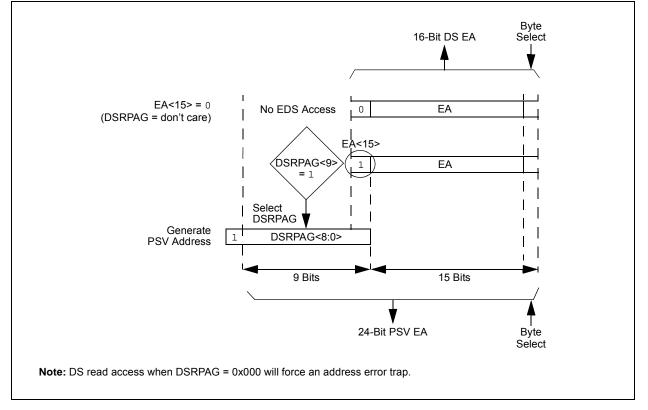

The dsPIC33EPXXXGS70X/80X family architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre- and post-modified Effective Addresses (EAs). The upper half of the base Data Space address is used in conjunction with the Data Space Read Page (DSRPAG) register to form the Program Space Visibility (PSV) address.

The Data Space Read Page (DSRPAG) register is located in the SFR space. Construction of the PSV address is shown in Figure 4-7. When DSRPAG<9> = 1 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit PSV read address.

The paged memory scheme provides access to multiple 32-Kbyte windows in the PSV memory. The Data Space Read Page (DSRPAG) register, in combination with the upper half of the Data Space address, can provide up to 8 Mbytes of PSV address space. The paged data memory space is shown in Figure 4-8.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG register.

| TABLE 7-1: | INTERRUPT VECTOR DETAILS ( | (CONTINUED) | ) |

|------------|----------------------------|-------------|---|

|            |                            |             |   |

| Interrupt Source               | Vector | IRQ   | IVT Address       | In                  | terrupt Bit Lo      | ocation                     |

|--------------------------------|--------|-------|-------------------|---------------------|---------------------|-----------------------------|

| interrupt Source               | #      | #     | IVI Address       | Flag                | Enable              | Priority                    |

| T4 – Timer4                    | 35     | 27    | 0x00004A          | IFS1<11><br>T4IF    | IEC1<11><br>T4IE    | IPC6<14:12><br>T4IP<2:0>    |

| T5 – Timer5                    | 36     | 28    | 0x00004C          | IFS1<12><br>T5IF    | IEC1<12><br>T5IE    | IPC7<2:0><br>T5IP<2:0>      |

| INT2 – External Interrupt 2    | 37     | 29    | 0x00004E          | IFS1<13><br>INT2IF  | IEC1<13><br>INT2IE  | IPC7<6:4><br>INT2IP<2:0>    |

| U2RX – UART2 Receiver          | 38     | 30    | 0x000050          | IFS1<14><br>U2RXIF  | IEC1<14><br>U2RXIE  | IPC7<10:8><br>U2RXIP<2:0>   |

| U2TX – UART2 Transmitter       | 39     | 31    | 0x000052          | IFS1<15><br>U2TXIF  | IEC1<15><br>U2TXIE  | IPC7<14:12><br>U2TXIP<2:0>  |

| SPI2TX – SPI2 Transfer Done    | 40     | 32    | 0x000054          | IFS2<0><br>SPI2TXIF | IEC2<0><br>SPI2TXIE | IPC8<2:0><br>SPI2TXIP<2:0>  |

| SPI2RX – SPI2 Receive Done     | 41     | 33    | 0x000056          | IFS2<1><br>SPI2RXIF | IEC2<1><br>SPI2RXIE | IPC8<6:4><br>SPI2RXIP<2:0>  |

| C1RX – CAN1 RX Data Ready      | 42     | 34    | 0x000058          | IFS2<2><br>C1RXIF   | IEC2<2><br>C1RXIE   | IPC8<10:8><br>C1RXIP<2:0>   |

| C1 – CAN1 Combined Error       | 43     | 35    | 0x000059          | IFS2<3><br>C1IF     | IEC2<3><br>C1IE     | IPC8<14:12><br>C1IP<2:0>    |

| DMA3 – DMA Channel 3           | 44     | 36    | 0x00005A          | IFS2<4><br>DMA3IF   | IEC2<4><br>DMA3IE   | IPC9<2:0><br>DMA3IP<2:0>    |

| IC3 – Input Capture 3          | 45     | 37    | 0x00005E          | IFS2<5><br>IC3IF    | IEC2<5><br>IC3IE    | IPC9<6:4><br>IC3IP<2:0>     |

| IC4 – Input Capture 4          | 46     | 38    | 0x000060          | IFS2<6><br>IC4IF    | IEC2<6><br>IC4IE    | IPC9<10:8><br>IC4IP<2:0>    |

| Reserved                       | 47-56  | 39-48 | 0x000062-0x000074 | _                   | _                   | _                           |

| SI2C2 – I2C2 Slave Event       | 57     | 49    | 0x000076          | IFS3<1><br>SI2C2IF  | IEC3<1><br>SI2C2IE  | IPC12<6:4><br>SI2C2IP<2:0>  |

| MI2C2 – I2C2 Master Event      | 58     | 50    | 0x000078          | IFS3<2><br>MI2C2IF  | IEC3<2><br>MI2C2IE  | IPC12<10:8><br>MI2C2IP<2:0> |

| Reserved                       | 59-61  | 51-53 | 0x00007A-0x00007E | _                   | —                   | _                           |

| INT4 – External Interrupt 4    | 62     | 54    | 0x000080          | IFS3<6><br>INT4IF   | IEC3<6><br>INT4IE   | IPC13<10:8><br>INT4IP<2:0>  |

| C2RX – CAN2 RX Data Ready      | 63     | 55    | 0x000082          | IFS3<7><br>C2RXIF   | IEC3<7><br>C2RXIE   | IPC13<14:12><br>C2RXIP<2:0> |

| C2 – CAN 2 Combined Error      | 64     | 56    | 0x000083          | IFS3<8><br>C2IF     | IEC3<8><br>C2IE     | IPC14<2:0><br>C2IP<2:0>     |

| PSEM – PWM Special Event Match | 65     | 57    | 0x000086          | IFS3<9><br>PSEMIF   | IEC3<9><br>PSEMIE   | IPC14<6:4><br>PSEMIP<2:0>   |

| Reserved                       | 66-72  | 58-64 | 0x000088-0x000094 | _                   | _                   | _                           |

| U1E – UART1 Error Interrupt    | 73     | 65    | 0x000096          | IFS4<1><br>U1EIF    | IEC4<1><br>U1EIE    | IPC16<6:4><br>U1EIP<2:0>    |

| U2E – UART2 Error Interrupt    | 74     | 66    | 0x000098          | IFS4<2><br>U2EIF    | IEC4<2><br>U2EIE    | IPC16<10:8><br>U2EIP<2:0>   |

| Reserved                       | 75-77  | 67-69 | 0x00009A-0x0000A2 | _                   | _                   | _                           |

| C1TX – CAN1 TX Data Request    | 78     | 70    | 0x0000A0          | IFS4<6><br>C1TXIF   | IEC4<6><br>C1TXIE   | IPC17<10:8><br>C1TXIP<2:0>  |

| C2TX – CAN2 TX Data Request    | 79     | 71    | 0x0000A           | IFS4<7><br>C2TXIF   | IEC4<7><br>C2TXIE   | IPC17<14:12><br>C2TXIP<2:0> |

| Reserved                       | 80     | 72    | 0x0000A4          | _                   | _                   | _                           |

| REGISTER 7-2: CORC | ON: CORE CONTROL REGISTER <sup>(1)</sup> |

|--------------------|------------------------------------------|

|--------------------|------------------------------------------|

| R/W-0  | U-0   | R/W-0 | R/W-0 | R/W-0 | R-0 | R-0   | R-0   |

|--------|-------|-------|-------|-------|-----|-------|-------|

| VAR    | —     | US1   | US0   | EDT   | DL2 | DL1   | DL0   |

| bit 15 | ·     |       |       |       |     |       | bit 8 |

|        |       |       |       |       |     |       |       |

| R/W-0  | R/W-0 | R/W-1 | R/W-0 | R/C-0 | R-0 | R/W-0 | R/W-0 |

| R/W-U | R/W-U | R/ VV- I | R/W-U  | R/C-0               | R-0 | R/W-U | R/VV-U |

|-------|-------|----------|--------|---------------------|-----|-------|--------|

| SATA  | SATB  | SATDW    | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF     |

| bit 7 |       |          |        |                     |     |       | bit 0  |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15 VAR: Variable Exception Processing Latency Control bit

1 = Variable exception processing is enabled

0 = Fixed exception processing is enabled

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup>

1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

Note 1: For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## 8.1 DMA Controller Registers

Each DMA Controller Channel x (where x = 0 through 3) contains the following registers:

- 16-Bit DMA Channel x Control Register (DMAxCON)

- 16-Bit DMA Channel x IRQ Select Register (DMAxREQ)

- 32-Bit DMA Channel x Start Address Register A (DMAxSTAL/H)

- 32-Bit DMA Channel x Start Address Register B (DMAxSTBL/H)

- 16-Bit DMA Channel x Peripheral Address Register (DMAxPAD)

- 14-Bit DMA Channel x Transfer Count Register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADRL/H) are common to all DMA Controller channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The interrupt flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding interrupt enable control bits (DMAxIE) are located in an IECx register in the interrupt controller and the corresponding interrupt priority control bits (DMAxIP) are located in an IPCx register in the interrupt controller.

#### REGISTER 8-1: DMAxCON: DMA CHANNEL x CONTROL REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|--------|-------|-------|-------|-------|-----|-----|-------|

| CHEN   | SIZE  | DIR   | HALF  | NULLW | —   | —   | —     |

| bit 15 |       |       |       |       |     |     | bit 8 |

| U-0   | U-0 | R/W-0  | R/W-0  | U-0 | U-0 | R/W-0 | R/W-0 |

|-------|-----|--------|--------|-----|-----|-------|-------|

| _     | —   | AMODE1 | AMODE0 | —   | —   | MODE1 | MODE0 |

| bit 7 |     |        |        |     |     |       | bit 0 |

#### Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15   | CHEN: DMA Channel Enable bit                                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Channel is enabled                                                                                                                                |

|          | 0 = Channel is disabled                                                                                                                               |

| bit 14   | SIZE: DMA Data Transfer Size bit                                                                                                                      |

|          | 1 = Byte<br>0 = Word                                                                                                                                  |

| bit 13   | DIR: Transfer Direction bit (source/destination bus select)                                                                                           |

|          | <ul> <li>1 = Reads from RAM address, writes to peripheral address</li> <li>0 = Reads from peripheral address, writes to RAM address</li> </ul>        |

| bit 12   | HALF: Block Transfer Interrupt Select bit                                                                                                             |

|          | <ul> <li>1 = Initiates interrupt when half of the data has been moved</li> <li>0 = Initiates interrupt when all of the data has been moved</li> </ul> |

| bit 11   | NULLW: Null Data Peripheral Write Mode Select bit                                                                                                     |

|          | <ul> <li>1 = Null data write to peripheral in addition to RAM write (DIR bit must also be clear)</li> <li>0 = Normal operation</li> </ul>             |

| bit 10-6 | Unimplemented: Read as '0'                                                                                                                            |

| bit 5-4  | AMODE<1:0>: DMA Channel Addressing Mode Select bits                                                                                                   |

|          | 11 = Reserved                                                                                                                                         |

|          | 10 = Peripheral Indirect mode                                                                                                                         |

|          | <ul><li>01 = Register Indirect without Post-Increment mode</li><li>00 = Register Indirect with Post-Increment mode</li></ul>                          |

| bit 3-2  | Unimplemented: Read as '0'                                                                                                                            |

| bit 1-0  | MODE<1:0>: DMA Channel Operating Mode Select bits                                                                                                     |

|          | 11 = One-Shot, Ping-Pong modes are enabled (one block transfer from/to each DMA buffer)                                                               |

|          | 10 = Continuous, Ping-Pong modes are enabled<br>01 = One-Shot, Ping-Pong modes are disabled                                                           |

|          | 00 = Continuous, Ping-Pong modes are disabled                                                                                                         |

|          |                                                                                                                                                       |

### 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of the these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

#### 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral (for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

bit 4-0

- **SYNCSEL<4:0>:** Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup> 11111 = No sync or trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = Reserved

- 11011 = CMP4 module synchronizes or triggers  $ICx^{(5)}_{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- 11001 = CMP2 module synchronizes or triggers ICx<sup>(5)</sup>

- 11000 = CMP1 module synchronizes or triggers ICx<sup>(5)</sup>

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module interrupt synchronizes or triggers ICx

- 10010 = IC3 module interrupt synchronizes or triggers ICx

- 10001 = IC2 module interrupt synchronizes or triggers ICx

- 10000 = IC1 module interrupt synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = Reserved

- 01001 = Reserved

- 01000 = IC4 module synchronizes or triggers ICx

- 00111 = IC3 module synchronizes or triggers ICx

- 00110 = IC2 module synchronizes or triggers ICx

- 00101 = IC1 module synchronizes or triggers ICx

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No sync or trigger source for ICx

- **Note 1:** The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own sync or trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

## REGISTER 16-22: FCLCONX: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER

|         | (X = 1 | to 8)  |        |        |        |                      |       |

|---------|--------|--------|--------|--------|--------|----------------------|-------|

| R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0                | R/W-0 |

| IFLTMOD | CLSRC4 | CLSRC3 | CLSRC2 | CLSRC1 | CLSRC0 | CLPOL <sup>(1)</sup> | CLMOD |

| bit 15  |        |        |        |        |        |                      | bit 8 |

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0                 | R/W-0   | R/W-0   |

|---------|---------|---------|---------|---------|-----------------------|---------|---------|

| FLTSRC4 | FLTSRC3 | FLTSRC2 | FLTSRC1 | FLTSRC0 | FLTPOL <sup>(1)</sup> | FLTMOD1 | FLTMOD0 |

| bit 7   |         |         |         |         |                       |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 IFLTMOD: Independent Fault Mode Enable bit

- I = Independent Fault mode: Current-limit input maps FLTDAT1 to the PWMxH output and the Fault input maps FLTDAT0 to the PWMxL output; the CLDAT<1:0> bits are not used for override functions

0 = Normal Fault mode: Current-Limit mode maps CLDAT<1:0> bits to the PWMxH and PWMxL

- outputs; the PWM Fault mode maps FLTDAT<1:0> to the PWMxH and PWMxL outputs

#### bit 14-10 CLSRC<4:0>: Current-Limit Control Signal Source Select for PWMx Generator bits

- 10001 = Reserved

- 10000 = Analog Comparator 4

- 01111 = Analog Comparator 3

- 01110 = Analog Comparator 2 01101 = Analog Comparator 1

- 01101 = Analog Com

- 01100 Fault 12 01011 = Fault 11

- 01010 = Fault 10

- 01001 = Fault 9

- 01000 = Fault 8

- 00111 = Fault 7

- 00110 = Fault 6

- 00110 = Fault 0

- 00100 = Fault 4

- 00011 = Fault 3

- 00010 = Fault 2

- 00001 = Fault 1

- 00000 = Reserved

bit 9

- CLPOL: Current-Limit Polarity for PWMx Generator bit<sup>(1)</sup>

- 1 = The selected current-limit source is active-low

- 0 = The selected current-limit source is active-high

- bit 8 **CLMOD:** Current-Limit Mode Enable for PWMx Generator bit

- 1 = Current-Limit mode is enabled

- 0 = Current-Limit mode is disabled

- Note 1: These bits should be changed only when PTEN = 0 (PTCON<15>).

#### REGISTER 18-7: SPIxIMSKH: SPIx INTERRUPT MASK REGISTER HIGH

| R/W-0  | U-0 | R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                 | R/W-0                 |

|--------|-----|-----------------------|-------------------------|-------------------------|-------------------------|-----------------------|-----------------------|

| RXWIEN | —   | RXMSK5 <sup>(1)</sup> | RXMSK4 <sup>(1,4)</sup> | RXMSK3 <sup>(1,3)</sup> | RXMSK2 <sup>(1,2)</sup> | RXMSK1 <sup>(1)</sup> | RXMSK0 <sup>(1)</sup> |

| bit 15 |     |                       |                         |                         |                         |                       | bit 8                 |

| R/W-0  | U-0 | R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                 | R/W-0                 |

|--------|-----|-----------------------|-------------------------|-------------------------|-------------------------|-----------------------|-----------------------|

| TXWIEN | —   | TXMSK5 <sup>(1)</sup> | TXMSK4 <sup>(1,4)</sup> | TXMSK3 <sup>(1,3)</sup> | TXMSK2 <sup>(1,2)</sup> | TXMSK1 <sup>(1)</sup> | TXMSK0 <sup>(1)</sup> |

| bit 7  |     |                       |                         |                         |                         |                       | bit 0                 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15   | RXWIEN: Receive Watermark Interrupt Enable bit                                                                                                                                          |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Triggers receive buffer element watermark interrupt when RXMSK<5:0> $\leq$ RXELM<5:0> 0 = Disables receive buffer element watermark interrupt                                       |

| bit 14   | Unimplemented: Read as '0'                                                                                                                                                              |

| bit 13-8 | RXMSK<5:0>: RX Buffer Mask bits <sup>(1,2,3,4)</sup>                                                                                                                                    |

|          | RX mask bits; used in conjunction with the RXWIEN bit.                                                                                                                                  |

| bit 7    | TXWIEN: Transmit Watermark Interrupt Enable bit                                                                                                                                         |

|          | <ul> <li>1 = Triggers transmit buffer element watermark interrupt when TXMSK&lt;5:0&gt; = TXELM&lt;5:0&gt;</li> <li>0 = Disables transmit buffer element watermark interrupt</li> </ul> |

| bit 6    | Unimplemented: Read as '0'                                                                                                                                                              |

| bit 5-0  | TXMSK<5:0>: TX Buffer Mask bits <sup>(1,2,3,4)</sup>                                                                                                                                    |

|          | TX mask bits; used in conjunction with the TXWIEN bit.                                                                                                                                  |

|          |                                                                                                                                                                                         |

- **Note 1:** Mask values higher than FIFODEPTH are not valid. The module will not trigger a match for any value in this case.

- 2: RXMSK2 and TXMSK2 bits are only present when FIFODEPTH = 8 or higher.

- 3: RXMSK3 and TXMSK3 bits are only present when FIFODEPTH = 16 or higher.

- 4: RXMSK4 and TXMSK4 bits are only present when FIFODEPTH = 32.

| REGISTER 22-8: | ADCON4H: ADC CONTROL REGISTER 4 HIGH |

|----------------|--------------------------------------|

|                |                                      |

| U-0          | U-0                                                    | U-0                                                                                                                                                              | U-0           | U-0              | U-0              | U-0             | U-0    |  |  |

|--------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|------------------|-----------------|--------|--|--|

|              | —                                                      | —                                                                                                                                                                |               | —                |                  | —               |        |  |  |

| bit 15       |                                                        |                                                                                                                                                                  |               |                  |                  |                 | bit 8  |  |  |

|              |                                                        |                                                                                                                                                                  |               |                  |                  |                 |        |  |  |

| R/W-0        | R/W-0                                                  | R/W-0                                                                                                                                                            | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |

| C3CHS1       | C3CHS0                                                 | C2CHS1                                                                                                                                                           | C2CHS0        | C1CHS1           | C1CHS0           | C0CHS1          | C0CHS0 |  |  |

| bit 7        |                                                        |                                                                                                                                                                  |               |                  |                  |                 | bit (  |  |  |

| Legend:      |                                                        |                                                                                                                                                                  |               |                  |                  |                 |        |  |  |

| R = Readab   | le hit                                                 | W = Writable                                                                                                                                                     | hit           | LI = Unimplen    | nented bit, read | las 'N'         |        |  |  |

| -n = Value a |                                                        | '1' = Bit is set                                                                                                                                                 |               | '0' = Bit is cle |                  | x = Bit is unkr |        |  |  |

|              |                                                        | 1 Dit lo bet                                                                                                                                                     |               | Bit lo bio       |                  |                 | lown   |  |  |

| bit 5-4      | 00 = AN3<br>C2CHS<1:0><br>11 = Reserve<br>10 = VREF ba |                                                                                                                                                                  | C Core 2 Inpu | it Channel Sele  | ction bits       |                 |        |  |  |

| bit 3-2      | 11 = AN1ALT<br>10 = PGA2                               | C1CHS<1:0>: Dedicated ADC Core 1 Input Channel Selection bits<br>11 = AN1ALT<br>10 = PGA2<br>01 = AN18 (differential negative input when DIFF1 (ADMOD0L<3>) = 1) |               |                  |                  |                 |        |  |  |

| bit 1-0      |                                                        |                                                                                                                                                                  |               |                  |                  |                 |        |  |  |

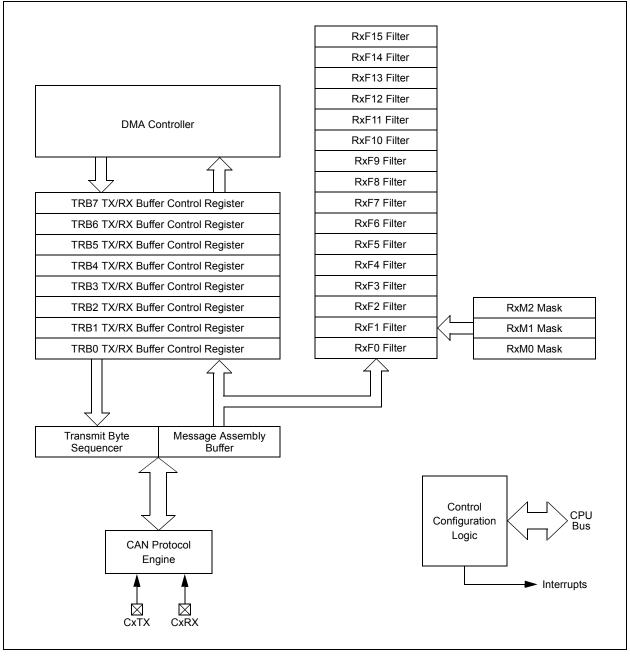

### FIGURE 23-1: CANX MODULE BLOCK DIAGRAM

### 23.2 Modes of Operation

The CANx module can operate in one of several operation modes selected by the user. These modes include:

- · Initialization mode

- · Disable mode

- Normal Operation mode

- · Listen Only mode

- Listen All Messages mode

- · Loopback mode

Modes are requested by setting the REQOP<2:0> bits (CxCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CxCTRL1<7:5>). The module does not change the mode and the OPMODEx bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

| R/W-0         | R/W-0                                                                     | R/W-0                                       | R/W-0         | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |  |  |

|---------------|---------------------------------------------------------------------------|---------------------------------------------|---------------|------------------------------------|--------|--------------------|--------|--|--|--|

| F15BP3        | F15BP2                                                                    | F15BP1                                      | F15BP0        | F14BP3                             | F14BP2 | F14BP1             | F14BP0 |  |  |  |

| bit 15        |                                                                           |                                             |               |                                    |        |                    | bit 8  |  |  |  |

|               |                                                                           |                                             |               |                                    |        |                    |        |  |  |  |

| R/W-0         | R/W-0                                                                     | R/W-0                                       | R/W-0         | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |  |  |

| F13BP3        | F13BP2                                                                    | F13BP1                                      | F13BP0        | F12BP3                             | F12BP2 | F12BP1             | F12BP0 |  |  |  |

| bit 7         |                                                                           |                                             |               |                                    |        |                    | bit 0  |  |  |  |

|               |                                                                           |                                             |               |                                    |        |                    |        |  |  |  |

| Legend:       |                                                                           |                                             |               |                                    |        |                    |        |  |  |  |

| R = Readable  | e bit                                                                     | W = Writable bit                            |               | U = Unimplemented bit, read as '0' |        |                    |        |  |  |  |

| -n = Value at | POR                                                                       | '1' = Bit is set                            |               | '0' = Bit is cleared               |        | x = Bit is unknown |        |  |  |  |

|               |                                                                           |                                             |               |                                    |        |                    |        |  |  |  |

| bit 15-12     | F15BP<3:0>                                                                | 5BP<3:0>: RX Buffer Mask for Filter 15 bits |               |                                    |        |                    |        |  |  |  |

|               | 1111 = Filter hits received in RX FIFO buffer                             |                                             |               |                                    |        |                    |        |  |  |  |

|               | 1110 = Filter hits received in RX Buffer 14                               |                                             |               |                                    |        |                    |        |  |  |  |

|               | •                                                                         |                                             |               |                                    |        |                    |        |  |  |  |

|               | •                                                                         |                                             |               |                                    |        |                    |        |  |  |  |

|               | 0001 = Filter                                                             | hits received in                            | n RX Buffer 1 |                                    |        |                    |        |  |  |  |

|               | 0000 <b>= Filte</b> r                                                     | hits received in                            | n RX Buffer 0 |                                    |        |                    |        |  |  |  |

| bit 11-8      | F14BP<3:0>: RX Buffer Mask for Filter 14 bits (same values as bits 15-12) |                                             |               |                                    |        |                    |        |  |  |  |

| bit 7-4       | F13BP<3:0>: RX Buffer Mask for Filter 13 bits (same values as bits 15-12) |                                             |               |                                    |        |                    |        |  |  |  |

| bit 7-4       | F13BP<3:0>: RX Buffer Mask for Filter 13 bits (same values as bits 15-12) |                                             |               |                                    |        |                    |        |  |  |  |

#### REGISTER 23-15: CxBUFPNT4: CANx FILTERS 12-15 BUFFER POINTER REGISTER 4

bit 3-0 F12BP<3:0>: RX Buffer Mask for Filter 12 bits (same values as bits 15-12)

## 26.3 Current Source Control Register

#### REGISTER 26-1: ISRCCON: CONSTANT-CURRENT SOURCE CONTROL REGISTER

| R/W-0                 | U-0                                                                                                              | U-0                             | U-0             | U-0              | R/W-0            | R/W-0                                     | R/W-0    |

|-----------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------|------------------|------------------|-------------------------------------------|----------|

| ISRCEN                | _                                                                                                                | —                               | _               | _                | OUTSEL2          | OUTSEL1                                   | OUTSEL0  |

| bit 15                |                                                                                                                  |                                 |                 |                  |                  |                                           | bit 8    |

|                       |                                                                                                                  |                                 |                 |                  |                  |                                           |          |

| U-0                   | U-0                                                                                                              | R/W-0                           | R/W-0           | R/W-0            | R/W-0            | R/W-0                                     | R/W-0    |

| —                     | —                                                                                                                | ISRCCAL5                        | ISRCCAL4        | ISRCCAL3         | ISRCCAL2         | ISRCCAL1                                  | ISRCCAL0 |

| bit 7                 |                                                                                                                  |                                 |                 |                  |                  |                                           | bit C    |

| Legend:               |                                                                                                                  |                                 |                 |                  |                  |                                           |          |

| R = Readable          | e bit                                                                                                            | W = Writable                    | bit             | U = Unimpler     | mented bit, read | d as '0'                                  |          |

| -n = Value at         | POR                                                                                                              | '1' = Bit is set                |                 | '0' = Bit is cle | ared             | x = Bit is unkr                           | nown     |

| bit 14-11<br>bit 10-8 | -                                                                                                                | ted: Read as '<br>>: Output Con |                 | Select bits      |                  |                                           |          |

|                       | 111 = Reserv<br>110 = Reserv<br>101 = Reserv<br>100 = Input p<br>011 = Input p<br>010 = Input p<br>001 = Input p | red<br>red                      | 4)<br>5)<br>6)  |                  |                  |                                           |          |

| bit 7-6               | Unimplemen                                                                                                       | ted: Read as '                  | 0'              |                  |                  |                                           |          |

| bit 5-0               | ISRCCAL<5:                                                                                                       | 0>: Constant-C                  | Current Source  | e Calibration bi | ts               |                                           |          |

|                       | module is ena                                                                                                    |                                 | the calibration |                  |                  | 8, into these b<br>7-3) in <b>Section</b> |          |

## 27.2 Device Calibration and Identification

The PGAx and current source modules on the dsPIC33EPXXXGS70X/80X family devices require Calibration Data registers to improve performance of the module over a wide operating range. These Calibration registers are read-only and are stored in configuration memory space. Prior to enabling the module, the calibration data must be read (TBLPAG and Table Read instruction) and loaded into its respective SFR registers. The device calibration addresses are shown in Table 27-3.

The dsPIC33EPXXXGS70X/80X devices have two Identification registers near the end of configuration memory space that store the Device ID (DEVID) and Device Revision (DEVREV). These registers are used to determine the mask, variant and manufacturing information about the device. These registers are read-only and are shown in Register 27-1 and Register 27-2.

| Calibration<br>Name | Address | Bits 23-16 | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3   | Bit 2    | Bit 1   | Bit 0 |

|---------------------|---------|------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|---------|---------|----------|---------|-------|

| PGA1CAL             | 800E48  | _          | _      | _      |        | _      | _      | _      | _     | _     | _     | _     |       | PGA     | 1 Calib | ration [ | Data    |       |

| PGA2CAL             | 800E4C  | _          | -      | —      | —      | _      | _      | _      | _     | -     | _     | -     |       | PGA     | 2 Calib | ration I | Data    |       |

| ISRCCAL             | 800E78  | _          | _      | _      |        | _      |        |        | _     | _     | _     | _     | Cu    | rrent S | ource ( | Calibra  | tion Da | ata   |

Note 1: The calibration data must be copied into its respective SFR registers prior to enabling the module.

#### **30.1 DC Characteristics**

#### TABLE 30-1: OPERATING MIPS vs. VOLTAGE

| Characteristic | VDD Range                                  | Temperature Range | Maximum MIPS                 |

|----------------|--------------------------------------------|-------------------|------------------------------|

| Characteristic | (in Volts)                                 | (in °C)           | dsPIC33EPXXXGS70X/80X Family |

| _              | 3.0V to 3.6V <sup>(1)</sup> -40°C to +85°C |                   | 70                           |

| —              | 3.0V to 3.6V <sup>(1)</sup>                | -40°C to +125°C   | 60                           |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, PGAs and comparators) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min.        | Тур.        | Max. | Unit |

|---------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| Industrial Temperature Devices                                                              |        |             |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40         | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40         | —           | +85  | °C   |

| Extended Temperature Devices                                                                |        |             |             |      |      |

| Operating Junction Temperature Range                                                        |        | -40         | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40         | —           | +125 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD     | PINT + PI/O |             |      | W    |

| I/O Pin Power Dissipation:<br>I/O = $\Sigma$ ({VDD - VOH} x IOH) + $\Sigma$ (VOL x IOL)     |        |             |             |      |      |

| Maximum Allowed Power Dissipation                                                           | PDMAX  | (           | TJ — TA)/θJ | IA   | W    |

#### TABLE 30-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                      | Symbol | Тур. | Max. | Unit | Notes |

|-----------------------------------------------------|--------|------|------|------|-------|

| Package Thermal Resistance, 80-Pin TQFP 12x12x1 mm  | θJA    | 53.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 64-Pin TQFP 10x10x1 mm  | θJA    | 49.0 | -    | °C/W | 1     |

| Package Thermal Resistance, 48-Pin TQFP 7x7x1 mm    | θJA    | 63.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin QFN 8x8 mm       | θJA    | 29.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin TQFP 10x10x1 mm  | θJA    | 50.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN-S 6x6x0.9 mm | θJA    | 30.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin UQFN 6x6x0.55 mm | θJA    | 26.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC 7.50 mm     | θJA    | 70.0 | _    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| TABLE 30-4: | DC TEMPERATURE AND VOLTAGE SPECIFICATIONS |

|-------------|-------------------------------------------|

|             |                                           |

| DC CHARACTERISTICS |                   |                                                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |                      |  |  |

|--------------------|-------------------|---------------------------------------------------------------------|-------------------------------------------------------|------|------|-------|----------------------|--|--|

| Param<br>No.       | Symbol            | Characteristic                                                      | Min.                                                  | Тур. | Max. | Units | Conditions           |  |  |

| Operati            | Operating Voltage |                                                                     |                                                       |      |      |       |                      |  |  |

| DC10               | Vdd               | Supply Voltage                                                      | 3.0                                                   | _    | 3.6  | V     |                      |  |  |

| DC12               | Vdr               | RAM Retention Voltage <sup>(2)</sup>                                | _                                                     |      | 1.95 | V     | +25°C, +85°C, +125°C |  |  |

|                    |                   |                                                                     |                                                       | _    | 2.0  | V     | -40°C                |  |  |

| DC16               | VPOR              | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal    | -                                                     | _    | Vss  | V     |                      |  |  |

| DC17               | SVDD              | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal | 1.0                                                   | —    | —    | V/ms  | 0V-3V in 3 ms        |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, PGAs and comparators) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: This is the limit to which VDD may be lowered and the RAM contents will always be retained.

#### TABLE 30-5: FILTER CAPACITOR (CEFC) SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated):Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |        |                                                   |      |      |      |       |                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------|------|------|------|-------|------------------------------------------------------|

| Param<br>No.                                                                                                                                                                             | Symbol | Characteristics                                   | Min. | Тур. | Max. | Units | Comments                                             |

|                                                                                                                                                                                          | Cefc   | External Filter Capacitor<br>Value <sup>(1)</sup> | 4.7  | _    | 10   | μF    | Capacitor must have a low series resistance (<1 Ohm) |

**Note 1:** Typical VCAP Voltage = 1.8 volts when VDD  $\ge$  VDDMIN.

## TABLE 30-45:SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS<sup>(5)</sup>

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                |  |

|--------------------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |  |

| SP70               | FscP                  | Maximum SCK3 Input Frequency                 | —                                                                                                                                                                                                                                                                                       | _                   | 25   | MHz   | (Note 3)                       |  |

| SP72               | TscF                  | SCK3 Input Fall Time                         | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32 (Note 4)    |  |

| SP73               | TscR                  | SCK3 Input Rise Time                         | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4)    |  |

| SP30               | TdoF                  | SDO3 Data Output Fall Time                   | —                                                                                                                                                                                                                                                                                       | _                   | _    | ns    | See Parameter DO32<br>(Note 4) |  |

| SP31               | TdoR                  | SDO3 Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                       | _                   | _    | ns    | See Parameter DO31 (Note 4)    |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO3 Data Output Valid after<br>SCK3 Edge    | —                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                                |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO3 Data Output Setup to<br>First SCK3 Edge | 20                                                                                                                                                                                                                                                                                      | _                   | _    | ns    |                                |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI3 Data Input to SCK3 Edge   | 20                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                                |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI3 Data Input<br>to SCK3 Edge | 15                                                                                                                                                                                                                                                                                      | —                   | —    | ns    |                                |  |

| SP50               | TssL2scH,<br>TssL2scL | SS3 ↓ to SCK3 ↑ or SCK3 ↓<br>Input           | 120                                                                                                                                                                                                                                                                                     | —                   | _    | ns    |                                |  |

| SP51               | TssH2doZ              | SS3 ↑ to SDO3 Output<br>High-Impedance       | 10                                                                                                                                                                                                                                                                                      | —                   | 50   | ns    | (Note 4)                       |  |

| SP52               | TscH2ssH,<br>TscL2ssH | SS3 ↑ after SCK3 Edge                        | 1.5 TCY + 40                                                                                                                                                                                                                                                                            | —                   |      | ns    | (Note 4)                       |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK3 is 66.7 ns. Therefore, the SCK3 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI3 pins.

5: For dsPIC33EPXXXGSX06 and dsPIC33EPXXXGSX08 devices with a fixed SCK3 pin.

## 32.0 PACKAGING INFORMATION

## 32.1 Package Marking Information

28-Lead SOIC (7.50 mm)

28-Lead UQFN (6x6x0.55 mm)

28-Lead QFN-S (6x6x0.9 mm)

44-Lead TQFP (10x10x1 mm)

Example

Example

### Example

Example

| Legei | nd: XXX<br>Y<br>YY<br>WW<br>NNN | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code |

|-------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | be carrie                       | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                            |

## APPENDIX A: REVISION HISTORY

## Revision A (May 2016)

This is the initial version of the document.

## **Revision B (January 2017)**

- Sections:

- Updates Note 1 in Section 5.0 "Flash Program Memory".

- Tables:

- Updates the device description table on page 2.

- Updates Table 1-1, Table 4-2, Table 4-11, Table 7-1, Table 8-1, Table 11-11, Table 11-13, Table 17-1, Table 30-3, Table 30-4, Table 30-6, Table 30-7, Table 30-8, Table 30-9, Table 30-10, Table 30-11, Table 30-52, Table 30-54 and Table 30-55.

- Adds Table 11-6, Table 11-7, Table 11-8, Table 11-9 and Table 11-10.

- Figures:

- Updates the Pin Function tables in the Pin Diagram figures on pages 5 through 8.

- Updates Figure 4-1, Figure 17-1, Figure 18-1 and Figure 18-2.

- Registers:

- Updates Register 3-3, Register 16-5, Register 17-11, Register 18-1 and Register 19-2.

- Adds Register 11-1, Register 11-2, Register 11-3, Register 11-4, Register 11-5, Register 11-6, Register 11-7 and Register 11-8.