Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 67                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                           |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-TQFP                                                                         |

| Supplier Device Package    | 80-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs808-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(1)</sup> | Pin<br>Type | Buffer<br>Type | PPS               | Description                                                                                                                                                                        |  |  |  |  |

|-------------------------|-------------|----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AN0-AN21                |             | Analog         | No                | Analog input channels.                                                                                                                                                             |  |  |  |  |

| AN0ALT-AN1ALT           | I           | Analog         | No                | Alternate analog input channels.                                                                                                                                                   |  |  |  |  |

| C1RXR                   | I           | ST             | Yes               | CAN1 receive.                                                                                                                                                                      |  |  |  |  |

| C2RXR                   | I           | ST             | Yes               | CAN2 receive.                                                                                                                                                                      |  |  |  |  |

| C1TX                    | 0           | ST             | Yes               | CAN1 transmit.                                                                                                                                                                     |  |  |  |  |

| C2TX                    | 0           | ST             | Yes               | CAN2 transmit.                                                                                                                                                                     |  |  |  |  |

| CLKI                    | I           | ST/            | No                | External clock source input. Always associated with OSC1 pin                                                                                                                       |  |  |  |  |

|                         |             | CMOS           |                   | function.                                                                                                                                                                          |  |  |  |  |

| CLKO                    | 0           | _              | No                | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |  |  |  |  |

| OSC1                    | I           | ST/<br>CMOS    | No                | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                    |  |  |  |  |

| OSC2                    | I/O         |                | No                | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                           |  |  |  |  |

| CLC1OUT                 | 0           | DIG            | Yes               | CLC1 output.                                                                                                                                                                       |  |  |  |  |

| CLC2OUT                 | 0           | DIG            | Yes               | CLC2 output.                                                                                                                                                                       |  |  |  |  |

| CLC3OUT                 | 0           | DIG            | No <sup>(4)</sup> | CLC3 output.                                                                                                                                                                       |  |  |  |  |

| CLC4OUT                 | 0           | DIG            | No <sup>(4)</sup> | CLC4 output.                                                                                                                                                                       |  |  |  |  |

| REFCLKO                 | 0           | —              | Yes               | Reference clock output.                                                                                                                                                            |  |  |  |  |

| IC1-IC4                 | I           | ST             | Yes               | Capture Inputs 1 through 4.                                                                                                                                                        |  |  |  |  |

| OCFA                    | I           | ST             | Yes               | Compare Fault A input (for compare channels).                                                                                                                                      |  |  |  |  |

| OC1-OC4                 | 0           |                | Yes               | Compare Outputs 1 through 4.                                                                                                                                                       |  |  |  |  |

| INT0                    | I           | ST             | No                | External Interrupt 0.                                                                                                                                                              |  |  |  |  |

| INT1                    | I           | ST             | Yes               | External Interrupt 1.                                                                                                                                                              |  |  |  |  |

| INT2                    | I           | ST             | Yes               | External Interrupt 2.                                                                                                                                                              |  |  |  |  |

| INT4                    | Ι           | ST             | Yes               | External Interrupt 4.                                                                                                                                                              |  |  |  |  |

| RA0-RA4                 | I/O         | ST             | No                | PORTA is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |

| RB0-RB15                | I/O         | ST             | No                | PORTB is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |

| RC0-RC15                | I/O         | ST             | No                | PORTC is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |

| RD0-RD15                | I/O         | ST             | No                | PORTD is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |

| RE0-RE15                | I/O         | ST             | No                | PORTE is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |

| T1CK                    | I           | ST             | Yes               | Timer1 external clock input.                                                                                                                                                       |  |  |  |  |

| T2CK                    | I           | ST             | Yes               | Timer2 external clock input.                                                                                                                                                       |  |  |  |  |

| T3CK                    | I           | ST             | Yes               | Timer3 external clock input.                                                                                                                                                       |  |  |  |  |

| T4CK                    |             | ST             | No                | Timer4 external clock input.                                                                                                                                                       |  |  |  |  |

| T5CK                    |             | ST             | No                | Timer5 external clock input.                                                                                                                                                       |  |  |  |  |

| U1CTS                   | I           | ST             | Yes               | UART1 Clear-to-Send.                                                                                                                                                               |  |  |  |  |

| U1RTS                   | 0           | _              | Yes               | UART1 Ready-to-Send.                                                                                                                                                               |  |  |  |  |

| U1RX                    |             | ST             | Yes               | UART1 receive.                                                                                                                                                                     |  |  |  |  |

| U1TX                    | 0           |                | Yes               | UART1 transmit.                                                                                                                                                                    |  |  |  |  |

| BCLK1                   | 0           | ST             | Yes               | UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                                         |  |  |  |  |

| Legend: CMOS = C        |             |                |                   |                                                                                                                                                                                    |  |  |  |  |

|                         |             |                |                   | IOS levels O = Output I = Input                                                                                                                                                    |  |  |  |  |

| PPS = Per               | ripneral    | Pin Selec      | л<br>Л            | TTL = TTL input buffer                                                                                                                                                             |  |  |  |  |

1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

**2:** PWM4H/L through PWM8H/L are fixed on dsPIC33EPXXXGS708/808 devices. PWM4H/L through PWM6H/L are fixed on dsPIC33EPXXXGS706/806 devices.

3: The SCK3 pin is fixed on dsPIC33EPXXXGS706/806 and dsPIC33EPXXXGS708/808 devices.

4: PPS is available on dsPIC33EPXXXGS702 devices only.

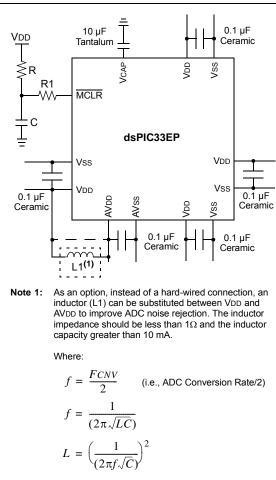

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including DSCs, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

#### 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 0.5 $\Omega$ ) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu$ F (10  $\mu$ F is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 30.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 27.4 "On-Chip Voltage Regulator"** for details.

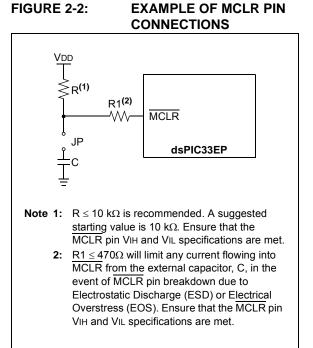

### 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{MCLR}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components as shown in Figure 2-2, within one-quarter inch (6 mm) from the MCLR pin.

#### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz < FIN < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings, after a POR with an oscillator frequency outside this range, will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

#### 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

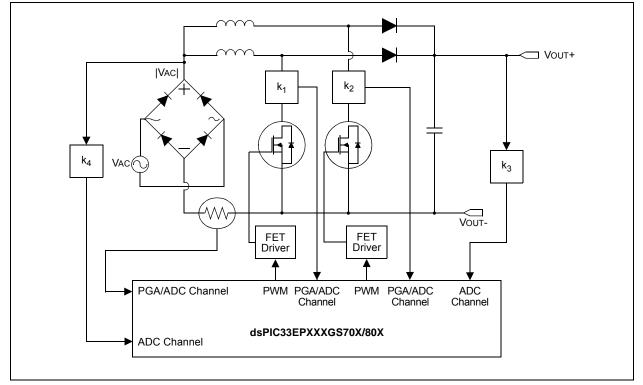

### Power Factor Correction (PFC)

- Interleaved PFC

- Interneaved FFC

- Critical Conduction PFC

- Bridgeless PFC

- DC/DC Converters

- Buck, Boost, Forward, Flyback, Push-Pull

**Targeted Applications**

- Half/Full-Bridge

- Phase-Shift Full-Bridge

- Resonant Converters

- DC/AC

2.9

- Half/Full-Bridge Inverter

- Resonant Inverter

Examples of typical application connections are shown in Figure 2-4 through Figure 2-6.

#### FIGURE 2-4: INTERLEAVED PFC

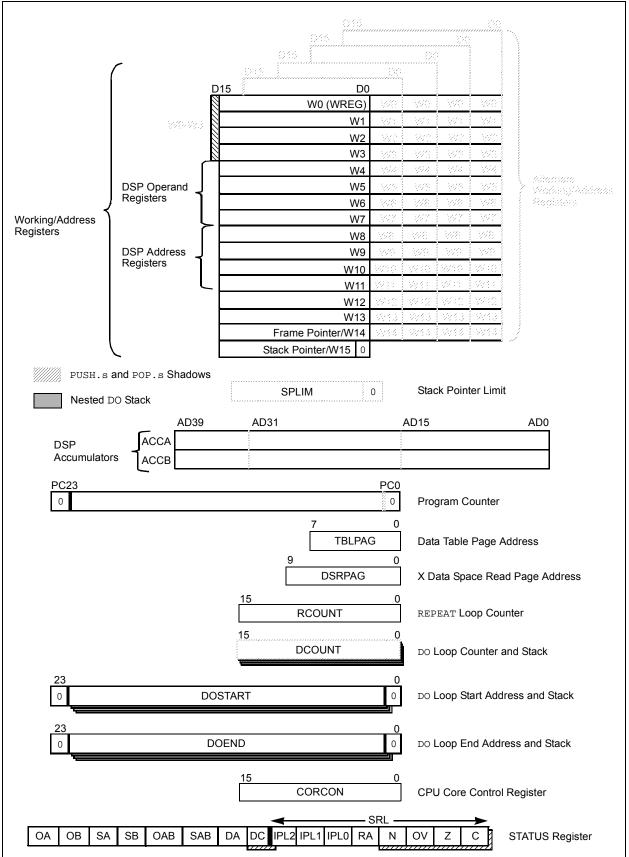

#### 3.7 CPU Control Registers

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| R/W-0                | R/W-0                            | R/W-0                                                                                                                             | R/W-0             | R/C-0                  | R/C-0            | R-0                | R/W-0           |  |  |  |

|----------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------|------------------|--------------------|-----------------|--|--|--|

| OA                   | OB                               | SA <sup>(3)</sup>                                                                                                                 | SB <sup>(3)</sup> | OAB                    | SAB              | DA                 | DC              |  |  |  |

| bit 15               |                                  |                                                                                                                                   | •                 |                        |                  |                    | bit 8           |  |  |  |

| D 444 0(2)           |                                  | D (A) (2)                                                                                                                         |                   | <b>D</b> 444 0         | DAMA             | <b>D</b> /// 0     |                 |  |  |  |

| R/W-0 <sup>(2)</sup> | R/W-0 <sup>(2)</sup>             | R/W-0 <sup>(2)</sup>                                                                                                              | R-0               | R/W-0                  | R/W-0            | R/W-0              | R/W-0           |  |  |  |

| IPL2 <sup>(1)</sup>  | IPL1 <sup>(1)</sup>              | IPL0 <sup>(1)</sup>                                                                                                               | RA                | Ν                      | OV               | Z                  | C               |  |  |  |

| bit 7                |                                  |                                                                                                                                   |                   |                        |                  |                    | bit (           |  |  |  |

| Legend:              |                                  | C = Clearable                                                                                                                     | e bit             |                        |                  |                    |                 |  |  |  |

| R = Readabl          | e bit                            | W = Writable                                                                                                                      | bit               | U = Unimpler           | nented bit, rea  | d as '0'           |                 |  |  |  |

| -n = Value at        | POR                              | '1'= Bit is set                                                                                                                   |                   | '0' = Bit is cle       | ared             | x = Bit is unkr    | nown            |  |  |  |

|                      |                                  |                                                                                                                                   |                   |                        |                  |                    |                 |  |  |  |

| bit 15               | OA: Accumu                       | lator A Overflov                                                                                                                  | v Status bit      |                        |                  |                    |                 |  |  |  |

|                      |                                  | ator A has over<br>ator A has not c                                                                                               |                   |                        |                  |                    |                 |  |  |  |

| bit 14               |                                  | lator B Overflov                                                                                                                  |                   |                        |                  |                    |                 |  |  |  |

|                      |                                  | ator B has over                                                                                                                   |                   |                        |                  |                    |                 |  |  |  |

|                      |                                  | ator B has not c                                                                                                                  |                   |                        |                  |                    |                 |  |  |  |

| bit 13               | SA: Accumul                      | <b>SA:</b> Accumulator A Saturation 'Sticky' Status bit <sup>(3)</sup>                                                            |                   |                        |                  |                    |                 |  |  |  |

|                      |                                  | <ul> <li>1 = Accumulator A is saturated or has been saturated at some time</li> <li>0 = Accumulator A is not saturated</li> </ul> |                   |                        |                  |                    |                 |  |  |  |

| bit 12               | SB: Accumul                      | <b>SB:</b> Accumulator B Saturation 'Sticky' Status bit <sup>(3)</sup>                                                            |                   |                        |                  |                    |                 |  |  |  |

|                      |                                  | ator B is saturat<br>ator B is not sat                                                                                            |                   | en saturated at        | some time        |                    |                 |  |  |  |

| bit 11               |                                  |                                                                                                                                   |                   | Verflow Status         | bit              |                    |                 |  |  |  |

|                      | 1 = Accumula                     | ator A or B has                                                                                                                   | overflowed        |                        |                  |                    |                 |  |  |  |

|                      |                                  | ccumulator A o                                                                                                                    |                   |                        |                  |                    |                 |  |  |  |

| bit 10               |                                  |                                                                                                                                   |                   | ticky' Status bit      |                  |                    |                 |  |  |  |

|                      |                                  | ator A or B is sa<br>accumulator A c                                                                                              |                   | is been saturate<br>ed | ed at some tim   | e                  |                 |  |  |  |

| bit 9                | DA: DO Loop                      | Active bit                                                                                                                        |                   |                        |                  |                    |                 |  |  |  |

|                      | 1 = DO <b>loop</b> is            | s in progress                                                                                                                     |                   |                        |                  |                    |                 |  |  |  |

|                      |                                  | s not in progres                                                                                                                  |                   |                        |                  |                    |                 |  |  |  |

| bit 8                |                                  | U Half Carry/Bo                                                                                                                   |                   |                        |                  |                    |                 |  |  |  |

|                      |                                  | out from the 4th sult occurred                                                                                                    | low-order bit     | (for byte-sized c      | lata) or 8th low | -order bit (for wo | ord-sized data  |  |  |  |

|                      | 0 = No carry                     |                                                                                                                                   |                   | bit (for byte-size     | ed data) or 8th  | n low-order bit (  | for word-sized  |  |  |  |

| Note 1: T            | he IPL<2:0> bits                 | are concatenat                                                                                                                    | ted with the IF   | PL<3> bit (COR         | CON<3>) to fo    | orm the CPU Int    | errupt Priority |  |  |  |

|                      | evel. The value in<br>PL<3> = 1. | n parentheses i                                                                                                                   | ndicates the      | IPL, if IPL<3> =       | 1. User interro  | upts are disable   | d when          |  |  |  |

| <b>2</b> : T         | he IPL<2:0> Stat                 | us bits are read                                                                                                                  | d-only when t     | he NSTDIS bit (        | (INTCON1<15      | >)=1.              |                 |  |  |  |

| ~ .                  |                                  |                                                                                                                                   |                   |                        |                  |                    |                 |  |  |  |

**3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

#### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| h:+ 7 C | $ \mathbf{p}  \sim 2 \cdot \mathbf{p} \sim C \mathbf{p} $   Interment Driver in Level Contraction hits (1.2) |

|---------|--------------------------------------------------------------------------------------------------------------|

| bit 7-5 | <b>IPL&lt;2:0&gt;:</b> CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                             |

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled                                   |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                                                                 |

|         | 101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)                 |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                                                                 |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                                                                 |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                                                  |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                                                  |

| bit 4   | RA: REPEAT Loop Active bit                                                                                   |

|         | 1 = REPEAT loop is in progress                                                                               |

|         | 0 = REPEAT loop is not in progress                                                                           |

| bit 3   | N: MCU ALU Negative bit                                                                                      |

|         | 1 = Result was negative                                                                                      |

|         | 0 = Result was non-negative (zero or positive)                                                               |

| bit 2   | OV: MCU ALU Overflow bit                                                                                     |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that      |

|         | causes the sign bit to change state.                                                                         |

|         | 1 = Overflow occurred for signed arithmetic (in this arithmetic operation)                                   |

|         | 0 = No overflow occurred                                                                                     |

| bit 1   | Z: MCU ALU Zero bit                                                                                          |

|         | 1 = An operation that affects the Z bit has set it at some time in the past                                  |

|         | 0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)                |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                  |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                         |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                        |

| Note 1: | The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority        |

|         |                                                                                                              |

- Iote 1: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 2: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

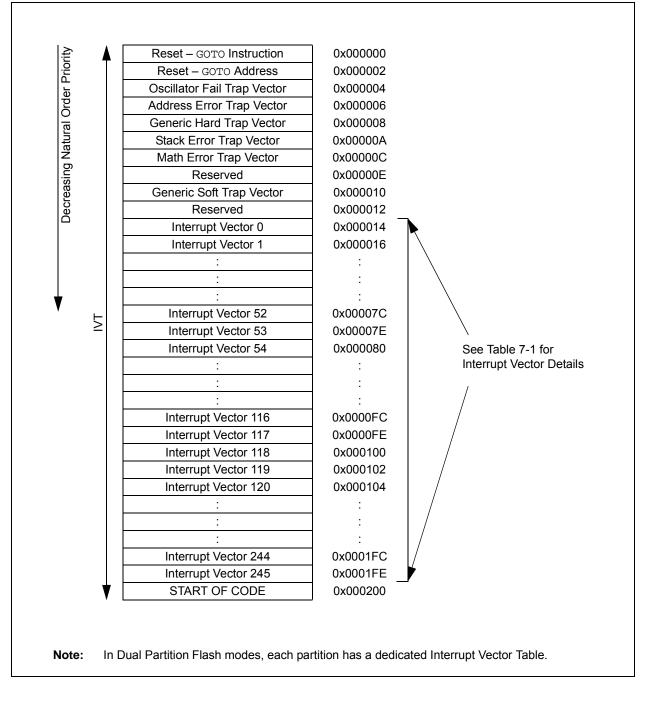

#### FIGURE 7-1: dsPIC33EPXXXGS70X/80X FAMILY INTERRUPT VECTOR TABLE

| Function               | RPnR<6:0> | Output Name                                                 |

|------------------------|-----------|-------------------------------------------------------------|

| Default PORT           | 0000000   | RPn tied to Default Pin                                     |

| U1TX                   | 0000001   | RPn tied to UART1 Transmit                                  |

| U1RTS                  | 0000010   | RPn tied to UART1 Request-to-Send                           |

| U2TX                   | 0000011   | RPn tied to UART2 Transmit                                  |

| U2RTS                  | 0000100   | RPn tied to UART2 Request-to-Send                           |

| SDO1                   | 0000101   | RPn tied to SPI1 Data Output                                |

| SCK1                   | 0000110   | RPn tied to SPI1 Clock Output                               |

| SS1                    | 0000111   | RPn tied to SPI1 Slave Select                               |

| SDO2                   | 0001000   | RPn tied to SPI2 Data Output                                |

| SCK2                   | 0001001   | RPn tied to SPI2 Clock Output                               |

| SS2                    | 0001010   | RPn tied to SPI2 Slave Select                               |

| C1TX                   | 0001110   | RPn tied to CAN1 Transmit                                   |

| C2TX                   | 0001111   | RPn tied to CAN2 Transmit                                   |

| OC1                    | 0010000   | RPn tied to Output Compare 1 Output                         |

| OC2                    | 0010001   | RPn tied to Output Compare 2 Output                         |

| OC3                    | 0010010   | RPn tied to Output Compare 3 Output                         |

| OC4                    | 0010011   | RPn tied to Output Compare 4 Output                         |

| ACMP1                  | 0011000   | RPn tied to Analog Comparator 1 Output                      |

| ACMP2                  | 0011001   | RPn tied to Analog Comparator 2 Output                      |

| ACMP3                  | 0011010   | RPn tied to Analog Comparator 3 Output                      |

| SDO3                   | 0011111   | RPn tied to SPI3 Data Output                                |

| SCK3                   | 0100000   | RPn tied to SPI3 Clock Output                               |

| SS3                    | 0100001   | RPn tied to SPI3 Slave Select                               |

| SYNCO1                 | 0101101   | RPn tied to PWM Primary Master Time Base Sync Output        |

| SYNCO2                 | 0101110   | RPn tied to PWM Secondary Master Time Base Sync Output      |

| REFCLKO                | 0110001   | RPn tied to Reference Clock Output                          |

| ACMP4                  | 0110010   | RPn tied to Analog Comparator 4 Output                      |

| PWM4H                  | 0110011   | RPn tied to PWM Output Pins Associated with PWM Generator 4 |

| PWM4L                  | 0110100   | RPn tied to PWM Output Pins Associated with PWM Generator 4 |

| PWM5H                  | 0110101   | RPn tied to PWM Output Pins Associated with PWM Generator 5 |

| PWM5L                  | 0110110   | RPn tied to PWM Output Pins Associated with PWM Generator 5 |

| PWM6H                  | 0111001   | RPn tied to PWM Output Pins Associated with PWM Generator 6 |

| PWM6L                  | 0111010   | RPn tied to PWM Output Pins Associated with PWM Generator 6 |

| PWM7H                  | 0111011   | RPn tied to PWM Output Pins Associated with PWM Generator 7 |

| PWM7L                  | 0111100   | RPn tied to PWM Output Pins Associated with PWM Generator 7 |

| PWM8H                  | 0111101   | RPn tied to PWM Output Pins Associated with PWM Generator 8 |

| PWM8L                  | 0111110   | RPn tied to PWM Output Pins Associated with PWM Generator 8 |

| CLC1OUT                | 0111111   | RPn tied to CLC1 Output                                     |

| CLC2OUT                | 1000000   | RPn tied to CLC2 Output                                     |

| CLC3OUT <sup>(1)</sup> | 1000001   | RPn tied to CLC3 Output                                     |

| CLC4OUT <sup>(1)</sup> | 1000010   | RPn tied to CLC4 Output                                     |

Note 1: PPS outputs are only available on dsPIC33EPXXXGS702 (28-pin) devices.

| U-0    | R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| _      | RP45R6 | RP45R5 | RP45R4 | RP45R3 | RP45R2 | RP45R1 | RP45R0 |

| bit 15 | ·      | •      |        | •      |        | •      | bit    |

#### **REGISTER 11-41: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8**

| U-0   | R/W-0  |

|-------|--------|--------|--------|--------|--------|--------|--------|

| —     | RP44R6 | RP44R5 | RP44R4 | RP44R3 | RP44R2 | RP44R1 | RP44R0 |

| bit 7 |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15   | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-8 | <b>RP45R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP45 Output Pin bits (see Table 11-13 for peripheral function numbers) |

| bit 7    | Unimplemented: Read as '0'                                                                                                                |

| bit 6-0  | <b>RP44R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP44 Output Pin bits (see Table 11-13 for peripheral function numbers) |

#### **REGISTER 11-42: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9**

| U-0                                | R/W-0                                                                                   | R/W-0        | R/W-0  | R/W-0                                   | R/W-0            | R/W-0    | R/W-0  |  |

|------------------------------------|-----------------------------------------------------------------------------------------|--------------|--------|-----------------------------------------|------------------|----------|--------|--|

| _                                  | RP47R6                                                                                  | RP47R5       | RP47R4 | RP47R3                                  | RP47R2           | RP47R1   | RP47R0 |  |

| bit 15                             |                                                                                         |              |        |                                         |                  |          | bit 8  |  |

|                                    |                                                                                         |              |        |                                         |                  |          |        |  |

| U-0                                | R/W-0                                                                                   | R/W-0        | R/W-0  | R/W-0                                   | R/W-0            | R/W-0    | R/W-0  |  |

| —                                  | RP46R6                                                                                  | RP46R5       | RP46R4 | RP46R3                                  | RP46R2           | RP46R1   | RP46R0 |  |

| bit 7                              |                                                                                         |              |        |                                         |                  |          | bit 0  |  |

|                                    |                                                                                         |              |        |                                         |                  |          |        |  |

| Legend:                            |                                                                                         |              |        |                                         |                  |          |        |  |

| R = Readable                       | e bit                                                                                   | W = Writable | bit    | U = Unimpler                            | mented bit, read | l as '0' |        |  |

| -n = Value at POR '1' = Bit is set |                                                                                         |              |        | '0' = Bit is cleared x = Bit is unknown |                  |          |        |  |

| <u>.</u>                           |                                                                                         |              |        |                                         |                  |          |        |  |

| bit 15                             | Unimplemented: Read as '0'                                                              |              |        |                                         |                  |          |        |  |

| bit 14-8                           | <b>RP47R&lt;6:0&gt;:</b> Peripheral Output Function is Assigned to RP47 Output Pin bits |              |        |                                         |                  |          |        |  |

bit 14-8 **RP47R<6:0>:** Peripheral Output Function is Assigned to RP47 Output Pin bits (see Table 11-13 for peripheral function numbers)

bit 7 Unimplemented: Read as '0'

bit 6-0 RP46R<6:0>: Peripheral Output Function is Assigned to RP46 Output Pin bits (see Table 11-13 for peripheral function numbers)

bit 8

#### BUFFER 21-7: CANx MESSAGE BUFFER WORD 6

| R/W-x                              | R/W-x | R/W-x | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |

|------------------------------------|-------|-------|-------|------------------------------------|-------|-----------------|-------|--|

|                                    |       |       | Byte  | 7<15:8>                            |       |                 |       |  |

| bit 15                             |       |       |       |                                    |       |                 | bit 8 |  |

|                                    |       |       |       |                                    |       |                 |       |  |

| R/W-x                              | R/W-x | R/W-x | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |

|                                    |       |       | Byte  | 6<7:0>                             |       |                 |       |  |

| bit 7                              |       |       |       |                                    |       |                 | bit 0 |  |

|                                    |       |       |       |                                    |       |                 |       |  |

| Legend:                            |       |       |       |                                    |       |                 |       |  |

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplemented bit, read as '0' |       |                 |       |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cle                   | ared  | x = Bit is unki | nown  |  |

| bit 15-8 | Byte 7<15:8>: CANx Message Byte 7 bits |

|----------|----------------------------------------|

|          |                                        |

bit 7-0 Byte 6<7:0>: CANx Message Byte 6 bits

#### BUFFER 21-8: CANx MESSAGE BUFFER WORD 7

| U-0    | U-0 | U-0 | R/W-x | R/W-x | R/W-x         | R/W-x | R/W-x |

|--------|-----|-----|-------|-------|---------------|-------|-------|

| _      | —   | —   |       |       | FILHIT<4:0>(1 | )     |       |

| bit 15 |     |     |       |       |               |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | _   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                     |

|-----------|----------------------------------------------------------------|

| bit 12-8  | FILHIT<4:0>: Filter Hit Code bits <sup>(1)</sup>               |

|           | Encodes number of filter that resulted in writing this buffer. |

| bit 7-0   | Unimplemented: Read as '0'                                     |

Note 1: Only written by module for receive buffers, unused for transmit buffers.

#### 25.2 PGA Resources

Many useful resources are provided on the main product page of the Microchip website for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 25.2.1 KEY RESOURCES

- "Programmable Gain Amplifier (PGA)" (DS70005146) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 25-1: PGAxCON: PGAx CONTROL REGISTER

| R/W-0         | R/W-0        | R/W-0            | R/W-0           | R/W-0            | R/W-0            | R/W-0              | R/W-0  |  |

|---------------|--------------|------------------|-----------------|------------------|------------------|--------------------|--------|--|

| PGAEN         | PGAOEN       | SELPI2           | SELPI1          | SELPI0           | SELNI2           | SELNI1             | SELNI0 |  |

| bit 15        |              |                  |                 |                  |                  | <u>.</u>           | bit 8  |  |

|               |              |                  |                 |                  |                  |                    |        |  |

| U-0           | U-0          | U-0              | U-0             | U-0              | R/W-0            | R/W-0              | R/W-0  |  |

| _             | _            | _                | _               | _                | GAIN2            | GAIN1              | GAIN0  |  |

| bit 7         |              | •                |                 |                  |                  |                    | bit C  |  |

|               |              |                  |                 |                  |                  |                    |        |  |

| Legend:       |              |                  |                 |                  |                  |                    |        |  |

| R = Readabl   | e bit        | W = Writable     | bit             | U = Unimpler     | mented bit, read | 1 as '0'           |        |  |

| -n = Value at | t POR        | '1' = Bit is set | t               | '0' = Bit is cle | ared             | x = Bit is unknown |        |  |

|               |              |                  |                 |                  |                  |                    |        |  |

| bit 15        | PGAEN: PGA   | Ax Enable bit    |                 |                  |                  |                    |        |  |

|               | 1 = PGAx mo  | dule is enable   | d               |                  |                  |                    |        |  |

|               | 0 = PGAx mo  | odule is disable | d (reduces po   | wer consumpt     | ion)             |                    |        |  |

| bit 14        | PGAOEN: PO   | GAx Output En    | able bit        |                  |                  |                    |        |  |

|               | 1 = PGAx out | tput is connect  | ed to the DAC   | OUTx pin         |                  |                    |        |  |

|               | 0 = PGAx out | tput is not conr | nected to the I | DACOUTx pin      |                  |                    |        |  |

| bit 13-11     | SELPI<2:0>:  | PGAx Positive    | e Input Selecti | on bits          |                  |                    |        |  |

|               | 111 = Reserv | ved              |                 |                  |                  |                    |        |  |

|               | 110 = Reserv | ved              |                 |                  |                  |                    |        |  |

|               | 101 = Reserv | ved              |                 |                  |                  |                    |        |  |

|               | 100 = Reserv | ved              |                 |                  |                  |                    |        |  |

|               | 011 = PGAxF  | -                |                 |                  |                  |                    |        |  |

|               | 010 = PGAxF  | >3               |                 |                  |                  |                    |        |  |

|               |              | 22               |                 |                  |                  |                    |        |  |

001 = PGAxP2 000 = PGAxP1

#### bit 10-8 **SELNI<2:0>:** PGAx Negative Input Selection bits

- 111 = Reserved 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = Ground (Single-Ended mode)

- 010 = PGAxN3

- 001 = PGAxN2

- 000 = Ground (Single-Ended mode)

- bit 7-3 Unimplemented: Read as '0'

| Bit Field   | Description                                                                 |

|-------------|-----------------------------------------------------------------------------|

| WDTWIN<1:0> | Watchdog Timer Window Select bits                                           |

|             | 11 = WDT window is 25% of the WDT period                                    |

|             | 10 = WDT window is 37.5% of the WDT period                                  |

|             | 01 = WDT window is 50% of the WDT period                                    |

|             | 00 = WDT window is 75% of the WDT period                                    |

| ALTI2C1     | Alternate I2C1 Pin bit                                                      |

|             | 1 = I2C1 is mapped to the SDA1/SCL1 pins                                    |

|             | 0 = I2C1 is mapped to the ASDA1/ASCL1 pins                                  |

| ALTI2C2     | Alternate I2C2 Pin bit                                                      |

|             | 1 = I2C2 is mapped to the SDA2/SCL2 pins                                    |

|             | 0 = I2C2 is mapped to the ASDA2/ASCL2 pins                                  |

| JTAGEN      | JTAG Enable bit                                                             |

|             | 1 = JTAG is enabled                                                         |

|             | 0 = JTAG is disabled                                                        |

| ICS<1:0>    | ICD Communication Channel Select bits                                       |

|             | 11 = Communicates on PGEC1 and PGED1                                        |

|             | 10 = Communicates on PGEC2 and PGED2                                        |

|             | 01 = Communicates on PGEC3 and PGED3                                        |

|             | 00 = Reserved, do not use                                                   |

| DBCC        | DACx Output Cross Connection Select bit                                     |

|             | 1 = No cross connection between DAC outputs                                 |

|             | 0 = Interconnects DACOUT1 and DACOUT2                                       |

| CTXT1<2:0>  | Alternate Working Register Set 1 Interrupt Priority Level (IPL) Select bits |

|             | 111 = Reserved                                                              |

|             | 110 = Assigned to IPL of 7                                                  |

|             | 101 = Assigned to IPL of 6                                                  |

|             | 100 = Assigned to IPL of 5                                                  |

|             | 011 = Assigned to IPL of 4                                                  |

|             | 010 = Assigned to IPL of 3<br>001 = Assigned to IPL of 2                    |

|             | 000 = Assigned to IPL of 1                                                  |

| CTXT2<2:0>  | Alternate Working Register Set 2 Interrupt Priority Level (IPL) Select bits |

| 01/12/2.0/  | 111 = Reserved                                                              |

|             | 110 = Assigned to IPL of 7                                                  |

|             | 101 = Assigned to IPL of 6                                                  |

|             | 100 = Assigned to IPL of 5                                                  |

|             | 011 = Assigned to IPL of 4                                                  |

|             | 010 = Assigned to IPL of 3                                                  |

|             | 001 = Assigned to IPL of 2                                                  |

|             | 000 = Assigned to IPL of 1                                                  |

| CTXT3<2:0>  | Alternate Working Register Set 3 Interrupt Priority Level (IPL) Select bits |

|             | 111 = Reserved                                                              |

|             | 110 = Assigned to IPL of 7                                                  |

|             | 101 = Assigned to IPL of 6                                                  |

|             | 100 = Assigned to IPL of 5                                                  |

|             | 011 = Assigned to IPL of 4                                                  |

|             | 010 = Assigned to IPL of 3<br>001 = Assigned to IPL of 2                    |

|             | 000 = Assigned to IPL of 1                                                  |

| L           |                                                                             |

#### TABLE 27-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

Note 1: The Boot Segment must be present to use the Alternate Interrupt Vector Table.

| DC CHARACTERISTICS |        |                                                     | Standard Operating Co<br>(unless otherwise state<br>Operating temperature |                     |      |       |                                                                |  |

|--------------------|--------|-----------------------------------------------------|---------------------------------------------------------------------------|---------------------|------|-------|----------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                      | Min.                                                                      | Тур. <sup>(1)</sup> | Max. | Units | Conditions                                                     |  |

|                    |        | Program Flash Memory                                |                                                                           |                     |      |       |                                                                |  |

| D130               | Eр     | Cell Endurance                                      | 10,000                                                                    | —                   | _    | E/W   | -40°C to +125°C                                                |  |

| D131               | Vpr    | VDD for Read                                        | 3.0                                                                       | —                   | 3.6  | V     |                                                                |  |

| D132b              | VPEW   | VDD for Self-Timed Write                            | 3.0                                                                       | —                   | 3.6  | V     |                                                                |  |

| D134               | TRETD  | Characteristic Retention                            | 20                                                                        | —                   | —    | Year  | Provided no other specifications are violated, -40°C to +125°C |  |

| D135               | IDDP   | Supply Current during<br>Programming <sup>(2)</sup> | _                                                                         | 10                  | —    | mA    |                                                                |  |

| D136               | IPEAK  | Instantaneous Peak Current<br>During Start-up       | _                                                                         | —                   | 150  | mA    |                                                                |  |

| D137a              | TPE    | Page Erase Time                                     | 19.7                                                                      | —                   | 20.1 | ms    | TPE = 146893 FRC cycles,<br>TA = +85°C <b>(Note 3)</b>         |  |

| D137b              | TPE    | Page Erase Time                                     | 19.5                                                                      | —                   | 20.3 | ms    | TPE = 146893 FRC cycles,<br>Ta = +125°C <b>(Note 3)</b>        |  |

| D138a              | Tww    | Word Write Cycle Time                               | 46.5                                                                      | —                   | 47.3 | μs    | Tww = 346 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>            |  |

| D138b              | Tww    | Word Write Cycle Time                               | 46.0                                                                      | —                   | 47.9 | μs    | Tww = 346 FRC cycles,<br>Ta = +125°C <b>(Note 3)</b>           |  |

| D139a              | Trw    | Row Write Time                                      | 667                                                                       | -                   | 679  | μs    | Trw = 4965 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>           |  |

| D139b              | Trw    | Row Write Time                                      | 660                                                                       | -                   | 687  | μs    | Trw = 4965 FRC cycles,<br>Ta = +125°C <b>(Note 3)</b>          |  |

#### TABLE 30-14: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

2: Parameter characterized but not tested in manufacturing.

3: Other conditions: FRC = 7.37 MHz, TUN<5:0> = 011111 (for Minimum), TUN<5:0> = 100000 (for Maximum). This parameter depends on the FRC accuracy (see Table 30-20) and the value of the FRC Oscillator Tuning register (see Register 9-4). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

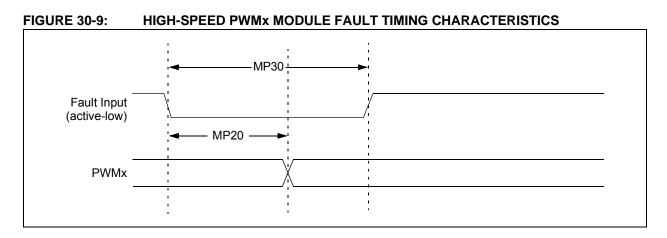

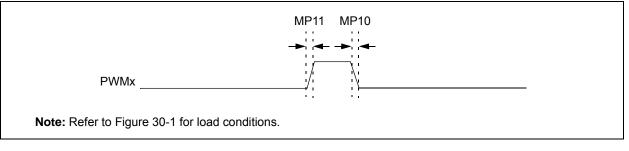

#### FIGURE 30-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 30-30: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |   |    |    |                    |  |

|--------------------|--------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|----|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>       | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                                                       |   |    |    |                    |  |

| MP10               | TFPWM  | PWMx Output Fall Time               | _                                                                                                                                                                                                                                                                                     | _ | —  | ns | See Parameter DO32 |  |

| MP11               | TRPWM  | PWMx Output Rise Time               | —                                                                                                                                                                                                                                                                                     | _ | —  | ns | See Parameter DO31 |  |

| MP20               | Tfd    | Fault Input ↓ to PWMx<br>I/O Change | _                                                                                                                                                                                                                                                                                     | _ | 15 | ns |                    |  |

| MP30               | Tfh    | Fault Input Pulse Width             | 15                                                                                                                                                                                                                                                                                    | — | —  | ns |                    |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

### TABLE 30-38:SPI1, SPI2 AND SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)TIMING REQUIREMENTS<sup>(5)</sup>

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                             |  |

|--------------------|-----------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                   | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP70               | FscP                  | Maximum SCKx Input Frequency                 | —                                                                                                                                                                                                                                                                                      | _                   | 11   | MHz   | (Note 3)                    |  |

| SP72               | TscF                  | SCKx Input Fall Time                         | —                                                                                                                                                                                                                                                                                      | _                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP73               | TscR                  | SCKx Input Rise Time                         | —                                                                                                                                                                                                                                                                                      | _                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                   | —                                                                                                                                                                                                                                                                                      | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                      | —                   |      | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    | —                                                                                                                                                                                                                                                                                      | 6                   | 20   | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge | 30                                                                                                                                                                                                                                                                                     | _                   | _    | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge   | 30                                                                                                                                                                                                                                                                                     | —                   | _    | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge    | 30                                                                                                                                                                                                                                                                                     | —                   | _    | ns    |                             |  |

| SP50               | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↑ or SCKx ↓<br>Input           | 120                                                                                                                                                                                                                                                                                    | —                   | —    | ns    |                             |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance       | 10                                                                                                                                                                                                                                                                                     | —                   | 50   | ns    | (Note 4)                    |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                        | 1.5 TCY + 40                                                                                                                                                                                                                                                                           | —                   |      | ns    | (Note 4)                    |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

5: Pertaining to SPI3: dsPIC33EPXXXGS702, dsPIC33EPXXXGSX04 and dsPIC33EPXXXGSX05 devices with a remappable SCK3 pin.

### TABLE 30-43:SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS<sup>(5)</sup>

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extende} \end{array}$ |                     |      |       |                             |  |

|--------------------|-----------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                   | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP70               | FscP                  | Maximum SCK3 Input Frequency                 | —                                                                                                                                                                                                                                                                                      | —                   | 25   | MHz   | (Note 3)                    |  |

| SP72               | TscF                  | SCK3 Input Fall Time                         |                                                                                                                                                                                                                                                                                        |                     |      | ns    | See Parameter DO32 (Note 4) |  |

| SP73               | TscR                  | SCK3 Input Rise Time                         | —                                                                                                                                                                                                                                                                                      | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO3 Data Output Fall Time                   | —                                                                                                                                                                                                                                                                                      | -                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO3 Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                      | _                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO3 Data Output Valid after<br>SCK3 Edge    | —                                                                                                                                                                                                                                                                                      | 6                   | 20   | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO3 Data Output Setup to<br>First SCK3 Edge | 20                                                                                                                                                                                                                                                                                     | _                   | _    | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI3 Data Input to SCK3 Edge   | 20                                                                                                                                                                                                                                                                                     | —                   |      | ns    |                             |  |