Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                             |

| Number of I/O              | 50                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                          |

| Data Converters            | A/D 16x16b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LFBGA                                                              |

| Supplier Device Package    | 64-MAPBGA (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl27z128vmp4 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Operating Characteristics**

- Voltage range: 1.71 to 3.6 V

- Flash write voltage range: 1.71 to 3.6 V

- Temperature range: –40 to 105 °C

#### Packages

- 64 LQFP 10mm x 10mm, 0.5mm pitch, 1.6mm thickness

- 64 MAPBGA 5mm x 5mm, 0.5mm pitch, 1.23mm thickness

- 48 QFN 7mm x 7mm, 0.5mm pitch, 0.65mm thickness

- 32 QFN 5mm x 5mm, 0.5mm pitch, 0.65mm thickness

#### Security and Integrity

- 80-bit unique identification number per chip

- Advanced flash security

#### I/O

• Up to 50 general-purpose input/output pins (GPIO) and 6 high-drive pad

#### Low Power

- Down to 54uA/MHz in very low power run mode

- Down to 1.96uA in VLLS3 mode (RAM + RTC

- retained)

- · Six flexible static modes

| Product       |                           | Mer           | nory         | Package      |         | IO and ADC channel |                                |                            |

|---------------|---------------------------|---------------|--------------|--------------|---------|--------------------|--------------------------------|----------------------------|

| Part number   | Marking (Line1/<br>Line2) | Flash<br>(KB) | SRAM<br>(KB) | Pin<br>count | Package | GPIOs              | GPIOs<br>(INT/HD) <sup>1</sup> | ADC<br>channels<br>(SE/DP) |

| MKL27Z128VFM4 | M27P7V                    | 128           | 32           | 32           | QFN     | 23                 | 19/6                           | 7/0                        |

| MKL27Z256VFM4 | M27P8V                    | 256           | 32           | 32           | QFN     | 23                 | 19/6                           | 7/0                        |

| MKL27Z128VFT4 | M27P7V                    | 128           | 32           | 48           | QFN     | 36                 | 24/6                           | 14/1                       |

| MKL27Z256VFT4 | M27P8V                    | 256           | 32           | 48           | QFN     | 36                 | 24/6                           | 14/1                       |

| MKL27Z128VLH4 | MKL27Z128V//LH4           | 128           | 32           | 64           | LQFP    | 50                 | 31/6                           | 16/2                       |

| MKL27Z256VLH4 | MKL27Z256V//LH4           | 256           | 32           | 64           | LQFP    | 50                 | 31/6                           | 16/2                       |

| MKL27Z128VMP4 | M27P7V                    | 128           | 32           | 64           | MAPBGA  | 50                 | 31/6                           | 16/2                       |

| MKL27Z256VMP4 | M27P8V                    | 256           | 32           | 64           | MAPBGA  | 50                 | 31/6                           | 16/2                       |

#### **Ordering Information**

1. INT: interrupt pin numbers; HD: high drive pin numbers

#### **Related Resources**

| Туре                | Description                                                                                                                      | Resource                                                                                                                                         |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Selector<br>Guide   | The Freescale Solution Advisor is a web-based tool that features interactive application wizards and a dynamic product selector. | Solution Advisor                                                                                                                                 |

| Product Brief       | The Product Brief contains concise overview/summary information to enable quick evaluation of a device for design suitability.   | KL2XPB <sup>1</sup>                                                                                                                              |

| Reference<br>Manual | The Reference Manual contains a comprehensive description of the structure and function (operation) of a device.                 | KL27P64M48SF6RM <sup>1</sup>                                                                                                                     |

| Data Sheet          | The Data Sheet includes electrical characteristics and signal connections.                                                       | This document.                                                                                                                                   |

| Chip Errata         | The chip mask set Errata provides additional or corrective information for a particular device mask set.                         | KINETIS_L_1N71K <sup>1</sup>                                                                                                                     |

| Package<br>drawing  | Package dimensions are provided in package drawings.                                                                             | 64-LQFP: 98ASS23234W <sup>1</sup> 64<br>MAPBGA: 98ASA00420D <sup>1</sup> 32<br>QFN: 98ASA00615D <sup>1</sup> 48 QFN:<br>98ASA00616D <sup>1</sup> |

1. To find the associated resource, go to http://www.freescale.com and perform a search using this term.

2

# 1.4 Voltage and current operating ratings

Table 4. Voltage and current operating ratings

| Symbol                       | Description                                                               | Min.                  | Max.                  | Unit |

|------------------------------|---------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>DD</sub>              | Digital supply voltage                                                    | -0.3                  | 3.8                   | V    |

| I <sub>DD</sub>              | Digital supply current                                                    | _                     | 120                   | mA   |

| V <sub>IO</sub>              | IO pin input voltage                                                      | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| Ι <sub>D</sub>               | Instantaneous maximum current single pin limit (applies to all port pins) | -25                   | 25                    | mA   |

| V <sub>DDA</sub>             | Analog supply voltage                                                     | V <sub>DD</sub> – 0.3 | V <sub>DD</sub> + 0.3 | V    |

| V <sub>USB_DP</sub>          | USB_DP input voltage                                                      | -0.3                  | 3.63                  | V    |

| $V_{\text{USB}_{\text{DM}}}$ | USB_DM input voltage                                                      | -0.3                  | 3.63                  | V    |

| V <sub>REGIN</sub>           | USB regulator input                                                       | -0.3                  | 6.0                   | V    |

# 2 General

# 2.1 AC electrical characteristics

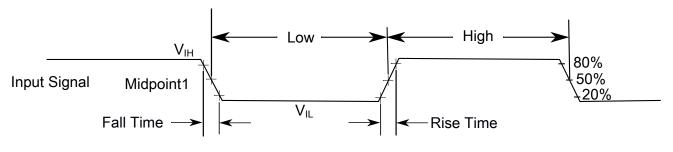

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{\text{IL}}$  +  $(V_{\text{IH}}$  -  $V_{\text{IL}})$  / 2

## Figure 1. Input signal measurement reference

All digital I/O switching characteristics, unless otherwise specified, assume that the output pins have the following characteristics.

- $C_L=30$  pF loads

- Slew rate disabled

- Normal drive strength

6

| Symbol              | Description                                                                                                                                        | Min. | Тур. | Max. | Unit | Notes |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

|                     | • at 25 °C                                                                                                                                         |      |      |      |      |       |

|                     | • at 105 °C                                                                                                                                        |      |      |      |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running<br>CoreMark in Flash all peripheral clock disable 12<br>MHz core/6 MHz flash, $V_{DD} = 3.0 V$             |      |      |      | _    | 2     |

|                     | • at 25 °C                                                                                                                                         |      | 2.68 | 3.32 | mA   |       |

|                     | • at 105 °C                                                                                                                                        |      | 2.96 | 3.60 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running<br>CoreMark in Flash all peripheral clock enable 48<br>MHz core/24 MHz flash, $V_{DD} = 3.0 \text{ V}$     |      |      |      |      | 2     |

|                     | • at 25 °C                                                                                                                                         |      | 8.08 | 8.72 | mA   |       |

|                     | • at 105 °C                                                                                                                                        | _    | 8.39 | 9.03 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running<br>While(1) loop in flash all peripheral clock disable,<br>48 MHz core/24 MHz flash, $V_{DD} = 3.0 V$      |      |      |      |      |       |

|                     | • at 25 °C                                                                                                                                         |      | 3.90 | 4.54 | mA   |       |

|                     | • at 105 °C                                                                                                                                        | —    | 4.21 | 4.85 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running<br>While(1) loop in Flash all peripheral clock disable,<br>24 MHz core/12 MHz flash, $V_{DD}$ = 3.0 V      |      |      |      |      |       |

|                     | • at 25 °C                                                                                                                                         | —    | 2.66 | 3.30 | mA   |       |

|                     | • at 105 °C                                                                                                                                        | _    | 2.94 | 3.58 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, Running<br>While(1) loop in Flash all peripheral clock disable,<br>12 MHz core/6 MHz flash, $V_{DD} = 3.0 V$       |      |      |      |      |       |

|                     | • at 25 °C                                                                                                                                         | —    | 2.03 | 2.67 | mA   |       |

|                     | • at 105 °C                                                                                                                                        | _    | 2.31 | 2.95 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, Running<br>While(1) loop in Flash all peripheral clock enable,<br>48 MHz core/24 MHz flash, $V_{DD} = 3.0 V$       |      |      |      |      |       |

|                     | • at 25 °C                                                                                                                                         | —    | 5.52 | 6.16 | mA   |       |

|                     | • at 105 °C                                                                                                                                        | —    | 5.83 | 6.47 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running<br>While(1) loop in SRAM all peripheral clock<br>disable, 48 MHz core/24 MHz flash, $V_{DD} = 3.0 V$       |      | 5.00 | 5.02 |      |       |

|                     | • at 25 °C                                                                                                                                         |      | 5.29 | 5.93 | mA   |       |

|                     | • at 105 °C                                                                                                                                        |      | 5.56 | 6.20 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running<br>While(1) loop in SRAM all peripheral clock<br>enable, 48 MHz core/24 MHz flash, V <sub>DD</sub> = 3.0 V |      |      |      |      |       |

|                     |                                                                                                                                                    | —    | 6.91 | 7.55 | mA   |       |

|                     |                                                                                                                                                    | _    | 7.19 | 7.91 |      |       |

| Table 9.    Power consumption o | perating | behavio | rs (contir | າued) |

|---------------------------------|----------|---------|------------|-------|

| scription                       | Min.     | Tvp.    | Max.       | Unit  |

Table continues on the next page...

| Symbol                 | Description                                                                                                                                                                                | Min. | Тур.   | Max.   | Unit | Notes |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|--------|------|-------|

|                        | disable, 125 kHz core / 31.25 kHz flash, V <sub>DD</sub> =<br>3.0 V<br>• at 25 °C                                                                                                          | _    | 50     | 131    | μΑ   |       |

| I <sub>DD_VLPR</sub>   | Very-low-power run mode current—2 MHz LIRC<br>mode, While(1) loop in SRAM all peripheral clock<br>enable, 2 MHz core / 0.5 MHz flash, V <sub>DD</sub> = 3.0 V<br>• at 25 °C                | _    | 208    | 289    | μΑ   |       |

| I <sub>DD_WAIT</sub>   | Wait mode current—core disabled, 48 MHz<br>system/24 MHz bus, flash disabled (flash doze<br>enabled), all peripheral clocks disabled,<br>MCG_Lite under HIRC mode, V <sub>DD</sub> = 3.0 V | _    | 1.81   | 1.89   | mA   |       |

| I <sub>DD_WAIT</sub>   | Wait mode current—core disabled, 24 MHz<br>system/12 MHz bus, flash disabled (flash doze<br>enabled), all peripheral clocks disabled,<br>MCG_Lite under HIRC mode, V <sub>DD</sub> = 3.0 V |      | 1.22   | 1.39   | mA   |       |

| I <sub>DD_VLPW</sub>   | Very-low-power wait mode current, core disabled, 4 MHz system/ 1 MHz bus and flash, all peripheral clocks disabled, $V_{DD} = 3.0$ V                                                       | —    | 172    | 182    | μA   |       |

| I <sub>DD_VLPW</sub>   | Very-low-power wait mode current, core disabled, 2 MHz system/ 0.5 MHz bus and flash, all peripheral clocks disabled, $V_{DD} = 3.0 V$                                                     | _    | 69     | 76     | μΑ   |       |

| I <sub>DD_VLPW</sub>   | Very-low-power wait mode current, core disabled, 125 kHz system/ 31.25 kHz bus and flash, all peripheral clocks disabled, $V_{\text{DD}}$ = 3.0 V                                          | —    | 36     | 40     | μΑ   |       |

| I <sub>DD_PSTOP2</sub> | Partial Stop 2, core and system clock disabled, 12 MHz bus and flash, $V_{\text{DD}}$ = 3.0 V                                                                                              |      |        |        |      |       |

|                        |                                                                                                                                                                                            | —    | 1.81   | 2.06   | mA   |       |

| I <sub>DD_PSTOP2</sub> | Partial Stop 2, core and system clock disabled, flash doze enabled, 12 MHz bus, $V_{DD}$ = 3.0 V                                                                                           |      |        |        |      |       |

|                        |                                                                                                                                                                                            | _    | 1.00   | 1.25   | mA   |       |

| I <sub>DD_STOP</sub>   | Stop mode current at 3.0 V<br>• at 25 °C and below                                                                                                                                         | _    | 161.93 | 171.82 |      |       |

|                        | • at 50 °C                                                                                                                                                                                 | _    | 181.45 | 191.96 |      |       |

|                        | • at 85 °C                                                                                                                                                                                 | _    | 236.29 | 271.17 | μA   |       |

|                        | • at 105 °C                                                                                                                                                                                | _    | 390.33 | 465.58 | ·    |       |

| I <sub>DD_VLPS</sub>   | Very-low-power stop mode current at 3.0 V<br>• at 25 °C and below                                                                                                                          |      | 3.31   | 5.14   |      |       |

|                        | • at 50 °C                                                                                                                                                                                 | _    | 10.43  | 17.68  |      |       |

|                        | • at 85 °C                                                                                                                                                                                 | _    | 34.14  | 61.06  | μA   |       |

|                        | • at 105 °C                                                                                                                                                                                | _    | 104.38 | 164.44 | ۳A   |       |

| I <sub>DD_VLPS</sub>   | Very-low-power stop mode current at 1.8 V<br>• at 25 °C and below                                                                                                                          | _    | 3.21   | 5.22   |      |       |

Table continues on the next page...

| Symbol            | Description                                                                                                                                                                                                                                                                                                                                                                                                |           | Temperature (°C) |           |           |           |           |    |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|-----------|-----------|-----------|-----------|----|

|                   |                                                                                                                                                                                                                                                                                                                                                                                                            |           | 25               | 50        | 70        | 85        | 105       |    |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                            |           |                  |           |           |           |           | nA |

| I <sub>CMP</sub>  | CMP peripheral adder measured by<br>placing the device in VLLS1 mode with<br>CMP enabled using the 6-bit DAC and a<br>single external input for compare. Includes<br>6-bit DAC power consumption.                                                                                                                                                                                                          | 22        | 22               | 22        | 22        | 22        | 22        | μA |

| I <sub>UART</sub> | <ul> <li>UART peripheral adder measured by placing the device in STOP or VLPS mode with selected clock source waiting for RX data at 115200 baud rate. Includes selected clock source power consumption.</li> <li>IRC8M (8 MHz internal reference clock)</li> <li>IRC2M (2 MHz internal reference clock)</li> </ul>                                                                                        | 114<br>34 | 114<br>34        | 114<br>34 | 114<br>34 | 114<br>34 | 114<br>34 | μA |

| I <sub>TPM</sub>  | <ul> <li>TPM peripheral adder measured by placing the device in STOP or VLPS mode with selected clock source configured for output compare generating 100 Hz clock signal. No load is placed on the I/O generating the clock signal. Includes selected clock source and I/O switching currents.</li> <li>IRC8M (8 MHz internal reference clock)</li> <li>IRC2M (2 MHz internal reference clock)</li> </ul> | 147<br>42 | 147<br>42        | 147<br>42 | 147<br>42 | 147<br>42 | 147<br>42 | μΑ |

| I <sub>BG</sub>   | Bandgap adder when BGEN bit is set and device is placed in VLPx or VLLSx mode.                                                                                                                                                                                                                                                                                                                             | 45        | 45               | 45        | 45        | 45        | 45        | μA |

| I <sub>ADC</sub>  | ADC peripheral adder combining the measured values at $V_{DD}$ and $V_{DDA}$ by placing the device in STOP or VLPS mode. ADC is configured for low power mode using the internal clock and continuous conversions.                                                                                                                                                                                         | 330       | 330              | 330       | 330       | 330       | 330       | μΑ |

| Table 10. | Low power mode p | eripheral adders — | typical value | (continued) |

|-----------|------------------|--------------------|---------------|-------------|

|-----------|------------------|--------------------|---------------|-------------|

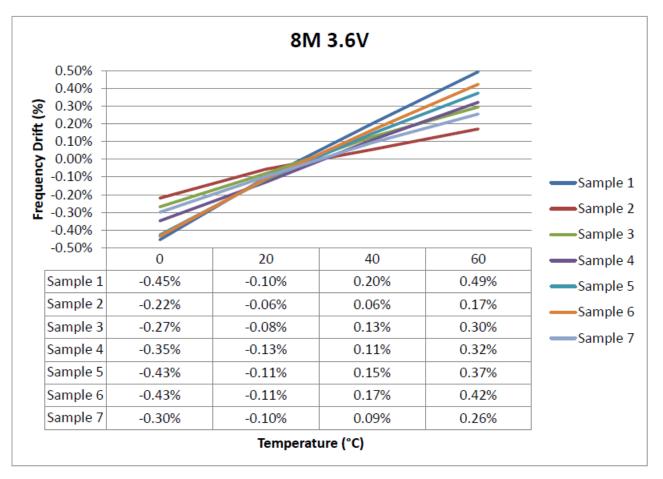

## 2.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG-Lite in HIRC for run mode, and LIRC for VLPR mode

- USB regulator disabled

- No GPIOs toggled

- Code execution from flash

- For the ALLOFF curve, all peripheral clocks are disabled except FTFA

Figure 6. IRC8M Frequency Drift vs Temperature curve

## 3.3.2 Oscillator electrical specifications

## 3.3.2.1 Oscillator DC electrical specifications Table 20. Oscillator DC electrical specifications

| Symbol             | Description                             | Min. | Тур. | Max. | Unit | Notes |

|--------------------|-----------------------------------------|------|------|------|------|-------|

| V <sub>DD</sub>    | Supply voltage                          | 1.71 | —    | 3.6  | V    |       |

| I <sub>DDOSC</sub> | Supply current — low-power mode (HGO=0) |      |      |      |      | 1     |

|                    | • 32 kHz                                | _    | 500  | _    | nA   |       |

|                    | • 4 MHz                                 | _    | 200  | _    | μA   |       |

|                    | • 8 MHz (RANGE=01)                      | _    | 300  | _    | μA   |       |

|                    | • 16 MHz                                | _    | 950  | _    | μA   |       |

|                    |                                         | _    | 1.2  | _    | mA   |       |

Table continues on the next page ...

- C<sub>x</sub>,C<sub>y</sub> can be provided by using the integrated capacitors when the low frequency oscillator (RANGE = 00) is used. For all other cases external capacitors must be used.

- 4. When low power mode is selected, R<sub>F</sub> is integrated and must not be attached externally.

- 5. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other devices.

### 3.3.2.2 Oscillator frequency specifications Table 21. Oscillator frequency specifications

| Symbol                | Description                                                                                           | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low-<br>frequency mode (MCG_C2[RANGE]=00)                 | 32   | —    | 40   | kHz  |       |

| f <sub>osc_hi_1</sub> | Oscillator crystal or resonator frequency —<br>high-frequency mode (low range)<br>(MCG_C2[RANGE]=01)  | 3    | _    | 8    | MHz  |       |

| f <sub>osc_hi_2</sub> | Oscillator crystal or resonator frequency —<br>high frequency mode (high range)<br>(MCG_C2[RANGE]=1x) | 8    |      | 32   | MHz  |       |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)                                                           | _    | —    | 48   | MHz  | 1, 2  |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                                                          | 40   | 50   | 60   | %    |       |

| t <sub>cst</sub>      | Crystal startup time — 32 kHz low-frequency,<br>low-power mode (HGO=0)                                | —    | 750  | _    | ms   | 3, 4  |

|                       | Crystal startup time — 32 kHz low-frequency,<br>high-gain mode (HGO=1)                                | —    | 250  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), low-power mode<br>(HGO=0)          | _    | 0.6  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), high-gain mode<br>(HGO=1)          | _    | 1    | —    | ms   |       |

1. Other frequency limits may apply when external clock is being used as a reference for the FLL

- 2. When transitioning from FEI or FBI to FBE mode, restrict the frequency of the input clock so that, when it is divided by FRDIV, it remains within the limits of the DCO input clock frequency.

- 3. Proper PC board layout procedures must be followed to achieve specifications.

- 4. Crystal startup time is defined as the time between the oscillator being enabled and the OSCINIT bit in the MCG\_S register being set.

## 3.4 Memories and memory interfaces

## 3.4.1 Flash electrical specifications

This section describes the electrical characteristics of the flash memory module.

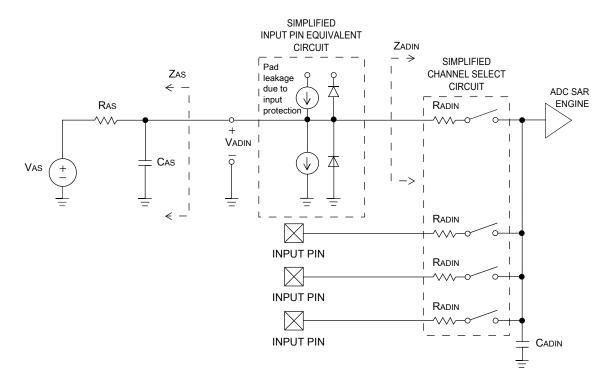

Figure 7. ADC input impedance equivalency diagram

## 3.6.1.2 16-bit ADC electrical characteristics

| Symbol               | Description                  | Conditions <sup>1</sup>              | Min.                                          | Typ. <sup>2</sup> | Max.                   | Unit             | Notes                |

|----------------------|------------------------------|--------------------------------------|-----------------------------------------------|-------------------|------------------------|------------------|----------------------|

| I <sub>DDA_ADC</sub> | Supply current               |                                      | 0.215                                         | —                 | 1.7                    | mA               | 3                    |

|                      | ADC                          | • ADLPC = 1, ADHSC = 0               | 1.2                                           | 2.4               | 3.9                    | MHz              | t <sub>ADACK</sub> = |

|                      | asynchronous<br>clock source | • ADLPC = 1, ADHSC = 1               | 2.4                                           | 4.0               | 6.1                    | MHz              | 1/f <sub>ADACK</sub> |

| f <sub>ADACK</sub>   |                              | • ADLPC = 0, ADHSC = 0               | 3.0                                           | 5.2               | 7.3                    | MHz              |                      |

|                      |                              | • ADLPC = 0, ADHSC = 1               | 4.4                                           | 6.2               | 9.5                    | MHz              |                      |

|                      | Sample Time                  | See Reference Manual chapter for     | See Reference Manual chapter for sample times |                   |                        |                  |                      |

| TUE                  | Total                        | 12-bit modes                         | _                                             | ±4                | ±6.8                   | LSB <sup>4</sup> | 5                    |

|                      | unadjusted<br>error          | <ul> <li>&lt;12-bit modes</li> </ul> | _                                             | ±1.4              | ±2.1                   |                  |                      |

| DNL                  | Differential non-            | 12-bit modes                         | —                                             | ±0.7              | -1.1 to                | LSB <sup>4</sup> | 5                    |

|                      | linearity                    | <ul> <li>&lt;12-bit modes</li> </ul> | _                                             | ±0.2              | +1.9<br>-0.3 to<br>0.5 |                  |                      |

| INL                  | Integral non-<br>linearity   | 12-bit modes                         | —                                             | ±1.0              | -2.7 to<br>+1.9        | LSB <sup>4</sup> | 5                    |

| Table 27. | 16-bit ADC characteristics | (V <sub>REFH</sub> = | V <sub>DDA</sub> , | $V_{REFL} = V_S$ | ssa) |

|-----------|----------------------------|----------------------|--------------------|------------------|------|

|-----------|----------------------------|----------------------|--------------------|------------------|------|

Table continues on the next page...

| Symbol         | Description | Min. | Max. | Unit | Notes |

|----------------|-------------|------|------|------|-------|

| T <sub>A</sub> | Temperature | 0    | 50   | °C   | —     |

#### Table 30. VREF limited-range operating requirements

#### Table 31. VREF limited-range operating behaviors

| Symbol           | Description                                | Min.  | Max.  | Unit | Notes |

|------------------|--------------------------------------------|-------|-------|------|-------|

| V <sub>out</sub> | Voltage reference output with factory trim | 1.173 | 1.225 | V    | —     |

# 3.6.3 CMP and 6-bit DAC electrical specifications

Table 32.

Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                         | Min.                  | Тур. | Max.            | Unit             |

|--------------------|-----------------------------------------------------|-----------------------|------|-----------------|------------------|

| V <sub>DD</sub>    | Supply voltage                                      | 1.71                  | _    | 3.6             | V                |

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)     | —                     | _    | 200             | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)      | —                     | _    | 20              | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                | V <sub>SS</sub> – 0.3 | _    | V <sub>DD</sub> | V                |

| V <sub>AIO</sub>   | Analog input offset voltage                         | —                     | —    | 20              | mV               |

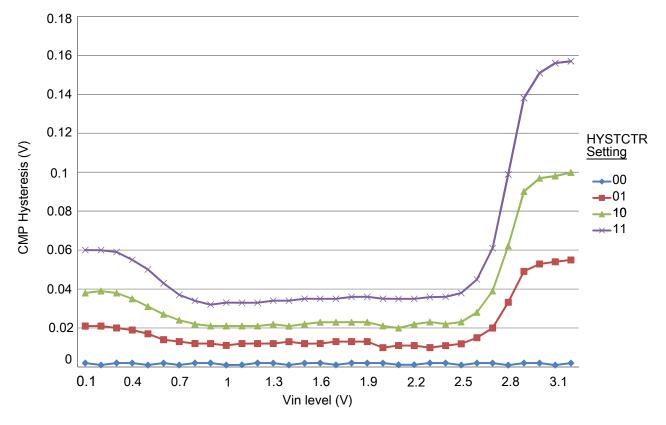

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>           |                       |      |                 |                  |

|                    | • CR0[HYSTCTR] = 00                                 | _                     | 5    | _               | mV               |

|                    | • CR0[HYSTCTR] = 01                                 | —                     | 10   | _               | mV               |

|                    | • CR0[HYSTCTR] = 10                                 | _                     | 20   | _               | mV               |

|                    | • CR0[HYSTCTR] = 11                                 | _                     | 30   | _               | mV               |

| V <sub>CMPOh</sub> | Output high                                         | V <sub>DD</sub> – 0.5 |      | _               | V                |

| V <sub>CMPOI</sub> | Output low                                          | _                     |      | 0.5             | V                |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN=1, PMODE=1)  | 20                    | 50   | 200             | ns               |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN=1, PMODE=0)   | 80                    | 250  | 600             | ns               |

|                    | Analog comparator initialization delay <sup>2</sup> |                       |      | 40              | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (enabled)                   | —                     | 7    | —               | μA               |

| INL                | 6-bit DAC integral non-linearity                    | -0.5                  |      | 0.5             | LSB <sup>3</sup> |

| DNL                | 6-bit DAC differential non-linearity                | -0.3                  |      | 0.3             | LSB              |

1. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{\text{DD}}$ –0.6 V.

Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to CMP\_DACCR[DACEN], CMP\_DACCR[VRSEL], CMP\_DACCR[VOSEL], CMP\_MUXCR[PSEL], and CMP\_MUXCR[MSEL]) and the comparator output settling to a stable level.

3. 1 LSB = V<sub>reference</sub>/64

Figure 11. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 1)

## 3.6.4 12-bit DAC electrical characteristics

### 3.6.4.1 12-bit DAC operating requirements Table 33. 12-bit DAC operating requirements

| Symbol            | Desciption              | Min. | Max. | Unit | Notes |

|-------------------|-------------------------|------|------|------|-------|

| V <sub>DDA</sub>  | Supply voltage          |      | 3.6  | V    |       |

| V <sub>DACR</sub> | Reference voltage       | 1.13 | 3.6  | V    | 1     |

| CL                | Output load capacitance | —    | 100  | pF   | 2     |

| ١L                | Output load current     | —    | 1    | mA   |       |

1. The DAC reference can be selected to be  $V_{\text{DDA}}$  or  $V_{\text{REFH}}.$

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC.

## NOTE

The IRC48M do not meet the USB jitter specifications for certification for Host mode operation.

This device cannot support Host mode operation.

## 3.8.2 USB VREG electrical specifications Table 35. USB VREG electrical specifications

| Symbol                | Description                                                                             | Min. | Typ. <sup>1</sup> | Max. | Unit     | Notes |

|-----------------------|-----------------------------------------------------------------------------------------|------|-------------------|------|----------|-------|

| VREGIN                | Input supply voltage                                                                    | 2.7  |                   | 5.5  | V        |       |

| I <sub>DDon</sub>     | Quiescent current — Run mode, load current<br>equal zero, input supply (VREGIN) > 3.6 V | _    | 125               | 186  | μA       |       |

| I <sub>DDstby</sub>   | Quiescent current — Standby mode, load current equal zero                               | —    | 1.1               | 10   | μA       |       |

| I <sub>DDoff</sub>    | Quiescent current — Shutdown mode<br>• VREGIN = 5.0 V and temperature=25 °C             | _    | 650               | 4    | nA<br>µA |       |

|                       | Across operating voltage and temperature                                                |      |                   |      | μ.,      |       |

| I <sub>LOADrun</sub>  | Maximum load current — Run mode                                                         | _    | —                 | 120  | mA       |       |

| I <sub>LOADstby</sub> | Maximum load current — Standby mode                                                     | —    | —                 | 1    | mA       |       |

| V <sub>Reg33out</sub> | Regulator output voltage — Input supply<br>(VREGIN) > 3.6 V                             |      |                   |      |          |       |

|                       | Run mode                                                                                | 3    | 3.3               | 3.6  | v        |       |

|                       | Standby mode                                                                            | 2.1  | 2.8               | 3.6  | v        |       |

| V <sub>Reg33out</sub> | Regulator output voltage — Input supply<br>(VREGIN) < 3.6 V, pass-through mode          | 2.1  |                   | 3.6  | V        | 2     |

| C <sub>OUT</sub>      | External output capacitor                                                               | 1.76 | 2.2               | 8.16 | μF       |       |

| ESR                   | External output capacitor equivalent series resistance                                  | 1    | _                 | 100  | mΩ       |       |

| I <sub>LIM</sub>      | Short circuit current                                                                   |      | 290               | _    | mA       |       |

1. Typical values assume VREGIN = 5.0 V, Temp = 25  $^\circ\text{C}$  unless otherwise stated.

2. Operating in pass-through mode: regulator output voltage equal to the input voltage minus a drop proportional to I<sub>Load</sub>.

#### Peripheral operating requirements and behaviors

1.If configured as output

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

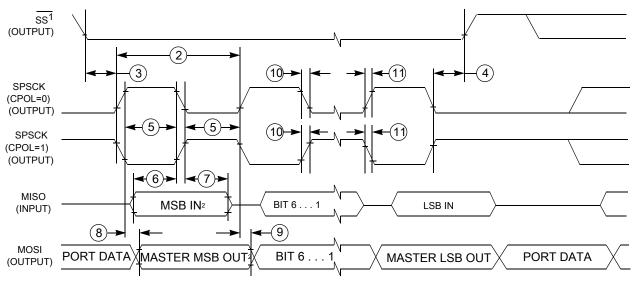

#### Figure 15. SPI master mode timing (CPHA = 1)

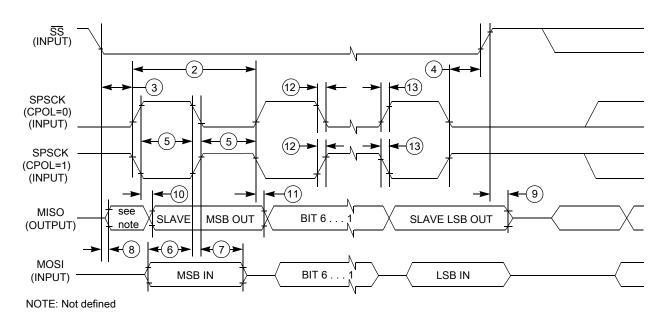

| Table 38. | SPI slave mode timing on slew rate disabled pac | st |

|-----------|-------------------------------------------------|----|

|-----------|-------------------------------------------------|----|

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit                | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|---------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | 0                        | f <sub>periph</sub> /4   | Hz                  | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 4 x t <sub>periph</sub>  | _                        | ns                  | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1                        | _                        | t <sub>periph</sub> | —    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1                        |                          | t <sub>periph</sub> | _    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | _                        | ns                  | —    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 2.5                      | _                        | ns                  | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 3.5                      |                          | ns                  | _    |

| 8    | t <sub>a</sub>      | Slave access time              | —                        | t <sub>periph</sub>      | ns                  | 3    |

| 9    | t <sub>dis</sub>    | Slave MISO disable time        | —                        | t <sub>periph</sub>      | ns                  | 4    |

| 10   | t <sub>v</sub>      | Data valid (after SPSCK edge)  | —                        | 31                       | ns                  | —    |

| 11   | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | _                        | ns                  | —    |

| 12   | t <sub>RI</sub>     | Rise time input                | _                        | t <sub>periph</sub> - 25 | ns                  | _    |

|      | t <sub>FI</sub>     | Fall time input                | 1                        |                          |                     |      |

| 13   | t <sub>RO</sub>     | Rise time output               | —                        | 25                       | ns                  | —    |

|      | t <sub>FO</sub>     | Fall time output               |                          |                          |                     |      |

1. For SPI0  $f_{periph}$  is the bus clock (f\_{BUS}). For SPI1  $f_{periph}$  is the system clock (f\_{SYS}).

- 2.  $t_{periph} = 1/f_{periph}$

- 3. Time to data active from high-impedance state

- 4. Hold time to high-impedance state

#### Peripheral operating requirements and behaviors

Figure 17. SPI slave mode timing (CPHA = 1)

# 3.8.4 I<sup>2</sup>C

## 3.8.4.1 Inter-Integrated Circuit Interface (I2C) timing Table 40. I2C timing

| Characteristic                                                                                     | Symbol                | Standa           | rd Mode           | Fast                               | Mode             | Unit |  |

|----------------------------------------------------------------------------------------------------|-----------------------|------------------|-------------------|------------------------------------|------------------|------|--|

|                                                                                                    |                       | Minimum          | Maximum           | Minimum                            | Maximum          |      |  |

| SCL Clock Frequency                                                                                | f <sub>SCL</sub>      | 0                | 100               | 0                                  | 400 <sup>1</sup> | kHz  |  |

| Hold time (repeated) START condition.<br>After this period, the first clock pulse is<br>generated. | t <sub>HD</sub> ; STA | 4                | —                 | 0.6                                | —                | μs   |  |

| LOW period of the SCL clock                                                                        | t <sub>LOW</sub>      | 4.7              | —                 | 1.25                               | —                | μs   |  |

| HIGH period of the SCL clock                                                                       | t <sub>HIGH</sub>     | 4                | —                 | 0.6                                | —                | μs   |  |

| Set-up time for a repeated START condition                                                         | t <sub>SU</sub> ; STA | 4.7              | _                 | 0.6                                | —                | μs   |  |

| Data hold time for I <sup>2</sup> C bus devices                                                    | t <sub>HD</sub> ; DAT | 0 <sup>2</sup>   | 3.45 <sup>3</sup> | 04                                 | 0.9 <sup>2</sup> | μs   |  |

| Data set-up time                                                                                   | t <sub>SU</sub> ; DAT | 250 <sup>5</sup> | —                 | 100 <sup>3</sup> , <sup>6</sup>    | —                | ns   |  |

| Rise time of SDA and SCL signals                                                                   | t <sub>r</sub>        | _                | 1000              | 20 +0.1C <sub>b</sub> <sup>7</sup> | 300              | ns   |  |

| Fall time of SDA and SCL signals                                                                   | t <sub>f</sub>        | _                | 300               | 20 +0.1C <sub>b</sub> <sup>6</sup> | 300              | ns   |  |

| Set-up time for STOP condition                                                                     | t <sub>SU</sub> ; STO | 4                | _                 | 0.6                                | _                | μs   |  |

| Bus free time between STOP and<br>START condition                                                  | t <sub>BUF</sub>      | 4.7              | —                 | 1.3                                | —                | μs   |  |

| Pulse width of spikes that must be<br>suppressed by the input filter                               | t <sub>SP</sub>       | N/A              | N/A               | 0                                  | 50               | ns   |  |

- 1. The maximum SCL Clock Frequency in Fast mode with maximum bus loading can be achieved only when using the high drive pins across the full voltage range and when using the normal drive pins and VDD ≥ 2.7 V.

- The master mode I<sup>2</sup>C deasserts ACK of an address byte simultaneously with the falling edge of SCL. If no slaves

acknowledge this address byte, then a negative hold time can result, depending on the edge rates of the SDA and

SCL lines.

- 3. The maximum tHD; DAT must be met only if the device does not stretch the LOW period (tLOW) of the SCL signal.

- 4. Input signal Slew = 10 ns and Output Load = 50 pF

- 5. Set-up time in slave-transmitter mode is 1 IPBus clock period, if the TX FIFO is empty.

- 6. A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I2C bus system, but the requirement t<sub>SU; DAT</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, then it must output the next data bit to the SDA line t<sub>rmax</sub> + t<sub>SU; DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

- 7.  $C_b$  = total capacitance of the one bus line in pF.

To achieve 1MHz I2C clock rates, consider the following recommendations:

- To counter the effects of clock stretching, the I2C baud Rate select bits can be configured for faster than desired baud rate.

- Use high drive pad and DSE bit should be set in PORTx\_PCRn register.

- Minimize loading on the I2C SDA and SCL pins to ensure fastest rise times for the SCL line to avoid clock stretching.

- Use smaller pull up resistors on SDA and SCL to reduce the RC time constant.

| Characteristic                                                                               | Symbol                | Minimum                            | Maximum        | Unit |

|----------------------------------------------------------------------------------------------|-----------------------|------------------------------------|----------------|------|

| SCL Clock Frequency                                                                          | f <sub>SCL</sub>      | 0                                  | 1 <sup>1</sup> | MHz  |

| Hold time (repeated) START condition. After this period, the first clock pulse is generated. | t <sub>HD</sub> ; STA | 0.26                               |                | μs   |

| LOW period of the SCL clock                                                                  | t <sub>LOW</sub>      | 0.5                                | —              | μs   |

| HIGH period of the SCL clock                                                                 | t <sub>HIGH</sub>     | 0.26                               |                | μs   |

| Set-up time for a repeated START condition                                                   | t <sub>SU</sub> ; STA | 0.26                               |                | μs   |

| Data hold time for I <sub>2</sub> C bus devices                                              | t <sub>HD</sub> ; DAT | 0                                  | —              | μs   |

| Data set-up time                                                                             | t <sub>SU</sub> ; DAT | 50                                 | —              | ns   |

| Rise time of SDA and SCL signals                                                             | t <sub>r</sub>        | 20 +0.1C <sub>b</sub>              | 120            | ns   |

| Fall time of SDA and SCL signals                                                             | t <sub>f</sub>        | 20 +0.1C <sub>b</sub> <sup>2</sup> | 120            | ns   |

| Set-up time for STOP condition                                                               | t <sub>SU</sub> ; STO | 0.26                               | —              | μs   |

| Bus free time between STOP and START condition                                               | t <sub>BUF</sub>      | 0.5                                |                | μs   |

| Pulse width of spikes that must be suppressed by the input filter                            | t <sub>SP</sub>       | 0                                  | 50             | ns   |

Table 41.

I <sup>2</sup>C 1Mbit/s timing

1. The maximum SCL clock frequency of 1 Mbit/s can support maximum bus loading when using the high drive pins across the full voltage range.

2.  $C_b$  = total capacitance of the one bus line in pF.

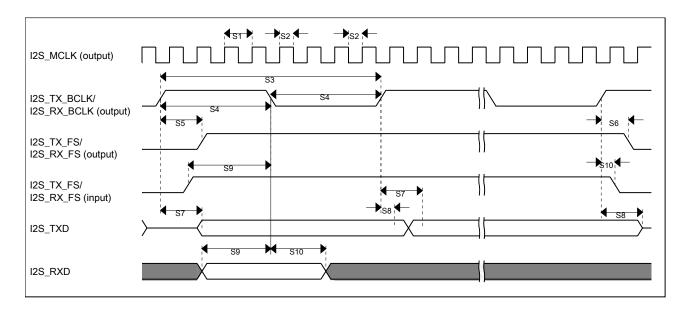

| Num. | Characteristic                                                    | Min. | Max. | Unit |

|------|-------------------------------------------------------------------|------|------|------|

| S6   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output invalid | 0    | —    | ns   |

| S7   | I2S_TX_BCLK to I2S_TXD valid                                      | —    | 19   | ns   |

| S8   | I2S_TX_BCLK to I2S_TXD invalid                                    | 0    | —    | ns   |

| S9   | I2S_RXD/I2S_RX_FS input setup before<br>I2S_RX_BCLK               | 26   | —    | ns   |

| S10  | I2S_RXD/I2S_RX_FS input hold after I2S_RX_BCLK                    | 0    | —    | ns   |

| Table 42. I2S/SAI master mode timing (continued) | Table 42. | I2S/SAI | master | mode | timing | (continued) |

|--------------------------------------------------|-----------|---------|--------|------|--------|-------------|

|--------------------------------------------------|-----------|---------|--------|------|--------|-------------|

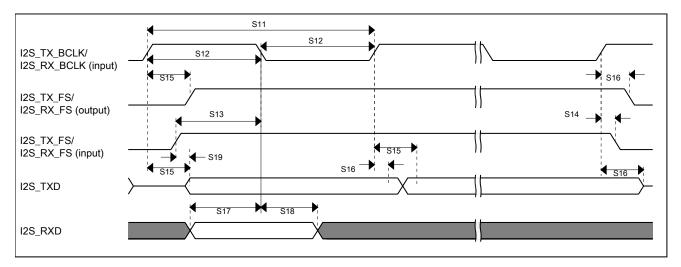

### Figure 19. I2S/SAI timing — master modes

|      |                                                                   |      | -    |             |

|------|-------------------------------------------------------------------|------|------|-------------|

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |

| S11  | I2S_TX_BCLK/I2S_RX_BCLK cycle time (input)                        | 80   | _    | ns          |

| S12  | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low (input)              | 45%  | 55%  | MCLK period |

| S13  | I2S_TX_FS/I2S_RX_FS input setup before<br>I2S_TX_BCLK/I2S_RX_BCLK | 10   | —    | ns          |

| S14  | I2S_TX_FS/I2S_RX_FS input hold after<br>I2S_TX_BCLK/I2S_RX_BCLK   | 2    | —    | ns          |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid                     | -    | 33   | ns          |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                   | 0    | —    | ns          |

| S17  | I2S_RXD setup before I2S_RX_BCLK                                  | 10   | _    | ns          |

## Table 43. I2S/SAI slave mode timing

Table continues on the next page ...

#### Peripheral operating requirements and behaviors

| Num. | Characteristic                                                 | Min. | Max. | Unit |

|------|----------------------------------------------------------------|------|------|------|

| S18  | I2S_RXD hold after I2S_RX_BCLK                                 | 2    | —    | ns   |

| S19  | I2S_TX_FS input assertion to I2S_TXD output valid <sup>1</sup> | _    | 28   | ns   |

#### Table 43. I2S/SAI slave mode timing (continued)

1. Applies to first bit in each frame and only if the TCR4[FSE] bit is clear

Figure 20. I2S/SAI timing — slave modes

# 3.8.6.2 VLPR, VLPW, and VLPS mode performance over the full operating voltage range

This section provides the operating performance over the full operating voltage for the device in VLPR, VLPW, and VLPS modes.

# Table 44. I2S/SAI master mode timing in VLPR, VLPW, and VLPS modes (full voltage range)

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|------|-------------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |

| S1   | I2S_MCLK cycle time                                               | 62.5 | _    | ns          |

| S2   | I2S_MCLK pulse width high/low                                     | 45%  | 55%  | MCLK period |

| S3   | I2S_TX_BCLK/I2S_RX_BCLK cycle time (output)                       | 250  | —    | ns          |

| S4   | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low                      | 45%  | 55%  | BCLK period |

| S5   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output valid   | —    | 45   | ns          |

| S6   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output invalid | 0    | —    | ns          |

| S7   | I2S_TX_BCLK to I2S_TXD valid                                      | —    | 45   | ns          |

Table continues on the next page...

| 32<br>QFN | 48<br>QFN | 64<br>Map | 64<br>LQFP | Pin Name                       | Default   | ALT0      | ALT1                           | ALT2      | ALT3                 | ALT4             | ALT5      | ALT6             | ALT7    |

|-----------|-----------|-----------|------------|--------------------------------|-----------|-----------|--------------------------------|-----------|----------------------|------------------|-----------|------------------|---------|

|           |           | BGA       |            |                                |           |           |                                |           |                      |                  |           |                  |         |

| 17        | 24        | H8        | 32         | PTA18                          | EXTAL0    | EXTAL0    | PTA18                          |           | LPUART1_<br>RX       | TPM_<br>CLKIN0   |           |                  |         |

| 18        | 25        | G8        | 33         | PTA19                          | XTAL0     | XTAL0     | PTA19                          |           | LPUART1_<br>TX       | TPM_<br>CLKIN1   |           | LPTMR0_<br>ALT1  |         |

| 19        | 26        | F8        | 34         | PTA20                          | RESET_b   |           | PTA20                          |           |                      |                  |           |                  | RESET_b |

| 20        | 27        | F7        | 35         | PTB0/<br>LLWU_P5               | ADC0_SE8  | ADC0_SE8  | PTB0/<br>LLWU_P5               | I2C0_SCL  | TPM1_CH0             |                  |           |                  |         |

| 21        | 28        | F6        | 36         | PTB1                           | ADC0_SE9  | ADC0_SE9  | PTB1                           | I2C0_SDA  | TPM1_CH1             |                  |           |                  |         |

| 22        | 34        | C6        | 44         | PTC1/<br>LLWU_P6/<br>RTC_CLKIN | ADC0_SE15 | ADC0_SE15 | PTC1/<br>LLWU_P6/<br>RTC_CLKIN | I2C1_SCL  |                      | TPM0_CH0         |           | 12S0_TXD0        |         |

| 23        | 35        | B7        | 45         | PTC2                           | ADC0_SE11 | ADC0_SE11 | PTC2                           | I2C1_SDA  |                      | TPM0_CH1         |           | I2S0_TX_FS       |         |

| 24        | 36        | C8        | 46         | PTC3/<br>LLWU_P7               | DISABLED  |           | PTC3/<br>LLWU_P7               | SPI1_SCK  | LPUART1_<br>RX       | TPM0_CH2         | CLKOUT    | I2S0_TX_<br>BCLK |         |

| 25        | 37        | B8        | 49         | PTC4/<br>LLWU_P8               | DISABLED  |           | PTC4/<br>LLWU_P8               | SPI0_SS   | LPUART1_<br>TX       | TPM0_CH3         | I2S0_MCLK |                  |         |

| 26        | 38        | A8        | 50         | PTC5/<br>LLWU_P9               | DISABLED  |           | PTC5/<br>LLWU_P9               | SPI0_SCK  | LPTMR0_<br>ALT2      | I2S0_RXD0        |           | CMP0_OUT         |         |

| 27        | 39        | A7        | 51         | PTC6/<br>LLWU_P10              | CMP0_IN0  | CMP0_IN0  | PTC6/<br>LLWU_P10              | SPI0_MOSI | EXTRG_IN             | I2S0_RX_<br>BCLK | SPI0_MISO | I2S0_MCLK        |         |

| 28        | 40        | B6        | 52         | PTC7                           | CMP0_IN1  | CMP0_IN1  | PTC7                           | SPI0_MISO | audioUSB_<br>SOF_OUT | I2S0_RX_FS       | SPI0_MOSI |                  |         |

| 29        | 45        | A3        | 61         | PTD4/<br>LLWU_P14              | DISABLED  |           | PTD4/<br>LLWU_P14              | SPI1_SS   | UART2_RX             | TPM0_CH4         |           | FXI00_D4         |         |

| 30        | 46        | C1        | 62         | PTD5                           | ADC0_SE6b | ADC0_SE6b | PTD5                           | SPI1_SCK  | UART2_TX             | TPM0_CH5         |           | FXIO0_D5         |         |

| 31        | 47        | B2        | 63         | PTD6/<br>LLWU_P15              | ADC0_SE7b | ADC0_SE7b | PTD6/<br>LLWU_P15              | SPI1_MOSI | LPUART0_<br>RX       |                  | SPI1_MISO | FXIO0_D6         |         |

| 32        | 48        | A2        | 64         | PTD7                           | DISABLED  |           | PTD7                           | SPI1_MISO | LPUART0_<br>TX       |                  | SPI1_MOSI | FXIO0_D7         |         |

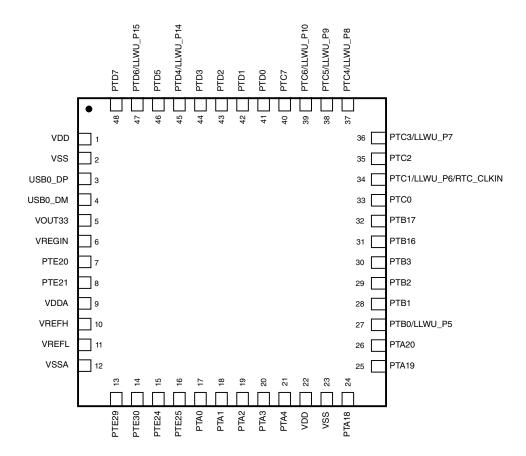

# 5.2 KL27 Family Pinouts

Figure below shows the 32 QFN pinouts:

#### Figure 24. 48 QFN Pinout diagram

Figure below shows the 64 LQFP pinouts:

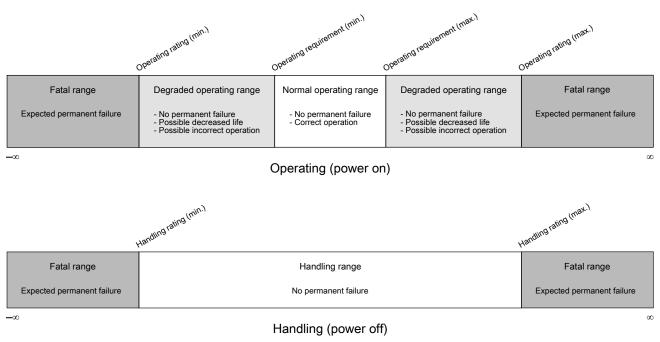

Terminology and guidelines

#### Examples 8.2

## Operating rating:

| Symbol          | Description                  | Min,     | Max. | Unit |

|-----------------|------------------------------|----------|------|------|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | -0.3 JAM | 1.2  | V    |

|                 |                              |          |      |      |

## Operating requirement:

| Operating requ  | irement:                     | <u> </u> | ¢    |      |

|-----------------|------------------------------|----------|------|------|

| Symbol          | Description                  | Min.     | Max. | Unit |

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | 0.9      | 1.1  | V    |

|                 |                              |          |      |      |

## Operating behavior that includes a typical value:

| Symbol | Description                                    | Min.  | Тур. | Max. | Unit |

|--------|------------------------------------------------|-------|------|------|------|

| Iwp    | Digital I/O weak<br>pullup/pulldown<br>current | 10 AM | 70   | 130  | μA   |

#### **Typical-value conditions** 8.3

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description          | Value | Unit |

|-----------------|----------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature  | 25    | C°   |

| V <sub>DD</sub> | 3.3 V supply voltage | 3.3   | V    |

# 8.4 Relationship between ratings and operating requirements

# 8.5 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

- Never exceed any of the chip's ratings.

- During normal operation, don't exceed any of the chip's operating requirements.

- If you must exceed an operating requirement at times other than during normal operation (for example, during power sequencing), limit the duration as much as possible.

# 9 Revision History

The following table provides a revision history for this document.

| Rev. No. | Date              | Substantial Changes                                                                                                                                                                |

|----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3        | 09 August<br>2014 | <ul> <li>Initial Public release</li> <li>Updated Table 9 - Power consumption operating behaviors.</li> <li>Added a note related to 32 QFN pin package in Pinouts topic.</li> </ul> |

| 4        | 03 March<br>2015  | <ul><li>Updated the features and completed the ordering information.</li><li>Removed thickness dimension from package diagrams.</li></ul>                                          |

#### Table 47. Revision History

Table continues on the next page ...