Welcome to **E-XFL.COM**

**Understanding Embedded - DSP (Digital Signal Processors)**

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

# Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                          |

|-------------------------|----------------------------------------------------------|

| Product Status          | Obsolete                                                 |

| Туре                    | Audio                                                    |

| Interface               | I²C, SDA                                                 |

| Clock Rate              | 4.1MHz                                                   |

| Non-Volatile Memory     | -                                                        |

| On-Chip RAM             | -                                                        |

| Voltage - I/O           | -                                                        |

| Voltage - Core          | -                                                        |

| Operating Temperature   | 0°C ~ 40°C (TA)                                          |

| Mounting Type           | Surface Mount                                            |

| Package / Case          | 32-SMD Module                                            |

| Supplier Device Package | 32-SIP                                                   |

| Purchase URL            | https://www.e-xfl.com/product-detail/onsemi/sa3291a-e1-t |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Adaptive Noise Reduction** – The Ayre SA3291 adaptive noise reduction algorithm monitors noise levels independently in 128 individual bands and employs advanced psychoacoustic models to provide user comfort.

**Tinnitus Masking** – The Ayre SA3291 is equipped with a noise source that can be used to mask tinnitus. The noise can be shaped and attenuated and then summed into the audio path either before or after the volume control.

**In–situ Tone Generator** – The narrow–band noise stimulus feature can be used for in–situ validation of the hearing aid fitting. The frequency, level and duration of the stimuli are individually adjustable.

#### **Features**

- Wireless:

- Complete NFMI Wireless Transceiver of Bi-directional Transmission

- Channel Rate of 298 kbps

- Wireless Data Transfer

- ◆ CROS/BiCROS

- Relay Device Reference Design Available

- Advanced Research Algorithms:

- iSceneDetect Environmental Classification

- Automatic Adaptive Directional Microphones (ADM)

- ◆ FrontWave Directionality

- 128-band Adaptive Noise Reduction

- ◆ Adaptive Feedback Cancellation (AFC)

- Streaming Stereo and Mono Audio

- iLog 4.0 Datalogging

- Tinnitus Masking Noise Generator

- Evoke Acoustic Indicators

- Auto Telecoil with Programmable Delay

- 1, 2, 4, 6 or 8 Channel WDRC

- Feedback Path Measurement Tool

- AGC-O with Variable Threshold, Time Constants, and Optional Adaptive Release

- 16-band Graphic Equalizer

- Narrow-band Noise Stimulus

- SDA or I<sup>2</sup>C Programming

Other Key Features – Ayre SA3291 also supports the following features: FRONTWAVE® directional processing, built–in feedback path measurement, cross fading between audio paths for click–free program changes, 16–band graphic equalizer, 8 generic biquad filters (configurable as parametric or other filter types), programming speed nhancements, optional peak clipping, flexible ompression adjustments, direct interfaces to analog or digital volume control, rocker switch, direct audio input and telecoil. Ayre SA3291 also encompasses industry–leading security features to avoid cloning and software piracy.

- 8 Biquadratic Filters

- 4 Analog Inputs

- 16 kHz or 8 kHz Bandwidth

- 6 Fully Configurable Memories with Audible Memory Change Indicator

- 96 dB Input Dynamic Range with HRX Headroom Extension

- 28-bit Fingerprint Security System and Other Security Features to Protect Against Device Cloning and Software Policy

- High Fidelity Audio CODEC

- Soft acoustic Fade Between Memory Changes

- Drives Zero-bias 2-terminal Receivers

- Internal or External Digital Volume Control with Programmable Range

- Rocker Switch Support

- 20-bit Audio Processing

- thinSTAX<sup>®</sup> Packaging

- E1 RoHS Compliant Hybrid

# thinSTAX Packaging

Hybrid typical dimensions: 0.250 x 0.145 x 0.065 in. (6.35 x 3.68 x 1.65 mm)

Nominal dimensions of Hybrid only; height of solder bump not included.

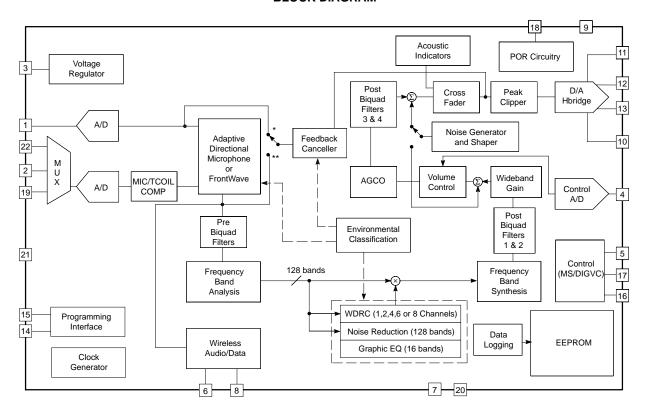

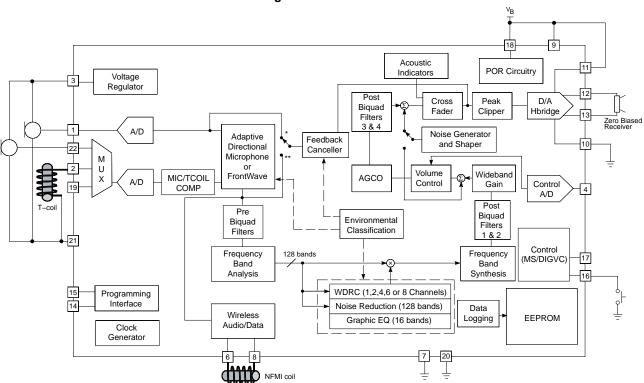

# **BLOCK DIAGRAM**

<sup>\*</sup> If Input Mode = 1 mic omni, mic + telecoil, mic + DAI \*\* If Input Mode = 2 mic omni, rear only, directional

Figure 1. Hybrid Block Diagram

# **SPECIFICATIONS**

**Table 1. ABSOLUTE MAXIMUM RATINGS**

| Parameter                          | Value      | Units |

|------------------------------------|------------|-------|

| Operating Temperature Range        | 0 to +40   | °C    |

| Storage Temperature Range          | -20 to +70 | °C    |

| Absolute Maximum Power Dissipation | 50         | mW    |

| Maximum Operating Supply Voltage   | 1.65       | VDC   |

| Absolute Maximum Supply Voltage    | 1.8        | VDC   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

**WARNING:** Electrostatic Sensitive Device – Do not open packages or handle except at a static–free workstation.

WARNING: Moisture Sensitive Device - RoHS Compliant; Level 4 MSL. Do not open packages except under controlled conditions.

Table 2. ELECTRICAL CHARACTERISTICS (Supply Voltage V<sub>B</sub> = NV<sub>B</sub> = 1.25 V; Temperature = 25°C)

| Parameter                        | Symbol               | Conditions                                                | Min   | Тур    | Max  | Units           |

|----------------------------------|----------------------|-----------------------------------------------------------|-------|--------|------|-----------------|

| Minimum Operating Supply Voltage | V <sub>BOFF</sub>    | Ramp down, audio path                                     | 0.93  | 0.95   | 0.97 | V               |

|                                  |                      | Ramp down, control logic                                  | 0.77  | 0.80   | 0.83 |                 |

|                                  | NV <sub>BOFF</sub>   | Transceiver Operation                                     | 0.93  | 0.965  | 1.0  |                 |

| Supply Voltage Turn On Threshold | V <sub>BON</sub>     | Ramp up, Zinc Air battery                                 | 1.06  | 1.10   | 1.16 | V               |

|                                  | NV <sub>BON</sub>    | Ramp up, Zinc Air battery                                 | 1.06  | 1.10   | 1.14 |                 |

| EEPROM Burn Cycles               | _                    | -                                                         | 100 k | _      | -    | cycles          |

| Flash-RAM Write/Erase Cycle      | _                    | -                                                         | 10 k  | 100 k  | -    | cycles          |

| Low Frequency System Limit       | -                    | DSP, Transceiver                                          | -     | 125    | -    | Hz              |

| High Frequency System Limit      | -                    | DSP                                                       | _     | -      | 16   | kHz             |

|                                  | _                    | Transceiver (-3 dB)                                       | -     | 7      | -    | -               |

| Total Harmonic Distortion        | THD                  | $V_{IN} = -40 \text{ dBV}$                                | -     | -      | 1    | %               |

| THD at Maximum Input             | THD <sub>M</sub>     | V <sub>IN</sub> = -15 dBV, HRX - ON                       | -     | -      | 3    | %               |

| Clock Frequency                  | <i>f</i> clk         | -                                                         | 3.78  | -      | 4.10 | MHz             |

| NFMI TRANSCEIVER                 | •                    |                                                           |       | •      |      |                 |

| Carrier Frequency                | <i>f</i> c           | -                                                         | -     | 10.597 | -    | MHz             |

| Modulation Scheme                | -                    | TDMA, CPFSK                                               | -     | -      | -    | -               |

| Supply Current in Sleep Mode     | I <sub>sleep</sub>   | -                                                         | -     | 2      | -    | μА              |

| Supply Current in Standby Mode   | I <sub>standby</sub> | -                                                         | 189   | 227    | 273  | μА              |

| Average Operating Current        | I <sub>AVE</sub>     | Bi-directional TDMA mode,<br>full chip operation          | -     | 3.2    | -    | mA              |

| Transmitter Antenna Coil Voltage | V <sub>TX</sub>      | AC Signal                                                 | -     | -      | 12   | V <sub>PP</sub> |

| REGULATOR                        | •                    |                                                           |       | •      | •    | •               |

| Regulator Voltage                | V <sub>REG</sub>     | -                                                         | 0.87  | 0.90   | 0.93 | V               |

| System PSRR                      | PSRR <sub>SYS</sub>  | 1 kHz, Input referred, HRX enabled                        | -     | 70     | -    | dB              |

| INPUT                            | •                    |                                                           |       | 1      |      |                 |

| Input Referred Noise             | IRN                  | Bandwidth 100 Hz – 8 kHz                                  | -     | -108   | -106 | dBV             |

| Input Impedance                  | Z <sub>IN</sub>      | 1 kHz                                                     | -     | 3      | -    | ΜΩ              |

| Anti-aliasing Filter Rejection   | _                    | $f = f_{CLK/2} - 8 \text{ kHz}, V_{IN} = -40 \text{ dBV}$ | -     | 80     | -    | dB              |

| Crosstalk                        | _                    | Between both A/D and Mux                                  | -     | 60     | -    | dB              |

| Maximum Input Level              | _                    | -                                                         | _     | -15    | -    | dBV             |

$\textbf{Table 2. ELECTRICAL CHARACTERISTICS} \ (Supply \ Voltage \ V_B = NV_B = 1.25 \ V; \ Temperature = 25^{\circ}C) \ (continued)$

| Parameter                     | Symbol              | Conditions                           | Min   | Тур   | Max   | Units |

|-------------------------------|---------------------|--------------------------------------|-------|-------|-------|-------|

| INPUT                         |                     |                                      | •     | •     | •     | •     |

| Analog Input Voltage Range    | V <sub>AN_IN</sub>  | $V_{IN1}, V_{IN2}, AI$               | 0     | _     | 800   | mV    |

|                               | V <sub>AN_TIN</sub> | T <sub>IN</sub>                      | -100  | _     | 800   |       |

| Input Dynamic Range           | -                   | HRX – ON Bandwidth<br>100 Hz – 8 kHz | -     | 95    | 96    | dB    |

| Audio Sampling Rate           | -                   | -                                    | 8     | -     | 48    | kHz   |

| OUTPUT                        | •                   |                                      |       |       |       |       |

| D/A Dynamic Range             | -                   | 100 Hz – 8 kHz                       | _     | 88    | _     | dB    |

| Output Impedance              | Z <sub>OUT</sub>    | _                                    | -     | 10    | 13    | Ω     |

| VOLUME CONTROL                | ·                   |                                      |       | •     | •     |       |

| Volume Control Resistance     | R <sub>VC</sub>     | Three-terminal connection            | 200   | _     | 1000  | kΩ    |

| Volume Control Range          | -                   | -                                    | -     | _     | 42    | dB    |

| PC_SDA INPUT                  | •                   |                                      |       |       |       |       |

| Logic 0 Voltage               | -                   | -                                    | 0     | _     | 0.3   | V     |

| Logic 1 Voltage               | -                   | -                                    | 1     | _     | 1.25  | V     |

| PC_SDA OUTPUT                 | ·                   |                                      |       |       |       |       |

| Stand-by Pull Up Current      | -                   | Creftrim = 6                         | 3     | 5     | 6.5   | μΑ    |

| Sync Pull Up Current          | -                   | Creftrim = 6                         | 748   | 880   | 1020  | μΑ    |

| Max Sync Pull Up Current      | -                   | Creftrim = 15                        | -     | 1380  | _     | μΑ    |

| Min Sync Pull Up Current      | -                   | Creftrim = 0                         | -     | 550   | -     | μΑ    |

| Logic 0 Current (Pull Down)   | -                   | Creftrim = 6                         | 374   | 440   | 506   | μΑ    |

| Logic 1 Current (Pull Up)     | -                   | Creftrim = 6                         | 374   | 440   | 506   | μΑ    |

| Synchronization Time          | T <sub>SYNC</sub>   | Baud = 0                             | 237   | 250   | 263   | μs    |

| (Synchronization Pulse Width) |                     | Baud = 1                             | 118   | 125   | 132   |       |

|                               |                     | Baud = 2                             | 59    | 62.5  | 66    |       |

|                               |                     | Baud = 3                             | 29.76 | 31.25 | 32.81 |       |

|                               |                     | Baud = 4                             | 14.88 | 15.63 | 16.41 |       |

|                               |                     | Baud = 5                             | 7.44  | 7.81  | 8.20  |       |

|                               |                     | Baud = 6                             | 3.72  | 3.91  | 4.10  |       |

|                               |                     | Baud = 7                             | 1.86  | 1.95  | 2.05  |       |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

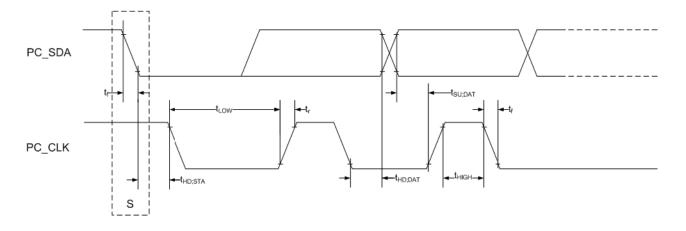

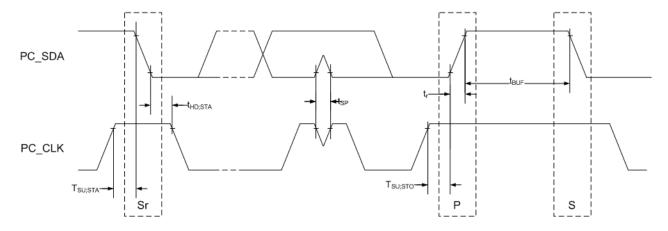

Table 3, I<sup>2</sup>C TIMING

|                                                                                                            |                     |                   | ard Mode           | Fast N                              | /lode             |       |

|------------------------------------------------------------------------------------------------------------|---------------------|-------------------|--------------------|-------------------------------------|-------------------|-------|

| Parameter                                                                                                  | Symbol              | Min               | Max                | Min                                 | Max               | Units |

| Clock Frequency                                                                                            | f <sub>PC_CLK</sub> | 0                 | 100                | 0                                   | 400               | kHz   |

| Hold time (repeated) START condition. After this period, the first clock pulse is generated.               | t <sub>HD;STA</sub> | 4.0               | -                  | 0.6                                 | -                 | μsec  |

| LOW Period of the PC_CLK Clock                                                                             | t <sub>LOW</sub>    | 4.7               | -                  | -                                   | -                 | μsec  |

| HIGH Period of the PC_CLK Clock                                                                            | t <sub>HIGH</sub>   | 4.0               | -                  | -                                   | -                 | μsec  |

| Set-up time for a repeated START condition                                                                 | t <sub>SU;STA</sub> | 4.7               | -                  | -                                   | -                 | μsec  |

| Data Hold Time:<br>for CBUS Compatible Masters<br>for I <sup>2</sup> C-bus Devices                         | <sup>t</sup> HD;DAT | 5.0<br>0 (Note 1) | -<br>3.45 (Note 2) | _<br>0 (Note 1)                     | -<br>0.9 (Note 2) | μsec  |

| Data set-up time                                                                                           | t <sub>SU;DAT</sub> | 250               | _                  | 100                                 | -                 | nsec  |

| Rise time of both PC_SDA and PC_CLK signals                                                                | t <sub>r</sub>      | -                 | 1000               | 20 + 0.1 C <sub>b</sub><br>(Note 4) | 300               | nsec  |

| Fall time of both PC_SDA and PC_CLK signals                                                                | t <sub>f</sub>      | -                 | 300                | 20 + 0.1 C <sub>b</sub><br>(Note 4) | 300               | nsec  |

| Set-up time for STOP condition                                                                             | t <sub>SU;STO</sub> | 4.0               | -                  | 0.6                                 | -                 | nsec  |

| Bus free time between a STOP and START condition                                                           | t <sub>BUF</sub>    | 4.7               | _                  | 1.3                                 | -                 | μsec  |

| Output fall time from V <sub>IHmin</sub> to V <sub>ILmax</sub> with a bus capacitance from 10 pF to 400 pF | t <sub>of</sub>     | _                 | 250                | 20 + 0.1 C <sub>b</sub><br>(Note 4) | 250               | nsec  |

| Pulse width of spikes which must be suppressed by the input filter                                         | t <sub>SP</sub>     | n/a               | n/a                | 0                                   | 50                | nsec  |

| Capacitive load for each bus line                                                                          | C <sub>b</sub>      | -                 | 400                | -                                   | 400               | pF    |

A device must internally provide a hold time of at least 300 ns for the PC\_SDA signal to bridge the undefined region of the falling edge of PC\_CLK.

The maximum t<sub>HD;DAT</sub> has only to be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the PC\_CLK signal.

A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement t<sub>SU;DAT</sub> P250ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the PC\_CLK signal. If such a device does stretch the LOW period of the PC\_CLK signal, it must output the next data bit to the PC\_SDA line t<sub>r</sub> max + t<sub>SU;DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard-mode I<sup>2</sup>C-bus specification) before the PC\_CLK line is released.

C<sub>b</sub> = total capacitance of one bus line in pF.

Figure 2. I<sup>2</sup>C Mode Timing

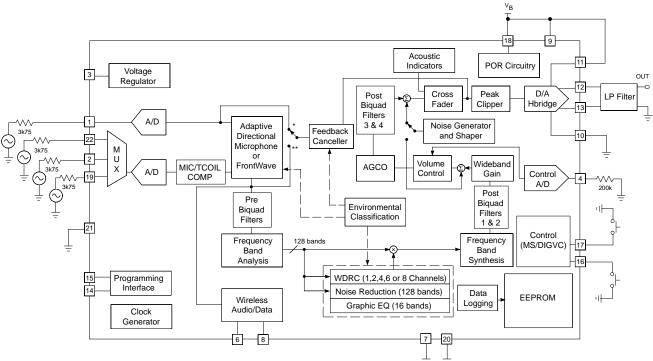

#### TYPICAL APPLICATIONS

\* If Input Mode = 1 mic omni, mic + telecoil, mic + DAI

\*\* If Input Mode = 2 mic omni, rear only, directional

Note: All resistors in ohms and all capacitors in farads, unless otherwise stated.

Figure 3. Test Circuit

<sup>\*</sup> If Input Mode = 1 mic omni, mic + telecoil, mic + DAI \*\* If Input Mode = 2 mic omni, rear only, directional

Note: All resistors in ohms and all capacitors in farads, unless otherwise stated.

Figure 4. Typical Application Circuit

#### SIGNAL PATH

The integrated NFMI transceiver is designed to provide many highly desirable features in a wireless hearing aid product. With minimal processing overhead, the transceiver and its built-in MAC and link control function provides networked mode support for 3 or more devices, unidirectional low latency stereo audio streaming and high-speed data transfer from one transmitter device to two hearing instruments. The use of NFMI technology avoids all the propagation problems that exist in an RF-based wireless system. While having a small wireless range typically limited to less than 60 cm, depending on the transmitter device, the NFMI system has good immunity to the human body blockage effect and it is not sensitive to RF interference. The very high Q-factor for its coil antenna ensures a very small operating system bandwidth in the radio front end.

There are two main audio input signal paths. The first path contains the front microphone and the second path contains the rear microphone, telecoil or direct audio input as selected by a programmable MUX. The front microphone input is intended as the main microphone audio input for single microphone applications.

In iSceneDetect, FrontWave, ADM or Automatic ADM operation, a multi-microphone signal is used to produce a directional hearing instrument response. The two audio inputs are buffered, sampled and converted into digital form using dual A/D converters. The digital outputs are converted into a 32 kHz or 16 kHz, 20-bit digital audio signal. Further IIR filter blocks process the front microphone and rear microphone signals. One biquad filter is used to match the rear microphone's gain to that of the front microphone. After

that, other filtering is used to provide an adjustable group delay to create the desired polar response pattern during the calibration process. In iSceneDetect, ADM and Automatic ADM, the two microphone inputs are combined in an adaptive way while in FrontWave operation the combination is static.

In the Telecoil mode gains are trimmed during Cal/Config process to compensate for microphone/telecoil mismatches.

The FrontWave block is followed by four cascaded biquad filters: *pre1*, *pre2*, *pre3* and *pre4*. These filters can be used for frequency response shaping before the signal goes through channel and adaptive processing.

The channel and adaptive processing consists of the following:

- Frequency band analysis

- 1, 2, 4, 6 or 8 channel WDRC

- 16 frequency shaping bands (spaced linearly at 500 Hz intervals, except for first and last bands)

- 128 frequency band adaptive noise reduction

- Frequency band synthesis

After the processing the signal goes through two more biquad filters, *post1* and *post2*, which are followed by the AGC–O block. The AGC–O block incorporates the Wideband Gain and the volume control (VC). There are also two more biquad filters, *post3* and *post4*, and the Peak Clipper. The last stage in the signal path is the D/A H–bridge.

White noise can be shaped, attenuated and then added into the signal path at two possible locations: before the VC (between the Wideband Gain and the VC) or after the VC (between post 4 and the Peak Clipper) as shown in Figure 1.

# **FUNCTIONAL BLOCK DESCRIPTION**

#### **Binaural Synchronization**

The binaural synchronization feature allows two hearing aids to wirelessly synchronize adjustments such as program modes or volume control.

#### **Binaural Telecoil**

The binaural telecoil wirelessly streams telecoil audio signals from one hearing aid to the other, enabling hearing aid users to hear phone calls in both ears.

In this mode, the user can also adjust the VC on the ear not using the telephone. If the hearing aids become disconnected by going out of range, in 94% of cases they will reconnect in less than a second.

# **Wireless Streaming**

Stereo audio signals can be streamed wirelessly from a relay device to hearing aids equipped with Ayre SA3291. A relay device can use Bluetooth or other far–field wireless technology to wirelessly connect with TVs, music players, mobile phones or other audio sources.

Streaming is primarily a one way mode, with the transmitter streaming audio or commands to all devices within its range. Streaming devices can operate across a greater distance due to the larger transmit antenna and greater transmit power.

A receiver must be configured in IDS to allow streaming audio or remote control commands to be received.

# **CROS/BiCROS**

To compensate for single sided deafness, AYRE SA3291 can be configured for use as a CROS/BiCROS device. It does this by transmitting audio from a microphone on a device on the completely deaf ear to the device on the aided or unaided ear over a wireless link.

# iSceneDetect 1.0 Environment Classification

The iSceneDetect feature, when enabled, will sense the environment and automatically control the enhancement algorithms without any user involvement. It will detect speech in quiet, speech in noise, wind, music, quiet and noise

environments and make the necessary adjustments to the parameters in the audio path, such as ADM, ANR, WDRC, FBC, in order to optimize the hearing aid settings for the specific environment.

iSceneDetect will gradually make the adjustments so the change in settings based on the environment is smooth and virtually unnoticeable. This feature will enable the hearing aid wearer to have an instrument which will work in any environment with a single "memory".

#### **EVOKE Advanced Acoustic Indicators**

Advanced acoustic indicators provide alerting sounds that are more complex, more pleasing and potentially more meaningful to the end user than the simple tones used on previous products. The feature is capable of providing pulsed, multi–frequency pure tones with smooth on and off transitions and also damped, multi–frequency tones that can simulate musical notes or chords.

A unique indicator sound can be assigned to each of the ten system events: memory select (A, B, C, D, E or F), low battery warning, digital VC movement and digital VC minimum/maximum. Each sound can consist of a number of either pure tones or damped tones but not both.

A pure tone sound can consist of up to four tones, each with a separate frequency, amplitude, duration and start time. Each frequency component is smoothly faded in and out with a fade time of 64 ms. The start time indicates the beginning of the fade in. The duration includes the initial fade—in period. By manipulating the frequencies, start times, durations and amplitudes various types of sounds can be obtained (e.g., various signalling tones in the public switched telephone network).

A damped tone sound can consist of up to six tones, each with a separate frequency, amplitude, duration, start time and decay time. Each frequency component starts with a sudden onset and then decays according to the specified time constant. This gives the audible impression of a chime or ring. By manipulating the frequencies, start times, durations, decays and amplitudes, various musical melodies can be obtained.

Acoustic indication can be used without the need to completely fade out the audio path. For example, the low-battery indicator can be played out and the user can still hear an attenuated version of the conversation.

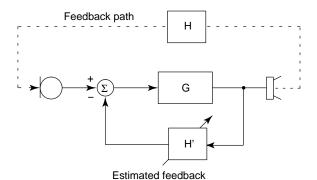

# **Adaptive Feedback Canceller**

The Adaptive Feedback Canceller (AFC) reduces acoustic feedback by forming an estimate of the hearing aid feedback signal and then subtracting this estimate from the hearing aid input. The forward path of the hearing aid is not affected. Unlike adaptive notch filter approaches, the Ayre SA3291's AFC does not reduce the hearing aid's gain. The AFC is based on a time–domain model of the feedback path.

The Ayre SA3291 third-generation AFC provides an increase in added stable gain and minimal artefacts for music and tonal input signals. As with previous products, the feedback canceller in the Ayre SA3291 provides completely

automatic operation. The feedback canceller can be activated in any front-end mode except for Telecoil-only or DAI-only mode.

When the AFC is enabled, it is highly recommended that you either have all channels with Squelch ON or all channels with Squelch OFF. If you choose to have all channels with Squelch ON then there is an additional requirement to have all Squelch thresholds above the microphone noise floor. If you require any assistance in determining what threshold levels to set, please contact the applications department at ON Semiconductor. Squelch ON/OFF does not incur any current penalty. When Squelch and AFC are both ON, the Squelch is limited to 1:2 expansion.

Figure 5. Adaptive Feedback Canceller (AFC)

Block Diagram

#### **Feedback Path Measurement Tool**

The Feedback Path Measurement Tool uses the onboard feedback cancellation algorithm and noise generator to measure the acoustic feedback path of the device. The noise generator is used to create an acoustic output signal from the hearing aid, some of which leaks back to the microphone via the feedback path. The feedback canceller algorithm automatically calculates the feedback path impulse response by analyzing the input and output signals. Following a suitable adaptation period, the feedback canceller coefficients can be read out of the device and used as an estimate of the feedback—path impulse response.

#### **Adaptive Noise Reduction**

The noise reduction algorithm is built upon a high resolution 128—band filter bank enabling precise removal of noise. The algorithm monitors the signal and noise activities in these bands, and imposes a carefully calculated attenuation gain independently in each of the 128 bands.

The noise reduction gain applied to a given band is determined by a combination of three factors:

- Signal-to-Noise Ratio (SNR)

- Masking threshold

- Dynamics of the SNR per band

The SNR in each band determines the maximum amount of attenuation to be applied to the band – the poorer the SNR, the greater the amount of attenuation. Simultaneously, in

each band, the masking threshold variations resulting from the energy in other adjacent bands is taken into account. Finally, the noise reduction gain is also adjusted to take advantage of the natural masking of 'noisy' bands by speech bands over time.

Based on this approach, only enough attenuation is applied to bring the energy in each 'noisy' band to just below the masking threshold. This prevents excessive amounts of attenuation from being applied and thereby reduces unwanted artifacts and audio distortion. The Noise Reduction algorithm efficiently removes a wide variety of types of noise, while retaining natural speech quality and level. The level of noise reduction (aggressiveness) is configurable to 3, 6, 9 and 12 dB of reduction.

### **Directional Microphones**

In any directional mode, the circuitry includes a fixed filter for compensating the sensitivity and frequency response differences between microphones. The filter parameters are adjusted during product calibration.

A dedicated biquad filter following the directional block has been allocated for low frequency equalization to compensate for the 6 dB/octave roll-off in frequency response that occurs in directional mode. The amount of low frequency equalization that is applied is programmable.

ON Semiconductor recommends using matched microphones. The maximum spacing between the front and rear microphones cannot exceed 20 mm (0.787 in).

# **Adaptive Directional Microphones (ADM)**

ON Semiconductor's Adaptive Directional Microphone algorithm is a two-microphone processing scheme for hearing aids. It is designed to automatically reduce the level of sound sources that originate from behind or the side of the hearing-aid wearer without affecting sounds from the front. The algorithm accomplishes this by adjusting the null in the microphone polar pattern to minimize the noise level at the output of the ADM. The discrimination between desired signal and noise is based entirely on the direction of arrival with respect to the hearing aid: sounds from the front hemisphere are passed unattenuated whereas sounds arriving from the rear hemisphere are reduced.

The angular location of the null in the microphone polar pattern is continuously variable over a range of 90 to 180 degrees where 0 degrees represents the front.

The location of the null in the microphone pattern is influenced by the nature of the acoustic signals (spectral content, direction of arrival) as well as the acoustical characteristics of the room. The ADM algorithm steers a single, broadband null to a location that minimizes the output noise power. If a specific noise signal has frequency components that are dominant, then these will have a larger influence on the null location than a weaker signal at a different location. In addition, the position of the null is affected by acoustic reflections. The presence of an acoustic reflection may cause a noise source to appear as if it originates at a location other than the true location. In this

case, the ADM algorithm chooses a compromise null location that minimizes the level of noise at the ADM output.

# **Automatic Adaptive Directional Microphones**

When Automatic ADM mode is selected, the adaptive directional microphone remains enabled as long as the ambient sound level is above a specific threshold and the directional microphone has not converged to an omni–directional polar pattern. On the other hand, if the ambient sound level is below a specific threshold, or if the directional microphone has converged to an omni–directional polar pattern, then the algorithm will switch to single microphone, omni–directional state to reduce current consumption. While in this omni–directional state, the algorithm will periodically check for conditions warranting the enabling of the adaptive directional microphone.

#### FrontWave Directionality

The FrontWave block provides the resources necessary to implement directional microphone processing. The block accepts inputs from both a front and rear microphone and provides a synthesized directional microphone signal as its output. The directional microphone output is obtained by delaying the rear microphone signal and subtracting it from the front microphone signal. Various microphone response patterns can be obtained by adjusting the time delay.

### In-Situ Datalogging - iLog 4.0

The Ayre SA3291 has a datalogging function that records information every 4 s to 60 minutes (programmable) about the state of the hearing aid and its environment to non–volatile memory. The function can be enabled with the ARK software and information collection will begin the next time the hybrid is powered up. This information is recorded over time and can be downloaded for analysis.

The following parameters are sampled:

- Battery level

- Volume control setting

- Program memory selection

- Environment

- Ambient sound level

- Length of time the hearing aid was powered on

- Wireless audio and phone streaming

The information is recorded using two methods in parallel:

- Short–term method a circular buffer is serially filled with entries that record the state of the first five of the above variables at the configured time interval.

- Long-term method increments a counter based on the memory state at the same time interval as that of the short-term method. Based on the value stored in the counter, length of time the hearing aid was powered on can be calculated.

There are 750 log entries plus 6 memory select counters which are all protected using a checksum verification. A new log entry is made whenever there is a change in memory state, VC, or battery level state. A new log entry can also be optionally made when the environmental sound level changes more than the programmed threshold, thus it is possible to log only significantly large changes in the environmental level, or not log them at all.

The ARK software iLog graph displays the iLog data graphically in a way that can be interpreted to counsel the user and fine tune the fitting. This iLog graph can be easily incorporated into other applications or the underlying data can be accessed to be used in a custom display of the information.

#### **Tinnitus Treatment**

The Ayre SA3291 has an internal white noise generator that can be used for Tinnitus Treatment. The noise can be attenuated to a level that will either mask or draw attenuation away from the user's tinnitus. The noise can also be shaped using low–pass and/or high–pass filters with adjustable slopes and corner frequencies.

As shown in Figure 1, the Tinnitus Treatment noise can be injected into the signal path either before or after the VC or it can be disabled. If the noise is injected before the VC then the level of the noise will change along with the rest of the audio through the device when the VC is adjusted. If the noise is injected after the VC then it is not affected by VC changes.

The Tinnitus Treatment noise can be used on its own without the main audio path in a very low power mode by selecting the Tinnitus Treatment noise only. This is beneficial either when amplification is not needed at all by a user or if the user would benefit from having the noise supplied to them during times when they do not need acoustic cues but their sub—conscious is still active, such as when they are asleep.

The ARK software has a Tinnitus Treatment tool that can be used to explore the noise shaping options of this feature. This tool can also be easily incorporated into another software application.

#### Narrow-band Noise Stimulus

The Ayre SA3291 is capable of producing Narrow-band Noise Stimuli that can be used for in situ audiometry. Each narrow-band noise is centred on an audiometric frequency. The duration of the stimuli is adjustable and the level of the stimuli are individually adjustable.

#### A/D and D/A Converters

The system's two A/D converters are second order sigma-delta modulators operating at a 2.048 MHz sample rate. The system's two audio inputs are pre-conditioned with antialias filtering and programmable gain pre-amplifiers. These analog outputs are over-sampled and modulated to produce two, 1-bit Pulse Density Modulated (PDM) data streams. The digital PDM data is then

decimated down to Pulse–Code Modulated (PCM) digital words at the system sampling rate of 32 kHz.

The D/A is comprised of a digital, third order sigma—delta modulator and an H-bridge. The modulator accepts PCM audio data from the DSP path and converts it into a 64-times or 128-times over-sampled, 1-bit PDM data stream, which is then supplied to the H-bridge. The H-bridge is a specialized CMOS output driver used to convert the 1-bit data stream into a low-impedance, differential output voltage waveform suitable for driving zero-biased hearing aid receivers.

# **HRX Head Room Expander**

The Ayre SA3291 has an enhanced Head Room Expander (HRX) circuit that increases the input dynamic range of the Ayre SA3291 without any audible artifacts. This is accomplished by dynamically adjusting the pre–amplifier's gain and the post–A/D attenuation depending on the input level.

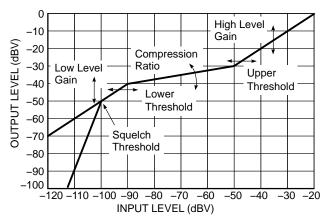

#### **Channel Processing**

Figure 6 represents the I/O characteristic of independent AGC channel processing. The I/O curve can be divided into the following main regions:

- Low input level expansion (squelch) region

- Low input level linear region

- Compression region

- High input level linear region (return to linear)

Figure 6. Independent Channel I/O Curve Flexibility

The I/O characteristic of the channel processing can be adjusted in the following ways:

- Squelch threshold (SQUELCHTH)

- Low level gain (LLGAIN)

- Lower threshold (LTH)

- High level gain (HLGAIN)

- Upper threshold (UTH)

- Compression ratio (CR)

To ensure that the I/O characteristics are continuous, it is necessary to limit adjustment to a maximum of four of the last five parameters. During Parameter Map creation, it is necessary to select four parameters as user adjustable, or fixed, and to allow one parameter to be calculated.

The squelch region within each channel implements a low level noise reduction scheme (1:2 or 1:3 expansion ratio) for listener comfort. This scheme operates in quiet listening environments (programmable threshold) to reduce the gain at very low levels. When the Squelch and AFC are both enabled it is highly recommended that the Squelch be turned on in all channels and that the Squelch thresholds be set above the microphone noise floor (see Adaptive Feedback Canceller).

The number of compression channels is programmable in ARKonline<sup>®</sup> and can be 1, 2, 4, 6 or 8.

#### **Telecoil Path**

The telecoil input is calibrated during the Cal/Config process. To compensate for the telecoil/microphone frequency response mismatch, a first order filter with 500 Hz corner frequency is implemented. Through ARKonline, it is possible to implement a telecoil compensation filter with an adjustable corner frequency. To accommodate for the gain mismatch, the telecoil gain is adjusted to match the microphone gain at 500 Hz or 1 kHz (default) and is selectable in ARKonline.

There is also a telecoil gain adjustment parameter that can be enabled in ARKonline and set in IDS, enabling manual adjustment of the telecoil gain compensation.

# **Automatic Telecoil**

The Ayre SA3291 is equipped with an automatic telecoil feature, which causes the hybrid to switch to a specific memory upon the closing of a switch connected to MS2. This feature is useful when MS2 is connected to a switch, such as a reed switch, that is open or closed depending on the presence of a static magnetic field. Memory D can be programmed to be the telecoil or mic+telecoil memory so that, when a telephone handset is brought close to such a switch, its static magnetic field closes the switch and causes the hybrid to change to memory D. However, it is possible that the hearing aid wearer may move his or her head away from the telephone handset momentarily, in which case it is undesirable to immediately change out of telecoil mode and then back in moments later.

The Ayre SA3291 has a debounce circuit that prevents this needless switching. The debounce circuit delays the device from switching out of memory D when MS2 is configured as a static switch in 'D–only' mode. The debounce time is programmable to be 1.5, 3.5 or 5.5 seconds after the switch opens (i.e., the handset is moved away from the hearing instrument) or this feature can be disabled.

#### **DAI Path**

The DAI input can be adjusted using a first order filter with a variable corner frequency similar to the telecoil compensation filter. Through ARKonline, it is possible to implement this DAI filter to set either a static or adjustable corner frequency.

The Mic plus DAI mode mixes the Mic1 and DAI signals. The Mic1 input signal is attenuated by 0, -6 or -12 dB before being added to the DAI input signal. The DAI input also has gain adjustment in 1 dB steps to assist in matching it to the Mic1 input level.

# **Graphic Equalizer**

The Ayre SA3291 has a 16-band graphic equalizer. The bands are spaced linearly at 500 Hz intervals, except for the first and the last band, and each one provides up to 24 dB of gain adjustment in 1 dB increments.

# **Biquad Filters**

Additional frequency shaping can be achieved by configuring generic biquad filters. The transfer function for each of the biquad filters is as follows:

$$H(z) = \frac{b0 + b1 \times z^{-1} + b2 \times z^{-2}}{1 + a1 \times z^{-1} + a2 \times z^{-2}}$$

Note that the a0 coefficient is hard—wired to always be '1'. The coefficients are each 16 bits in length and include one sign bit, one bit to the left of the decimal point, and 14 bits to the right of the decimal point. Thus, before quantization, the floating—point coefficients must be in the range  $-2.0 \le x < 2.0$  and quantized with the function:

round

$$(x \times 2^{14})$$

After designing a filter, the quantized coefficients can be entered into the PreBiquads or PostBiquads tab in the Interactive Data Sheet. The coefficients b0, b1, b2, a1, and a2 are as defined in the transfer function above. The parameters meta0 and meta1 do not have any effect on the signal processing, but can be used to store additional information related to the associated biquad.

The underlying code in the product components automatically checks all of the filters in the system for stability (i.e., the poles have to be within the unit circle) before updating the graphs on the screen or programming the coefficients into the hybrid. If the Interactive Data Sheet receives an exception from the underlying stability checking code, it automatically disables the biquad being modified and display a warning message. When the filter is made stable again, it can be re—enabled.

Also note that in some configurations, some of these filters may be used by the product component for microphone/telecoil compensation, low-frequency EQ, etc. If this is the case, the coefficients entered by the user into IDS are ignored and the filter designed by the software is programmed instead.

# **Rocker Switch**

The Ayre SA3291 is equipped with a rocker switch feature that can perform both VC adjustments or an audio memory switch.

There are 3 modes of operation:

- Digital VC

- Momentary Memory Select

- Mixed Mode

In Mixed Mode, the switches behaviour is configurable to be set to that a short or long press of the switch will invoke either a memory or VC change (i.e., a short press is a memory select, a long press is a VC change).

There is a programmable threshold that can be used to set the timing behaviour.

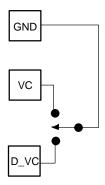

#### **Volume Control**

The VC can be either external (digital VC) or programmable. When using a Digital Volume Control (DVC) with the Ayre SA3291, the switch should be connected to the VC and D\_VC pins with momentary switches connected to each. Closure of the switch to the VC pin indicates a gain increase while closure to the D\_VC pin indicates a gain decrease. Figure 7 shows how to wire the DVC to SA3291.

A toggle switch can be used as a DVC, momentarily connecting the VC to either Vreg or GND. By connecting the VC to Vreg, the volume will be increased one step, and by connecting the VC to GND, the volume will be decreased one step.

The following parameters can be programmed into the hybrid to specify the DVC functionality:

- DVC enable or disable

- Volume up/down step size of 1 dB, 2 dB, 3 dB or 4 dB

- Volume up/down beep frequency and volume

- DVC range between 0 dB and 48 dB in 1 dB steps

- Default DVC value when the hybrid is powered up

- Volume up/down beep enable

- Max/Min beep enable

- Max/Min beep frequency & volume

If the Max/Min beep is enabled then when the volume has been incremented to the maximum value of the specified DVC range the device will play two beeps to indicate that it cannot increase the volume any more. The same is true for decrementing the volume and reaching the minimum value of the DVC range.

Figure 7. Wiring for Digital Volume Control

#### **Memory Select Switches**

One or two, two-pole Memory Select (MS) switches can be used with the Ayre SA3291. This enables users tremendous flexibility in switching between configurations. These switches may be either momentary or static and are configurable to be either pull-up or pull-down through the settings tab in IDS.

Up to six program modes can be configured on the Ayre SA3291. Memory A must always be valid. All memory select options are selectable via the settings tab in IDS.

### **Momentary Switch on MS**

This mode uses a single momentary switch on MS (Pin 17) to change program modes. Using this mode causes the part to start in memory A, and whenever the button is pressed, the next valid memory is loaded. When the user is in the last valid memory, a button press causes memory A to be loaded.

This mode is set by programming the 'MSSMode' parameter to 'Momentary' and 'Donly' to 'disabled'.

# **Example:**

If 6 valid program modes: ABCDEFABCDEF...

If 5 valid program modes: ABCDEABCDE...

If 4 valid program modes: ABCDABCDA...

If 3 valid program modes: ABCABCA...

If 2 valid program modes: ABABA...

If 1 valid program mode: AAA...

# Momentary Switch on MS, Static Switch on MS2 (Jump to Last Memory)

This mode uses a static switch on MS2 (Pin 16) and a momentary switch on MS (Pin 17) to change program modes. If the static switch is OPEN, the part starts in memory A and behaves like momentary, with the exception that memory D is not used. If the static switch on MS2 is set to HIGH, the part automatically jumps to memory D (occurs on start—up or during normal operation). In this setup, the momentary switch's state is ignored, preventing memory select beeps from occurring. When MS2 is set to OPEN, the part loads in the last select memory.

This mode is set by programming the 'MSSMode' parameter to 'Momentary' and 'Donly' to 'enabled'.

# **Example:**

If MS2 = OPEN and there are 6 valid program modes: ABCEFABCEF...

If MS2 = OPEN and there are 5 valid program modes: ABCEABCE...

If MS2 = OPEN and there are 4 valid program modes: ABCABCA...

If MS2 = OPEN and there are 3 valid program modes: ABABA...

If MS2 = HIGH: D...

Table 4. DYNAMIC EXAMPLE WITH FOUR VALID PROGRAM MODES (T = momentary switch is toggled; 0 = OPEN; 1 = HIGH)

| MS2    | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

|--------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| MS     | 0 | Т | Т | 0 | Т | Т | 0 | Т | Т | 0 | 0 | Т | Т | Т | Т | Т |

| Memory | Α | В | С | D | D | D | С | Α | В | D | В | С | Α | В | С | Α |

#### Static Switch on MS and MS2

This mode uses two static switches to change program modes. Table 5 describes which memory is selected depending on the state of the switches.

In this mode, it is possible to jump from any memory to any other memory simply by changing the state of both switches. If both switches are changed simultaneously, then the transition is smooth. Otherwise, if one switch is changed and then the other, the part transitions to an intermediate memory before reaching the final memory. The part starts in whatever memory the switches are selecting. If a memory is invalid, the part defaults to memory A.

This mode is set by programming the 'MSSMode' parameter to 'static' and 'Donly' to 'disabled'.

Table 5. MEMORY SELECTED IN STATIC SWITCH ON MS and MS2 MODE; Internal Resistors Set to Pull Down (Example with Four Valid Program Modes)

| MS   | MS2  | Memory                    |

|------|------|---------------------------|

| OPEN | OPEN | А                         |

| HIGH | OPEN | B (if valid, otherwise A) |

| OPEN | HIGH | C (if valid, otherwise A) |

| HIGH | HIGH | D (if valid, otherwise A) |

# Static Switch on MS, Static Switch on MS2 (Jump to Last Memory)

This mode uses two static switches to change program modes. Unlike in the previous example, this mode will switch to the last valid memory when the static switch on MS2 is HIGH. This means that this mode will only use a maximum of three program modes (even if four valid program modes are programmed). Table 6 describes which memory is selected depending on the state of the switches.

This mode is set by programming the 'MSSMode' parameter to 'static' and 'Donly' to 'enabled'.

Table 6. MEMORY SELECTED IN STATIC SWITCH ON MS, Static Switch on MS2 (Jump to Last Memory) Mode; Internal Resistors Set to Pull Down

| MS   | MS2  | Memory                    |

|------|------|---------------------------|

| OPEN | OPEN | А                         |

| HIGH | OPEN | B (if valid, otherwise A) |

| OPEN | HIGH | D                         |

| HIGH | HIGH | D                         |

In this mode, it is possible to jump from any memory to any other memory simply by changing the state of both switches. If both switches are changed simultaneously, then the transition is smooth. Otherwise, if one switch is changed and then the other, the part transitions to an intermediate memory before reaching the final memory.

When MS2 is set HIGH, the state of the switch on MS is ignored. This prevents memory select beeps from occurring if switching MS when MS2 is HIGH. The part starts in whatever memory the switches are selecting. If a memory is invalid, the part defaults to memory A.

# AGC-O and Peak Clipper

The output compression-limiting block (AGC-O) is an output limiting circuit whose compression ratio is fixed at ∞: 1. The threshold level is programmable. The AGC-O module has programmable attack and release time constants.

The AGC-O on the Ayre SA3291 has optional adaptive release functionality. When this function is enabled, the release time varies depending on the environment. In general terms, the release time becomes faster in environments where the average level is well below the threshold and only brief intermittent transients exceed the threshold.

Conversely, in environments where the average level is close to the AGC–O threshold, the release time applied to portions of the signal exceeding the threshold is longer. The result is an effective low distortion output limiter that clamps down very quickly on momentary transients but reacts more smoothly in loud environments to minimize compression pumping artifacts. The programmed release time is the longest release time applied, while the fastest release time is 16 times faster. For example, if a release time of 128 ms is selected, the fastest release time applied by the AGC–O block is 8 ms.

The Ayre SA3291 also includes the Peak Clipper block for added flexibility.

# **Memory Switch Fader**

To minimize potential loud transients when switching between program modes, the Ayre SA3291 uses a memory switch fader block. When the memory is changed, the audio signal is faded out, followed by the memory select acoustic indicators (if enabled), and after switching to the next memory, the audio signal is faded back in. The memory switch fader is also used when turning the Tone Generator on or off, and during SDA programming.

# **Power Management**

Ayre SA3291 has three user–selectable power management schemes to ensure the hearing aid turns off gracefully at the end of battery life. Shallow reset, Deep reset and Advanced Reset mode. It also contains a programmable power on reset delay function.

#### **Power On Reset Delay**

The programmable POR delay controls the amount of time between power being connected to the hybrid and the audio output being enabled. This gives the user time to properly insert the hearing aid before the audio starts, avoiding the temporary feedback that can occur while the device is being inserted. During the delay period, momentary button presses are ignored.

NOTE: The values set in IDS are relative values from 0 to 11 seconds; not absolute. The POR delay is relative to the configuration loaded on the WOLVERINE platform.

# **Power Management Functionality**

As the voltage on the hearing aid battery decreases, an audible warning is given to the user indicating the battery life is low. In addition to this audible warning, the hearing aid takes other steps to ensure proper operation given the weak supply. The exact hearing aid behaviour in low supply conditions depends on the selected POR mode. The hearing aid has three POR modes:

- Shallow Reset Mode

- Deep Reset Mode

- · Advanced Mode

#### **Shallow Reset Mode**

In Shallow Reset mode, the hearing aid will operate normally when the battery is above 0.95 V. Once the supply voltage drops below 0.95 V the audio will be muted and remain in that state until the supply voltage rises above 1.1 V. Once the supply voltage drops below the control logic ramp down voltage, the device will undergo a hardware reset. At this point, the device will remain off until the supply voltage returns to 1.1 V. When the supply voltage is below the control logic voltage, but above 0.6 V and rises above the 1.1 V turn on threshold, the device will activate its output and operate from the memory that was active prior to reset. If the supply voltage drops below 0.6 V, and rises above the 1.1 V turn on threshold, the device will reinitialize, activate its output and operate from memory A.

# **Deep Reset Mode**

In Deep Reset mode, the hearing aid will operate normally when the battery is above 0.95 V. Once the supply voltage drops below 0.95 V the audio will be muted. The device remains in this state until the supply voltage drops below the hardware reset voltage of 0.6 V. When this occurs, the device will load memory A and operate normally after the supply voltage goes above 1.1 V.

# **Advanced Reset Mode**

Advanced Reset Mode on Ayre SA3291 is a more sophisticated power management scheme than shallow and deep reset modes. This mode attempts to maximize the device's usable battery life by reducing the gain to stabilize the supply based on the instantaneous and average supply voltage levels. Instantaneous supply fluctuations below

0.95 V can trigger up to two 3 dB, instantaneous gain reductions. Average supply drops below 0.95 V can trigger up to eighteen, 1 dB average gain reductions.

While operating with no instantaneous gain reductions, an instantaneous supply voltage fluctuation below 0.95 V will trigger an immediate 3 dB gain reduction. A waiting period of 30 seconds is in place after the first instantaneous gain reduction. Only after the waiting period has elapsed will an instantaneous supply voltage fluctuation trigger the second 3 dB gain reduction. While an instantaneous gain reduction is being applied, the instantaneous supply voltage level will be checked every 30 seconds and a 3 dB gain reduction removed should the level be above a certain threshold.

Should the average supply voltage drop below 0.95 V, the device will begin to reduce the gain by 1 dB every 10 seconds until either the average supply voltage rises above 0.95 V or all 18 average gain reductions have been applied, at which point the audio path will be muted. If the average supply voltage returns to a level above 1.1 V, the audio path will first be un—muted, if required. The gain will then be increased by 1 dB every 10 seconds until either the average supply voltage drops below 1.1 V, or all average gain reductions have been removed. No action is taken while the average supply voltage resides between 0.95 V and 1.1 V.

NOTE: Instantaneous and average gain reductions are adjusted independently.

When the instantaneous voltage falls below the hardware shutdown voltage, the device will undergo a hardware reset. When it turns back on because the voltage has risen above the turn—on threshold, it will behave the same as it would in shallow reset mode.

# **Low Battery Notification**

Notification of the low battery condition via an acoustic indicator is optionally performed when the battery voltage drops below a configurable low battery notification threshold. The low battery indicator is repeated every five minutes until the device shuts down.

### **Software and Security**

The Ayre SA3291 incorporates the following security features to protect the device from cloning and against software piracy:

- DLL protection by password prevents a third party from using IDS to reconfigure parts.

- Hybrid authentication by 128-bit fingerprint to identify parts in application software prevents a third party from cloning a device's EEPROM because the fingerprint cannot be overwritten. Special functions can be used in fitting software to reject parts that do not match the expected fingerprint. This would prevent the piracy of fitting software.

- DLL to hybrid pairing by using a software key in ARK

to match product libraries with client software a part

can be 'locked' at manufacturing time so that it only

communicates with the library it was programmed with.

This prevents a third party from potentially upgrading a device with a different library in IDS or other application software.

Full software support is provided for every stage of development from design to manufacturing to fitting. For details, refer to the Getting Started with the ARK Software information note.

#### SDA and I<sup>2</sup>C Communication

The Ayre SA3291 can be programmed using the SDA or I<sup>2</sup>C protocol. During parameter changes, the main audio signal path of the hybrid is temporarily muted using the memory switch fader to avoid the generation of disturbing audio transients. Once the changes are complete, the main audio path is reactivated. Any changes made during programming are lost at power—off unless they are explicitly burned to EEPROM memory.

Improvements have been made to the ARK software for the Ayre SA3291 resulting in increased communication speed. Certain parameters in ARKonline can be selected to reduce the number of pages that need to be read out.

In SDA mode, the Ayre SA3291 is programmed via the SDA pin using industry standard programming boxes. I<sup>2</sup>C mode is a two wire interface which uses the SDA pin for bidirectional data and CLK as the interface clock input. I<sup>2</sup>C programming support is available on the HiPro (serial or

USB versions) and ON Semiconductor's DSP Programmer 3.0.

# **Power Supply Considerations**

The Ayre SA3291 was designed to accommodate high power applications. AC ripple on the supply can cause instantaneous reduction of the battery's voltage, potentially disrupting the circuit's function. The Ayre SA3291 hybrids have a separate power supply and ground connections for the output stage. This enables hearing instrument designers to accommodate external RC filters to minimize any AC ripple from the supply line. Reducing this AC ripple greatly improves the stability of the circuit and prevents unwanted reset of the circuit caused by spikes on the supply line.

For more information on properly designing a filter to reduce supply ripple, refer to the Using DSP Hybrids in High Power Applications Initial Design Tips information note (AND9028).

#### **Material Handling**

It is recommended that any exposed material be dry baked for a minimum of 37 hours ±1 hour at 90°C ±5°C before storage again. For general handling specifications, please refer to the 'How to Store, Reflow and Solder ON Semiconductor Hybrids' application note (AND8493).

#### **ORDERING INFORMATION**

| Device       | Package       | Shipping <sup>†</sup>   |

|--------------|---------------|-------------------------|

| SA3291A-E1   | 32 Pad Hybrid | 25 Units / Bubble Pack  |

| SA3291A-E1-T | 32 Pad Hybrid | 250 Units / Tape & Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# **Hybrid Jig Ordering Information**

To order a Hybrid Jig Kit for Ayre SA3291 contact your Sales Account Manager or FAE and use part number SA3410GEVK. Kit includes:

- Two Ayre SA3291 Hybrid Jig Evaluation Boards

- Two NFMI Antennas

- Two Ayre SA3291 Hybrids

- Two Programming Cables

To order a Hybrid Jig Board for Ayre SA3291 contact your Sales Account Manager or FAE and use part number SA3410GEVB.

# **PAD LOCATIONS**

**Table 7. PAD POSITION AND DIMENSIONS**

|         | Pad Po | osition | Pad Dimensions |            |  |

|---------|--------|---------|----------------|------------|--|

| Pad No. | Х      | Y       | Xdim (mil)     | Ydim (mil) |  |

| 1       | 0      | 0       | 20             | 24         |  |

| 2       | -27.5  | 0       | 20             | 24         |  |

| 3       | -55    | 0       | 20             | 24         |  |

| 4       | -82.5  | 0       | 20             | 24         |  |

| 5       | -110   | 0       | 20             | 24         |  |

| 6       | -137.5 | 0       | 20             | 24         |  |

| 7       | -165   | 0       | 20             | 24         |  |

| 8       | -192.5 | 0       | 20             | 24         |  |

| 9       | -220   | 0       | 20             | 24         |  |

| 10      | -220   | 36      | 20             | 24         |  |

| 11      | -220   | 72      | 20             | 24         |  |

| 12      | -220   | 108     | 20             | 24         |  |

| 13      | -192.5 | 108     | 20             | 24         |  |

| 14      | -165   | 108     | 20             | 24         |  |

| 15      | -137.5 | 108     | 20             | 24         |  |

| 16      | -110   | 108     | 20             | 24         |  |

| 17      | -82.5  | 108     | 20             | 24         |  |

| 18      | -55    | 108     | 20             | 24         |  |

| 19      | -27.5  | 108     | 20             | 24         |  |

| 20      | 0      | 108     | 20             | 24         |  |

| 21      | -13.75 | 72      | 47.5           | 24         |  |

| 22      | 0      | 36      | 20             | 24         |  |

| 23      | -82.5  | 72      | 20             | 24         |  |

| 24      | -110   | 72      | 20             | 24         |  |

| 25      | -137.5 | 72      | 20             | 24         |  |

| 26      | -165   | 72      | 20             | 24         |  |

| 27      | -32.5  | 36      | 12             | 12         |  |

| 28      | -60    | 36      | 12             | 12         |  |

| 29      | -102   | 36      | 12             | 12         |  |

| 30      | -129.5 | 36      | 12             | 12         |  |

| 31      | -157   | 36      | 12             | 12         |  |

| 32      | -184.5 | 36      | 12             | 12         |  |

**Table 7. PAD POSITION AND DIMENSIONS**

| Pad No. | Х      | Y     | Xdim (mm) | Ydim (mm) |

|---------|--------|-------|-----------|-----------|

| 1       | 0      | 0     | 0.51      | 0.610     |

| 2       | -0.699 | 0     | 0.51      | 0.610     |

| 3       | -1.397 | 0     | 0.51      | 0.610     |

| 4       | -2.096 | 0     | 0.51      | 0.610     |

| 5       | -2.794 | 0     | 0.51      | 0.610     |

| 6       | -3.493 | 0     | 0.51      | 0.610     |

| 7       | -4.191 | 0     | 0.51      | 0.610     |

| 8       | -4.890 | 0     | 0.51      | 0.610     |

| 9       | -5.588 | 0     | 0.51      | 0.610     |

| 10      | -5.588 | 0.914 | 0.51      | 0.610     |

| 11      | -5.588 | 1.829 | 0.51      | 0.610     |

| 12      | -5.588 | 2.743 | 0.51      | 0.610     |

| 13      | -4.890 | 2.743 | 0.51      | 0.610     |

| 14      | -4.191 | 2.743 | 0.51      | 0.610     |

| 15      | -3.493 | 2.743 | 0.51      | 0.610     |

| 16      | -2.794 | 2.743 | 0.51      | 0.610     |

| 17      | -2.096 | 2.743 | 0.51      | 0.610     |

| 18      | -1.397 | 2.743 | 0.51      | 0.610     |

| 19      | -0.699 | 2.743 | 0.51      | 0.610     |

| 20      | 0      | 2.743 | 0.51      | 0.610     |

| 21      | -0.349 | 1.829 | 1.207     | 0.610     |

| 22      | 0      | 0.914 | 0.51      | 0.610     |

| 23      | -2.096 | 1.829 | 0.51      | 0.610     |

| 24      | -2.794 | 1.829 | 0.51      | 0.610     |

| 25      | -3.493 | 1.829 | 0.51      | 0.610     |

| 26      | -4.191 | 1.829 | 0.51      | 0.610     |

| 27      | -0.826 | 0.914 | 0.305     | 0.305     |

| 28      | -1.524 | 0.914 | 0.305     | 0.305     |

| 29      | -2.591 | 0.914 | 0.305     | 0.305     |

| 30      | -3.289 | 0.914 | 0.305     | 0.305     |

| 31      | -3.988 | 0.914 | 0.305     | 0.305     |

| 32      | -4.686 | 0.914 | 0.305     | 0.305     |

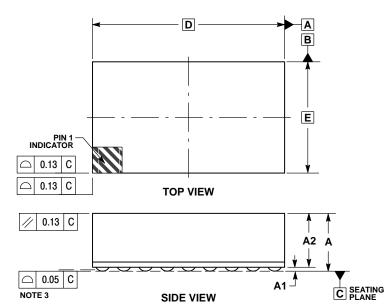

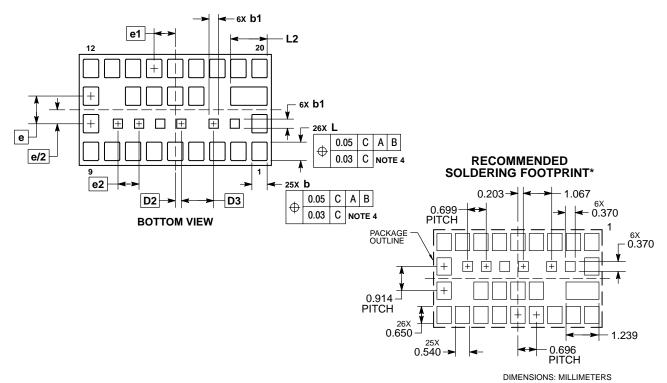

#### PACKAGE DIMENSIONS

# SIP32 6.35x3.68 CASE 127DW **ISSUE O**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME DIMENSIONING AND TOLERANGING FELLOW

Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

COPLANARITY APPLIES TO SPHERICAL

CROWNS OF SOLDER BUMPS.

- CROWNS OF SOLDER BUMPS.

DIMENSIONS b, b1, L AND L2 ARE MEASURED

AT THE MAXIMUM BUMP DIMENSION PARALLEL

TO DATUM C. THE POSITIONAL TOLERANCE

APPLIES TO ALL OF THE SOLDER BUMPS.

|     | MILLIMETERS |       |  |  |  |  |

|-----|-------------|-------|--|--|--|--|

| DIM | MIN         | MAX   |  |  |  |  |

| Α   |             | 1.960 |  |  |  |  |

| A1  | 0.076       | 0.180 |  |  |  |  |

| A2  |             | 1.780 |  |  |  |  |

| b   | 0.478       | 0.538 |  |  |  |  |

| b1  | 0.275       | 0.335 |  |  |  |  |

| D   | 6.350 BSC   |       |  |  |  |  |

| D2  | 0.203       | BSC   |  |  |  |  |

| D3  | 1.067       | BSC   |  |  |  |  |

| E   | 3.683       | BSC   |  |  |  |  |

| е   | 0.914       | BSC   |  |  |  |  |

| e1  | 0.696 BSC   |       |  |  |  |  |

| e2  | 0.699 BSC   |       |  |  |  |  |

| L   | 0.580       | 0.640 |  |  |  |  |

| 12  | 1.177       | 1 237 |  |  |  |  |

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

AYRE, iSceneDetect, iLog, VOYAGEUR, HRX, WOLVERINE and EVOKE are trademarks of Semiconductor Components Industries, LLC. thinSTAX, FRONTWAVE, PARAGON and ARKonline are registered trademarks of Semiconductor Components Industries, LLC. Bluetooth is a registered trademark of Bluetooth SIG, Inc.

ON Semiconductor and in are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative