Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | HCS12                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                              |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 60                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.5V                                                           |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 80-QFP                                                                 |

| Supplier Device Package    | 80-QFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12c128cfue |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.3.2 Signal Properties Summary

**Table 1-5. Signal Properties**

| Pin Name   | Pin Name                 | Pin Name   | Power              |                 | al Pull<br>istor           | Description                                        |  |  |  |

|------------|--------------------------|------------|--------------------|-----------------|----------------------------|----------------------------------------------------|--|--|--|

| Function 1 | Function 2               | Function 3 | Domain             | CTRL            | Reset<br>State             | Besonption                                         |  |  |  |

| EXTAL      | _                        | _          | V <sub>DDPLL</sub> | NA              | NA                         | Oscillator pins                                    |  |  |  |

| XTAL       | _                        | _          | V <sub>DDPLL</sub> | NA              | NA                         |                                                    |  |  |  |

| RESET      | _                        | _          | $V_{DDX}$          | None            | None                       | External reset pin                                 |  |  |  |

| XFC        | _                        | _          | V <sub>DDPLL</sub> | NA              | NA                         | PLL loop filter pin                                |  |  |  |

| TEST       | V <sub>PP</sub>          | _          | V <sub>SSX</sub>   | NA              | NA                         | Test pin only                                      |  |  |  |

| BKGD       | MODC                     | TAGHI      | $V_{DDX}$          | Up              | Up                         | Background debug, mode pin, tag signal high        |  |  |  |

| PE7        | NOACC                    | XCLKS      | $V_{DDX}$          | PUCR            | Up                         | Port E I/O pin, access, clock select               |  |  |  |

| PE6        | IPIPE1                   | MODB       | V <sub>DDX</sub>   | 1               | RESET<br>w: Down           | Port E I/O pin and pipe status                     |  |  |  |

| PE5        | IPIPE0                   | MODA       | V <sub>DDX</sub>   |                 | RESET<br>w: Down           | Port E I/O pin and pipe status                     |  |  |  |

| PE4        | ECLK                     | _          | V <sub>DDX</sub>   | PUCR            | Mode<br>Dep <sup>(1)</sup> | Port E I/O pin, bus clock output                   |  |  |  |

| PE3        | LSTRB                    | TAGLO      | V <sub>DDX</sub>   | PUCR            | Mode<br>Dep <sup>1</sup>   | Port E I/O pin, low strobe, tag signal low         |  |  |  |

| PE2        | R/W                      | _          | V <sub>DDX</sub>   | PUCR            | Mode<br>Dep <sup>1</sup>   | Port E I/O pin, R/W in expanded modes              |  |  |  |

| PE1        | ĪRQ                      | _          | $V_{DDX}$          | PUCR            | Up                         | Port E input, external interrupt pin               |  |  |  |

| PE0        | XIRQ                     | _          | $V_{DDX}$          | PUCR            | Up                         | Port E input, non-maskable interrupt pin           |  |  |  |

| PA[7:3]    | ADDR[15:1/<br>DATA[15:1] | _          | V <sub>DDX</sub>   | PUCR            | Disabled                   | Port A I/O pin and multiplexed address/data        |  |  |  |

| PA[2:1]    | ADDR[10:9/<br>DATA[10:9] | _          | V <sub>DDX</sub>   | PUCR            | Disabled                   | Port A I/O pin and multiplexed address/data        |  |  |  |

| PA[0]      | ADDR[8]/<br>DATA[8]      | _          | V <sub>DDX</sub>   | PUCR            | Disabled                   | Port A I/O pin and multiplexed address/data        |  |  |  |

| PB[7:5]    | ADDR[7:5]/<br>DATA[7:5]  | _          | V <sub>DDX</sub>   | PUCR            | Disabled                   | Port B I/O pin and multiplexed address/data        |  |  |  |

| PB[4]      | ADDR[4]/<br>DATA[4]      | _          | V <sub>DDX</sub>   | PUCR            | Disabled                   | Port B I/O pin and multiplexed address/data        |  |  |  |

| PB[3:0]    | ADDR[3:0]/<br>DATA[3:0]  | _          | V <sub>DDX</sub>   | PUCR            | Disabled                   | Port B I/O pin and multiplexed address/data        |  |  |  |

| PAD[7:0]   | AN[7:0]                  | _          | V <sub>DDA</sub>   | PERAD/P<br>PSAD | Disabled                   | Port AD I/O pins and ATD inputs                    |  |  |  |

| PP[7]      | KWP[7]                   | _          | V <sub>DDX</sub>   | PERP/<br>PPSP   | Disabled                   | Port P I/O pins and keypad wake-up                 |  |  |  |

| PP[6]      | KWP[6]                   | ROMCTL     | V <sub>DDX</sub>   | PERP/<br>PPSP   | Disabled                   | Port P I/O pins, keypad wake-up, and ROMON enable. |  |  |  |

| PP[5]      | KWP[5]                   | PW5        | V <sub>DDX</sub>   | PERP/<br>PPSP   | Disabled                   | Port P I/O pin, keypad wake-up, PW5 output         |  |  |  |

| PP[4:3]    | KWP[4:3]                 | PW[4:3]    | V <sub>DDX</sub>   | PERP/<br>PPSP   | Disabled                   | Port P I/O pin, keypad wake-up, PWM output         |  |  |  |

### 1.3.4.27 PS[3:2] — Port S I/O Pins [3:2]

PS3 and PS2 are general purpose input or output pins. These pins are not available in the 48- / 52-pin package versions.

#### 1.3.4.28 PS1 / TXD — Port S I/O Pin 1

PS1 is a general purpose input or output pin and the transmit pin, TXD, of serial communication interface (SCI).

#### 1.3.4.29 PS0 / RXD — Port S I/O Pin 0

PS0 is a general purpose input or output pin and the receive pin, RXD, of serial communication interface (SCI).

### 1.3.4.30 PT[7:5] / IOC[7:5] — Port T I/O Pins [7:5]

PT7–PT5 are general purpose input or output pins. They can also be configured as the timer system input capture or output compare pins IOC7-IOC5.

## 1.3.4.31 PT[4:0] / IOC[4:0] / PW[4:0]— Port T I/O Pins [4:0]

PT4–PT0 are general purpose input or output pins. They can also be configured as the timer system input capture or output compare pins IOC[n] or as the PWM outputs PW[n].

## 1.3.5 Power Supply Pins

## 1.3.5.1 V<sub>DDX</sub>,V<sub>SSX</sub> — Power and Ground Pins for I/O Drivers

External power and ground for I/O drivers. Bypass requirements depend on how heavily the MCU pins are loaded.

## 1.3.5.2 V<sub>DDR</sub>, V<sub>SSR</sub> — Power and Ground Pins for I/O Drivers and for Internal Voltage Regulator

External power and ground for the internal voltage regulator. Connecting  $V_{DDR}$  to ground disables the internal voltage regulator.

## 1.3.5.3 V<sub>DD1</sub>, V<sub>DD2</sub>, V<sub>SS1</sub>, V<sub>SS2</sub> — Internal Logic Power Pins

Power is supplied to the MCU through  $V_{DD}$  and  $V_{SS}$ . This 2.5V supply is derived from the internal voltage regulator. There is no static load on those pins allowed. The internal voltage regulator is turned off, if  $V_{DDR}$  is tied to ground.

A valid edge on input is detected if 4 consecutive samples of a passive level are followed by 4 consecutive samples of an active level directly or indirectly.

The filters are continuously clocked by the bus clock in RUN and WAIT mode. In STOP mode the clock is generated by a single RC oscillator in the Port Integration Module. To maximize current saving the RC oscillator runs only if the following condition is true on any pin:

Sample count <= 4 and port interrupt enabled (PIE=1) and port interrupt flag not set (PIF=0).

#### 2.4.2.6 Port J

In all modes, port J pins PJ[7:6] can be used for general purpose I/O or interrupt driven general purpose I/O's. During reset, port J pins are configured as inputs.

Port J offers 2 I/O ports with the same interrupt features as on port P.

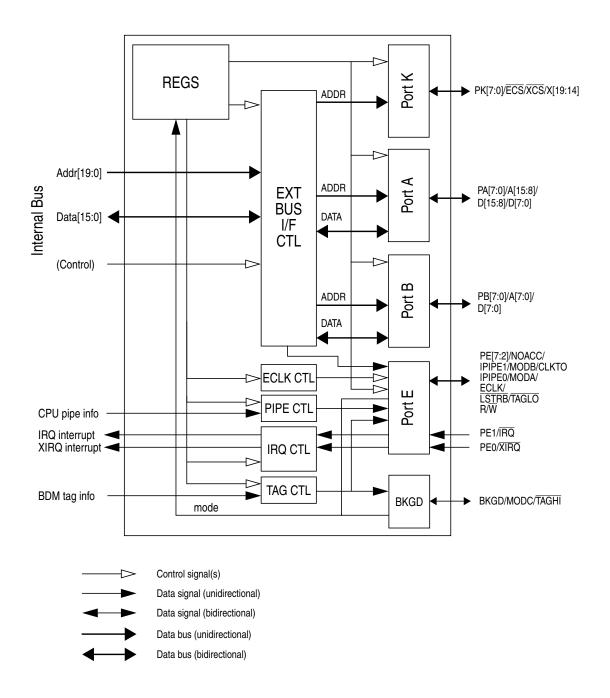

### 2.4.3 Port A, B, E and BKGD Pin

All port and pin logic is located in the core module. Please refer to S12\_mebi Block User Guide for details.

## 2.4.4 External Pin Descriptions

All ports start up as general purpose inputs on reset.

## 2.4.5 Low Power Options

#### 2.4.5.1 Run Mode

No low power options exist for this module in run mode.

#### 2.4.5.2 Wait Mode

No low power options exist for this module in wait mode.

#### 2.4.5.3 Stop Mode

All clocks are stopped. There are asynchronous paths to generate interrupts from STOP on port P and J.

#### 2.5 Initialization Information

The reset values of all registers are given in Section 2.3.2, "Register Descriptions".

#### 2.5.1 Reset Initialization

All registers including the data registers get set/reset asynchronously. Table 2-39 summarizes the port properties after reset initialization.

#### 3.1.1 Features

- Registers for mapping of address space for on-chip RAM, EEPROM, and FLASH (or ROM) memory blocks and associated registers

- Memory mapping control and selection based upon address decode and system operating mode

- Core address bus control

- Core data bus control and multiplexing

- Core security state decoding

- Emulation chip select signal generation ( $\overline{ECS}$ )

- External chip select signal generation ( $\overline{XCS}$ )

- Internal memory expansion

- External stretch and ROM mapping control functions via the MISC register

- Reserved registers for test purposes

- Configurable system memory options defined at integration of core into the system-on-a-chip (SoC).

## 3.1.2 Modes of Operation

Some of the registers operate differently depending on the mode of operation (i.e., normal expanded wide, special single chip, etc.). This is best understood from the register descriptions.

## 3.2 External Signal Description

All interfacing with the MMC sub-block is done within the core, it has no external signals.

## 3.3 Memory Map and Register Definition

A summary of the registers associated with the MMC sub-block is shown in Figure 3-2. Detailed descriptions of the registers and bits are given in the subsections that follow.

## 3.3.1 Module Memory Map

Table 3-1. MMC Memory Map

| Address<br>Offset | Register                                                        | Access |

|-------------------|-----------------------------------------------------------------|--------|

| 0x0010            | Initialization of Internal RAM Position Register (INITRM)       | R/W    |

| 0x0011            | Initialization of Internal Registers Position Register (INITRG) | R/W    |

| 0x0012            | Initialization of Internal EEPROM Position Register (INITEE)    | R/W    |

| 0x0013            | Miscellaneous System Control Register (MISC)                    | R/W    |

| 0x0014            | Reserved                                                        | _      |

|                   |                                                                 | _      |

| •                 |                                                                 |        |

Figure 4-1. MEBI Block Diagram

#### 4.4.3.2 Special Operating Modes

There are two special operating modes that correspond to normal operating modes. These operating modes are commonly used in factory testing and system development.

#### 4.4.3.2.1 Special Single-Chip Mode

When the MCU is reset in this mode, the background debug mode is enabled and active. The MCU does not fetch the reset vector and execute application code as it would in other modes. Instead the active background mode is in control of CPU execution and BDM firmware is waiting for additional serial commands through the BKGD pin. When a serial command instructs the MCU to return to normal execution, the system will be configured as described below unless the reset states of internal control registers have been changed through background commands after the MCU was reset.

There is no external expansion bus after reset in this mode. Ports A and B are initially simple bidirectional I/O pins that are configured as high-impedance inputs with internal pull resistors disabled; however, writing to the mode select bits in the MODE register (which is allowed in special modes) can change this after reset. All of the Port E pins (except PE4/ECLK) are initially configured as general purpose high-impedance inputs with internal pull resistors enabled. PE4/ECLK is configured as the E clock output in this mode.

The pins associated with Port E bits 6, 5, 3, and 2 cannot be configured for their alternate functions IPIPE1, IPIPE0,  $\overline{LSTRB}$ , and R/W while the MCU is in single chip modes. In single chip modes, the associated control bits PIPOE, LSTRE and RDWE are reset to zero. Writing the opposite value into these bits in single chip mode does not change the operation of the associated Port E pins.

Port E, bit 4 can be configured for a free-running E clock output by clearing NECLK=0. Typically the only use for an E clock output while the MCU is in single chip modes would be to get a constant speed clock for use in the external application system.

#### 4.4.3.2.2 Special Test Mode

In expanded wide modes, Ports A and B are configured as a 16-bit multiplexed address and data bus and Port E provides bus control and status signals. In special test mode, the write protection of many control bits is lifted so that they can be thoroughly tested without needing to go through reset.

## 4.4.3.3 Test Operating Mode

There is a test operating mode in which an external master, such as an I.C. tester, can control the on-chip peripherals.

#### 4.4.3.3.1 Peripheral Mode

This mode is intended for factory testing of the MCU. In this mode, the CPU is inactive and an external (tester) bus master drives address, data and bus control signals in through Ports A, B and E. In effect, the whole MCU acts as if it was a peripheral under control of an external CPU. This allows faster testing of on-chip memory and peripherals than previous testing methods. Since the mode control register is not accessible in peripheral mode, the only way to change to another mode is to reset the MCU into a different

Chapter 5 Interrupt (INTV1) Block Description

# Chapter 7 Debug Module (DBGV1) Block Description

#### 7.1 Introduction

This section describes the functionality of the debug (DBG) sub-block of the HCS12 core platform.

The DBG module is designed to be fully compatible with the existing BKP\_HCS12\_A module (BKP mode) and furthermore provides an on-chip trace buffer with flexible triggering capability (DBG mode). The DBG module provides for non-intrusive debug of application software. The DBG module is optimized for the HCS12 16-bit architecture.

#### 7.1.1 Features

The DBG module in BKP mode includes these distinctive features:

- Full or dual breakpoint mode

- Compare on address and data (full)

- Compare on either of two addresses (dual)

- BDM or SWI breakpoint

- Enter BDM on breakpoint (BDM)

- Execute SWI on breakpoint (SWI)

- Tagged or forced breakpoint

- Break just before a specific instruction will begin execution (TAG)

- Break on the first instruction boundary after a match occurs (Force)

- Single, range, or page address compares

- Compare on address (single)

- Compare on address 256 byte (range)

- Compare on any 16K page (page)

- At forced breakpoints compare address on read or write

- High and/or low byte data compares

- Comparator C can provide an additional tag or force breakpoint (enhancement for BKP mode)

| Name <sup>(1)</sup>               |        | Bit 7  | 6          | 5            | 4       | 3      | 2      | 1     | Bit 0 |

|-----------------------------------|--------|--------|------------|--------------|---------|--------|--------|-------|-------|

| 0x0022<br>DBGTBH                  | R<br>W | Bit 15 | Bit 14     | Bit 13       | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| 0x0023<br>DBGTBL                  | R<br>W | Bit 7  | Bit 6      | Bit 5        | Bit 4   | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

| 0x0024<br>DBGCNT                  | R<br>W | TBF    | 0          |              |         | Cl     | NT     |       |       |

| 0x0025<br>DBGCCX <sup>((2))</sup> | R<br>W | PAG    | SEL        |              |         | EXT    | CMP    |       |       |

| 0x0026<br>DBGCCH <sup>(2)</sup>   | R<br>W | Bit 15 | 14         | 13           | 12      | 11     | 10     | 9     | Bit 8 |

| 0x0027<br>DBGCCL <sup>(2)</sup>   | R<br>W | Bit 7  | 6          | 5            | 4       | 3      | 2      | 1     | Bit 0 |

| 0x0028<br>DBGC2<br>BKPCT0         | R<br>W | BKABEN | FULL       | BDM          | TAGAB   | BKCEN  | TAGC   | RWCEN | RWC   |

| 0x0029<br>DBGC3<br>BKPCT1         | R<br>W | ВКАМВН | BKAMBL     | вквмвн       | BKBMBL  | RWAEN  | RWA    | RWBEN | RWB   |

| 0x002A<br>DBGCAX<br>BKP0X         | R<br>W | PAG    | SEL        |              |         | EXT    | СМР    |       |       |

| 0x002B<br>DBGCAH<br>BKP0H         | R<br>W | Bit 15 | 14         | 13           | 12      | 11     | 10     | 9     | Bit 8 |

| 0x002C<br>DBGCAL<br>BKP0L         | R<br>W | Bit 7  | 6          | 5            | 4       | 3      | 2      | 1     | Bit 0 |

| 0x002D<br>DBGCBX<br>BKP1X         | R<br>W | PAG    | SEL        |              | EXTCMP  |        |        |       |       |

| 0x002E<br>DBGCBH<br>BKP1H         | R<br>W | Bit 15 | 14         | 13           | 12      | 11     | 10     | 9     | Bit 8 |

| 0x002F<br>DBGCBL<br>BKP1L         | R<br>W | Bit 7  | 6          | 5            | 4       | 3      | 2      | 1     | Bit 0 |

|                                   |        |        | = Unimpler | mented or Re | eserved |        |        |       |       |

Figure 7-3. DBG Register Summary (continued)

Chapter 8 Analog-to-Digital Converter (ATD10B8C) Block Description

#### 8.5.1.3 Step 3

Configure how many conversions you want to perform in one sequence and define other settings in ATDCTL3.

Example: Write S4C=1 to do 4 conversions per sequence.

#### 8.5.1.4 Step 4

Configure resolution, sampling time and ATD clock speed in ATDCTL4.

Example: Use default for resolution and sampling time by leaving SRES8, SMP1 and SMP0 clear. For a bus clock of 40MHz write 9 to PR4-0, this gives an ATD clock of 0.5\*40MHz/(9+1) = 2MHz which is within the allowed range for  $f_{ATDCLK}$ .

#### 8.5.1.5 Step 5

Configure starting channel, single/multiple channel, continuous or single sequence and result data format in ATDCTL5. Writing ATDCTL5 will start the conversion, so make sure your write ATDCTL5 in the last step.

Example: Leave CC,CB,CA clear to start on channel AN0. Write MULT=1 to convert channel AN0 to AN3 in a sequence (4 conversion per sequence selected in ATDCTL3).

## 8.5.2 Aborting an A/D conversion

## 8.5.2.1 Step 1

Disable the ATD Interrupt by writing ASCIE=0 in ATDCTL2. This will also abort any ongoing conversion sequence.

It is important to clear the interrupt enable at this point, prior to step 3, as depending on the device clock gating it may not always be possible to clear it or the SCF flag once the module is disabled (ADPU=0).

## 8.5.2.2 Step 2

Clear the SCF flag by writing a 1 in ATDSTAT0.

(Remaining flags will be cleared with the next start of a conversions, but SCF flag should be cleared to avoid SCF interrupt.)

## 8.5.2.3 Step 3

Power down ATD by writing ADPU=0 in ATDCTL2.

#### 8.6 Resets

At reset the ATD10B8C is in a power down state. The reset state of each individual bit is listed within Section 8.3.2, "Register Descriptions" which details the registers and their bit-field.

#### **Table 9-6. RTICTL Field Descriptions**

| Field           | Description                                                                                                                                                                                                                                                   |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:4<br>RTR[6:4] | Real-Time Interrupt Prescale Rate Select Bits — These bits select the prescale rate for the RTI. See Table 9-7.                                                                                                                                               |

| 3:0<br>RTR[3:0] | Real-Time Interrupt Modulus Counter Select Bits — These bits select the modulus counter target value to provide additional granularity. Table 9-7 shows all possible divide values selectable by the RTICTL register. The source clock for the RTI is OSCCLK. |

**Table 9-7. RTI Frequency Divide Rates**

|             | RTR[6:4] =   |                           |                           |                           |                           |                           |                           |                           |  |  |  |

|-------------|--------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|--|

| RTR[3:0]    | 000<br>(OFF) | 001<br>(2 <sup>10</sup> ) | 010<br>(2 <sup>11</sup> ) | 011<br>(2 <sup>12</sup> ) | 100<br>(2 <sup>13</sup> ) | 101<br>(2 <sup>14</sup> ) | 110<br>(2 <sup>15</sup> ) | 111<br>(2 <sup>16</sup> ) |  |  |  |

| 0000 (÷1)   | OFF*         | 2 <sup>10</sup>           | 2 <sup>11</sup>           | 2 <sup>12</sup>           | 2 <sup>13</sup>           | 2 <sup>14</sup>           | 2 <sup>15</sup>           | 2 <sup>16</sup>           |  |  |  |

| 0001 (÷2)   | OFF*         | 2x2 <sup>10</sup>         | 2x2 <sup>11</sup>         | 2x2 <sup>12</sup>         | 2x2 <sup>13</sup>         | 2x2 <sup>14</sup>         | 2x2 <sup>15</sup>         | 2x2 <sup>16</sup>         |  |  |  |

| 0010 (÷3)   | OFF*         | 3x2 <sup>10</sup>         | 3x2 <sup>11</sup>         | 3x2 <sup>12</sup>         | 3x2 <sup>13</sup>         | 3x2 <sup>14</sup>         | 3x2 <sup>15</sup>         | 3x2 <sup>16</sup>         |  |  |  |

| 0011 (÷4)   | OFF*         | 4x2 <sup>10</sup>         | 4x2 <sup>11</sup>         | 4x2 <sup>12</sup>         | 4x2 <sup>13</sup>         | 4x2 <sup>14</sup>         | 4x2 <sup>15</sup>         | 4x2 <sup>16</sup>         |  |  |  |

| 0100 (÷5)   | OFF*         | 5x2 <sup>10</sup>         | 5x2 <sup>11</sup>         | 5x2 <sup>12</sup>         | 5x2 <sup>13</sup>         | 5x2 <sup>14</sup>         | 5x2 <sup>15</sup>         | 5x2 <sup>16</sup>         |  |  |  |

| 0101 (÷6)   | OFF*         | 6x2 <sup>10</sup>         | 6x2 <sup>11</sup>         | 6x2 <sup>12</sup>         | 6x2 <sup>13</sup>         | 6x2 <sup>14</sup>         | 6x2 <sup>15</sup>         | 6x2 <sup>16</sup>         |  |  |  |

| 0110 (÷7)   | OFF*         | 7x2 <sup>10</sup>         | 7x2 <sup>11</sup>         | 7x2 <sup>12</sup>         | 7x2 <sup>13</sup>         | 7x2 <sup>14</sup>         | 7x2 <sup>15</sup>         | 7x2 <sup>16</sup>         |  |  |  |

| 0111 (÷8)   | OFF*         | 8x2 <sup>10</sup>         | 8x2 <sup>11</sup>         | 8x2 <sup>12</sup>         | 8x2 <sup>13</sup>         | 8x2 <sup>14</sup>         | 8x2 <sup>15</sup>         | 8x2 <sup>16</sup>         |  |  |  |

| 1000 (÷9)   | OFF*         | 9x2 <sup>10</sup>         | 9x2 <sup>11</sup>         | 9x2 <sup>12</sup>         | 9x2 <sup>13</sup>         | 9x2 <sup>14</sup>         | 9x2 <sup>15</sup>         | 9x2 <sup>16</sup>         |  |  |  |

| 1001 (÷10)  | OFF*         | 10x2 <sup>10</sup>        | 10x2 <sup>11</sup>        | 10x2 <sup>12</sup>        | 10x2 <sup>13</sup>        | 10x2 <sup>14</sup>        | 10x2 <sup>15</sup>        | 10x2 <sup>16</sup>        |  |  |  |

| 1010 (÷11)  | OFF*         | 11x2 <sup>10</sup>        | 11x2 <sup>11</sup>        | 11x2 <sup>12</sup>        | 11x2 <sup>13</sup>        | 11x2 <sup>14</sup>        | 11x2 <sup>15</sup>        | 11x2 <sup>16</sup>        |  |  |  |

| 1011 (÷12)  | OFF*         | 12x2 <sup>10</sup>        | 12x2 <sup>11</sup>        | 12x2 <sup>12</sup>        | 12x2 <sup>13</sup>        | 12x2 <sup>14</sup>        | 12x2 <sup>15</sup>        | 12x2 <sup>16</sup>        |  |  |  |

| 1100 (÷ 13) | OFF*         | 13x2 <sup>10</sup>        | 13x2 <sup>11</sup>        | 13x2 <sup>12</sup>        | 13x2 <sup>13</sup>        | 13x2 <sup>14</sup>        | 13x2 <sup>15</sup>        | 13x2 <sup>16</sup>        |  |  |  |

| 1101 (÷14)  | OFF*         | 14x2 <sup>10</sup>        | 14x2 <sup>11</sup>        | 14x2 <sup>12</sup>        | 14x2 <sup>13</sup>        | 14x2 <sup>14</sup>        | 14x2 <sup>15</sup>        | 14x2 <sup>16</sup>        |  |  |  |

| 1110 (÷15)  | OFF*         | 15x2 <sup>10</sup>        | 15x2 <sup>11</sup>        | 15x2 <sup>12</sup>        | 15x2 <sup>13</sup>        | 15x2 <sup>14</sup>        | 15x2 <sup>15</sup>        | 15x2 <sup>16</sup>        |  |  |  |

| 1111 (÷ 16) | OFF*         | 16x2 <sup>10</sup>        | 16x2 <sup>11</sup>        | 16x2 <sup>12</sup>        | 16x2 <sup>13</sup>        | 16x2 <sup>14</sup>        | 16x2 <sup>15</sup>        | 16x2 <sup>16</sup>        |  |  |  |

<sup>\*</sup> Denotes the default value out of reset. This value should be used to disable the RTI to ensure future backwards compatibility.

Chapter 10 Freescale's Scalable Controller Area Network (S12MSCANV2)

### 10.4.7.1 Description of Interrupt Operation

The MSCAN supports four interrupt vectors (see Table 10-36), any of which can be individually masked (for details see sections from Section 10.3.2.6, "MSCAN Receiver Interrupt Enable Register (CANRIER)," to Section 10.3.2.8, "MSCAN Transmitter Interrupt Enable Register (CANTIER)").

#### NOTE

The dedicated interrupt vector addresses are defined in the Resets and Interrupts chapter.

Table 10-36. Interrupt Vectors

| Interrupt Source                          | CCR Mask | Local Enable           |

|-------------------------------------------|----------|------------------------|

| Wake-Up Interrupt (WUPIF)                 | I bit    | CANRIER (WUPIE)        |

| Error Interrupts Interrupt (CSCIF, OVRIF) | l bit    | CANRIER (CSCIE, OVRIE) |

| Receive Interrupt (RXF)                   | l bit    | CANRIER (RXFIE)        |

| Transmit Interrupts (TXE[2:0])            | l bit    | CANTIER (TXEIE[2:0])   |

#### 10.4.7.2 Transmit Interrupt

At least one of the three transmit buffers is empty (not scheduled) and can be loaded to schedule a message for transmission. The TXEx flag of the empty message buffer is set.

#### 10.4.7.3 Receive Interrupt

A message is successfully received and shifted into the foreground buffer (RxFG) of the receiver FIFO. This interrupt is generated immediately after receiving the EOF symbol. The RXF flag is set. If there are multiple messages in the receiver FIFO, the RXF flag is set as soon as the next message is shifted to the foreground buffer.

## 10.4.7.4 Wake-Up Interrupt

A wake-up interrupt is generated if activity on the CAN bus occurs during MSCN internal sleep mode. WUPE (see Section 10.3.2.1, "MSCAN Control Register 0 (CANCTL0)") must be enabled.

## 10.4.7.5 Error Interrupt

An error interrupt is generated if an overrun of the receiver FIFO, error, warning, or bus-off condition occurrs. Section 10.3.2.5, "MSCAN Receiver Flag Register (CANRFLG) indicates one of the following conditions:

- **Overrun** An overrun condition of the receiver FIFO as described in Section 10.4.2.3, "Receive Structures," occurred.

- CAN Status Change The actual value of the transmit and receive error counters control the CAN bus state of the MSCAN. As soon as the error counters skip into a critical range (Tx/Rxwarning, Tx/Rx-error, bus-off) the MSCAN flags an error condition. The status change, which caused the error condition, is indicated by the TSTAT and RSTAT flags (see Section 10.3.2.5,

#### Chapter 13 Serial Communications Interface (S12SCIV2) Block Description

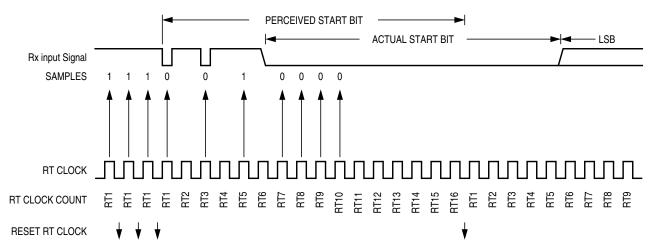

In Figure 13-16, a large burst of noise is perceived as the beginning of a start bit, although the test sample at RT5 is high. The RT5 sample sets the noise flag. Although this is a worst-case misalignment of perceived bit time, the data samples RT8, RT9, and RT10 are within the bit time and data recovery is successful.

Figure 13-16. Start Bit Search Example 3

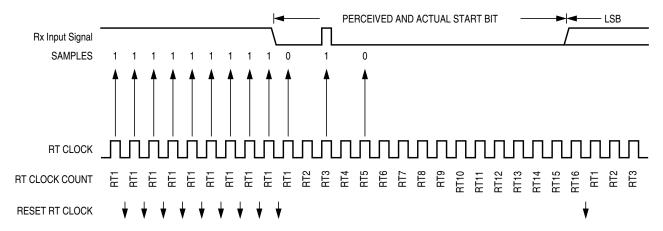

Figure 13-17 shows the effect of noise early in the start bit time. Although this noise does not affect proper synchronization with the start bit time, it does set the noise flag.

Figure 13-17. Start Bit Search Example 4

Table 14-7. Example SPI Baud Rate Selection (25 MHz Bus Clock) (continued)

| SPPR2 | SPPR1 | SPPR0 | SPR2 | SPR1 | SPR0 | Baud Rate<br>Divisor | Baud Rate   |

|-------|-------|-------|------|------|------|----------------------|-------------|

| 1     | 0     | 0     | 1    | 1    | 1    | 1280                 | 19.53 kHz   |

| 1     | 0     | 1     | 0    | 0    | 0    | 12                   | 2.08333 MHz |

| 1     | 0     | 1     | 0    | 0    | 1    | 24                   | 1.04167 MHz |

| 1     | 0     | 1     | 0    | 1    | 0    | 48                   | 520.83 kHz  |

| 1     | 0     | 1     | 0    | 1    | 1    | 96                   | 260.42 kHz  |

| 1     | 0     | 1     | 1    | 0    | 0    | 192                  | 130.21 kHz  |

| 1     | 0     | 1     | 1    | 0    | 1    | 384                  | 65.10 kHz   |

| 1     | 0     | 1     | 1    | 1    | 0    | 768                  | 32.55 kHz   |

| 1     | 0     | 1     | 1    | 1    | 1    | 1536                 | 16.28 kHz   |

| 1     | 1     | 0     | 0    | 0    | 0    | 14                   | 1.78571 MHz |

| 1     | 1     | 0     | 0    | 0    | 1    | 28                   | 892.86 kHz  |

| 1     | 1     | 0     | 0    | 1    | 0    | 56                   | 446.43 kHz  |

| 1     | 1     | 0     | 0    | 1    | 1    | 112                  | 223.21 kHz  |

| 1     | 1     | 0     | 1    | 0    | 0    | 224                  | 111.61 kHz  |

| 1     | 1     | 0     | 1    | 0    | 1    | 448                  | 55.80 kHz   |

| 1     | 1     | 0     | 1    | 1    | 0    | 896                  | 27.90 kHz   |

| 1     | 1     | 0     | 1    | 1    | 1    | 1792                 | 13.95 kHz   |

| 1     | 1     | 1     | 0    | 0    | 0    | 16                   | 1.5625 MHz  |

| 1     | 1     | 1     | 0    | 0    | 1    | 32                   | 781.25 kHz  |

| 1     | 1     | 1     | 0    | 1    | 0    | 64                   | 390.63 kHz  |

| 1     | 1     | 1     | 0    | 1    | 1    | 128                  | 195.31 kHz  |

| 1     | 1     | 1     | 1    | 0    | 0    | 256                  | 97.66 kHz   |

| 1     | 1     | 1     | 1    | 0    | 1    | 512                  | 48.83 kHz   |

| 1     | 1     | 1     | 1    | 1    | 0    | 1024                 | 24.41 kHz   |

| 1     | 1     | 1     | 1    | 1    | 1    | 2048                 | 12.21 kHz   |

#### **NOTE**

In slave mode of SPI S-clock speed DIV2 is not supported.

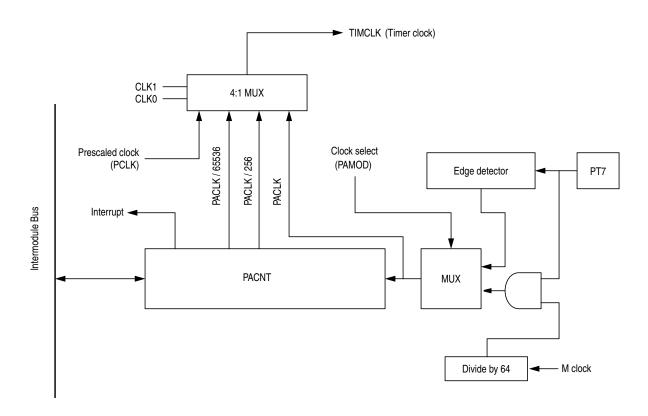

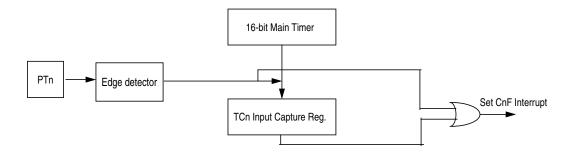

Figure 15-2. 16-Bit Pulse Accumulator Block Diagram

Figure 15-3. Interrupt Flag Setting

## 15.2.6 IOC2 — Input Capture and Output Compare Channel 2 Pin

This pin serves as input capture or output compare for channel 2.

### 15.2.7 IOC1 — Input Capture and Output Compare Channel 1 Pin

This pin serves as input capture or output compare for channel 1.

## 15.2.8 IOC0 — Input Capture and Output Compare Channel 0 Pin

This pin serves as input capture or output compare for channel 0.

#### NOTE

For the description of interrupts see Section 15.6, "Interrupts".

## 15.3 Memory Map and Register Definition

This section provides a detailed description of all memory and registers.

## 15.3.1 Module Memory Map

The memory map for the TIM16B8CV1 module is given below in Table 15-2. The address listed for each register is the address offset. The total address for each register is the sum of the base address for the TIM16B8CV1 module and the address offset for each register.

#### 15.4.6 Gated Time Accumulation Mode

Setting the PAMOD bit configures the pulse accumulator for gated time accumulation operation. An active level on the PACNT input pin enables a divided-by-64 clock to drive the pulse accumulator. The PEDGE bit selects low levels or high levels to enable the divided-by-64 clock.

The trailing edge of the active level at the IOC7 pin sets the PAIF. The PAI bit enables the PAIF flag to generate interrupt requests.

The pulse accumulator counter register reflect the number of pulses from the divided-by-64 clock since the last reset.

#### NOTE

The timer prescaler generates the divided-by-64 clock. If the timer is not active, there is no divided-by-64 clock.

#### 15.5 Resets

The reset state of each individual bit is listed within Section 15.3, "Memory Map and Register Definition" which details the registers and their bit fields.

## 15.6 Interrupts

This section describes interrupts originated by the TIM16B8CV1 block. Table 15-23 lists the interrupts generated by the TIM16B8CV1 to communicate with the MCU.

| Interrupt | Offset (1) | Vector <sup>1</sup> | Priority <sup>1</sup> | Source                        | Description                                   |

|-----------|------------|---------------------|-----------------------|-------------------------------|-----------------------------------------------|

| C[7:0]F   | _          | _                   | _                     | Timer Channel 7–0             | Active high timer channel interrupts 7–0      |

| PAOVI     | _          | _                   | _                     | Pulse Accumulator<br>Input    | Active high pulse accumulator input interrupt |

| PAOVF     | _          | _                   | _                     | Pulse Accumulator<br>Overflow | Pulse accumulator overflow interrupt          |

| TOF       | _          | _                   | _                     | Timer Overflow                | Timer Overflow interrupt                      |

Table 15-23. TIM16B8CV1 Interrupts

The TIM16B8CV1 uses a total of 11 interrupt vectors. The interrupt vector offsets and interrupt numbers are chip dependent.

## 15.6.1 Channel [7:0] Interrupt (C[7:0]F)

This active high outputs will be asserted by the module to request a timer channel 7-0 interrupt to be serviced by the system controller.

<sup>1.</sup> Chip Dependent.

Chapter 19 64 Kbyte Flash Module (S12FTS64KV4)

## 19.1.3 Modes of Operation

See Section 19.4.2, "Operating Modes" for a description of the Flash module operating modes. For program and erase operations, refer to Section 19.4.1, "Flash Command Operations".

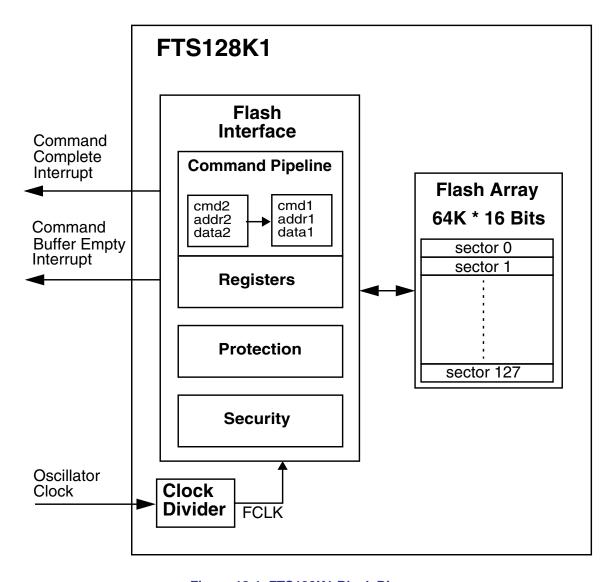

## 19.1.4 Block Diagram

Figure 19-1Figure 19-2 shows a block diagram of the FTS128K1FTS64K module.

Figure 19-1. FTS128K1 Block Diagram

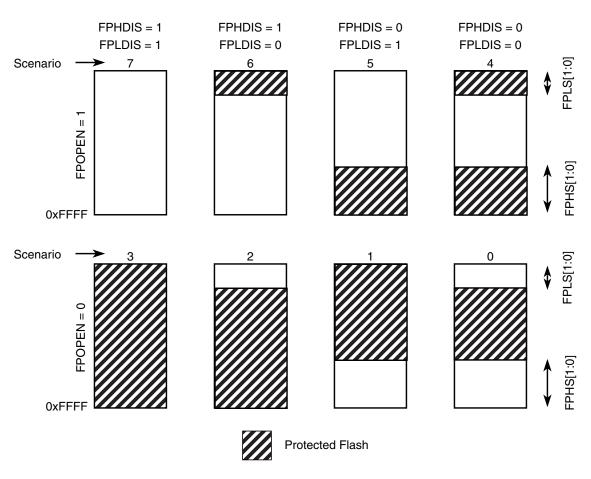

Figure 19-11. Flash Protection Scenarios

#### 19.3.2.5.1 Flash Protection Restrictions

The general guideline is that protection can only be added, not removed. All valid transitions between Flash protection scenarios are specified in Table 19-13. Any attempt to write an invalid scenario to the FPROT register will be ignored and the FPROT register will remain unchanged. The contents of the FPROT register reflect the active protection scenario.

| From                   |   | To Protection Scenario <sup>(1)</sup> |   |   |   |   |   |   |  |

|------------------------|---|---------------------------------------|---|---|---|---|---|---|--|

| Protection<br>Scenario | 0 | 1                                     | 2 | 3 | 4 | 5 | 6 | 7 |  |

| 0                      | Х | Х                                     | Х | Х |   |   |   |   |  |

| 1                      |   | Х                                     |   | Х |   |   |   |   |  |

| 2                      |   |                                       | Х | Х |   |   |   |   |  |

| 3                      |   |                                       |   | Х |   |   |   |   |  |

| 4                      |   |                                       |   | Х | Х |   |   |   |  |

| 5                      |   |                                       | Х | Х | Х | Х |   |   |  |

**Table 19-13. Flash Protection Scenario Transitions**

## A.2.2 ATD Operating Characteristics In 3.3V Range

The Table A-11 shows conditions under which the ATD operates.

The following constraints exist to obtain full-scale, full range results:  $V_{SSA} \le V_{RL} \le V_{IN} \le V_{RH} \le V_{DDA}$ . This constraint exists since the sample buffer amplifier can not drive beyond the power supply levels that it ties to. If the input level goes outside of this range it will effectively be clipped

**Table A-11. ATD Operating Characteristics**

| Condit | Conditions are shown in Table A-4 unless otherwise noted; Supply Voltage 3.3V-10% <= V <sub>DDA</sub> <= 3.3V+10% |                                                                                                              |                                            |                                         |        |                                         |              |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------|--------|-----------------------------------------|--------------|--|--|--|

| Num    | С                                                                                                                 | Rating                                                                                                       | Symbol                                     | Min                                     | Тур    | Max                                     | Unit         |  |  |  |

| 1      | D                                                                                                                 | Reference Potential Low High                                                                                 | V <sub>RL</sub><br>V <sub>RH</sub>         | V <sub>SSA</sub><br>V <sub>DDA</sub> /2 | _<br>_ | V <sub>DDA</sub> /2<br>V <sub>DDA</sub> | V<br>V       |  |  |  |

| 2      | С                                                                                                                 | Differential Reference Voltage                                                                               | $V_{RH}$ - $V_{RL}$                        | 3.0                                     | 3.3    | 3.6                                     | V            |  |  |  |

| 3      | D                                                                                                                 | ATD Clock Frequency                                                                                          | f <sub>ATDCLK</sub>                        | 0.5                                     | _      | 2.0                                     | MHz          |  |  |  |

| 4      | D                                                                                                                 | ATD 10-Bit Conversion Period  Clock Cycles <sup>(1)</sup> Conv, Time at 2.0MHz ATD Clock f <sub>ATDCLK</sub> | N <sub>CONV10</sub><br>T <sub>CONV10</sub> | 14<br>7                                 |        | 28<br>14                                | Cycles<br>μs |  |  |  |

| 5      | D                                                                                                                 | ATD 8-Bit Conversion Period  Clock Cycles <sup>1</sup> Conv, Time at 2.0MHz ATD Clock f <sub>ATDCLK</sub>    | N <sub>CONV8</sub><br>T <sub>CONV8</sub>   | 12<br>6                                 | _<br>_ | 26<br>13                                | Cycles<br>μs |  |  |  |

| 6      | D                                                                                                                 | Recovery Time (V <sub>DDA</sub> =3.3 Volts)                                                                  | t <sub>REC</sub>                           | _                                       | _      | 20                                      | μs           |  |  |  |

| 7      | Р                                                                                                                 | Reference Supply current                                                                                     | I <sub>REF</sub>                           | _                                       | _      | 0.250                                   | mA           |  |  |  |

<sup>1.</sup> The minimum time assumes a final sample period of 2 ATD clocks cycles while the maximum time assumes a final sample period of 16 ATD clocks.

## A.2.3 Factors Influencing Accuracy

Three factors — source resistance, source capacitance and current injection — have an influence on the accuracy of the ATD.

#### A.2.3.1 Source Resistance

Due to the input pin leakage current as specified in Table A-6 in conjunction with the source resistance there will be a voltage drop from the signal source to the ATD input. The maximum source resistance  $R_S$  specifies results in an error of less than 1/2 LSB (2.5 mV) at the maximum leakage current. If device or operating conditions are less than worst case or leakage-induced error is acceptable, larger values of source resistance is allowable.

## A.2.3.2 Source Capacitance

When sampling an additional internal capacitor is switched to the input. This can cause a voltage drop due to charge sharing with the external and the pin capacitance. For a maximum sampling error of the input voltage  $\leq$  1LSB, then the external filter capacitor,  $C_f \geq$  1024 \*  $(C_{INS} - C_{INN})$ .