Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | HCS12                                                       |

| Core Size                  | 16-Bit                                                      |

| Speed                      | 25MHz                                                       |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                   |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 31                                                          |

| Program Memory Size        | 128KB (128K x 8)                                            |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 4K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.5V                                                |

| Data Converters            | A/D 8x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 105°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 48-LQFP                                                     |

| Supplier Device Package    | 48-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12c128vfae |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 4.4.3 | Modes of Operation  | . 151 |

|-------|---------------------|-------|

|       | Internal Visibility |       |

| 4.4.5 | Low-Power Options   | . 156 |

# Chapter 5 Interrupt (INTV1) Block Description

| 5.1 |           | ction                                     |      |     |

|-----|-----------|-------------------------------------------|------|-----|

|     | 5.1.1     | Features                                  | <br> | 158 |

|     | 5.1.2     | Modes of Operation                        | <br> | 158 |

| 5.2 | External  | l Signal Description                      | <br> | 159 |

| 5.3 | Memory    | y Map and Register Definition             | <br> | 159 |

|     | 5.3.1     | Module Memory Map                         | <br> | 159 |

|     | 5.3.2     | Register Descriptions                     | <br> | 159 |

| 5.4 | Function  | nal Description                           | <br> | 161 |

|     | 5.4.1     | Low-Power Modes                           | <br> | 162 |

| 5.5 | Resets    |                                           | <br> | 162 |

| 5.6 |           | ts                                        |      |     |

|     | 5.6.1     | Interrupt Registers                       | <br> | 162 |

|     | 5.6.2     | Highest Priority I-Bit Maskable Interrupt | <br> | 162 |

|     | 5.6.3     | Interrupt Priority Decoder                | <br> | 163 |

| 5.7 | Exception | on Priority                               | <br> | 163 |

# Chapter 6

# Background Debug Module (BDMV4) Block Description

| 6.1 | Introduc | ction                                           |  |

|-----|----------|-------------------------------------------------|--|

|     | 6.1.1    | Features                                        |  |

|     | 6.1.2    | Modes of Operation                              |  |

| 6.2 | Externa  | l Signal Description                            |  |

|     | 6.2.1    | BKGD — Background Interface Pin                 |  |

|     | 6.2.2    | TAGHI       — High Byte Instruction Tagging Pin |  |

|     | 6.2.3    | TAGLO — Low Byte Instruction Tagging Pin        |  |

| 6.3 | Memory   | y Map and Register Definition                   |  |

|     | 6.3.1    | Module Memory Map                               |  |

|     | 6.3.2    | Register Descriptions                           |  |

| 6.4 | Function | nal Description                                 |  |

|     | 6.4.1    | Security                                        |  |

|     | 6.4.2    | Enabling and Activating BDM                     |  |

|     | 6.4.3    | BDM Hardware Commands                           |  |

|     | 6.4.4    | Standard BDM Firmware Commands                  |  |

|     | 6.4.5    | BDM Command Structure                           |  |

|     | 6.4.6    | BDM Serial Interface                            |  |

|     | 6.4.7    | Serial Interface Hardware Handshake Protocol    |  |

|     | 6.4.8    | Hardware Handshake Abort Procedure              |  |

|     | 6.4.9    | SYNC — Request Timed Reference Pulse            |  |

|     |          |                                                 |  |

| BKGD =<br>MODC | PE6 =<br>MODB | PE5 =<br>MODA | PP6 =<br>ROMCTL | ROMON<br>Bit | Mode Description                                                                                                                    |  |  |  |

|----------------|---------------|---------------|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0              | 0             | 0             | х               | 1            | Special Single Chip, BDM allowed and ACTIVE. BDM is allowed in all other modes but a serial command is required to make BDM active. |  |  |  |

| 0              | 0             | 1             | 0               | 1            | Emulation Expanded Narrow, BDM allowed                                                                                              |  |  |  |

| 0              | 0             | I             | 1               | 0            |                                                                                                                                     |  |  |  |

| 0              | 1             | 0             | Х               | 0            | Special Test (Expanded Wide), BDM allowed                                                                                           |  |  |  |

| 0              | -             | -             | 0               | 1            | Emulation Expanded Wide, BDM allowed                                                                                                |  |  |  |

| 0              | 1             |               | 1               | 0            |                                                                                                                                     |  |  |  |

| 1              | 0             | 0             | Х               | 1            | Normal Single Chip, BDM allowed                                                                                                     |  |  |  |

| 4              | 0             | 1             | 0               | 0            | Normal Expanded Narrow, BDM allowed                                                                                                 |  |  |  |

| 1              | 0             |               | 1               | 1            |                                                                                                                                     |  |  |  |

| 1              | 1             | 0             | х               | 1            | Peripheral; BDM allowed but bus operations would cause bus conflicts (must not be used)                                             |  |  |  |

| 4              | 4             | 4             | 0               | 0            | Normal Expanded Wide, BDM allowed                                                                                                   |  |  |  |

|                | I             | I             | 1               | 1            |                                                                                                                                     |  |  |  |

### Table 1-7. Mode Selection

For further explanation on the modes refer to the S12\_MEBI block guide.

Table 1-8. Clock Selection Based on PE7

| PE7 = XCLKS                    | Description                               |  |  |

|--------------------------------|-------------------------------------------|--|--|

| 1 Colpitts Oscillator selected |                                           |  |  |

| 0                              | Pierce Oscillator/external clock selected |  |  |

# 1.5.2 Security

The device will make available a security feature preventing the unauthorized read and write of the memory contents. This feature allows:

- Protection of the contents of FLASH,

- Operation in single-chip mode,

- Operation from external memory with internal FLASH disabled.

The user must be reminded that part of the security must lie with the user's code. An extreme example would be user's code that dumps the contents of the internal program. This code would defeat the purpose of security. At the same time the user may also wish to put a back door in the user's program. An example of this is the user downloads a key through the SCI which allows access to a programming routine that updates parameters.

# 1.5.2.1 Securing the Microcontroller

Once the user has programmed the FLASH, the part can be secured by programming the security bits located in the FLASH module. These non-volatile bits will keep the part secured through resetting the part and through powering down the part.

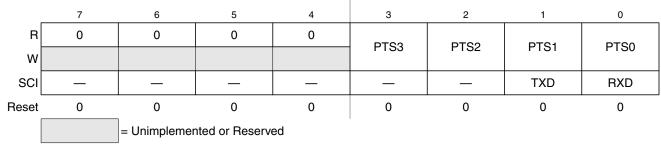

## 2.3.2.2 Port S Registers

## 2.3.2.2.1 Port S I/O Register (PTS)

Module Base + 0x0008

Figure 2-10. Port S I/O Register (PTS)

Read: Anytime.

Write: Anytime.

If the data direction bits of the associated I/O pins are set to 1, a read returns the value of the port register, otherwise the value at the pins is read.

The SCI port associated with transmit pin 1 is configured as output if the transmitter is enabled and the SCI pin associated with receive pin 0 is configured as input if the receiver is enabled. *Please refer to SCI Block User Guide for details*.

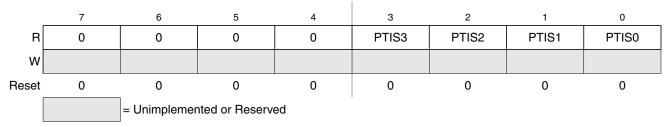

## 2.3.2.2.2 Port S Input Register (PTIS)

Module Base + 0x0009

### Figure 2-11. Port S Input Register (PTIS)

Read: Anytime.

Write: Never, writes to this register have no effect.

| Table 2- | 10. PTIS | Field | Descriptions |

|----------|----------|-------|--------------|

|----------|----------|-------|--------------|

| Field            | Description                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3–0<br>PTIS[3:0] | <b>Port S Input Register</b> — This register always reads back the status of the associated pins. This also can be used to detect overload or short circuit conditions on output pins. |

Chapter 2 Port Integration Module (PIM9C32) Block Description

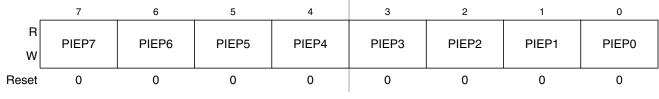

# 2.3.2.4.7 Port P Interrupt Enable Register (PIEP)

Figure 2-30. Port P Interrupt Enable Register (PIEP)

## Read: Anytime.

Write: Anytime.

### Table 2-26. PIEP Field Descriptions

| Field            | Description                                                                                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>PIEP[7:0] | <ul> <li>Pull Select Port P — This register disables or enables on a per pin basis the edge sensitive external interrupt associated with port P.</li> <li>0 Interrupt is disabled (interrupt flag masked).</li> <li>1 Interrupt is enabled.</li> </ul> |

## 2.3.2.4.8 Port P Interrupt Flag Register (PIFP)

Module Base + 0x001F

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | PIFP7 | PIFP6 | PIFP5 | PIFP4 | PIFP3 | PIFP2 | PIFP1 | PIFP0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

### Figure 2-31. Port P Interrupt Flag Register (PIFP)

Read: Anytime.

Write: Anytime.

### Table 2-27. PIFP Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>PIFP[7:0] | <ul> <li>Interrupt Flags Port P — Each flag is set by an active edge on the associated input pin. This could be a rising or a falling edge based on the state of the PPSP register. To clear this flag, write a "1" to the corresponding bit in the PIFP register. Writing a "0" has no effect.</li> <li>0 No active edge pending.<br/>Writing a "0" has no effect.</li> <li>1 Active edge on the associated bit has occurred (an interrupt will occur if the associated enable bit is set).<br/>Writing a "1" clears the associated flag.</li> </ul> |

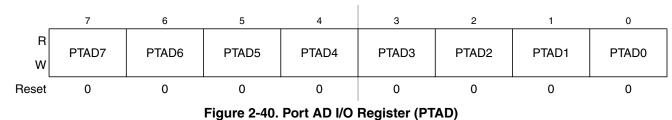

# 2.3.2.6 Port AD Registers

## 2.3.2.6.1 Port AD I/O Register (PTAD)

Module Base + 0x0030

Read: Anytime.

Write: Anytime.

If the data direction bits of the associated I/O pins are set to 1, a read returns the value of the port register, otherwise the value at the pins is read.

## 2.3.2.6.2 Port AD Input Register (PTIAD)

Module Base + 0x0031

|       | 7                           | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|-------|-----------------------------|--------|--------|--------|--------|--------|--------|--------|--|--|

| R     | PTIAD7                      | PTIAD6 | PTIAD5 | PTIAD4 | PTIAD3 | PTIAD2 | PTIAD1 | PTIAD0 |  |  |

| w     |                             |        |        |        |        |        |        |        |  |  |

| Reset | _                           | _      | _      | _      | _      |        | _      |        |  |  |

|       | = Unimplemented or Reserved |        |        |        |        |        |        |        |  |  |

Figure 2-41. Port AD Input Register (PTIAD)

Read: Anytime.

Write: Never, writes to this register have no effect.

This register always reads back the status of the associated pins. This can be used to detect overload or short circuit conditions on output pins.

Chapter 3 Module Mapping Control (MMCV4) Block Description

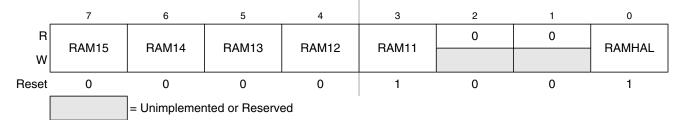

# 3.3.2.1 Initialization of Internal RAM Position Register (INITRM)

Module Base + 0x0010

Starting address location affected by INITRG register setting.

### Figure 3-3. Initialization of Internal RAM Position Register (INITRM)

Read: Anytime

Write: Once in normal and emulation modes, anytime in special modes

## NOTE

Writes to this register take one cycle to go into effect.

This register initializes the position of the internal RAM within the on-chip system memory map.

### Table 3-2. INITRM Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|             | Internal RAM Map Position — These bits determine the upper five bits of the base address for the system's internal RAM array.                                                                                                                                |  |

| 0<br>RAMHAL | <ul> <li>RAM High-Align — RAMHAL specifies the alignment of the internal RAM array.</li> <li>0 Aligns the RAM to the lowest address (0x0000) of the mappable space</li> <li>1 Aligns the RAM to the higher address (0xFFFF) of the mappable space</li> </ul> |  |

#### Chapter 4 Multiplexed External Bus Interface (MEBIV3)

This register is not in the on-chip memory map in expanded and special peripheral modes. Therefore, these accesses will be echoed externally.

## NOTE

These bits have no effect when the associated pin(s) are outputs. (The pull resistors are inactive.)

### Table 4-9. PUCR Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                             |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>PUPKE | Pull resistors Port K Enable         0       Port K pull resistors are disabled.         1       Enable pull resistors for port K input pins.                                                                                                                                                                           |  |  |

| 4<br>PUPEE | <ul> <li>Pull resistors Port E Enable</li> <li>0 Port E pull resistors on bits 7, 4:0 are disabled.</li> <li>1 Enable pull resistors for port E input pins bits 7, 4:0.</li> <li>Note: Pins 5 and 6 of port E have pull resistors which are only enabled during reset. This bit has no effect on these pins.</li> </ul> |  |  |

| 1<br>PUPBE | Pull resistors Port B Enable         0       Port B pull resistors are disabled.         1       Enable pull resistors for all port B input pins.                                                                                                                                                                       |  |  |

| 0<br>PUPAE | Pull resistors Port A Enable         0       Port A pull resistors are disabled.         1       Enable pull resistors for all port A input pins.                                                                                                                                                                       |  |  |

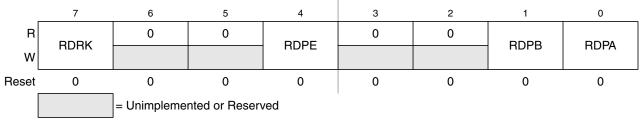

# 4.3.2.11 Reduced Drive Register (RDRIV)

### Module Base + 0x000D

Starting address location affected by INITRG register setting.

### Figure 4-15. Reduced Drive Register (RDRIV)

Read: Anytime (provided this register is in the map)

Write: Anytime (provided this register is in the map)

This register is used to select reduced drive for the pins associated with the core ports. This gives reduced power consumption and reduced RFI with a slight increase in transition time (depending on loading). This feature would be used on ports which have a light loading. The reduced drive function is independent of which function is being used on a particular port.

This register is not in the on-chip memory map in expanded and special peripheral modes. Therefore, these accesses will be echoed externally.

Chapter 4 Multiplexed External Bus Interface (MEBIV3)

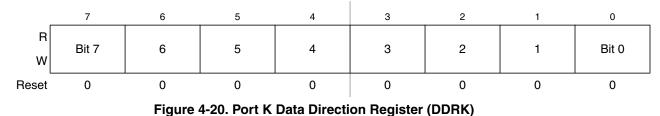

# 4.3.2.16 Port K Data Direction Register (DDRK)

Module Base + 0x0033

Starting address location affected by INITRG register setting.

Read: Anytime

Write: Anytime

This register determines the primary direction for each port K pin configured as general-purpose I/O. This register is not in the map in peripheral or expanded modes while the EMK control bit in MODE register is set. Therefore, these accesses will be echoed externally.

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7:0<br>DDRK | <ul> <li>Data Direction Port K Bits         <ul> <li>Associated pin is a high-impedance input</li> <li>Associated pin is an output</li> </ul> </li> <li>Note: It is unwise to write PORTK and DDRK as a word access. If you are changing port K pins from inputs to outputs, the data may have extra transitions during the write. It is best to initialize PORTK before enabling as outputs.</li> <li>Note: To ensure that you read the correct value from the PORTK pins, always wait at least one cycle after writing to the DDRK register before reading from the PORTK register.</li> </ul> |  |  |

# 4.4 Functional Description

# 4.4.1 Detecting Access Type from External Signals

The external signals  $\overline{\text{LSTRB}}$ ,  $R/\overline{W}$ , and AB0 indicate the type of bus access that is taking place. Accesses to the internal RAM module are the only type of access that would produce  $\overline{\text{LSTRB}} = \text{AB0} = 1$ , because the internal RAM is specifically designed to allow misaligned 16-bit accesses in a single cycle. In these cases the data for the address that was accessed is on the low half of the data bus and the data for address + 1 is on the high half of the data bus. This is summarized in Table 4-15.

| LSTRB | AB0 | R/W | Type of Access                 |

|-------|-----|-----|--------------------------------|

| 1     | 0   | 1   | 8-bit read of an even address  |

| 0     | 1   | 1   | 8-bit read of an odd address   |

| 1     | 0   | 0   | 8-bit write of an even address |

| 0     | 1   | 0   | 8-bit write of an odd address  |

# 5.6.3 Interrupt Priority Decoder

The priority decoder evaluates all interrupts pending and determines their validity and priority. When the CPU requests an interrupt vector, the decoder will provide the vector for the highest priority interrupt request. Because the vector is not supplied until the CPU requests it, it is possible that a higher priority interrupt request could override the original exception that caused the CPU to request the vector. In this case, the CPU will receive the highest priority vector and the system will process this exception instead of the original request.

## NOTE

Care must be taken to ensure that all exception requests remain active until the system begins execution of the applicable service routine; otherwise, the exception request may not be processed.

If for any reason the interrupt source is unknown (e.g., an interrupt request becomes inactive after the interrupt has been recognized but prior to the vector request), the vector address will default to that of the last valid interrupt that existed during the particular interrupt sequence. If the CPU requests an interrupt vector when there has never been a pending interrupt request, the INT will provide the software interrupt (SWI) vector address.

# 5.7 Exception Priority

The priority (from highest to lowest) and address of all exception vectors issued by the INT upon request by the CPU is shown in Table 5-5.

| Vector Address | Source                                                                          |

|----------------|---------------------------------------------------------------------------------|

| 0xFFFE-0xFFFF  | System reset                                                                    |

| 0xFFFC-0xFFFD  | Crystal monitor reset                                                           |

| 0xFFFA-0xFFFB  | COP reset                                                                       |

| 0xFFF8-0xFFF9  | Unimplemented opcode trap                                                       |

| 0xFFF6-0xFFF7  | Software interrupt instruction (SWI) or BDM vector request                      |

| 0xFFF4–0xFFF5  | XIRQ signal                                                                     |

| 0xFFF2-0xFFF3  | IRQ signal                                                                      |

| 0xFFF0-0xFF00  | Device-specific I-bit maskable interrupt sources (priority in descending order) |

Table 5-5. Exception Vector Map and Priority

| Table 9-2. CRGFLG Field Descriptions (continued) |

|--------------------------------------------------|

|--------------------------------------------------|

| Field      | Description                                                                                                                                                                                                                                                                                                                                  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>SCMIF | <ul> <li>Self-Clock Mode Interrupt Flag — SCMIF is set to 1 when SCM status bit changes. This flag can only be cleared by writing a 1. Writing a 0 has no effect. If enabled (SCMIE=1), SCMIF causes an interrupt request.</li> <li>0 No change in SCM bit.</li> <li>1 SCM bit has changed.</li> </ul>                                       |

| 0<br>SCM   | <ul> <li>Self-Clock Mode Status Bit — SCM reflects the current clocking mode. Writes have no effect.</li> <li>MCU is operating normally with OSCCLK available.</li> <li>MCU is operating in self-clock mode with OSCCLK in an unknown state. All clocks are derived from PLLCLK running at its minimum frequency f<sub>SCM</sub>.</li> </ul> |

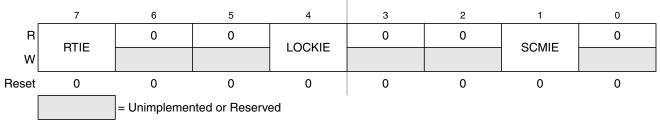

# 9.3.2.5 CRG Interrupt Enable Register (CRGINT)

This register enables CRG interrupt requests.

Module Base + 0x0004

## Figure 9-8. CRG Interrupt Enable Register (CRGINT)

Read: anytime

Write: anytime

| Field       | Description                                                                                                                                                  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>RTIE   | Real-Time Interrupt Enable Bit         0 Interrupt requests from RTI are disabled.         1 Interrupt will be requested whenever RTIF is set.               |  |  |

| 4<br>LOCKIE | Lock Interrupt Enable Bit         0       LOCK interrupt requests are disabled.         1       Interrupt will be requested whenever LOCKIF is set.          |  |  |

| 1<br>SCMIE  | Self-Clock Mode Interrupt Enable Bit         0       SCM interrupt requests are disabled.         1       Interrupt will be requested whenever SCMIF is set. |  |  |

| СМЕ | SCME | SCMIE | CRG Actions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Х    | х     | Clock failure><br>No action, clock loss not detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1   | 0    | Х     | Clock failure><br>CRG performs Clock Monitor Reset immediately                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1   | 1    | 0     | Clock failure> Scenario 1: OSCCLK recovers prior to exiting Wait Mode MCU remains in Wait Mode, - VREG enabled, - PLL enabled, - SCM activated, - Start Clock Quality Check, - Set SCMIF interrupt flag. Some time later OSCCLK recovers CM no longer indicates a failure, - 4096 OSCCLK cycles later Clock Quality Check indicates clock o.k., - SCM deactivated, - PLL disabled depending on PLLWAI, - VREG remains enabled (never gets disabled in Wait Mode) MCU remains in Wait Mode. Some time later either a wakeup interrupt occurs (no SCM interrupt) - Exit Wait Mode using OSCCLK as system clock (SYSCLK), - Continue normal operation.                                                                                                                                                                                                                                                                                                                                                              |

|     |      |       | <ul> <li>Continue normal operation.</li> <li>or an External Reset is applied.</li> <li>Exit Wait Mode using OSCCLK as system clock,</li> <li>Start reset sequence.</li> <li>Scenario 2: OSCCLK does not recover prior to exiting Wait Mode.</li> <li>MCU remains in Wait Mode,</li> <li>VREG enabled,</li> <li>PLL enabled,</li> <li>SCM activated,</li> <li>Start Clock Quality Check,</li> <li>Set SCMIF interrupt flag,</li> <li>Keep performing Clock Quality Checks (could continue infinitely) while in Wait Mode.</li> <li>Some time later either a wakeup interrupt occurs (no SCM interrupt)</li> <li>Exit Wait Mode in SCM using PLL clock (f<sub>SCM</sub>) as system clock,</li> <li>Continue to perform additional Clock Quality Checks until OSCCLK is o.k. again.</li> <li>or an External RESET is applied.</li> <li>Exit Wait Mode in SCM using PLL clock (f<sub>SCM</sub>) as system clock,</li> <li>Continue to perform additional Clock Quality Checks until OSCCLK is o.k. again.</li> </ul> |

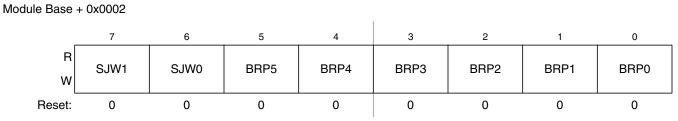

# 10.3.2.3 MSCAN Bus Timing Register 0 (CANBTR0)

The CANBTR0 register configures various CAN bus timing parameters of the MSCAN module.

Figure 10-6. MSCAN Bus Timing Register 0 (CANBTR0)

Read: Anytime Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

### Table 10-3. CANBTR0 Register Field Descriptions

| Field           | Description                                                                                                                                                                                                                                    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6<br>SJW[1:0] | Synchronization Jump Width — The synchronization jump width defines the maximum number of time quanta (Tq) clock cycles a bit can be shortened or lengthened to achieve resynchronization to data transitions on the CAN bus (see Table 10-4). |

| 5:0<br>BRP[5:0] | <b>Baud Rate Prescaler</b> — These bits determine the time quanta (Tq) clock which is used to build up the bit timing (see Table 10-5).                                                                                                        |

### Table 10-4. Synchronization Jump Width

| SJW1 | SJW0 | Synchronization Jump Width |

|------|------|----------------------------|

| 0    | 0    | 1 Tq clock cycle           |

| 0    | 1    | 2 Tq clock cycles          |

| 1    | 0    | 3 Tq clock cycles          |

| 1    | 1    | 4 Tq clock cycles          |

### Table 10-5. Baud Rate Prescaler

| BRP5 | BRP4 | BRP3 | BRP2 | BRP1 | BRP0 | Prescaler value (P) |

|------|------|------|------|------|------|---------------------|

| 0    | 0    | 0    | 0    | 0    | 0    | 1                   |

| 0    | 0    | 0    | 0    | 0    | 1    | 2                   |

| 0    | 0    | 0    | 0    | 1    | 0    | 3                   |

| 0    | 0    | 0    | 0    | 1    | 1    | 4                   |

| :    | :    | :    | :    | :    | :    | :                   |

| 1    | 1    | 1    | 1    | 1    | 1    | 64                  |

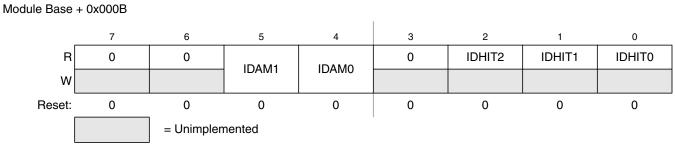

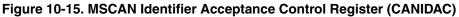

# 10.3.2.12 MSCAN Identifier Acceptance Control Register (CANIDAC)

The CANIDAC register is used for identifier acceptance control as described below.

## Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1), except bits IDHITx, which are read-only

| Field             | Description                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 5:4<br>IDAM[1:0]  | Identifier Acceptance Mode — The CPU sets these flags to define the identifier acceptance filter organization (see Section 10.4.3, "Identifier Acceptance Filter"). Table 10-17 summarizes the different settings. In filter closed mode, no message is accepted such that the foreground buffer is never reloaded. |  |  |  |  |  |

| 2:0<br>IDHIT[2:0] | Identifier Acceptance Hit Indicator — The MSCAN sets these flags to indicate an identifier acceptance hit (see Section 10.4.3, "Identifier Acceptance Filter"). Table 10-18 summarizes the different settings.                                                                                                      |  |  |  |  |  |

### Table 10-17. Identifier Acceptance Mode Settings

| IDAM1 | IDAM0 | Identifier Acceptance Mode     |  |  |  |

|-------|-------|--------------------------------|--|--|--|

| 0     | 0     | Two 32-bit acceptance filters  |  |  |  |

| 0     | 1     | Four 16-bit acceptance filters |  |  |  |

| 1     | 0     | Eight 8-bit acceptance filters |  |  |  |

| 1     | 1     | Filter closed                  |  |  |  |

### Table 10-18. Identifier Acceptance Hit Indication

| IDHIT2 | IDHIT1 | IDHIT0 | Identifier Acceptance Hit |

|--------|--------|--------|---------------------------|

| 0      | 0      | 0      | Filter 0 hit              |

| 0      | 0      | 1      | Filter 1 hit              |

| 0      | 1      | 0      | Filter 2 hit              |

| 0      | 1      | 1      | Filter 3 hit              |

| 1      | 0      | 0      | Filter 4 hit              |

| 1      | 0      | 1      | Filter 5 hit              |

| 1      | 1      | 0      | Filter 6 hit              |

| 1      | 1      | 1      | Filter 7 hit              |

### Table 12-3. PWMPOL Field Descriptions (continued)

| Field      | Description                                                                                                                                                                                                                                                                                    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>PPOL3 | Pulse Width Channel 3 Polarity0PWM channel 3 output is low at the beginning of the period, then goes high when the duty count is reached.1PWM channel 3 output is high at the beginning of the period, then goes low when the duty count is reached.                                           |

| 2<br>PPOL2 | Pulse Width Channel 2 Polarity0PWM channel 2 output is low at the beginning of the period, then goes high when the duty count is reached.1PWM channel 2 output is high at the beginning of the period, then goes low when the duty count is reached.                                           |

| 1<br>PPOL1 | <ul> <li>Pulse Width Channel 1 Polarity</li> <li>0 PWM channel 1 output is low at the beginning of the period, then goes high when the duty count is reached.</li> <li>1 PWM channel 1 output is high at the beginning of the period, then goes low when the duty count is reached.</li> </ul> |

| 0<br>PPOL0 | Pulse Width Channel 0 Polarity0PWM channel 0 output is low at the beginning of the period, then goes high when the duty count is reached1PWM channel 0 output is high at the beginning of the period, then goes low when the duty count is reached.                                            |

# 12.3.2.3 PWM Clock Select Register (PWMCLK)

Each PWM channel has a choice of two clocks to use as the clock source for that channel as described below.

Module Base + 0x0002

|       | 7 | 6            | 5               | 4     | 3      | 2       | 1     | 0       |

|-------|---|--------------|-----------------|-------|--------|---------|-------|---------|

| R     | 0 | 0            | PCLK5           | PCLK4 | PCLK3  | PCLK2   | PCLK1 | PCLK0   |

| w     |   |              | I OEKS          |       | I OLKO | I OLINZ | TOLKI | I OLINO |

| Reset | 0 | 0            | 0               | 0     | 0      | 0       | 0     | 0       |

|       |   | = Unimplemer | nted or Reserve | ed    |        |         |       |         |

## Figure 12-5. PWM Clock Select Register (PWMCLK)

Read: anytime

Write: anytime

### NOTE

Register bits PCLK0 to PCLK5 can be written anytime. If a clock select is changed while a PWM signal is being generated, a truncated or stretched pulse can occur during the transition.

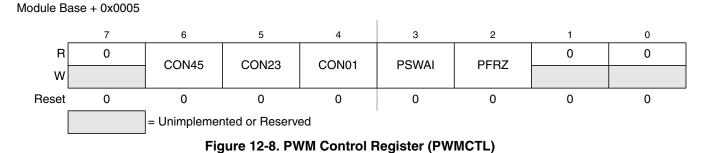

## Read: anytime

Write: anytime

There are three control bits for concatenation, each of which is used to concatenate a pair of PWM channels into one 16-bit channel. When channels 4 and 5 are concatenated, channel 4 registers become the high-order bytes of the double-byte channel. When channels 2 and 3 are concatenated, channel 2 registers become the high-order bytes of the double-byte channel. When channels 0 and 1 are concatenated, channel 0 registers become the high-order bytes of the double-byte of the double-byte channel.

Reference Section 12.4.2.7, "PWM 16-Bit Functions," for a more detailed description of the concatenation PWM function.

### NOTE

Change these bits only when both corresponding channels are disabled.

# 12.4.1.3 Clock Select

Each PWM channel has the capability of selecting one of two clocks. For channels 0, 1, 4, and 5 the clock choices are clock A or clock SA. For channels 2 and 3 the choices are clock B or clock SB. The clock selection is done with the PCLKx control bits in the PWMCLK register.

### NOTE

Changing clock control bits while channels are operating can cause irregularities in the PWM outputs.

# 12.4.2 PWM Channel Timers

The main part of the PWM module are the actual timers. Each of the timer channels has a counter, a period register and a duty register (each are 8 bit). The waveform output period is controlled by a match between the period register and the value in the counter. The duty is controlled by a match between the duty register and the counter value and causes the state of the output to change during the period. The starting polarity of the output is also selectable on a per channel basis. Figure 12-35 shows a block diagram for PWM timer.

Figure 12-35. PWM Timer Channel Block Diagram

Chapter 15 Timer Module (TIM16B8CV1) Block Description

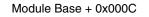

# 15.3.2.10 Timer Interrupt Enable Register (TIE)

## Read: Anytime

Write: Anytime.

| Field   | Description                                                                                                                                                                                                                                                                                     |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C7I:C0I | <b>Input Capture/Output Compare "x" Interrupt Enable</b> — The bits in TIE correspond bit-for-bit with the bits in the TFLG1 status register. If cleared, the corresponding flag is disabled from causing a hardware interrupt. If set, the corresponding flag is enabled to cause a interrupt. |

# 15.3.2.11 Timer System Control Register 2 (TSCR2)

Module Base + 0x000D

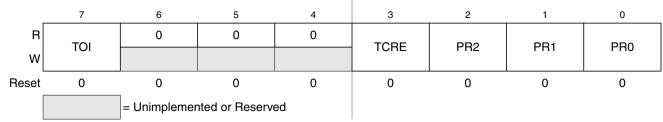

### Figure 15-19. Timer System Control Register 2 (TSCR2)

Read: Anytime

Write: Anytime.

#### Chapter 19 64 Kbyte Flash Module (S12FTS64KV4)

address 0x8000 to 0xBFFF to any physical 16K byte page in the Flash array memory.<sup>1</sup> The FPROT register (see Section 19.3.2.5) can be set to globally protect the entire Flash array. Three separate areas, one starting from the Flash array starting address (called lower) towards higher addresses, one growing downward from the Flash array end address (called higher), and the remaining addresses, can be activated for protection. The Flash array addresses covered by these protectable regions are shown in Figure 19-3Figure 19-4. The higher address area is mainly targeted to hold the boot loader code since it covers the vector space. The lower address area can be used for EEPROM emulation in an MCU without an EEPROM module since it can be left unprotected while the remaining addresses are protected from program or erase. Default protection settings as well as security information that allows the MCU to restrict access to the Flash module are stored in the Flash configuration field described in Table 19-1.

| Flash Address | Size<br>(bytes) | Description                                                                                |  |  |  |

|---------------|-----------------|--------------------------------------------------------------------------------------------|--|--|--|

| 0xFF00-0xFF07 | 8               | Backdoor Key to unlock security                                                            |  |  |  |

| 0xFF08-0xFF0C | 5               | Reserved                                                                                   |  |  |  |

| 0xFF0D        | 1               | Flash Protection byte<br>Refer to Section 19.3.2.5, "Flash Protection Register (FPROT)"    |  |  |  |

| 0xFF0E        | 1               | Reserved                                                                                   |  |  |  |

| 0xFF0F        | 1               | Flash Security/Options byte<br>Refer to Section 19.3.2.2, "Flash Security Register (FSEC)" |  |  |  |

### Table 19-1. Flash Configuration Field

1. By placing 0x3E/0x3F in the HCS12 Core PPAGE register, the bottom/top fixed 16 Kbyte pages can be seen twice in the MCU memory map.

### Table 20-5. FSEC Field Descriptions

| Field             | Description                                                                                                                                                                                           |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–6<br>KEYEN[1:0] | <b>Backdoor Key Security Enable Bits</b> — The KEYEN[1:0] bits define the enabling of the backdoor key access to the Flash module as shown in Table 20-6.                                             |

| 5–2<br>NV[5:2]    | Nonvolatile Flag Bits — The NV[5:2] bits are available to the user as nonvolatile flags.                                                                                                              |

| 1–0<br>SEC[1:0]   | Flash Security Bits — The SEC[1:0] bits define the security state of the MCU as shown in Table 20-7. If the Flash module is unsecured using backdoor key access, the SEC[1:0] bits are forced to 1:0. |

| KEYEN[1:0]        | Status of Backdoor Key Access |  |  |  |

|-------------------|-------------------------------|--|--|--|

| 00                | DISABLED                      |  |  |  |

| 01 <sup>(1)</sup> | DISABLED                      |  |  |  |

| 10                | ENABLED                       |  |  |  |

| 11                | DISABLED                      |  |  |  |

### Table 20-6. Flash KEYEN States

1. Preferred KEYEN state to disable Backdoor Key Access.

| SEC[1:0]          | Status of Security |

|-------------------|--------------------|

| 00                | Secured            |

| 01 <sup>(1)</sup> | Secured            |

| 10                | Unsecured          |

| 11                | Secured            |

#### Table 20-7. Flash Security States

1. Preferred SEC state to set MCU to secured state.

The security function in the Flash module is described in Section 20.4.3, "Flash Module Security".

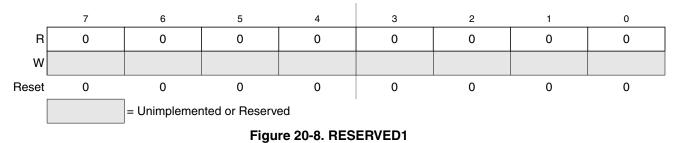

## 20.3.2.3 RESERVED1

This register is reserved for factory testing and is not accessible to the user.

Module Base + 0x0002

All bits read 0 and are not writable.

| From                   | To Protection Scenario <sup>(1)</sup> |   |   |   |   |   |   |   |

|------------------------|---------------------------------------|---|---|---|---|---|---|---|

| Protection<br>Scenario | 0                                     | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 6                      |                                       | Х |   | Х | Х |   | Х |   |

| 7                      | X                                     | Х | Х | Х | Х | Х | Х | Х |

1. Allowed transitions marked with X.

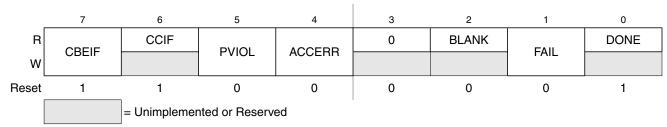

# 21.3.2.6 Flash Status Register (FSTAT)

The FSTAT register defines the status of the Flash command controller and the results of command execution.

Module Base + 0x0005

Figure 21-10. Flash Status Register (FSTAT)

In normal modes, bits CBEIF, PVIOL, and ACCERR are readable and writable, bits CCIF and BLANK are readable and not writable, remaining bits, including FAIL and DONE, read 0 and are not writable. In special modes, FAIL is readable and writable while DONE is readable but not writable. FAIL must be clear in special modes when starting a command write sequence.

Table 21-13. FSTAT Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CBEIF | Command Buffer Empty Interrupt Flag — The CBEIF flag indicates that the address, data and command<br>buffers are empty so that a new command write sequence can be started. The CBEIF flag is cleared by writing<br>a 1 to CBEIF. Writing a 0 to the CBEIF flag has no effect on CBEIF. Writing a 0 to CBEIF after writing an aligned<br>word to the Flash address space but before CBEIF is cleared will abort a command write sequence and cause<br>the ACCERR flag in the FSTAT register to be set. Writing a 0 to CBEIF outside of a command write sequence<br>will not set the ACCERR flag. The CBEIF flag is used together with the CBEIE bit in the FCNFG register to<br>generate an interrupt request (see Figure 21-26).<br>0 Buffers are full<br>1 Buffers are ready to accept a new command |

| 6<br>CCIF  | <ul> <li>Command Complete Interrupt Flag — The CCIF flag indicates that there are no more commands pending. The CCIF flag is cleared when CBEIF is clear and sets automatically upon completion of all active and pending commands. The CCIF flag does not set when an active commands completes and a pending command is fetched from the command buffer. Writing to the CCIF flag has no effect. The CCIF flag is used together with the CCIE bit in the FCNFG register to generate an interrupt request (see Figure 21-26).</li> <li>0 Command in progress</li> <li>1 All commands are completed</li> </ul>                                                                                                                                                                                         |