Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | HCS12                                                                 |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 25MHz                                                                 |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                             |

| Peripherals                | POR, PWM, WDT                                                         |

| Number of I/O              | 31                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.5V                                                          |

| Data Converters            | A/D 8x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12c64mfae |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Chapter 1 MC9S12C and MC9S12GC Device Overview (MC9S12C128)

# 0x0240-0x027F PIM (Port Interface Module) (Sheet 2 of 3)

| Address | Name     |                 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0253  | RDRM     | Read:<br>Write: | 0     | 0     | RDRM5 | RDRM4 | RDRM3 | RDRM2 | RDRM1 | RDRM0 |

| 0x0254  | PERM     | Read:<br>Write: | 0     | 0     | PERM5 | PERM4 | PERM3 | PERM2 | PERM1 | PERM0 |

| 0x0255  | PPSM     | Read:<br>Write: | 0     | 0     | PPSM5 | PPSM4 | PPSM3 | PPSM2 | PPSM1 | PPSM0 |

| 0x0256  | WOMM     | Read:           | 0     | 0     | WOMM5 | WOMM4 | WOMM3 | WOMM2 | WOMM1 | WOMM0 |

| 0x0257  | Reserved | Write:<br>Read: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|         |          | Write:          |       |       |       |       |       |       |       |       |

| 0x0258  | PTP      | Write:          | PTP7  | PTP6  | PTP5  | PTP4  | PTP3  | PTP2  | PTP1  | PTP0  |

| 0x0259  | PTIP     | Read:<br>Write: | PTIP7 | PTIP6 | PTIP5 | PTIP4 | PTIP3 | PTIP2 | PTIP1 | PTIP0 |

| 0x025A  | DDRP     | Read:<br>Write: | DDRP7 | DDRP7 | DDRP5 | DDRP4 | DDRP3 | DDRP2 | DDRP1 | DDRP0 |

| 0x025B  | RDRP     | Read:<br>Write: | RDRP7 | RDRP6 | RDRP5 | RDRP4 | RDRP3 | RDRP2 | RDRP1 | RDRP0 |

| 0x025C  | PERP     | Read:<br>Write: | PERP7 | PERP6 | PERP5 | PERP4 | PERP3 | PERP2 | PERP1 | PERP0 |

| 0x025D  | PPSP     | Read:<br>Write: | PPSP7 | PPSP6 | PPSP5 | PPSP4 | PPSP3 | PPSP2 | PPSP1 | PPSS0 |

| 0x025E  | PIEP     | Read:<br>Write: | PIEP7 | PIEP6 | PIEP5 | PIEP4 | PIEP3 | PIEP2 | PIEP1 | PIEP0 |

| 0x025F  | PIFP     | Read:<br>Write: | PIFP7 | PIFP6 | PIFP5 | PIFP4 | PIFP3 | PIFP2 | PIFP1 | PIFP0 |

| 0x0260  | Reserved | Read:           | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0261  | Reserved | Write:<br>Read: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0.0201  | neserveu | Write:          | ^     |       |       | 0     | 0     | 0     | 0     |       |

| 0x0262  | Reserved | Read:<br>Write: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0263  | Reserved | Read:           | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|         |          | Write:<br>Read: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0264  | Reserved | Write:          | •     |       |       |       |       | -     |       | -     |

| 0x0265  | Reserved | Read:<br>Write: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0,0000  | Decembed | Read:           | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0266  | Reserved | Write:          |       |       | _     | _     | _     | _     |       | _     |

| 0x0267  | Reserved | Read:<br>Write: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0268  | PTJ      | Read:           | PTJ7  | PTJ6  | 0     | 0     | 0     | 0     | 0     | 0     |

| 0.0200  | 1 10     | Write:          | PTIJ7 |       | 0     | 0     | 0     | 0     | 0     |       |

| 0x0269  | PTIJ     | Read:<br>Write: | FIIJ/ | PTIJ6 | 0     | 0     | 0     | 0     | 0     | 0     |

Chapter 2 Port Integration Module (PIM9C32) Block Description

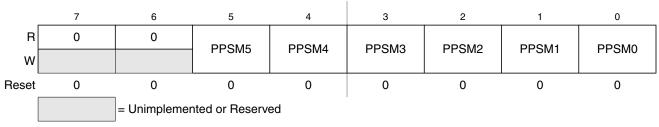

## 2.3.2.3.6 Port M Polarity Select Register (PPSM)

Module Base + 0x0015

Figure 2-22. Port M Polarity Select Register (PPSM)

Read: Anytime. Write: Anytime.

**Table 2-20. PPSM Field Descriptions**

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-0<br>PPSM[5:0] | Polarity Select Port M — This register selects whether a pull-down or a pull-up device is connected to the pin.  O A pull-up device is connected to the associated port M pin, if enabled by the associated bit in register PERM and if the port is used as input or as wired-or output.  A pull-down device is connected to the associated port M pin, if enabled by the associated bit in register PERM and if the port is used as input. |

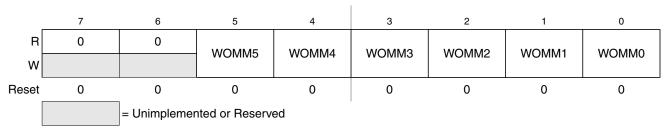

## 2.3.2.3.7 Port M Wired-OR Mode Register (WOMM)

Module Base + 0x0016

Figure 2-23. Port M Wired-OR Mode Register (WOMM)

Read: Anytime. Write: Anytime.

**Table 2-21. WOMM Field Descriptions**

| Field            | Description                                                                                                                                                                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5–0<br>WOMM[5:0] | Wired-OR Mode Port M — This register configures the output pins as wired-or. If enabled the output is driven active low only (open-drain). A logic level of "1" is not driven. This bit has no influence on pins used as inputs.  Output buffers operate as push-pull outputs.  Output buffers operate as open-drain outputs. |

Chapter 2 Port Integration Module (PIM9C32) Block Description

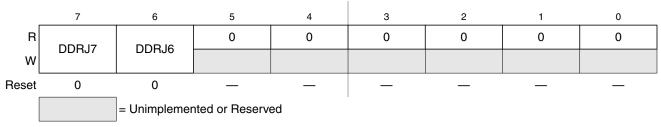

## 2.3.2.5.3 Port J Data Direction Register (DDRJ)

Module Base + 0x002A

Figure 2-34. Port J Data Direction Register (DDRJ)

Read: Anytime. Write: Anytime.

**Table 2-28. DDRJ Field Descriptions**

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–6<br>DDRJ[7:6] | <ul> <li>Data Direction Port J — This register configures port pins J[7:6] as either input or output.</li> <li>DDRJ[7:6] — Data Direction Port J</li> <li>Associated pin is configured as input.</li> <li>Associated pin is configured as output.</li> <li>Note: Due to internal synchronization circuits, it can take up to 2 bus cycles until the correct value is read on PTJ or PTIJ registers, when changing the DDRJ register.</li> </ul> |

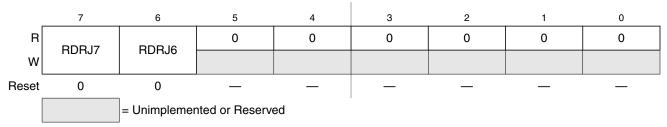

# 2.3.2.5.4 Port J Reduced Drive Register (RDRJ)

Module Base + 0x002B

Figure 2-35. Port J Reduced Drive Register (RDRJ)

Read: Anytime. Write: Anytime.

Table 2-29. RDRJ Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–6<br>RDRJ[7:6] | Reduced Drive Port J — This register configures the drive strength of each port J output pin as either full or reduced. If the port is used as input this bit is ignored.  0 Full drive strength at output.  1 Associated pin drives at about 1/3 of the full drive strength. |

**Table 2-39. Port Reset State Summary**

| Port     | Reset States                           |           |                     |               |           |  |  |

|----------|----------------------------------------|-----------|---------------------|---------------|-----------|--|--|

|          | Data Direction                         | Pull Mode | Reduced Drive       | Wired-OR Mode | Interrupt |  |  |

| Т        | Input                                  | Hi-z      | Disabled            | n/a           | n/a       |  |  |

| S        | Input                                  | Pull up   | Disabled            | Disabled      | n/a       |  |  |

| М        | Input                                  | Pull up   | Disabled            | Disabled      | n/a       |  |  |

| Р        | Input                                  | Hi-z      | Disabled            | n/a           | Disabled  |  |  |

| J        | Input                                  | Hi-z      | Disabled            | n/a           | Disabled  |  |  |

| Α        |                                        | •         |                     | •             |           |  |  |

| В        |                                        | Defer to  | MEDI Block Cuido fo | v dataila     |           |  |  |

| Е        | Refer to MEBI Block Guide for details. |           |                     |               |           |  |  |

|          |                                        |           |                     |               |           |  |  |

| BKGD pin | Refer to BDM Block Guide for details.  |           |                     |               |           |  |  |

# 2.6 Interrupts

Port P and J generate a separate edge sensitive interrupt if enabled.

## 2.6.1 Interrupt Sources

**Table 2-40. Port Integration Module Interrupt Sources**

| Interrupt Source | Interrupt Flag | Local Enable | Global (CCR) Mask |  |

|------------------|----------------|--------------|-------------------|--|

| Port P           | PIFP[7:0]      | PIEP[7:0]    | l Bit             |  |

| Port J           | PIFJ[7:6]      | PIEJ[7:6]    | l Bit             |  |

#### NOTE

Vector addresses and their relative interrupt priority are determined at the MCU level.

# 2.6.2 Recovery from STOP

The PIM can generate wake-up interrupts from STOP on port P and J. For other sources of external interrupts please refer to the respective Block User Guide.

# 2.7 Application Information

It is not recommended to write PORTx and DDRx in a word access. When changing the register pins from inputs to outputs, the data may have extra transitions during the write access. Initialize the port data register before enabling the outputs.

Power consumption will increase the more the voltages on general purpose input pins deviate from the supply voltages towards mid-range because the digital input buffers operate in the linear region.

### Chapter 6 Background Debug Module (BDMV4) Block Description

- Nine hardware commands using free cycles, if available, for minimal CPU intervention

- Hardware commands not requiring active BDM

- 15 firmware commands execute from the standard BDM firmware lookup table

- Instruction tagging capability

- Software control of BDM operation during wait mode

- Software selectable clocks

- When secured, hardware commands are allowed to access the register space in special single-chip mode, if the FLASH and EEPROM erase tests fail.

## 6.1.2 Modes of Operation

BDM is available in all operating modes but must be enabled before firmware commands are executed. Some system peripherals may have a control bit which allows suspending the peripheral function during background debug mode.

## 6.1.2.1 Regular Run Modes

All of these operations refer to the part in run mode. The BDM does not provide controls to conserve power during run mode.

- Normal operation

General operation of the BDM is available and operates the same in all normal modes.

- Special single-chip mode

In special single-chip mode, background operation is enabled and active out of reset. This allows programming a system with blank memory.

- Special peripheral mode

BDM is enabled and active immediately out of reset. BDM can be disabled by clearing the BDMACT bit in the BDM status (BDMSTS) register. The BDM serial system should not be used in special peripheral mode.

### NOTE

The BDM serial system should not be used in special peripheral mode since the CPU, which in other modes interfaces with the BDM to relinquish control of the bus during a free cycle or a steal operation, is not operating in this mode.

• Emulation modes

General operation of the BDM is available and operates the same as in normal modes.

# 6.1.2.2 Secure Mode Operation

If the part is in secure mode, the operation of the BDM is reduced to a small subset of its regular run mode operation. Secure operation prevents access to FLASH or EEPROM other than allowing erasure.

Chapter 6 Background Debug Module (BDMV4) Block Description

### 6.4.8 Hardware Handshake Abort Procedure

The abort procedure is based on the SYNC command. In order to abort a command, which had not issued the corresponding ACK pulse, the host controller should generate a low pulse in the BKGD pin by driving it low for at least 128 serial clock cycles and then driving it high for one serial clock cycle, providing a speedup pulse. By detecting this long low pulse in the BKGD pin, the target executes the SYNC protocol, see Section 6.4.9, "SYNC — Request Timed Reference Pulse," and assumes that the pending command and therefore the related ACK pulse, are being aborted. Therefore, after the SYNC protocol has been completed the host is free to issue new BDM commands.

Although it is not recommended, the host could abort a pending BDM command by issuing a low pulse in the BKGD pin shorter than 128 serial clock cycles, which will not be interpreted as the SYNC command. The ACK is actually aborted when a falling edge is perceived by the target in the BKGD pin. The short abort pulse should have at least 4 clock cycles keeping the BKGD pin low, in order to allow the falling edge to be detected by the target. In this case, the target will not execute the SYNC protocol but the pending command will be aborted along with the ACK pulse. The potential problem with this abort procedure is when there is a conflict between the ACK pulse and the short abort pulse. In this case, the target may not perceive the abort pulse. The worst case is when the pending command is a read command (i.e., READ\_BYTE). If the abort pulse is not perceived by the target the host will attempt to send a new command after the abort pulse was issued, while the target expects the host to retrieve the accessed memory byte. In this case, host and target will run out of synchronism. However, if the command to be aborted is not a read command the short abort pulse could be used. After a command is aborted the target assumes the next falling edge, after the abort pulse, is the first bit of a new BDM command.

### NOTE

The details about the short abort pulse are being provided only as a reference for the reader to better understand the BDM internal behavior. It is not recommended that this procedure be used in a real application.

Because the host knows the target serial clock frequency, the SYNC command (used to abort a command) does not need to consider the lower possible target frequency. In this case, the host could issue a SYNC very close to the 128 serial clock cycles length. Providing a small overhead on the pulse length in order to assure the SYNC pulse will not be misinterpreted by the target. See Section 6.4.9, "SYNC — Request Timed Reference Pulse."

Figure 6-12 shows a SYNC command being issued after a READ\_BYTE, which aborts the READ\_BYTE command. Note that, after the command is aborted a new command could be issued by the host computer.

### NOTE

Figure 6-12 does not represent the signals in a true timing scale

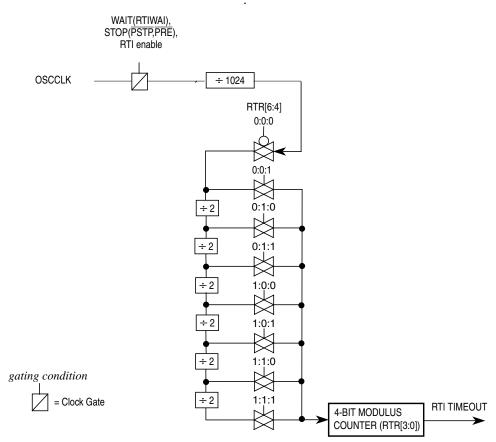

If the PRE bit is set, the RTI will continue to run in pseudo-stop mode.

Figure 9-22. Clock Chain for RTI

# 9.4.7 Modes of Operation

## **9.4.7.1 Normal Mode**

The CRGV4 block behaves as described within this specification in all normal modes.

### 9.4.7.2 Self-Clock Mode

The VCO has a minimum operating frequency,  $f_{SCM}$ . If the external clock frequency is not available due to a failure or due to long crystal start-up time, the bus clock and the core clock are derived from the VCO running at minimum operating frequency; this mode of operation is called self-clock mode. This requires CME = 1 and SCME = 1. If the MCU was clocked by the PLL clock prior to entering self-clock mode, the PLLSEL bit will be cleared. If the external clock signal has stabilized again, the CRG will automatically select OSCCLK to be the system clock and return to normal mode. See Section 9.4.4, "Clock Quality Checker" for more information on entering and leaving self-clock mode.

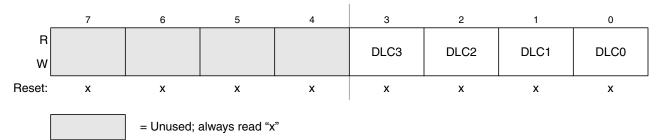

## 10.3.3.3 Data Length Register (DLR)

This register keeps the data length field of the CAN frame.

Module Base + 0x00XB

Figure 10-34. Data Length Register (DLR) — Extended Identifier Mapping

Table 10-31. DLR Register Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>DLC[3:0] | Data Length Code Bits — The data length code contains the number of bytes (data byte count) of the respective message. During the transmission of a remote frame, the data length code is transmitted as programmed while the number of transmitted data bytes is always 0. The data byte count ranges from 0 to 8 for a data frame. Table 10-32 shows the effect of setting the DLC bits. |

**Data Length Code Data Byte** Count DLC<sub>3</sub> DLC2 DLC1 DLC<sub>0</sub>

Table 10-32. Data Length Codes

# 10.3.3.4 Transmit Buffer Priority Register (TBPR)

This register defines the local priority of the associated message buffer. The local priority is used for the internal prioritization process of the MSCAN and is defined to be highest for the smallest binary number. The MSCAN implements the following internal prioritization mechanisms:

- All transmission buffers with a cleared TXEx flag participate in the prioritization immediately before the SOF (start of frame) is sent.

- The transmission buffer with the lowest local priority field wins the prioritization.

#### Chapter 10 Freescale's Scalable Controller Area Network (S12MSCANV2)

- If there are one or more message buffers scheduled for transmission (TXEx = 0), the MSCAN will continue to transmit until all transmit message buffers are empty (TXEx = 1, transmitted successfully or aborted) and then goes into sleep mode.

- If the MSCAN is receiving, it continues to receive and goes into sleep mode as soon as the CAN bus next becomes idle.

- If the MSCAN is neither transmitting nor receiving, it immediately goes into sleep mode.

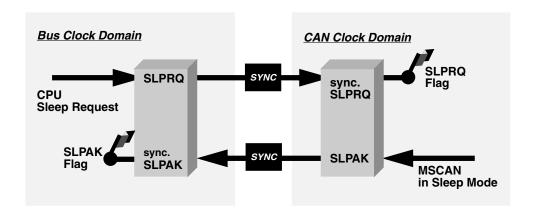

Figure 10-44. Sleep Request / Acknowledge Cycle

#### NOTE

The application software must avoid setting up a transmission (by clearing one or more TXEx flag(s)) and immediately request sleep mode (by setting SLPRQ). Whether the MSCAN starts transmitting or goes into sleep mode directly depends on the exact sequence of operations.

If sleep mode is active, the SLPRQ and SLPAK bits are set (Figure 10-44). The application software must use SLPAK as a handshake indication for the request (SLPRQ) to go into sleep mode.

When in sleep mode (SLPRQ = 1 and SLPAK = 1), the MSCAN stops its internal clocks. However, clocks that allow register accesses from the CPU side continue to run.

If the MSCAN is in bus-off state, it stops counting the 128 occurrences of 11 consecutive recessive bits due to the stopped clocks. The TXCAN pin remains in a recessive state. If RXF = 1, the message can be read and RXF can be cleared. Shifting a new message into the foreground buffer of the receiver FIFO (RxFG) does not take place while in sleep mode.

It is possible to access the transmit buffers and to clear the associated TXE flags. No message abort takes place while in sleep mode.

If the WUPE bit in CANCLT0 is not asserted, the MSCAN will mask any activity it detects on CAN. The RXCAN pin is therefore held internally in a recessive state. This locks the MSCAN in sleep mode (Figure 10-45). WUPE must be set before entering sleep mode to take effect.

### Chapter 12 Pulse-Width Modulator (PWM8B6CV1) Block Description

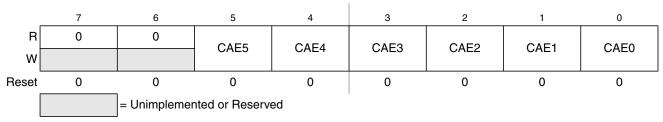

Module Base + 0x0004

Figure 12-7. PWM Center Align Enable Register (PWMCAE)

Read: anytime Write: anytime

## NOTE

Write these bits only when the corresponding channel is disabled.

**Table 12-8. PWMCAE Field Descriptions**

| Field     | Description                                                                                                                                     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>CAE5 | Center Aligned Output Mode on Channel 5  0 Channel 5 operates in left aligned output mode.  1 Channel 5 operates in center aligned output mode. |

| 4<br>CAE4 | Center Aligned Output Mode on Channel 4  0 Channel 4 operates in left aligned output mode.  1 Channel 4 operates in center aligned output mode. |

| 3<br>CAE3 | Center Aligned Output Mode on Channel 3  1 Channel 3 operates in left aligned output mode.  1 Channel 3 operates in center aligned output mode. |

| 2<br>CAE2 | Center Aligned Output Mode on Channel 2  0 Channel 2 operates in left aligned output mode.  1 Channel 2 operates in center aligned output mode. |

| 1<br>CAE1 | Center Aligned Output Mode on Channel 1 0 Channel 1 operates in left aligned output mode. 1 Channel 1 operates in center aligned output mode.   |

| 0<br>CAE0 | Center Aligned Output Mode on Channel 0 0 Channel 0 operates in left aligned output mode. 1 Channel 0 operates in center aligned output mode.   |

# 12.3.2.6 PWM Control Register (PWMCTL)

The PWMCTL register provides for various control of the PWM module.

Table 14-7. Example SPI Baud Rate Selection (25 MHz Bus Clock) (continued)

| SPPR2 | SPPR1 | SPPR0 | SPR2 | SPR1 | SPR0 | Baud Rate<br>Divisor | Baud Rate   |

|-------|-------|-------|------|------|------|----------------------|-------------|

| 1     | 0     | 0     | 1    | 1    | 1    | 1280                 | 19.53 kHz   |

| 1     | 0     | 1     | 0    | 0    | 0    | 12                   | 2.08333 MHz |

| 1     | 0     | 1     | 0    | 0    | 1    | 24                   | 1.04167 MHz |

| 1     | 0     | 1     | 0    | 1    | 0    | 48                   | 520.83 kHz  |

| 1     | 0     | 1     | 0    | 1    | 1    | 96                   | 260.42 kHz  |

| 1     | 0     | 1     | 1    | 0    | 0    | 192                  | 130.21 kHz  |

| 1     | 0     | 1     | 1    | 0    | 1    | 384                  | 65.10 kHz   |

| 1     | 0     | 1     | 1    | 1    | 0    | 768                  | 32.55 kHz   |

| 1     | 0     | 1     | 1    | 1    | 1    | 1536                 | 16.28 kHz   |

| 1     | 1     | 0     | 0    | 0    | 0    | 14                   | 1.78571 MHz |

| 1     | 1     | 0     | 0    | 0    | 1    | 28                   | 892.86 kHz  |

| 1     | 1     | 0     | 0    | 1    | 0    | 56                   | 446.43 kHz  |

| 1     | 1     | 0     | 0    | 1    | 1    | 112                  | 223.21 kHz  |

| 1     | 1     | 0     | 1    | 0    | 0    | 224                  | 111.61 kHz  |

| 1     | 1     | 0     | 1    | 0    | 1    | 448                  | 55.80 kHz   |

| 1     | 1     | 0     | 1    | 1    | 0    | 896                  | 27.90 kHz   |

| 1     | 1     | 0     | 1    | 1    | 1    | 1792                 | 13.95 kHz   |

| 1     | 1     | 1     | 0    | 0    | 0    | 16                   | 1.5625 MHz  |

| 1     | 1     | 1     | 0    | 0    | 1    | 32                   | 781.25 kHz  |

| 1     | 1     | 1     | 0    | 1    | 0    | 64                   | 390.63 kHz  |

| 1     | 1     | 1     | 0    | 1    | 1    | 128                  | 195.31 kHz  |

| 1     | 1     | 1     | 1    | 0    | 0    | 256                  | 97.66 kHz   |

| 1     | 1     | 1     | 1    | 0    | 1    | 512                  | 48.83 kHz   |

| 1     | 1     | 1     | 1    | 1    | 0    | 1024                 | 24.41 kHz   |

| 1     | 1     | 1     | 1    | 1    | 1    | 2048                 | 12.21 kHz   |

## **NOTE**

In slave mode of SPI S-clock speed DIV2 is not supported.

Chapter 17 16 Kbyte Flash Module (S12FTS16KV1)

## 17.1.3 Modes of Operation

See Section 17.4.2, "Operating Modes" for a description of the Flash module operating modes. For program and erase operations, refer to Section 17.4.1, "Flash Command Operations".

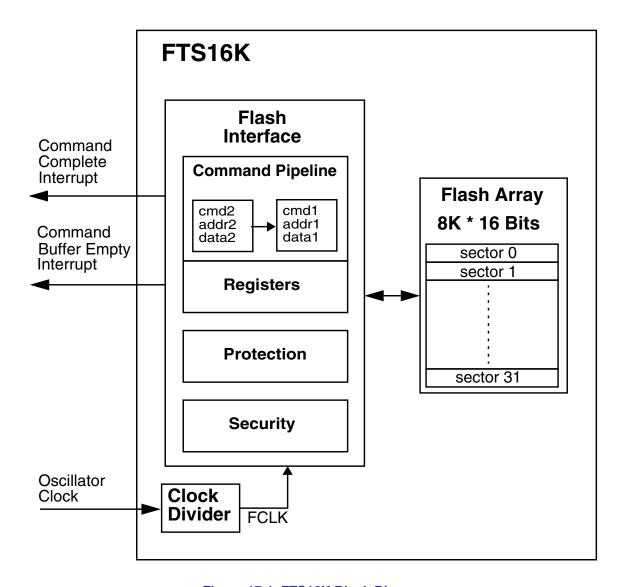

# 17.1.4 Block Diagram

Figure 17-1 shows a block diagram of the FTS16K module.

Figure 17-1. FTS16K Block Diagram

# 17.2 External Signal Description

The FTS16K module contains no signals that connect off-chip.

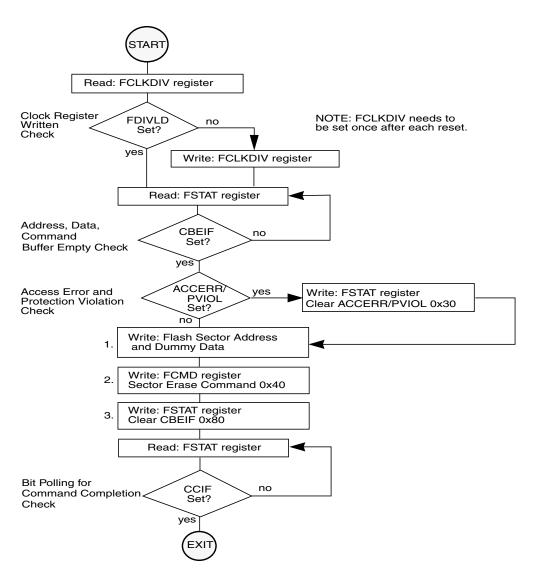

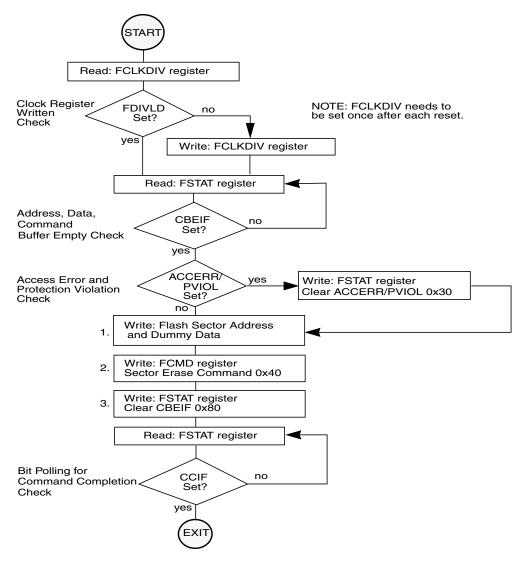

### 17.4.1.3.3 Sector Erase Command

The sector erase operation will erase all addresses in a 512 byte sector of the Flash array using an embedded algorithm.

An example flow to execute the sector erase operation is shown in Figure 17-24. The sector erase command write sequence is as follows:

- 1. Write to a Flash array address to start the command write sequence for the sector erase command. The Flash address written determines the sector to be erased while MCU address bits [8:0] and the data written are ignored.

- 2. Write the sector erase command, 0x40, to the FCMD register.

- 3. Clear the CBEIF flag in the FSTAT register by writing a 1 to CBEIF to launch the sector erase command.

If a Flash sector to be erased is in a protected area of the Flash array, the PVIOL flag in the FSTAT register will set and the sector erase command will not launch. Once the sector erase command has successfully launched, the CCIF flag in the FSTAT register will set after the sector erase operation has completed unless a new command write sequence has been buffered.

### Chapter 18 32 Kbyte Flash Module (S12FTS32KV1)

Figure 18-24. Example Sector Erase Command Flow

addresses sequentially staring with 0xFF00-0xFF01 and ending with 0xFF06-0xFF07. The values 0x0000 and 0xFFFF are not permitted as keys. When the KEYACC bit is set, reads of the Flash array will return invalid data.

The user code stored in the Flash array must have a method of receiving the backdoor key from an external stimulus. This external stimulus would typically be through one of the on-chip serial ports.

If KEYEN[1:0] = 1:0 in the FSEC register, the MCU can be unsecured by the backdoor key access sequence described below:

- 1. Set the KEYACC bit in the FCNFG register

- 2. Write the correct four 16-bit words to Flash addresses 0xFF00–0xFF07 sequentially starting with 0xFF00

- 3. Clear the KEYACC bit in the FCNFG register

- 4. If all four 16-bit words match the backdoor key stored in Flash addresses 0xFF00–0xFF07, the MCU is unsecured and bits SEC[1:0] in the FSEC register are forced to the unsecure state of 1:0

The backdoor key access sequence is monitored by the internal security state machine. An illegal operation during the backdoor key access sequence will cause the security state machine to lock, leaving the MCU in the secured state. A reset of the MCU will cause the security state machine to exit the lock state and allow a new backdoor key access sequence to be attempted. The following illegal operations will lock the security state machine:

- 1. If any of the four 16-bit words does not match the backdoor key programmed in the Flash array

- 2. If the four 16-bit words are written in the wrong sequence

- 3. If more than four 16-bit words are written

- 4. If any of the four 16-bit words written are 0x0000 or 0xFFFF

- 5. If the KEYACC bit does not remain set while the four 16-bit words are written

After the backdoor key access sequence has been correctly matched, the MCU will be unsecured. The Flash security byte can be programmed to the unsecure state, if desired.

In the unsecure state, the user has full control of the contents of the four word backdoor key by programming bytes 0xFF00–0xFF07 of the Flash configuration field.

The security as defined in the Flash security/options byte at address 0xFF0F is not changed by using the backdoor key access sequence to unsecure. The backdoor key stored in addresses 0xFF00–0xFF07 is unaffected by the backdoor key access sequence. After the next reset sequence, the security state of the Flash module is determined by the Flash security/options byte at address 0xFF0F. The backdoor key access sequence has no effect on the program and erase protection defined in the FPROT register.

It is not possible to unsecure the MCU in special single chip mode by executing the backdoor key access sequence in background debug mode.

**Table 19-5. FSEC Field Descriptions**

| Field             | Description                                                                                                                                                                                           |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–6<br>KEYEN[1:0] | <b>Backdoor Key Security Enable Bits</b> — The KEYEN[1:0] bits define the enabling of the backdoor key access to the Flash module as shown in Table 19-6.                                             |

| 5–2<br>NV[5:2]    | Nonvolatile Flag Bits — The NV[5:2] bits are available to the user as nonvolatile flags.                                                                                                              |

| 1–0<br>SEC[1:0]   | Flash Security Bits — The SEC[1:0] bits define the security state of the MCU as shown in Table 19-7. If the Flash module is unsecured using backdoor key access, the SEC[1:0] bits are forced to 1:0. |

Table 19-6. Flash KEYEN States

| KEYEN[1:0]        | Status of Backdoor Key Access |

|-------------------|-------------------------------|

| 00                | DISABLED                      |

| 01 <sup>(1)</sup> | DISABLED                      |

| 10                | ENABLED                       |

| 11                | DISABLED                      |

<sup>1.</sup> Preferred KEYEN state to disable Backdoor Key Access.

Table 19-7. Flash Security States

| SEC[1:0]          | Status of Security |

|-------------------|--------------------|

| 00                | Secured            |

| 01 <sup>(1)</sup> | Secured            |

| 10                | Unsecured          |

| 11                | Secured            |

<sup>1.</sup> Preferred SEC state to set MCU to secured state.

The security function in the Flash module is described in Section 19.4.3, "Flash Module Security".

## 19.3.2.3 RESERVED1

This register is reserved for factory testing and is not accessible to the user.

Module Base + 0x0002

Figure 19-8. RESERVED1

All bits read 0 and are not writable.

Figure 20-26. Example Sector Erase Command Flow

#### Chapter 20 96 Kbyte Flash Module (S12FTS96KV1)

addresses sequentially staring with 0xFF00-0xFF01 and ending with 0xFF06-0xFF07. The values 0x0000 and 0xFFFF are not permitted as keys. When the KEYACC bit is set, reads of the Flash array will return invalid data.

The user code stored in the Flash array must have a method of receiving the backdoor key from an external stimulus. This external stimulus would typically be through one of the on-chip serial ports.

If KEYEN[1:0] = 1:0 in the FSEC register, the MCU can be unsecured by the backdoor key access sequence described below:

- 1. Set the KEYACC bit in the FCNFG register

- 2. Write the correct four 16-bit words to Flash addresses 0xFF00–0xFF07 sequentially starting with 0xFF00

- 3. Clear the KEYACC bit in the FCNFG register

- 4. If all four 16-bit words match the backdoor key stored in Flash addresses 0xFF00–0xFF07, the MCU is unsecured and bits SEC[1:0] in the FSEC register are forced to the unsecure state of 1:0

The backdoor key access sequence is monitored by the internal security state machine. An illegal operation during the backdoor key access sequence will cause the security state machine to lock, leaving the MCU in the secured state. A reset of the MCU will cause the security state machine to exit the lock state and allow a new backdoor key access sequence to be attempted. The following illegal operations will lock the security state machine:

- 1. If any of the four 16-bit words does not match the backdoor key programmed in the Flash array

- 2. If the four 16-bit words are written in the wrong sequence

- 3. If more than four 16-bit words are written

- 4. If any of the four 16-bit words written are 0x0000 or 0xFFFF

- 5. If the KEYACC bit does not remain set while the four 16-bit words are written

After the backdoor key access sequence has been correctly matched, the MCU will be unsecured. The Flash security byte can be programmed to the unsecure state, if desired.

In the unsecure state, the user has full control of the contents of the four word backdoor key by programming bytes 0xFF00–0xFF07 of the Flash configuration field.

The security as defined in the Flash security/options byte at address 0xFF0F is not changed by using the backdoor key access sequence to unsecure. The backdoor key stored in addresses 0xFF00–0xFF07 is unaffected by the backdoor key access sequence. After the next reset sequence, the security state of the Flash module is determined by the Flash security/options byte at address 0xFF0F. The backdoor key access sequence has no effect on the program and erase protection defined in the FPROT register.

It is not possible to unsecure the MCU in special single chip mode by executing the backdoor key access sequence in background debug mode.

**Appendix A Electrical Characteristics**

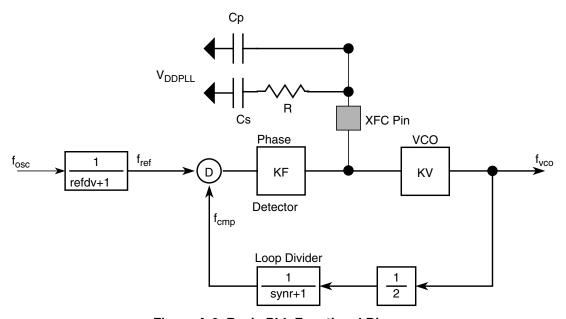

## A.4.3 Phase Locked Loop

The oscillator provides the reference clock for the PLL. The PLL's Voltage Controlled Oscillator (VCO) is also the system clock source in self clock mode.

## A.4.3.1 XFC Component Selection

This section describes the selection of the XFC components to achieve a good filter characteristics.

Figure A-2. Basic PLL Functional Diagram

The following procedure can be used to calculate the resistance and capacitance values using typical values for  $K_1$ ,  $f_1$  and  $i_{ch}$  from Table A-17.

The grey boxes show the calculation for  $f_{VCO} = 50 MHz$  and  $f_{ref} = 1 MHz$ . E.g., these frequencies are used for  $f_{OSC} = 4 MHz$  and a 25MHz bus clock.

The VCO Gain at the desired VCO frequency is approximated by:

$$K_V = K_1 \cdot e^{\frac{(f_1 - f_{vco})}{K_1 \cdot 1V}} = -100 \cdot e^{\frac{(60 - 50)}{-100}} = -90.48MHz/V$$

The phase detector relationship is given by:

$$K_{\Phi} = -|i_{ch}| \cdot K_{V}$$

= 316.7Hz/ $\Omega$

i<sub>ch</sub> is the current in tracking mode.

**Appendix A Electrical Characteristics**

## A.5.1.1 Single Word Programming

The programming time for single word programming is dependant on the bus frequency as a well as on the frequency  $f_{NVMOP}$  and can be calculated according to the following formula.

$$t_{swpgm} = 9 \cdot \frac{1}{f_{NVMOP}} + 25 \cdot \frac{1}{f_{bus}}$$

## A.5.1.2 Row Programming

Generally the time to program a consecutive word can be calculated as:

$$t_{bwpgm} = 4 \cdot \frac{1}{f_{NVMOP}} + 9 \cdot \frac{1}{f_{bus}}$$

For the C16, GC16, C32 and GC32 device flash arrays, where up to 32 words in a row can be programmed consecutively by keeping the command pipeline filled, the time to program a whole row is:

$$t_{brpgm} = t_{swpgm} + 31 \cdot t_{bwpgm}$$

For the C64, GC64, C96, C128 and GC128 device flash arrays, where up to 64 words in a row can be programmed consecutively by keeping the command pipeline filled, the time to program a whole row is:

$$t_{brpgm} = t_{swpgm} + 63 \cdot t_{bwpgm}$$

Row programming is more than 2 times faster than single word programming.

### A.5.1.3 Sector Erase

Erasing either a 512 byte or 1024 byte Flash sector takes:

$$t_{era} \approx 4000 \cdot \frac{1}{f_{NVMOP}}$$

The setup times can be ignored for this operation.

### A.5.1.4 Mass Erase

Erasing a NVM block takes:

$$t_{mass} \approx 20000 \cdot \frac{1}{f_{NVMOP}}$$

This is independent of sector size.

The setup times can be ignored for this operation.