Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HCS12                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                              |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 35                                                                     |

| Program Memory Size        | 96KB (96K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.5V                                                           |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 52-LQFP                                                                |

| Supplier Device Package    | 52-TQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12c96cpber |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Appendix E | Ordering Information |  |

|------------|----------------------|--|

|------------|----------------------|--|

Chapter 1 MC9S12C and MC9S12GC Device Overview (MC9S12C128)

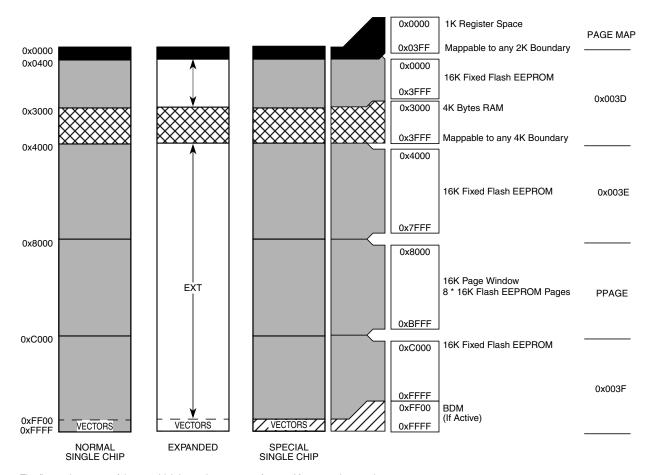

0x0000-0x03FF: Register Space

0x0000-0x0FFF: 4K RAM (only 3K visible 0x0400-0x0FFF)

Flash erase sector size is 1024 bytes

Figure 1-2. MC9S12C128 and MC9S12GC128 User Configurable Memory Map

Chapter 3 Module Mapping Control (MMCV4) Block Description

**Table 3-10. MEMSIZ0 Field Descriptions**

| Field | Description                                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|

|       | Allocated System FLASH or ROM Physical Memory Space — The allocated system FLASH or ROM physical memory space is as given in Table 3-11. |

|       | Allocated Off-Chip FLASH or ROM Memory Space — The allocated off-chip FLASH or ROM memory space size is as given in Table 3-12.          |

Table 3-11. Allocated FLASH/ROM Physical Memory Space

| rom_sw1:rom_sw0 | Allocated FLASH<br>or ROM Space |

|-----------------|---------------------------------|

| 00              | 0K byte                         |

| 01              | 16K bytes                       |

| 10              | 48K bytes <sup>(1)</sup>        |

| 11              | 64K bytes <sup>(1)</sup>        |

#### NOTES:

**Table 3-12. Allocated Off-Chip Memory Options**

| pag_sw1:pag_sw0 | Off-Chip Space | On-Chip Space |

|-----------------|----------------|---------------|

| 00              | 876K bytes     | 128K bytes    |

| 01              | 768K bytes     | 256K bytes    |

| 10              | 512K bytes     | 512K bytes    |

| 11              | 0K byte        | 1M byte       |

## **NOTE**

As stated, the bits in this register provide read visibility to the system memory space and on-chip/off-chip partitioning allocations defined at system integration. The actual array size for any given type of memory block may differ from the allocated size. Please refer to the device overview chapter for actual sizes.

<sup>1.</sup> The ROMHM software bit in the MISC register determines the accessibility of the FLASH/ROM memory space. Please refer to Section 3.3.2.8, "Memory Size Register 1 (MEMSIZ1)," for a detailed functional description of the ROMHM bit.

**Program Space** PIX5 PIX4 PIX3 PIX2 PIX1 PIX<sub>0</sub> Selected 16K page 0 0 0 0 0 0 0 0 0 0 1 16K page 1 16K page 2 0 0 0 0 1 0 0 0 0 0 1 1 16K page 3 0 16K page 60 1 1 1 1 0 1 1 1 0 16K page 61 1 1 1 1 1 0 16K page 62 1 1 1 1 16K page 63

Table 3-14. Program Page Index Register Bits

# 3.4 Functional Description

The MMC sub-block performs four basic functions of the core operation: bus control, address decoding and select signal generation, memory expansion, and security decoding for the system. Each aspect is described in the following subsections.

### 3.4.1 Bus Control

The MMC controls the address bus and data buses that interface the core with the rest of the system. This includes the multiplexing of the input data buses to the core onto the main CPU read data bus and control of data flow from the CPU to the output address and data buses of the core. In addition, the MMC manages all CPU read data bus swapping operations.

# 3.4.2 Address Decoding

As data flows on the core address bus, the MMC decodes the address information, determines whether the internal core register or firmware space, the peripheral space or a memory register or array space is being addressed and generates the correct select signal. This decoding operation also interprets the mode of operation of the system and the state of the mapping control registers in order to generate the proper select. The MMC also generates two external chip select signals, emulation chip select  $(\overline{ECS})$  and external chip select  $(\overline{XCS})$ .

# 3.4.2.1 Select Priority and Mode Considerations

Although internal resources such as control registers and on-chip memory have default addresses, each can be relocated by changing the default values in control registers. Normally, I/O addresses, control registers,

These register locations are not used (reserved). All unused registers and bits in this block return logic 0s when read. Writes to these registers have no effect.

These registers are not in the on-chip map in special peripheral mode.

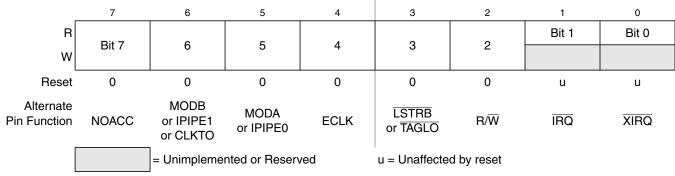

# 4.3.2.6 Port E Data Register (PORTE)

Module Base + 0x0008

Starting address location affected by INITRG register setting.

Figure 4-10. Port E Data Register (PORTE)

Read: Anytime when register is in the map

Write: Anytime when register is in the map

Port E is associated with external bus control signals and interrupt inputs. These include mode select (MODB/IPIPE1, MODA/IPIPE0), E clock, size ( $\overline{LSTRB}/\overline{TAGLO}$ ), read/write (R/ $\overline{W}$ ),  $\overline{IRQ}$ , and  $\overline{XIRQ}$ . When not used for one of these specific functions, port E pins 7:2 can be used as general-purpose I/O and pins 1:0 can be used as general-purpose input. The port E assignment register (PEAR) selects the function of each pin and DDRE determines whether each pin is an input or output when it is configured to be general-purpose I/O. DDRE also determines the source of data for a read of PORTE.

Some of these pins have software selectable pull resistors.  $\overline{IRQ}$  and  $\overline{XIRQ}$  can only be pulled up whereas the polarity of the PE7, PE4, PE3, and PE2 pull resistors are determined by chip integration. Please refer to the device overview chapter (Signal Property Summary) to determine the polarity of these resistors. A single control bit enables the pull devices for all of these pins when they are configured as inputs.

This register is not in the on-chip map in special peripheral mode or in expanded modes when the EME bit is set. Therefore, these accesses will be echoed externally.

#### NOTE

It is unwise to write PORTE and DDRE as a word access. If you are changing port E pins from being inputs to outputs, the data may have extra transitions during the write. It is best to initialize PORTE before enabling as outputs.

Chapter 6 Background Debug Module (BDMV4) Block Description

# 6.4 Functional Description

The BDM receives and executes commands from a host via a single wire serial interface. There are two types of BDM commands, namely, hardware commands and firmware commands.

Hardware commands are used to read and write target system memory locations and to enter active background debug mode, see Section 6.4.3, "BDM Hardware Commands." Target system memory includes all memory that is accessible by the CPU.

Firmware commands are used to read and write CPU resources and to exit from active background debug mode, see Section 6.4.4, "Standard BDM Firmware Commands." The CPU resources referred to are the accumulator (D), X index register (X), Y index register (Y), stack pointer (SP), and program counter (PC).

Hardware commands can be executed at any time and in any mode excluding a few exceptions as highlighted, see Section 6.4.3, "BDM Hardware Commands." Firmware commands can only be executed when the system is in active background debug mode (BDM).

# 6.4.1 Security

If the user resets into special single-chip mode with the system secured, a secured mode BDM firmware lookup table is brought into the map overlapping a portion of the standard BDM firmware lookup table. The secure BDM firmware verifies that the on-chip EEPROM and FLASH EEPROM are erased. This being the case, the UNSEC bit will get set. The BDM program jumps to the start of the standard BDM firmware and the secured mode BDM firmware is turned off and all BDM commands are allowed. If the EEPROM or FLASH do not verify as erased, the BDM firmware sets the ENBDM bit, without asserting UNSEC, and the firmware enters a loop. This causes the BDM hardware commands to become enabled, but does not enable the firmware commands. This allows the BDM hardware to be used to erase the EEPROM and FLASH. After execution of the secure firmware, regardless of the results of the erase tests, the CPU registers, INITEE and PPAGE, will no longer be in their reset state.

# 6.4.2 Enabling and Activating BDM

The system must be in active BDM to execute standard BDM firmware commands. BDM can be activated only after being enabled. BDM is enabled by setting the ENBDM bit in the BDM status (BDMSTS) register. The ENBDM bit is set by writing to the BDM status (BDMSTS) register, via the single-wire interface, using a hardware command such as WRITE\_BD\_BYTE.

After being enabled, BDM is activated by one of the following<sup>1</sup>:

- Hardware BACKGROUND command

- BDM external instruction tagging mechanism

- CPU BGND instruction

- Breakpoint sub-block's force or tag mechanism<sup>2</sup>

When BDM is activated, the CPU finishes executing the current instruction and then begins executing the firmware in the standard BDM firmware lookup table. When BDM is activated by the breakpoint sub-

- 1. BDM is enabled and active immediately out of special single-chip reset.

- 2. This method is only available on systems that have a a breakpoint or a debug sub-block.

| Address | Name    |   | Bit 7     | 6          | 5           | 4       | 3     | 2     | 1         | Bit 0 |

|---------|---------|---|-----------|------------|-------------|---------|-------|-------|-----------|-------|

|         |         | R | 0         | 0          | 0           | 0       | 0     | 0     | BIT 9 MSB | BIT 8 |

| 0x001C  | ATDDR6H |   | 0         | 0          | 0           | 0       | 0     | 0     | 0         | 0     |

|         |         | W |           |            |             |         |       |       |           |       |

|         |         | R | BIT 7     | BIT 6      | BIT 5       | BIT 4   | BIT 3 | BIT 2 | BIT 1     | BIT 0 |

| 0x001D  | ATDDR6L |   | BIT 7 MSB | BIT 6      | BIT 5       | BIT 4   | BIT 3 | BIT 2 | BIT 1     | BIT 0 |

|         |         | W |           |            |             |         |       |       |           |       |

|         |         | R | 0         | 0          | 0           | 0       | 0     | 0     | BIT 9 MSB | BIT 8 |

| 0x001E  | ATDDR7H |   | 0         | 0          | 0           | 0       | 0     | 0     | 0         | 0     |

|         |         | W |           |            |             |         |       |       |           |       |

|         |         | R | BIT 7     | BIT 6      | BIT 5       | BIT 4   | BIT 3 | BIT 2 | BIT 1     | BIT 0 |

| 0x001F  | ATDDR7L |   | BIT 7 MSB | BIT 6      | BIT 5       | BIT 4   | BIT 3 | BIT 2 | BIT 1     | BIT 0 |

|         |         | W |           |            |             |         |       |       |           |       |

|         |         |   |           | = Unimpler | nented or R | eserved |       |       |           |       |

Figure 8-2. ATD Register Summary (Sheet 4 of 4)

## **NOTE**

Register Address = Module Base Address + Address Offset, where the Module Base Address is defined at the MCU level and the Address Offset is defined at the module level.

Definition." All reset sources are listed in Table 9-13. Refer to the device overview chapter for related vector addresses and priorities.

**Table 9-13. Reset Summary**

| Reset Source        | Local Enable             |  |  |

|---------------------|--------------------------|--|--|

| Power-on Reset      | None                     |  |  |

| Low Voltage Reset   | None                     |  |  |

| External Reset      | None                     |  |  |

| Clock Monitor Reset | PLLCTL (CME=1, SCME=0)   |  |  |

| COP Watchdog Reset  | COPCTL (CR[2:0] nonzero) |  |  |

The reset sequence is initiated by any of the following events:

- Low level is detected at the  $\overline{RESET}$  pin (external reset).

- Power on is detected.

- Low voltage is detected.

- COP watchdog times out.

- Clock monitor failure is detected and self-clock mode was disabled (SCME = 0).

Upon detection of any reset event, an internal circuit drives the  $\overline{RESET}$  pin low for 128 SYSCLK cycles (see Figure 9-25). Because entry into reset is asynchronous it does not require a running SYSCLK. However, the internal reset circuit of the CRGV4 cannot sequence out of current reset condition without a running SYSCLK. The number of 128 SYSCLK cycles might be increased by n = 3 to 6 additional SYSCLK cycles depending on the internal synchronization latency. After 128+n SYSCLK cycles the  $\overline{RESET}$  pin is released. The reset generator of the CRGV4 waits for additional 64 SYSCLK cycles and then samples the RESET pin to determine the originating source. Table 9-14 shows which vector will be fetched.

Table 9-14. Reset Vector Selection

| Sampled RESET Pin<br>(64 Cycles After<br>Release) | Clock Monitor<br>Reset Pending | COP Reset<br>Pending | Vector Fetch                                      |

|---------------------------------------------------|--------------------------------|----------------------|---------------------------------------------------|

| 1                                                 | 0                              | 0                    | POR / LVR / External Reset                        |

| 1                                                 | 1                              | Х                    | Clock Monitor Reset                               |

| 1                                                 | 0                              | 1                    | COP Reset                                         |

| 0                                                 | Х                              | Х                    | POR / LVR / External Reset with rise of RESET pin |

### **NOTE**

External circuitry connected to the RESET pin should not include a large capacitance that would interfere with the ability of this signal to rise to a valid logic 1 within 64 SYSCLK cycles after the low drive is released.

## **NOTE**

The CANCTL0 register, except WUPE, INITRQ, and SLPRQ, is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1). This register is writable again as soon as the initialization mode is exited (INITRQ = 0 and INITAK = 0).

Read: Anytime

Write: Anytime when out of initialization mode; exceptions are read-only RXACT and SYNCH, RXFRM (which is set by the module only), and INITRQ (which is also writable in initialization mode).

Table 10-1. CANCTL0 Register Field Descriptions

| Field                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RXFRM <sup>(1)</sup> | Received Frame Flag — This bit is read and clear only. It is set when a receiver has received a valid message correctly, independently of the filter configuration. After it is set, it remains set until cleared by software or reset. Clearing is done by writing a 1. Writing a 0 is ignored. This bit is not valid in loopback mode.  O No valid message was received since last clearing this flag  A valid message was received since last clearing of this flag                                                                                                                                             |

| 6<br>RXACT                | Receiver Active Status — This read-only flag indicates the MSCAN is receiving a message. The flag is controlled by the receiver front end. This bit is not valid in loopback mode.  0 MSCAN is transmitting or idle <sup>2</sup> 1 MSCAN is receiving a message (including when arbitration is lost) <sup>(2)</sup>                                                                                                                                                                                                                                                                                                |

| 5<br>CSWAI <sup>(3)</sup> | CAN Stops in Wait Mode — Enabling this bit allows for lower power consumption in wait mode by disabling all the clocks at the CPU bus interface to the MSCAN module.  O The module is not affected during wait mode  The module ceases to be clocked during wait mode                                                                                                                                                                                                                                                                                                                                              |

| 4<br>SYNCH                | Synchronized Status — This read-only flag indicates whether the MSCAN is synchronized to the CAN bus and able to participate in the communication process. It is set and cleared by the MSCAN.  O MSCAN is not synchronized to the CAN bus  MSCAN is synchronized to the CAN bus                                                                                                                                                                                                                                                                                                                                   |

| 3<br>TIME                 | Timer Enable — This bit activates an internal 16-bit wide free running timer which is clocked by the bit clock rate. If the timer is enabled, a 16-bit time stamp will be assigned to each transmitted/received message within the active TX/RX buffer. Right after the EOF of a valid message on the CAN bus, the time stamp is written to the highest bytes (0x000E, 0x000F) in the appropriate buffer (see Section 10.3.3, "Programmer's Model of Message Storage"). The internal timer is reset (all bits set to 0) when disabled. This bit is held low in initialization mode.  1 Enable internal MSCAN timer |

| 2<br>WUPE <sup>(4)</sup>  | Wake-Up Enable — This configuration bit allows the MSCAN to restart from sleep mode when traffic on CAN is detected (see Section 10.4.5.4, "MSCAN Sleep Mode").  0 Wake-up disabled — The MSCAN ignores traffic on CAN  1 Wake-up enabled — The MSCAN is able to restart                                                                                                                                                                                                                                                                                                                                           |

Chapter 10 Freescale's Scalable Controller Area Network (S12MSCANV2)

#### Table 10-1. CANCTLO Register Field Descriptions (continued)

| Field                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>SLPRQ <sup>(5)</sup>      | Sleep Mode Request — This bit requests the MSCAN to enter sleep mode, which is an internal power saving mode (see Section 10.4.5.4, "MSCAN Sleep Mode"). The sleep mode request is serviced when the CAN bus is idle, i.e., the module is not receiving a message and all transmit buffers are empty. The module indicates entry to sleep mode by setting SLPAK = 1 (see Section 10.3.2.2, "MSCAN Control Register 1 (CANCTL1)"). SLPRQ cannot be set while the WUPIF flag is set (see Section 10.3.2.5, "MSCAN Receiver Flag Register (CANRFLG)"). Sleep mode will be active until SLPRQ is cleared by the CPU or, depending on the setting of WUPE, the MSCAN detects activity on the CAN bus and clears SLPRQ itself.  O Running — The MSCAN functions normally  Sleep mode request — The MSCAN enters sleep mode when CAN bus idle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0<br>INITRQ <sup>(6),(7)</sup> | Initialization Mode Request — When this bit is set by the CPU, the MSCAN skips to initialization mode (see Section 10.4.5.5, "MSCAN Initialization Mode"). Any ongoing transmission or reception is aborted and synchronization to the CAN bus is lost. The module indicates entry to initialization mode by setting INITAK = 1 (Section 10.3.2.2, "MSCAN Control Register 1 (CANCTL1)").  The following registers enter their hard reset state and restore their default values: CANCTL0 <sup>(8)</sup> , CANRFLG <sup>(9)</sup> , CANRIER <sup>(10)</sup> , CANTFLG, CANTIER, CANTARQ, CANTAAK, and CANTBSEL.  The registers CANCTL1, CANBTRO, CANBTR1, CANIDAC, CANIDARO-7, and CANIDMRO-7 can only be written by the CPU when the MSCAN is in initialization mode (INITRQ = 1 and INITAK = 1). The values of the error counters are not affected by initialization mode.  When this bit is cleared by the CPU, the MSCAN restarts and then tries to synchronize to the CAN bus. If the MSCAN is not in bus-off state, it synchronizes after 11 consecutive recessive bits on the CAN bus; if the MSCAN is in bus-off state, it continues to wait for 128 occurrences of 11 consecutive recessive bits.  Writing to other bits in CANCTLO, CANRFLG, CANRIER, CANTFLG, or CANTIER must be done only after initialization mode is exited, which is INITRQ = 0 and INITAK = 0.  0 Normal operation  1 MSCAN in initialization mode |

- 1. The MSCAN must be in normal mode for this bit to become set.

- 2. See the Bosch CAN 2.0A/B specification for a detailed definition of transmitter and receiver states.

- 3. In order to protect from accidentally violating the CAN protocol, the TXCAN pin is immediately forced to a recessive state when the CPU enters wait (CSWAI = 1) or stop mode (see Section 10.4.5.2, "Operation in Wait Mode" and Section 10.4.5.3, "Operation in Stop Mode").

- 4. The CPU has to make sure that the WUPE register and the WUPIE wake-up interrupt enable register (see Section 10.3.2.6, "MSCAN Receiver Interrupt Enable Register (CANRIER)) is enabled, if the recovery mechanism from stop or wait is required.

- 5. The CPU cannot clear SLPRQ before the MSCAN has entered sleep mode (SLPRQ = 1 and SLPAK = 1).

- 6. The CPU cannot clear INITRQ before the MSCAN has entered initialization mode (INITRQ = 1 and INITAK = 1).

- 7. In order to protect from accidentally violating the CAN protocol, the TXCAN pin is immediately forced to a recessive state when the initialization mode is requested by the CPU. Thus, the recommended procedure is to bring the MSCAN into sleep mode (SLPRQ = 1 and SLPAK = 1) before requesting initialization mode.

- 8. Not including WUPE, INITRQ, and SLPRQ.

- 9. TSTAT1 and TSTAT0 are not affected by initialization mode.

- 10. RSTAT1 and RSTAT0 are not affected by initialization mode.

# 10.3.2.2 MSCAN Control Register 1 (CANCTL1)

The CANCTL1 register provides various control bits and handshake status information of the MSCAN module as described below.

#### Chapter 10 Freescale's Scalable Controller Area Network (S12MSCANV2)

Module Base + 0x00X3

Figure 10-32. Identifier Register 3 — Standard Mapping

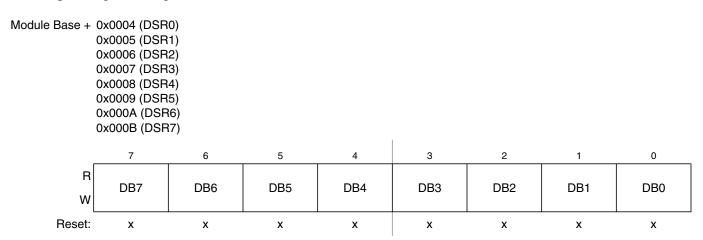

# 10.3.3.2 Data Segment Registers (DSR0-7)

The eight data segment registers, each with bits DB[7:0], contain the data to be transmitted or received. The number of bytes to be transmitted or received is determined by the data length code in the corresponding DLR register.

Figure 10-33. Data Segment Registers (DSR0-DSR7) — Extended Identifier Mapping

Table 10-30. DSR0-DSR7 Register Field Descriptions

| Field          | Description   |

|----------------|---------------|

| 7:0<br>DB[7:0] | Data bits 7:0 |

Chapter 10 Freescale's Scalable Controller Area Network (S12MSCANV2)

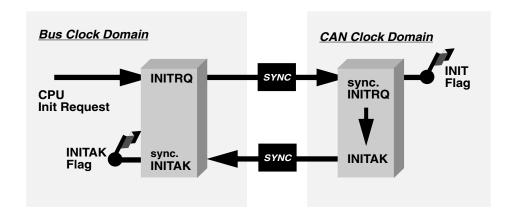

## 10.4.5.5 MSCAN Initialization Mode

In initialization mode, any on-going transmission or reception is immediately aborted and synchronization to the CAN bus is lost, potentially causing CAN protocol violations. To protect the CAN bus system from fatal consequences of violations, the MSCAN immediately drives the TXCAN pin into a recessive state.

#### NOTE

The user is responsible for ensuring that the MSCAN is not active when initialization mode is entered. The recommended procedure is to bring the MSCAN into sleep mode (SLPRQ = 1 and SLPAK = 1) before setting the INITRQ bit in the CANCTL0 register. Otherwise, the abort of an on-going message can cause an error condition and can impact other CAN bus devices.

In initialization mode, the MSCAN is stopped. However, interface registers remain accessible. This mode is used to reset the CANCTL0, CANRFLG, CANRIER, CANTFLG, CANTIER, CANTARQ, CANTAAK, and CANTBSEL registers to their default values. In addition, the MSCAN enables the configuration of the CANBTR0, CANBTR1 bit timing registers; CANIDAC; and the CANIDAR, CANIDMR message filters. See Section 10.3.2.1, "MSCAN Control Register 0 (CANCTL0)," for a detailed description of the initialization mode.

Figure 10-46. Initialization Request/Acknowledge Cycle

Due to independent clock domains within the MSCAN, INITRQ must be synchronized to all domains by using a special handshake mechanism. This handshake causes additional synchronization delay (see Section Figure 10-46., "Initialization Request/Acknowledge Cycle").

If there is no message transfer ongoing on the CAN bus, the minimum delay will be two additional bus clocks and three additional CAN clocks. When all parts of the MSCAN are in initialization mode, the INITAK flag is set. The application software must use INITAK as a handshake indication for the request (INITRQ) to go into initialization mode.

### NOTE

The CPU cannot clear INITRQ before initialization mode (INITRQ = 1 and INITAK = 1) is active.

### Chapter 12 Pulse-Width Modulator (PWM8B6CV1) Block Description

# Table 12-1. PWM8B6CV1 Memory Map

| Address<br>Offset | Register                                               | Access |

|-------------------|--------------------------------------------------------|--------|

| 0x0000            | PWM Enable Register (PWME)                             | R/W    |

| 0x0001            | PWM Polarity Register (PWMPOL)                         | R/W    |

| 0x0002            | PWM Clock Select Register (PWMCLK)                     | R/W    |

| 0x0003            | PWM Prescale Clock Select Register (PWMPRCLK)          | R/W    |

| 0x0004            | PWM Center Align Enable Register (PWMCAE)              | R/W    |

| 0x0005            | PWM Control Register (PWMCTL)                          | R/W    |

| 0x0006            | PWM Test Register (PWMTST) <sup>(1)</sup>              | R/W    |

| 0x0007            | PWM Prescale Counter Register (PWMPRSC) <sup>(2)</sup> | R/W    |

| 0x0008            | PWM Scale A Register (PWMSCLA)                         | R/W    |

| 0x0009            | PWM Scale B Register (PWMSCLB)                         | R/W    |

| 0x000A            | PWM Scale A Counter Register (PWMSCNTA) <sup>(3)</sup> | R/W    |

| 0x000B            | PWM Scale B Counter Register (PWMSCNTB) <sup>(4)</sup> | R/W    |

| 0x000C            | PWM Channel 0 Counter Register (PWMCNT0)               | R/W    |

| 0x000D            | PWM Channel 1 Counter Register (PWMCNT1)               | R/W    |

| 0x000E            | PWM Channel 2 Counter Register (PWMCNT2)               | R/W    |

| 0x000F            | PWM Channel 3 Counter Register (PWMCNT3)               | R/W    |

| 0x0010            | PWM Channel 4 Counter Register (PWMCNT4)               | R/W    |

| 0x0011            | PWM Channel 5 Counter Register (PWMCNT5)               | R/W    |

| 0x0012            | PWM Channel 0 Period Register (PWMPER0)                | R/W    |

| 0x0013            | PWM Channel 1 Period Register (PWMPER1)                | R/W    |

| 0x0014            | PWM Channel 2 Period Register (PWMPER2)                | R/W    |

| 0x0015            | PWM Channel 3 Period Register (PWMPER3)                | R/W    |

| 0x0016            | PWM Channel 4 Period Register (PWMPER4)                | R/W    |

| 0x0017            | PWM Channel 5 Period Register (PWMPER5)                | R/W    |

| 0x0018            | PWM Channel 0 Duty Register (PWMDTY0)                  | R/W    |

| 0x0019            | PWM Channel 1 Duty Register (PWMDTY1)                  | R/W    |

| 0x001A            | PWM Channel 2 Duty Register (PWMDTY2)                  | R/W    |

| 0x001B            | PWM Channel 3 Duty Register (PWMDTY3)                  | R/W    |

| 0x001C            | PWM Channel 4 Duty Register (PWMDTY4)                  | R/W    |

| 0x001D            | PWM Channel 5 Duty Register (PWMDTY5)                  | R/W    |

| 0x001E            | PWM Shutdown Register (PWMSDN)                         | R/W    |

<sup>1.</sup> PWMTST is intended for factory test purposes only.

<sup>2.</sup> PWMPRSC is intended for factory test purposes only.

<sup>3.</sup> PWMSCNTA is intended for factory test purposes only.

<sup>4.</sup> PWMSCNTB is intended for factory test purposes only.

Table 15-2. TIM16B8CV1 Memory Map

| Address Offset  | Use                                                     | Access             |  |  |

|-----------------|---------------------------------------------------------|--------------------|--|--|

| 0x0000          | Timer Input Capture/Output Compare Select (TIOS)        | R/W                |  |  |

| 0x0001          | Timer Compare Force Register (CFORC)                    | R/W <sup>(1)</sup> |  |  |

| 0x0002          | Output Compare 7 Mask Register (OC7M)                   | R/W                |  |  |

| 0x0003          | Output Compare 7 Data Register (OC7D)                   | R/W                |  |  |

| 0x0004          | Timer Count Register (TCNT(hi))                         | R/W <sup>(2)</sup> |  |  |

| 0x0005          | Timer Count Register (TCNT(lo))                         | R/W <sup>2</sup>   |  |  |

| 0x0006          | Timer System Control Register1 (TSCR1)                  | R/W                |  |  |

| 0x0007          | Timer Toggle Overflow Register (TTOV)                   | R/W                |  |  |

| 0x0008          | Timer Control Register1 (TCTL1)                         | R/W                |  |  |

| 0x0009          | Timer Control Register2 (TCTL2)                         | R/W                |  |  |

| 0x000A          | Timer Control Register3 (TCTL3)                         | R/W                |  |  |

| 0x000B          | Timer Control Register4 (TCTL4)                         | R/W                |  |  |

| 0x000C          | Timer Interrupt Enable Register (TIE)                   | R/W                |  |  |

| 0x000D          | Timer System Control Register2 (TSCR2)                  | R/W                |  |  |

| 0x000E          | Main Timer Interrupt Flag1 (TFLG1)                      | R/W                |  |  |

| 0x000F          | Main Timer Interrupt Flag2 (TFLG2)                      | R/W                |  |  |

| 0x0010          | Timer Input Capture/Output Compare Register 0 (TC0(hi)) | R/W <sup>(3)</sup> |  |  |

| 0x0011          | Timer Input Capture/Output Compare Register 0 (TC0(lo)) | R/W <sup>3</sup>   |  |  |

| 0x0012          | Timer Input Capture/Output Compare Register 1 (TC1(hi)) | R/W <sup>3</sup>   |  |  |

| 0x0013          | Timer Input Capture/Output Compare Register 1 (TC1(lo)) | R/W <sup>3</sup>   |  |  |

| 0x0014          | Timer Input Capture/Output Compare Register 2 (TC2(hi)) | R/W <sup>3</sup>   |  |  |

| 0x0015          | Timer Input Capture/Output Compare Register 2 (TC2(lo)) | R/W <sup>3</sup>   |  |  |

| 0x0016          | Timer Input Capture/Output Compare Register 3 (TC3(hi)) | R/W <sup>3</sup>   |  |  |

| 0x0017          | Timer Input Capture/Output Compare Register 3 (TC3(Io)) | R/W <sup>3</sup>   |  |  |

| 0x0018          | Timer Input Capture/Output Compare Register4 (TC4(hi))  | R/W <sup>3</sup>   |  |  |

| 0x0019          | Timer Input Capture/Output Compare Register 4 (TC4(Io)) | R/W <sup>3</sup>   |  |  |

| 0x001A          | Timer Input Capture/Output Compare Register 5 (TC5(hi)) | R/W <sup>3</sup>   |  |  |

| 0x001B          | Timer Input Capture/Output Compare Register 5 (TC5(Io)) | R/W <sup>3</sup>   |  |  |

| 0x001C          | Timer Input Capture/Output Compare Register 6 (TC6(hi)) | R/W <sup>3</sup>   |  |  |

| 0x001D          | Timer Input Capture/Output Compare Register 6 (TC6(Io)) | R/W <sup>3</sup>   |  |  |

| 0x001E          | Timer Input Capture/Output Compare Register 7 (TC7(hi)) | R/W <sup>3</sup>   |  |  |

| 0x001F          | Timer Input Capture/Output Compare Register 7 (TC7(lo)) | R/W <sup>3</sup>   |  |  |

| 0x0020          | 16-Bit Pulse Accumulator Control Register (PACTL)       | R/W                |  |  |

| 0x0021          | Pulse Accumulator Flag Register (PAFLG)                 | R/W                |  |  |

| 0x0022          | Pulse Accumulator Count Register (PACNT(hi))            | R/W                |  |  |

| 0x0023          | Pulse Accumulator Count Register (PACNT(Io))            | R/W                |  |  |

| 0x0024 - 0x002C | Reserved                                                | (4)                |  |  |

| 0x002D          | Timer Test Register (TIMTST)                            | R/W <sup>2</sup>   |  |  |

| 0x002E - 0x002F | Reserved                                                | 4                  |  |  |

<sup>1.</sup> Always read 0x0000.

<sup>2.</sup> Only writable in special modes (test\_mode = 1).

<sup>3.</sup> Write to these registers have no meaning or effect during input capture.

<sup>4.</sup> Write has no effect; return 0 on read

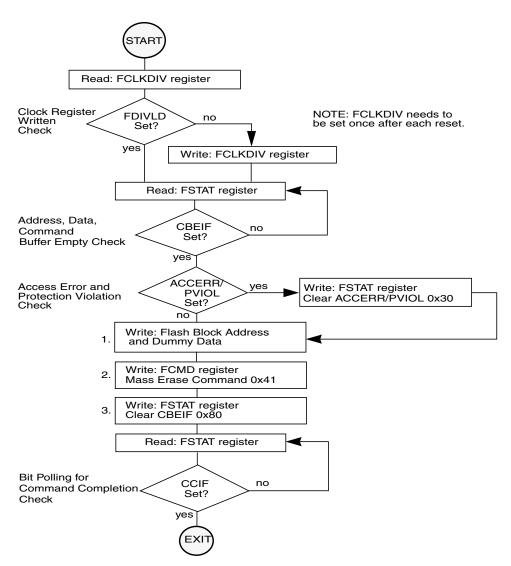

# 17.4.1.2 Command Write Sequence

The Flash command controller is used to supervise the command write sequence to execute program, erase, and erase verify algorithms.

Before starting a command write sequence, the ACCERR and PVIOL flags in the FSTAT register must be clear and the CBEIF flag should be tested to determine the state of the address, data, and command buffers. If the CBEIF flag is set, indicating the buffers are empty, a new command write sequence can be started. If the CBEIF flag is clear, indicating the buffers are not available, a new command write sequence will overwrite the contents of the address, data, and command buffers.

A command write sequence consists of three steps which must be strictly adhered to with writes to the Flash module not permitted between the steps. However, Flash register and array reads are allowed during a command write sequence. The basic command write sequence is as follows:

- 1. Write to a valid address in the Flash array memory.

- 2. Write a valid command to the FCMD register.

- 3. Clear the CBEIF flag in the FSTAT register by writing a 1 to CBEIF to launch the command.

The address written in step 1 will be stored in the FADDR registers and the data will be stored in the FDATA registers. When the CBEIF flag is cleared in step 3, the CCIF flag is cleared by the Flash command controller indicating that the command was successfully launched. For all command write sequences, the CBEIF flag will set after the CCIF flag is cleared indicating that the address, data, and command buffers are ready for a new command write sequence to begin. A buffered command will wait for the active operation to be completed before being launched. Once a command is launched, the completion of the command operation is indicated by the setting of the CCIF flag in the FSTAT register. The CCIF flag will set upon completion of all active and buffered commands.

### Chapter 17 16 Kbyte Flash Module (S12FTS16KV1)

Figure 17-25. Example Mass Erase Command Flow

Chapter 19 64 Kbyte Flash Module (S12FTS64KV4)

## 19.4.1.3.3 Sector Erase Command

The sector erase operation will erase all addresses in a 1024 byte sector of the Flash array using an embedded algorithm.

An example flow to execute the sector erase operation is shown in Figure 19-27. The sector erase command write sequence is as follows:

- 1. Write to a Flash array address to start the command write sequence for the sector erase command. The Flash address written determines the sector to be erased while MCU address bits [9:0] and the data written are ignored.

- 2. Write the sector erase command, 0x40, to the FCMD register.

- 3. Clear the CBEIF flag in the FSTAT register by writing a 1 to CBEIF to launch the sector erase command.

If a Flash sector to be erased is in a protected area of the Flash array, the PVIOL flag in the FSTAT register will set and the sector erase command will not launch. Once the sector erase command has successfully launched, the CCIF flag in the FSTAT register will set after the sector erase operation has completed unless a new command write sequence has been buffered.

### Chapter 20 96 Kbyte Flash Module (S12FTS96KV1)

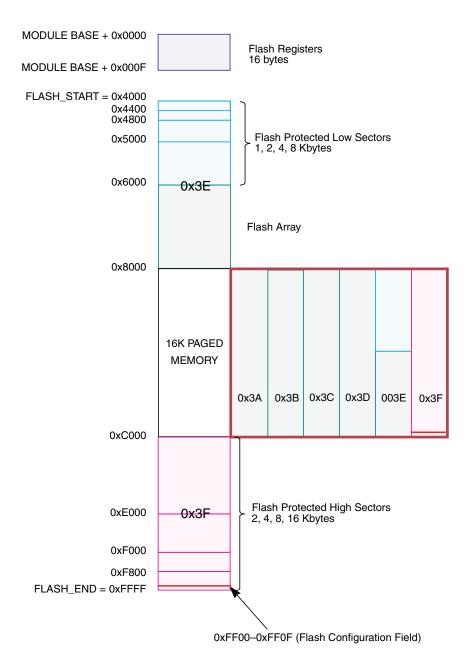

Note: 0x3A-0x3F correspond to the PPAGE register content

Figure 20-4. Flash Memory Map

Chapter 20 96 Kbyte Flash Module (S12FTS96KV1)

**Table 20-10. Flash Protection Function**

| FPOPEN | FPHDIS | FPHS[1] | FPHS[0] | FPLDIS | FPLS[1] | FPLS[0] | Function <sup>(1)</sup>         |  |

|--------|--------|---------|---------|--------|---------|---------|---------------------------------|--|

| 1      | 1      | х       | х       | 1      | х       | х       | No protection                   |  |

| 1      | 1      | х       | х       | 0      | х       | х       | Protect low range               |  |

| 1      | 0      | х       | х       | 1      | х       | х       | Protect high range              |  |

| 1      | 0      | х       | х       | 0      | х       | х       | Protect high and low ranges     |  |

| 0      | 1      | х       | х       | 1      | х       | х       | Full Flash array protected      |  |

| 0      | 0      | х       | х       | 1      | х       | х       | Unprotected high range          |  |

| 0      | 1      | х       | х       | 0      | х       | х       | Unprotected low range           |  |

| 0      | 0      | х       | х       | 0      | х       | х       | Unprotected high and low ranges |  |

<sup>1.</sup> For range sizes refer to Table 20-11 and Table 20-12 or .

Table 20-11. Flash Protection Higher Address Range

| FPHS[1:0] | Address Range | Range Size |  |  |

|-----------|---------------|------------|--|--|

| 00        | 0xF800-0xFFFF | 2 Kbytes   |  |  |

| 01        | 0xF000-0xFFFF | 4 Kbytes   |  |  |

| 10        | 0xE000-0xFFFF | 8 Kbytes   |  |  |

| 11        | 0xC000-0xFFFF | 16 Kbytes  |  |  |

Table 20-12. Flash Protection Lower Address Range

| FPLS[1:0] | Address Range | Range Size |  |  |  |

|-----------|---------------|------------|--|--|--|

| 00        | 0x4000-0x43FF | 1 Kbyte    |  |  |  |

| 01        | 0x4000-0x47FF | 2 Kbytes   |  |  |  |

| 10        | 0x4000-0x4FFF | 4 Kbytes   |  |  |  |

| 11        | 0x4000-0x5FFF | 8 Kbytes   |  |  |  |

Figure 20-11 illustrates all possible protection scenarios. Although the protection scheme is loaded from the Flash array after reset, it is allowed to change in normal modes. This protection scheme can be used by applications requiring re-programming in single chip mode while providing as much protection as possible if no re-programming is required.

### **Appendix A Electrical Characteristics**

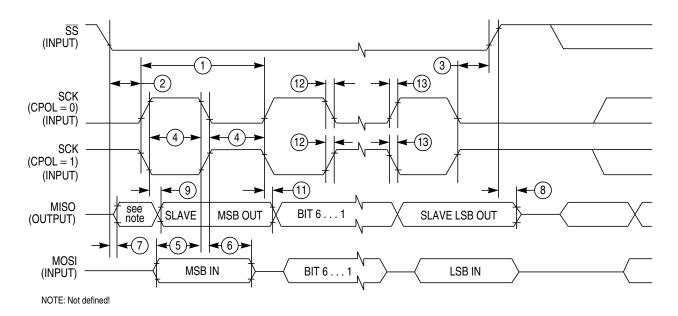

In Figure A-9 the timing diagram for slave mode with transmission format CPHA=1 is depicted.

Figure A-9. SPI Slave Timing (CPHA=1)

In Table A-22 the timing characteristics for slave mode are listed.

**Table A-22. SPI Slave Mode Timing Characteristics**

| Num | С | Characteristic                          | Symbol            | Min | Тур | Max                                | Unit             |

|-----|---|-----------------------------------------|-------------------|-----|-----|------------------------------------|------------------|

| 1   | D | SCK Frequency                           | f <sub>sck</sub>  | DC  | _   | 1/4                                | f <sub>bus</sub> |

| 1   | Р | SCK Period                              | t <sub>sck</sub>  | 4   | _   | ∞                                  | t <sub>bus</sub> |

| 2   | D | Enable Lead Time                        | t <sub>lead</sub> | 4   | _   | _                                  | t <sub>bus</sub> |

| 3   | D | Enable Lag Time                         | t <sub>lag</sub>  | 4   | _   | _                                  | t <sub>bus</sub> |

| 4   | D | Clock (SCK) High or Low Time            | t <sub>wsck</sub> | 4   | _   | _                                  | t <sub>bus</sub> |

| 5   | D | Data Setup Time (Inputs)                | t <sub>su</sub>   | 8   | _   | _                                  | ns               |

| 6   | D | Data Hold Time (Inputs)                 | t <sub>hi</sub>   | 8   | _   | _                                  | ns               |

| 7   | D | Slave Access Time (time to data active) | t <sub>a</sub>    | _   | _   | 20                                 | ns               |

| 8   | D | Slave MISO Disable Time                 | t <sub>dis</sub>  | _   | _   | 22                                 | ns               |

| 9   | D | Data Valid after SCK Edge               | t <sub>vsck</sub> | _   | _   | 30 + t <sub>bus</sub>              | ns               |

| 10  | D | Data Valid after SS fall                | t <sub>vss</sub>  | _   | _   | 30 + t <sub>bus</sub> <sup>1</sup> | ns               |

| 11  | D | Data Hold Time (Outputs)                | t <sub>ho</sub>   | 20  | _   | _                                  | ns               |

| 12  | D | Rise and Fall Time Inputs               | t <sub>rfi</sub>  | _   | _   | 8                                  | ns               |

| 13  | D | Rise and Fall Time Outputs              | t <sub>rfo</sub>  | _   | _   | 8                                  | ns               |

<sup>1.</sup> t<sub>bus</sub> added due to internal synchronization delay