Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| -                          |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Details                    |                                                                          |

| Product Status             | Obsolete                                                                 |

| Core Processor             | HCS12                                                                    |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 25MHz                                                                    |

| Connectivity               | EBI/EMI, SCI, SPI                                                        |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 35                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 4K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 52-LQFP                                                                  |

| Supplier Device Package    | 52-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12gc128vpber |

# 1.2.2 Detailed Register Map

The detailed register map of the MC9S12C128 is listed in address order below.

# 0x0000-0x000F MEBI Map 1 of 3 (HCS12 Multiplexed External Bus Interface)

| Address | Name      |                 | Bit 7  | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2 | Bit 1   | Bit 0 |

|---------|-----------|-----------------|--------|-------|-------|---------|-------|-------|---------|-------|

| 0x0000  | PORTA     | Read:<br>Write: | Bit 7  | 6     | 5     | 4       | 3     | 2     | 1       | Bit 0 |

| 0x0001  | PORTB     | Read:<br>Write: | Bit 7  | 6     | 5     | 4       | 3     | 2     | 1       | Bit 0 |

| 0x0002  | DDRA      | Read:<br>Write: | Bit 7  | 6     | 5     | 4       | 3     | 2     | 1       | Bit 0 |

| 0x0003  | DDRB      | Read:<br>Write: | Bit 7  | 6     | 5     | 4       | 3     | 2     | 1       | Bit 0 |

| 0x0004  | Reserved  | Read:           | 0      | 0     | 0     | 0       | 0     | 0     | 0       | 0     |

|         |           | Write:          | 0      | 0     | 0     | 0       | 0     | 0     | 0       | 0     |

| 0x0005  | Reserved  | Read:<br>Write: | 0      | U     | U     | 0       | U     | 0     | 0       | U     |

| 0.0000  | Б         | Read:           | 0      | 0     | 0     | 0       | 0     | 0     | 0       | 0     |

| 0x0006  | Reserved  | Write:          |        |       |       |         |       |       |         |       |

| 0x0007  | Reserved  | Read:           | 0      | 0     | 0     | 0       | 0     | 0     | 0       | 0     |

| 0,0007  | ricscrvca | Write:          |        |       |       |         |       |       |         |       |

| 0x0008  | PORTE     | Read:<br>Write: | Bit 7  | 6     | 5     | 4       | 3     | 2     | Bit 1   | Bit 0 |

| 0x0009  | DDRE      | Read:<br>Write: | Bit 7  | 6     | 5     | 4       | 3     | Bit 2 | 0       | 0     |

| 0x000A  | PEAR      | Read:<br>Write: | NOACCE | 0     | PIPOE | NECLK   | LSTRE | RDWE  | 0       | 0     |

| 0x000B  | MODE      | Read:<br>Write: | MODC   | MODB  | MODA  | 0       | IVIS  | 0     | EMK     | EME   |

| 0x000C  | PUCR      | Read:           | PUPKE  | 0     | 0     | PUPEE   | 0     | 0     | PUPBE   | PUPAE |

| 0,0000  | 1 0011    | Write:          | TOTAL  |       |       | 1 OI LL |       |       | 1 OI DE | TOTAL |

| 0x000D  | RDRIV     | Read:<br>Write: | RDPK   | 0     | 0     | RDPE    | 0     | 0     | RDPB    | RDPA  |

| 0x000E  | EBICTL    | Read:           | 0      | 0     | 0     | 0       | 0     | 0     | 0       | ESTR  |

| 3,0000  | 22.0.2    | Write:          |        |       |       |         |       |       |         |       |

| 0x000F  | Reserved  | Read:<br>Write: | 0      | 0     | 0     | 0       | 0     | 0     | 0       | 0     |

| Address | Name       |                 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|------------|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

| 0x005F  | TC7 (lo)   | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0060  | PACTL      | Read:<br>Write: | 0      | PAEN  | PAMOD | PEDGE | CLK1  | CLK0  | PAOVI | PAI   |

| 0x0061  | PAFLG      | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | PAOVF | PAIF  |

| 0x0062  | PACNT (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x0063  | PACNT (Io) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0064  | Reserved   | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0065  | Reserved   | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0066  | Reserved   | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0067  | Reserved   | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0068  | Reserved   | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0069  | Reserved   | Read:           | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x006A  | Reserved   | Write:          | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x006B  | Reserved   | Write:<br>Read: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x006C  | Reserved   | Write:<br>Read: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x006D  | Reserved   | Write:<br>Read: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|         |            | Write:<br>Read: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x006E  | Reserved   | Write:<br>Read: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x006F  | Reserved   | Write:          | -      | -     | -     | -     | -     | -     | -     | -     |

## 0x0070-0x007F Reserved

| Address | Name        |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------|-------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| 0x0070- | Reserved    | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| 0x007F  | i lesei veu | Write: |       |       |       |       |       |       |       |       |  |

**Chapter 3 Module Mapping Control (MMCV4) Block Description**

# 3.3.2.2 Initialization of Internal Registers Position Register (INITRG)

Module Base + 0x0011 Starting address location affected by INITRG register setting.

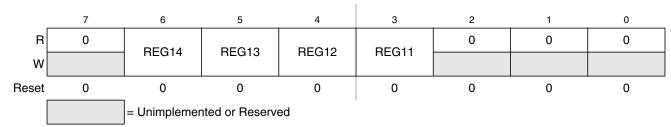

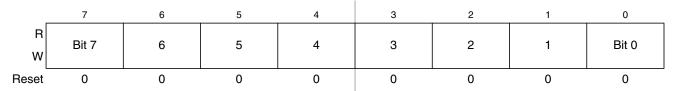

Figure 3-4. Initialization of Internal Registers Position Register (INITRG)

Read: Anytime

Write: Once in normal and emulation modes and anytime in special modes

This register initializes the position of the internal registers within the on-chip system memory map. The registers occupy either a 1K byte or 2K byte space and can be mapped to any 2K byte space within the first 32K bytes of the system's address space.

**Table 3-3. INITRG Field Descriptions**

| Field | Description                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------|

| 6:3   | Internal Register Map Position — These four bits in combination with the leading zero supplied by bit 7 of      |

|       | INITRG determine the upper five bits of the base address for the system's internal registers (i.e., the minimum |

|       | base address is 0x0000 and the maximum is 0x7FFF).                                                              |

Chapter 3 Module Mapping Control (MMCV4) Block Description

# 3.3.2.4 Miscellaneous System Control Register (MISC)

Module Base + 0x0013

Starting address location affected by INITRG register setting.

|                                  | 7 | 6 | 5 | 4 | 3      | 2      | 1     | 0     |

|----------------------------------|---|---|---|---|--------|--------|-------|-------|

| R                                | 0 | 0 | 0 | 0 | EVOTD4 | EVETDO | DOMUM | DOMON |

| W                                |   |   |   |   | EXSTR1 | EXSTR0 | ROMHM | ROMON |

| Reset: Expanded or Emulation     | 0 | 0 | 0 | 0 | 1      | 1      | 0     | _1    |

| Reset: Peripheral or Single Chip | 0 | 0 | 0 | 0 | 1      | 1      | 0     | 1     |

| Reset: Special Test              | 0 | 0 | 0 | 0 | 1      | 1      | 0     | 0     |

1. The reset state of this bit is determined at the chip integration level.

= Unimplemented or Reserved

Figure 3-6. Miscellaneous System Control Register (MISC)

Read: Anytime

Write: As stated in each bit description

#### NOTE

Writes to this register take one cycle to go into effect.

This register initializes miscellaneous control functions.

**Table 3-5. INITEE Field Descriptions**

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:2<br>EXSTR[1:0] | External Access Stretch Bits 1 and 0 Write: once in normal and emulation modes and anytime in special modes This two-bit field determines the amount of clock stretch on accesses to the external address space as shown in Table 3-6. In single chip and peripheral modes these bits have no meaning or effect.                                                                                                             |

| 1<br>ROMHM        | FLASH EEPROM or ROM Only in Second Half of Memory Map Write: once in normal and emulation modes and anytime in special modes 0 The fixed page(s) of FLASH EEPROM or ROM in the lower half of the memory map can be accessed. 1 Disables direct access to the FLASH EEPROM or ROM in the lower half of the memory map. These physical locations of the FLASH EEPROM or ROM remain accessible through the program page window. |

| 0<br>ROMON        | ROMON — Enable FLASH EEPROM or ROM Write: once in normal and emulation modes and anytime in special modes This bit is used to enable the FLASH EEPROM or ROM memory in the memory map.  0 Disables the FLASH EEPROM or ROM from the memory map.  1 Enables the FLASH EEPROM or ROM in the memory map.                                                                                                                        |

# 5.2 External Signal Description

Most interfacing with the interrupt sub-block is done within the core. However, the interrupt does receive direct input from the multiplexed external bus interface (MEBI) sub-block of the core for the  $\overline{IRQ}$  and  $\overline{XIRQ}$  pin data.

# 5.3 Memory Map and Register Definition

Detailed descriptions of the registers and associated bits are given in the subsections that follow.

## 5.3.1 Module Memory Map

**Table 5-1. INT Memory Map**

| Address<br>Offset | Use                                           | Access |

|-------------------|-----------------------------------------------|--------|

| 0x0015            | Interrupt Test Control Register (ITCR)        | R/W    |

| 0x0016            | Interrupt Test Registers (ITEST)              | R/W    |

| 0x001F            | Highest Priority Interrupt (Optional) (HPRIO) | R/W    |

## 5.3.2 Register Descriptions

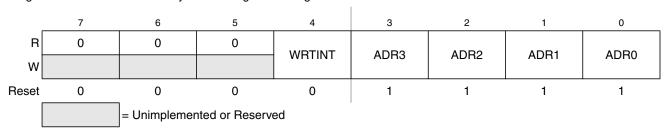

## 5.3.2.1 Interrupt Test Control Register

Module Base + 0x0015

Starting address location affected by INITRG register setting.

Figure 5-2. Interrupt Test Control Register (ITCR)

Read: See individual bit descriptions

Write: See individual bit descriptions

#### **Table 6-2. BDMSTS Field Descriptions**

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ENBDM  | Enable BDM — This bit controls whether the BDM is enabled or disabled. When enabled, BDM can be made active to allow firmware commands to be executed. When disabled, BDM cannot be made active but BDM hardware commands are allowed.  0 BDM disabled 1 BDM enabled Note: ENBDM is set by the firmware immediately out of reset in special single-chip mode. In secure mode, this bit will not be set by the firmware until after the EEPROM and FLASH erase verify tests are complete. |

| 6<br>BDMACT | BDM Active Status — This bit becomes set upon entering BDM. The standard BDM firmware lookup table is then enabled and put into the memory map. BDMACT is cleared by a carefully timed store instruction in the standard BDM firmware as part of the exit sequence to return to user code and remove the BDM memory from the map.  0 BDM not active 1 BDM active                                                                                                                         |

| 5<br>ENTAG  | Tagging Enable — This bit indicates whether instruction tagging in enabled or disabled. It is set when the TAGGO command is executed and cleared when BDM is entered. The serial system is disabled and the tag function enabled 16 cycles after this bit is written. BDM cannot process serial commands while tagging is active.  0 Tagging not enabled or BDM active 1 Tagging enabled                                                                                                 |

| 4<br>SDV    | Shift Data Valid — This bit is set and cleared by the BDM hardware. It is set after data has been transmitted as part of a firmware read command or after data has been received as part of a firmware write command. It is cleared when the next BDM command has been received or BDM is exited. SDV is used by the standard BDM firmware to control program flow execution.  O Data phase of command not complete  1 Data phase of command is complete                                 |

| 3<br>TRACE  | TRACE1 BDM Firmware Command is Being Executed — This bit gets set when a BDM TRACE1 firmware command is first recognized. It will stay set as long as continuous back-to-back TRACE1 commands are executed. This bit will get cleared when the next command that is not a TRACE1 command is recognized.  O TRACE1 command is not being executed  TRACE1 command is being executed                                                                                                        |

Chapter 8 Analog-to-Digital Converter (ATD10B8C) Block Description

# 8.3.2 Register Descriptions

This section describes in address order all the ATD10B8C registers and their individual bits.

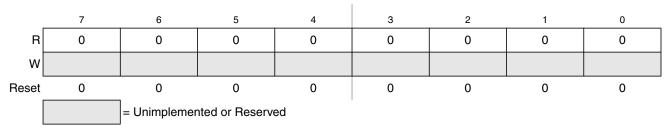

# 8.3.2.1 Reserved Register (ATDCTL0)

Module Base + 0x0000

Figure 8-3. Reserved Register (ATDCTL0)

Read: Always read \$00 in normal modes

Write: Unimplemented in normal modes

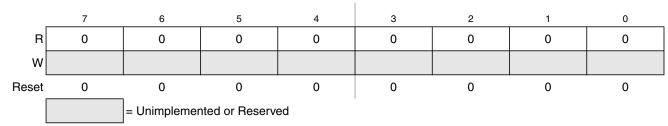

## 8.3.2.2 Reserved Register (ATDCTL1)

Module Base + 0x0001

Figure 8-4. Reserved Register (ATDCTL1)

Read: Always read \$00 in normal modes

Write: Unimplemented in normal modes

#### NOTE

Writing to this registers when in special modes can alter functionality.

#### **Table 9-2. CRGFLG Field Descriptions (continued)**

| Field      | Description                                                                                                                                                                                                                                                                                                    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>SCMIF | Self-Clock Mode Interrupt Flag — SCMIF is set to 1 when SCM status bit changes. This flag can only be cleared by writing a 1. Writing a 0 has no effect. If enabled (SCMIE=1), SCMIF causes an interrupt request.  0 No change in SCM bit.  1 SCM bit has changed.                                             |

| 0<br>SCM   | Self-Clock Mode Status Bit — SCM reflects the current clocking mode. Writes have no effect.  0 MCU is operating normally with OSCCLK available.  1 MCU is operating in self-clock mode with OSCCLK in an unknown state. All clocks are derived from PLLCLK running at its minimum frequency f <sub>SCM</sub> . |

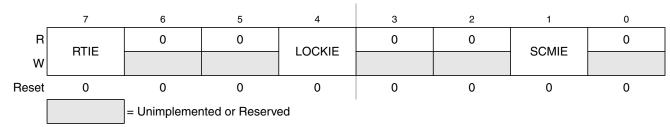

# 9.3.2.5 CRG Interrupt Enable Register (CRGINT)

This register enables CRG interrupt requests.

Module Base + 0x0004

Figure 9-8. CRG Interrupt Enable Register (CRGINT)

Read: anytime Write: anytime

**Table 9-3. CRGINT Field Descriptions**

| Field       | Description                                                                                                                      |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RTIE   | Real-Time Interrupt Enable Bit 0 Interrupt requests from RTI are disabled. 1 Interrupt will be requested whenever RTIF is set.   |

| 4<br>LOCKIE | Lock Interrupt Enable Bit  0 LOCK interrupt requests are disabled.  1 Interrupt will be requested whenever LOCKIF is set.        |

| 1<br>SCMIE  | Self-Clock Mode Interrupt Enable Bit 0 SCM interrupt requests are disabled. 1 Interrupt will be requested whenever SCMIF is set. |

Chapter 10 Freescale's Scalable Controller Area Network (S12MSCANV2)

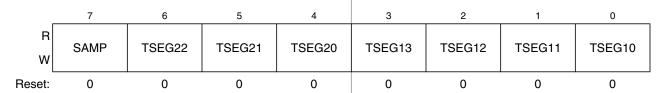

# 10.3.2.4 MSCAN Bus Timing Register 1 (CANBTR1)

The CANBTR1 register configures various CAN bus timing parameters of the MSCAN module.

Module Base + 0x0003

Figure 10-7. MSCAN Bus Timing Register 1 (CANBTR1)

Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

Table 10-6. CANBTR1 Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SAMP         | Sampling — This bit determines the number of CAN bus samples taken per bit time.  0 One sample per bit.  1 Three samples per bit <sup>(1)</sup> .  If SAMP = 0, the resulting bit value is equal to the value of the single bit positioned at the sample point. If SAMP = 1, the resulting bit value is determined by using majority rule on the three total samples. For higher bit rates, it is recommended that only one sample is taken per bit time (SAMP = 0). |

| 6:4<br>TSEG2[2:0] | <b>Time Segment 2</b> — Time segments within the bit time fix the number of clock cycles per bit time and the location of the sample point (see Figure 10-43). Time segment 2 (TSEG2) values are programmable as shown in Table 10-7.                                                                                                                                                                                                                                |

| 3:0<br>TSEG1[3:0] | Time Segment 1 — Time segments within the bit time fix the number of clock cycles per bit time and the location of the sample point (see Figure 10-43). Time segment 1 (TSEG1) values are programmable as shown in Table 10-8.                                                                                                                                                                                                                                       |

<sup>1.</sup> In this case, PHASE\_SEG1 must be at least 2 time quanta (Tq).

**Table 10-7. Time Segment 2 Values**

| TSEG22 | TSEG21 | TSEG20 | Time Segment 2                  |

|--------|--------|--------|---------------------------------|

| 0      | 0      | 0      | 1 Tq clock cycle <sup>(1)</sup> |

| 0      | 0      | 1      | 2 Tq clock cycles               |

| :      | :      | :      | :                               |

| 1      | 1      | 0      | 7 Tq clock cycles               |

| 1      | 1      | 1      | 8 Tq clock cycles               |

<sup>1.</sup> This setting is not valid. Please refer to Table 10-34 for valid settings.

# 12.3.2 Register Descriptions

The following paragraphs describe in detail all the registers and register bits in the PWM8B6CV1 module.

| Register<br>Name   |        | Bit 7      | 6                           | 5      | 4      | 3     | 2     | 1     | Bit 0      |

|--------------------|--------|------------|-----------------------------|--------|--------|-------|-------|-------|------------|

| 0x0000<br>PWME     | R<br>W | 0          | 0                           | PWME5  | PWME4  | PWME3 | PWME2 | PWME1 | PWME0      |

| 0x0001<br>PWMPOL   | R<br>W | 0          | 0                           | PPOL5  | PPOL4  | PPOL3 | PPOL2 | PPOL1 | PPOL0      |

| 0x0002<br>PWMCLK   | R<br>W | 0          | 0                           | PCLK5  | PCLK4  | PCLK3 | PCLK2 | PCLK1 | PCLK0      |

| 0x0003<br>PWMPRCLK | R<br>W | 0          | PCKB2                       | PCKB1  | PCKB0  | 0     | PCKA2 | PCKA1 | PCKA0      |

| 0x0004<br>PWMCAE   | R<br>W | 0          | 0                           | CAE5   | CAE4   | CAE2  | CAE2  | CAE1  | CAE0       |

| 0x0005<br>PWMCTL   | R<br>W | 0          | CON45                       | CON23  | CON01  | PSWAI | PFRZ  | 0     | 0          |

| 0x0006<br>PWMTST   | R<br>W | 0          | 0                           | 0      | 0      | 0     | 0     | 0     | 0          |

| 0x0007<br>PWMPRSC  | R<br>W | 0          | 0                           | 0      | 0      | 0     | 0     | 0     | 0          |

| 0x0008<br>PWMSCLA  | R<br>W | Bit 7      | 6                           | 5      | 4      | 3     | 2     | 1     | Bit 0      |

| 0x0009<br>PWMSCLB  | R<br>W | Bit 7      | 6                           | 5      | 4      | 3     | 2     | 1     | Bit 0      |

| 0x000A<br>PWMSCNTA | R<br>W | 0          | 0                           | 0      | 0      | 0     | 0     | 0     | 0          |

| 0x000B<br>PWMSCNTB | R<br>W | 0          | 0                           | 0      | 0      | 0     | 0     | 0     | 0          |

| 0x000C<br>PWMCNT0  | R<br>W | Bit 7      | 6                           | 5<br>0 | 4 0    | 3     | 2     | 1 0   | Bit 0      |

| 0x000D<br>PWMCNT1  | R<br>W | Bit 7      | 6                           | 5<br>0 | 4<br>0 | 3     | 2     | 1 0   | Bit 0      |

| 0x000E<br>PWMCNT2  | R<br>W | Bit 7<br>0 | 6                           | 5<br>0 | 0      | 3     | 2     | 0     | Bit 0<br>0 |

|                    |        |            | = Unimplemented or Reserved |        |        |       |       |       |            |

Figure 12-2. PWM Register Summary

#### Chapter 12 Pulse-Width Modulator (PWM8B6CV1) Block Description

• The channel is disabled

In this way, the output of the PWM will always be either the old waveform or the new waveform, not some variation in between. If the channel is not enabled, then writes to the period register will go directly to the latches as well as the buffer.

#### NOTE

Reads of this register return the most recent value written. Reads do not necessarily return the value of the currently active period due to the double buffering scheme.

Reference Section 12.4.2.3, "PWM Period and Duty," for more information.

To calculate the output period, take the selected clock source period for the channel of interest (A, B, SA, or SB) and multiply it by the value in the period register for that channel:

- Left aligned output (CAEx = 0)

- PWMx period = channel clock period \* PWMPERx center aligned output (CAEx = 1)

- PWMx period = channel clock period \* (2 \* PWMPERx)

For boundary case programming values, please refer to Section 12.4.2.8, "PWM Boundary Cases."

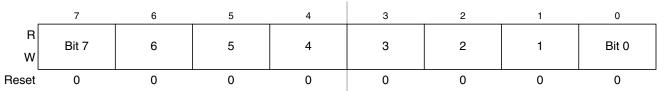

Module Base + 0x0012

Figure 12-21. PWM Channel Period Registers (PWMPER0)

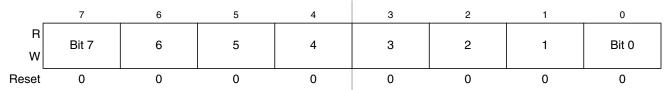

Module Base + 0x0013

Figure 12-22. PWM Channel Period Registers (PWMPER1)

Module Base + 0x0014

Figure 12-23. PWM Channel Period Registers (PWMPER2)

## 13.4.4.2 Character Reception

During an SCI reception, the receive shift register shifts a frame in from the **Rx input** signal. The SCI data register is the read-only buffer between the internal data bus and the receive shift register.

After a complete frame shifts into the receive shift register, the data portion of the frame transfers to the SCI data register. The receive data register full flag, RDRF, in SCI status register 1 (SCISR1) becomes set, indicating that the received byte can be read. If the receive interrupt enable bit, RIE, in SCI control register 2 (SCICR2) is also set, the RDRF flag generates an RDRF interrupt request.

## 13.4.4.3 Data Sampling

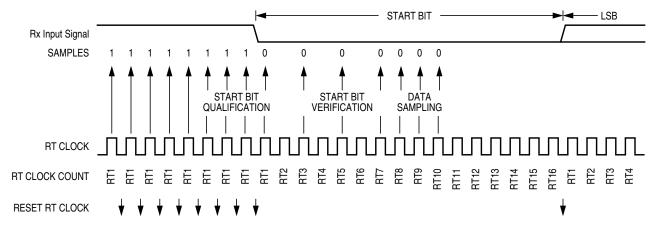

The receiver samples the **Rx input** signal at the RT clock rate. The RT clock is an internal signal with a frequency 16 times the baud rate. To adjust for baud rate mismatch, the RT clock (see Figure 13-13) is resynchronized:

- After every start bit

- After the receiver detects a data bit change from logic 1 to logic 0 (after the majority of data bit samples at RT8, RT9, and RT10 returns a valid logic 1 and the majority of the next RT8, RT9, and RT10 samples returns a valid logic 0)

To locate the start bit, data recovery logic does an asynchronous search for a logic 0 preceded by three logic 1s. When the falling edge of a possible start bit occurs, the RT clock begins to count to 16.

Figure 13-13. Receiver Data Sampling

To verify the start bit and to detect noise, data recovery logic takes samples at RT3, RT5, and RT7. Table 13-11 summarizes the results of the start bit verification samples.

| RT3, RT5, and RT7 Samples | Start Bit Verification | Noise Flag |  |  |

|---------------------------|------------------------|------------|--|--|

| 000                       | Yes                    | 0          |  |  |

| 001                       | Yes                    | 1          |  |  |

| 010                       | Yes                    | 1          |  |  |

| 011                       | No                     | 0          |  |  |

Table 13-11. Start Bit Verification

Chapter 13 Serial Communications Interface (S12SCIV2) Block Description

# 13.5.2 Interrupt Operation

# 13.5.2.1 System Level Interrupt Sources

There are five interrupt sources that can generate an SCI interrupt in to the CPU. They are listed in Table 13-14.

**Table 13-14. SCI Interrupt Source**

| Interrupt Source | Flag | Local Enable |  |  |

|------------------|------|--------------|--|--|

| Transmitter      | TDRE | TIE          |  |  |

| Transmitter      | TC   | TCIE         |  |  |

| Receiver         | RDRF | RIE          |  |  |

|                  | OR   |              |  |  |

| Receiver         | IDLE | ILIE         |  |  |

#### Chapter 18 32 Kbyte Flash Module (S12FTS32KV1)

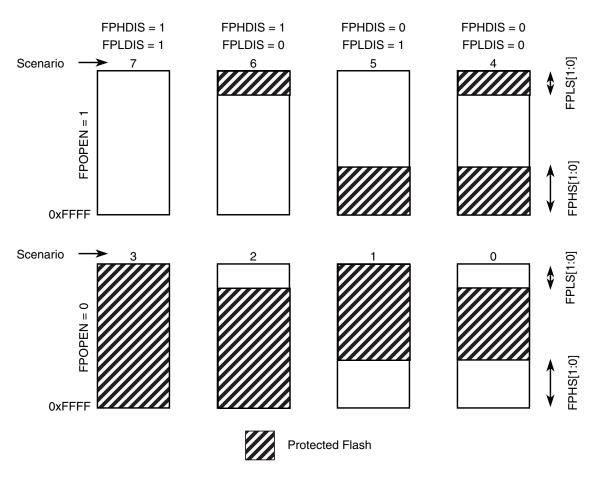

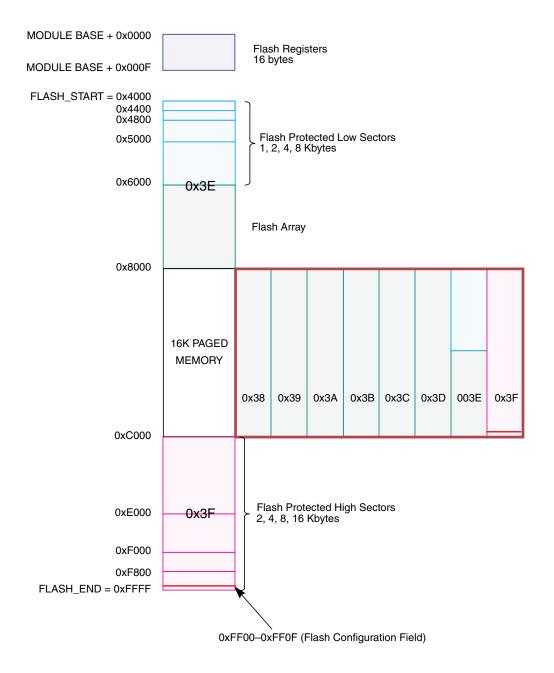

Figure 18-9. Flash Protection Scenarios

#### 18.3.2.5.1 Flash Protection Restrictions

The general guideline is that protection can only be added, not removed. All valid transitions between Flash protection scenarios are specified in Table 18-12. Any attempt to write an invalid scenario to the FPROT register will be ignored and the FPROT register will remain unchanged. The contents of the FPROT register reflect the active protection scenario.

To Protection Scenario<sup>(1)</sup> From **Protection** 7 0 2 3 4 5 Scenario 1 6 0 Χ Χ Χ Χ 1 Χ Χ 2 Х Χ 3 Χ 4 Χ Χ Х 5 Χ Χ Χ

**Table 18-12. Flash Protection Scenario Transitions**

**Table 19-5. FSEC Field Descriptions**

| Field             | Description                                                                                                                                                                                           |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–6<br>KEYEN[1:0] | <b>Backdoor Key Security Enable Bits</b> — The KEYEN[1:0] bits define the enabling of the backdoor key access to the Flash module as shown in Table 19-6.                                             |

| 5–2<br>NV[5:2]    | Nonvolatile Flag Bits — The NV[5:2] bits are available to the user as nonvolatile flags.                                                                                                              |

| 1–0<br>SEC[1:0]   | Flash Security Bits — The SEC[1:0] bits define the security state of the MCU as shown in Table 19-7. If the Flash module is unsecured using backdoor key access, the SEC[1:0] bits are forced to 1:0. |

Table 19-6. Flash KEYEN States

| KEYEN[1:0]        | Status of Backdoor Key Access |

|-------------------|-------------------------------|

| 00                | DISABLED                      |

| 01 <sup>(1)</sup> | DISABLED                      |

| 10                | ENABLED                       |

| 11                | DISABLED                      |

<sup>1.</sup> Preferred KEYEN state to disable Backdoor Key Access.

Table 19-7. Flash Security States

| SEC[1:0]          | Status of Security |

|-------------------|--------------------|

| 00                | Secured            |

| 01 <sup>(1)</sup> | Secured            |

| 10                | Unsecured          |

| 11                | Secured            |

<sup>1.</sup> Preferred SEC state to set MCU to secured state.

The security function in the Flash module is described in Section 19.4.3, "Flash Module Security".

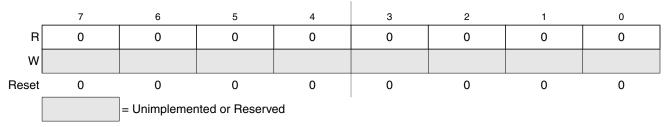

#### 19.3.2.3 RESERVED1

This register is reserved for factory testing and is not accessible to the user.

Module Base + 0x0002

Figure 19-8. RESERVED1

All bits read 0 and are not writable.

Chapter 19 64 Kbyte Flash Module (S12FTS64KV4)

## 19.4.1.2 Command Write Sequence

The Flash command controller is used to supervise the command write sequence to execute program, erase, and erase verify algorithms.

Before starting a command write sequence, the ACCERR and PVIOL flags in the FSTAT register must be clear and the CBEIF flag should be tested to determine the state of the address, data, and command buffers. If the CBEIF flag is set, indicating the buffers are empty, a new command write sequence can be started. If the CBEIF flag is clear, indicating the buffers are not available, a new command write sequence will overwrite the contents of the address, data, and command buffers.

A command write sequence consists of three steps which must be strictly adhered to with writes to the Flash module not permitted between the steps. However, Flash register and array reads are allowed during a command write sequence. The basic command write sequence is as follows:

- 1. Write to a valid address in the Flash array memory.

- 2. Write a valid command to the FCMD register.

- 3. Clear the CBEIF flag in the FSTAT register by writing a 1 to CBEIF to launch the command.

The address written in step 1 will be stored in the FADDR registers and the data will be stored in the FDATA registers. When the CBEIF flag is cleared in step 3, the CCIF flag is cleared by the Flash command controller indicating that the command was successfully launched. For all command write sequences, the CBEIF flag will set after the CCIF flag is cleared indicating that the address, data, and command buffers are ready for a new command write sequence to begin. A buffered command will wait for the active operation to be completed before being launched. Once a command is launched, the completion of the command operation is indicated by the setting of the CCIF flag in the FSTAT register. The CCIF flag will set upon completion of all active and buffered commands.

Chapter 19 64 Kbyte Flash Module (S12FTS64KV4)

Note: 0x38-0x3F correspond to the PPAGE register content

Figure 20-3. Flash Memory Map

# 20.3.2 Register Descriptions

The Flash module contains a set of 16 control and status registers located between module base + 0x0000 and 0x000F. A summary of the Flash module registers is given in Figure 20-5. Detailed descriptions of each register bit are provided.

| Register<br>Name                 |        | Bit 7  | 6      | 5      | 4      | 3     | 2      | 1     | Bit 0 |

|----------------------------------|--------|--------|--------|--------|--------|-------|--------|-------|-------|

| 0x0000<br>FCLKDIV                | R<br>W | FDIVLD | PRDIV8 | FDIV5  | FDIV4  | FDIV3 | FDIV2  | FDIV1 | FDIV0 |

| 0x0001                           | R      | KEYEN1 | KEYEN0 | NV5    | NV4    | NV3   | NV2    | SEC1  | SEC0  |

| FSEC                             | W      |        |        |        |        |       |        |       |       |

| 0x0002                           | R      | 0      | 0      | 0      | 0      | 0     | 0      | 0     | 0     |

| RESERVED1                        | W      |        |        |        |        |       |        |       |       |

| 0x0003                           | R      | CBEIE  | CCIE   | KEYACC | 0      | 0     | 0      | 0     | 0     |

| FCNFG                            | W      |        | 00.1   |        |        |       |        |       |       |

| 0x0004<br>FPROT                  | R<br>W | FPOPEN | NV6    | FPHDIS | FPHS1  | FPHS0 | FPLDIS | FPLS1 | FPLS0 |

| 0x0005                           | R      | CBEIF  | CCIF   | PVIOL  | ACCERR | 0     | BLANK  | FAIL  | DONE  |

| FSTAT                            | W      |        |        | 1 1102 |        |       |        |       |       |

| 0x0006<br>FCMD                   | R      | 0      | CMDB6  | CMDB5  | 0      | 0     | CMDB2  | 0     | CMDB0 |

| 0x0007                           | W<br>R | 0      | 0      | 0      | 0      | 0     | 0      | 0     | 0     |

| RESERVED2 <sup>1</sup>           | w      | U      | U      | U      | U      | U     | U      | U     | U     |

| 0x0008                           | R      |        |        |        |        | DI II |        |       |       |

| FADDRHI <sup>1</sup>             | W      |        |        |        | FAI    | ЗНІ   |        |       |       |

| 0x0009<br>FADDRLO <sup>1</sup>   | R<br>W |        |        |        | FAE    | BLO   |        |       |       |

| 0x000A                           | R      |        |        |        |        |       |        |       |       |

| FDATAHI <sup>1</sup>             | W      |        |        |        | FD     | )HI   |        |       |       |

| 0x000B                           | R      |        |        |        | FD     | LO    |        |       |       |

| FDATALO <sup>1</sup>             | W<br>R | 0      | 0      | 0      | 0      | 0     | 0      | 0     | 0     |

| 0x000C<br>RESERVED3 <sup>1</sup> | W      | U      | U      | U      | U      | U     | U      | U     | U     |

| 0x000D                           | R      | 0      | 0      | 0      | 0      | 0     | 0      | 0     | 0     |

| RESERVED4 <sup>1</sup>           | W      | ·      |        |        |        |       |        |       |       |

| 0x000E                           | R      | 0      | 0      | 0      | 0      | 0     | 0      | 0     | 0     |

| RESERVED5 <sup>1</sup>           | W      |        |        |        |        |       |        |       |       |

| 0x000F                           | R      | 0      | 0      | 0      | 0      | 0     | 0      | 0     | 0     |

| RESERVED61                       | W      |        |        |        |        |       |        |       |       |

<sup>=</sup> Unimplemented or Reserved

Figure 20-5. Flash Register Summary

<sup>1.</sup> Intended for factory test purposes only.

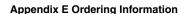

# **Appendix E Ordering Information**

Figure E-1. Order Part number Coding

Table E-1. lists C-family part number coding based on package, speed and temperature and die options.

Table E-2. lists CG-family part number coding based on package, speed and temperature and die options.

Table E-1. MC9S12C-Family / MC9S12GC-Family Part Number Coding

| Part Number   | Mask <sup>(1)</sup><br>set | Temp.        | Package | Speed | Die Type | Flash | RAM | I/O <sup>(2)</sup> , |

|---------------|----------------------------|--------------|---------|-------|----------|-------|-----|----------------------|

| MC9S12C128CFA | XL09S/0M66G                | -40°C, 85°C  | 48LQFP  | 25MHz | C128 die | 128K  | 4K  | 31                   |

| MC9S12C128CPB | XL09S/0M66G                | -40°C, 85°C  | 52LQFP  | 25MHz | C128 die | 128K  | 4K  | 35                   |

| MC9S12C128CFU | XL09S/0M66G                | -40°C, 85°C  | 80QFP   | 25MHz | C128 die | 128K  | 4K  | 60                   |

| MC9S12C128VFA | XL09S/0M66G                | -40°C,105°C  | 48LQFP  | 25MHz | C128 die | 128K  | 4K  | 31                   |

| MC9S12C128VPB | XL09S/0M66G                | -40°C,105°C  | 52LQFP  | 25MHz | C128 die | 128K  | 4K  | 35                   |

| MC9S12C128VFU | XL09S/0M66G                | -40°C, 105°C | 80QFP   | 25MHz | C128 die | 128K  | 4K  | 60                   |

| MC9S12C128MFA | XL09S/0M66G                | -40°C,125°C  | 48LQFP  | 25MHz | C128 die | 128K  | 4K  | 31                   |

| MC9S12C128MPB | XL09S/0M66G                | -40°C,125°C  | 52LQFP  | 25MHz | C128 die | 128K  | 4K  | 35                   |

| MC9S12C128MFU | XL09S/0M66G                | -40°C, 125°C | 80QFP   | 25MHz | C128 die | 128K  | 4K  | 60                   |

| MC9S12C96CFA  | XL09S/0M66G                | -40°C, 85°C  | 48LQFP  | 25MHz | C128 die | 96K   | 4K  | 31                   |

| MC9S12C96CPB  | XL09S/0M66G                | -40°C, 85°C  | 52LQFP  | 25MHz | C128 die | 96K   | 4K  | 35                   |

| MC9S12C96CFU  | XL09S/0M66G                | -40°C, 85°C  | 80QFP   | 25MHz | C128 die | 96K   | 4K  | 60                   |

| MC9S12C96VFA  | XL09S/0M66G                | -40°C,105°C  | 48LQFP  | 25MHz | C128 die | 96K   | 4K  | 31                   |

| MC9S12C96VPB  | XL09S/0M66G                | -40°C,105°C  | 52LQFP  | 25MHz | C128 die | 96K   | 4K  | 35                   |

| MC9S12C96VFU  | XL09S/0M66G                | -40°C, 105°C | 80QFP   | 25MHz | C128 die | 96K   | 4K  | 60                   |

| MC9S12C96MFA  | XL09S/0M66G                | -40°C,125°C  | 48LQFP  | 25MHz | C128 die | 96K   | 4K  | 31                   |

| MC9S12C96MPB  | XL09S/0M66G                | -40°C,125°C  | 52LQFP  | 25MHz | C128 die | 96K   | 4K  | 35                   |

| MC9S12C96MFU  | XL09S/0M66G                | -40°C, 125°C | 80QFP   | 25MHz | C128 die | 96K   | 4K  | 60                   |

| MC9S12C64CFA  | XL09S/0M66G                | -40°C, 85°C  | 48LQFP  | 25MHz | C128 die | 64K   | 4K  | 31                   |

| MC9S12C64CPB  | XL09S/0M66G                | -40°C, 85°C  | 52LQFP  | 25MHz | C128 die | 64K   | 4K  | 35                   |