Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | HCS12                                                       |

| Core Size                  | 16-Bit                                                      |

| Speed                      | 25MHz                                                       |

| Connectivity               | EBI/EMI, SCI, SPI                                           |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 60                                                          |

| Program Memory Size        | 16KB (16K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.5V                                                |

| Data Converters            | A/D 8x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 80-QFP                                                      |

| Supplier Device Package    | 80-QFP (14x14)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12gc16cfue |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Chapter 1 MC9S12C and MC9S12GC Device Overview (MC9S12C128)

| Address | Name     |                 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

| 0x0048  | TCTL1    | Read:<br>Write: | OM7    | OL7   | OM6   | OL6   | OM5   | OL5   | OM4   | OL4   |

| 0x0049  | TCTL2    | Read:<br>Write: | OM3    | OL3   | OM2   | OL2   | OM1   | OL1   | OM0   | OL0   |

| 0x004A  | TCTL3    | Read:<br>Write: | EDG7B  | EDG7A | EDG6B | EDG6A | EDG5B | EDG5A | EDG4B | EDG4A |

| 0x004B  | TCTL4    | Read:<br>Write: | EDG3B  | EDG3A | EDG2B | EDG2A | EDG1B | EDG1A | EDG0B | EDG0A |

| 0x004C  | TIE      | Read:<br>Write: | C7I    | C6I   | C5I   | C4I   | C3I   | C2I   | C1I   | COI   |

| 0x004D  | TSCR2    | Read:<br>Write: | ΤΟΙ    | 0     | 0     | 0     | TCRE  | PR2   | PR1   | PR0   |

| 0x004E  | TFLG1    | Read:<br>Write: | C7F    | C6F   | C5F   | C4F   | C3F   | C2F   | C1F   | C0F   |

| 0x004F  | TFLG2    | Read:<br>Write: | TOF    | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0050  | TC0 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x0051  | TC0 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0052  | TC1 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x0053  | TC1 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0054  | TC2 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x0055  | TC2 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0056  | TC3 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x0057  | TC3 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0058  | TC4 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x0059  | TC4 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x005A  | TC5 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x005B  | TC5 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x005C  | TC6 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x005D  | TC6 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x005E  | TC7 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

Chapter 2 Port Integration Module (PIM9C32) Block Description

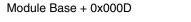

### 2.3.2.2.6 Port S Polarity Select Register (PPSS)

#### Figure 2-15. Port S Polarity Select Register (PPSS)

### Read: Anytime.

Write: Anytime.

#### Table 2-14. PPSS Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3–0<br>PPSS[3:0] | <ul> <li>Pull Select Port S — This register selects whether a pull-down or a pull-up device is connected to the pin.</li> <li>A pull-up device is connected to the associated port S pin, if enabled by the associated bit in register PERS and if the port is used as input or as wired-or output.</li> <li>A pull-down device is connected to the associated port S pin, if enabled by the associated bit in register PERS and if the port is used as input or as wired-or output.</li> <li>A pull-down device is connected to the associated port S pin, if enabled by the associated bit in register PERS and if the port is used as input.</li> </ul> |

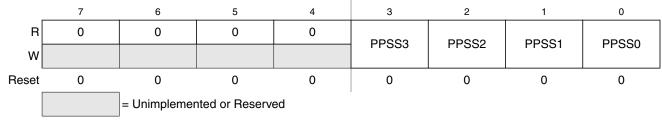

### 2.3.2.2.7 Port S Wired-OR Mode Register (WOMS)

Module Base + 0x000E

#### Figure 2-16. Port S Wired-Or Mode Register (WOMS)

Read: Anytime.

Write: Anytime.

#### Table 2-15. WOMS Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Wired-OR Mode Port S — This register configures the output pins as wired-or. If enabled the output is driven active low only (open-drain). A logic level of "1" is not driven. This bit has no influence on pins used as inputs.</li> <li>Output buffers operate as push-pull outputs.</li> <li>1 Output buffers operate as open-drain outputs.</li> </ul> |

Chapter 3 Module Mapping Control (MMCV4) Block Description

| Address<br>Offset | Register                              | Access |

|-------------------|---------------------------------------|--------|

| 0x0017            | Reserved                              | —      |

|                   | · · · · · · · · · · · · · · · · · · · | —      |

| 0x001C            | Memory Size Register 0 (MEMSIZ0)      | R      |

| 0x001D            | Memory Size Register 1 (MEMSIZ1)      | R      |

|                   | · · · · · · · · · · · · · · · · · · · |        |

| 0x0030            | Program Page Index Register (PPAGE)   | R/W    |

| 0x0031            | Reserved                              | —      |

### Table 3-1. MMC Memory Map (continued)

Chapter 3 Module Mapping Control (MMCV4) Block Description

vector spaces, expansion windows, and on-chip memory are mapped so that their address ranges do not overlap. The MMC will make only one select signal active at any given time. This activation is based upon the priority outlined in Table 3-15. If two or more blocks share the same address space, only the select signal for the block with the highest priority will become active. An example of this is if the registers and the RAM are mapped to the same space, the registers will have priority over the RAM and the portion of RAM mapped in this shared space will not be accessible. The expansion windows have the lowest priority. This means that registers, vectors, and on-chip memory are always visible to a program regardless of the values in the page select registers.

| Priority | Address Space                                     |

|----------|---------------------------------------------------|

| Highest  | BDM (internal to core) firmware or register space |

|          | Internal register space                           |

|          | RAM memory block                                  |

|          | EEPROM memory block                               |

|          | On-chip FLASH or ROM                              |

| Lowest   | Remaining external space                          |

Table 3-15. Select Signal Priority

In expanded modes, all address space not used by internal resources is by default external memory space. The data registers and data direction registers for ports A and B are removed from the on-chip memory map and become external accesses. If the EME bit in the MODE register (see MEBI block description chapter) is set, the data and data direction registers for port E are also removed from the on-chip memory map and become external accesses.

In special peripheral mode, the first 16 registers associated with bus expansion are removed from the onchip memory map (PORTA, PORTB, DDRA, DDRB, PORTE, DDRE, PEAR, MODE, PUCR, RDRIV, and the EBI reserved registers).

In emulation modes, if the EMK bit in the MODE register (see MEBI block description chapter) is set, the data and data direction registers for port K are removed from the on-chip memory map and become external accesses.

### 3.4.2.2 Emulation Chip Select Signal

When the EMK bit in the MODE register (see MEBI block description chapter) is set, port K bit 7 is used as an active-low emulation chip select signal,  $\overline{\text{ECS}}$ . This signal is active when the system is in emulation mode, the EMK bit is set and the FLASH or ROM space is being addressed subject to the conditions outlined in Section 3.4.3.2, "Extended Address (XAB19:14) and ECS Signal Functionality." When the EMK bit is clear, this pin is used for general purpose I/O.

## 3.4.2.3 External Chip Select Signal

When the EMK bit in the MODE register (see MEBI block description chapter) is set, port K bit 6 is used as an active-low external chip select signal,  $\overline{XCS}$ . This signal is active only when the  $\overline{ECS}$  signal described above is not active and when the system is addressing the external address space. Accesses to

#### Table 5-2. ITCR Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>WRTINT     | <ul> <li>Write to the Interrupt Test Registers</li> <li>Read: anytime</li> <li>Write: only in special modes and with I-bit mask and X-bit mask set.</li> <li>0 Disables writes to the test registers; reads of the test registers will return the state of the interrupt inputs.</li> <li>1 Disconnect the interrupt inputs from the priority decoder and use the values written into the ITEST registers instead.</li> <li>Note: Any interrupts which are pending at the time that WRTINT is set will remain until they are overwritten.</li> </ul> |

| 3:0<br>ADR[3:0] | Test Register Select Bits         Read: anytime         Write: anytime         These bits determine which test register is selected on a read or write. The hexadecimal value written here will         be the same as the upper nibble of the lower byte of the vector selects. That is, an "F" written into ADR[3:0] will         select vectors 0xFFFE–0xFFF0 while a "7" written to ADR[3:0] will select vectors 0xFF7E–0xFF70.                                                                                                                  |

### 5.3.2.2 Interrupt Test Registers

Module Base + 0x0016

Starting address location affected by INITRG register setting.

|        | 7                           | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|--------|-----------------------------|------|------|------|------|------|------|------|--|

| R<br>W | INTE                        | INTC | INTA | INT8 | INT6 | INT4 | INT2 | INTO |  |

| Reset  | 0                           | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |

|        | = Unimplemented or Reserved |      |      |      |      |      |      |      |  |

#### Figure 5-3. Interrupt TEST Registers (ITEST)

Read: Only in special modes. Reads will return either the state of the interrupt inputs of the interrupt subblock (WRTINT = 0) or the values written into the TEST registers (WRTINT = 1). Reads will always return 0s in normal modes.

Write: Only in special modes and with WRTINT = 1 and CCR I mask = 1.

## 6.4.9 SYNC — Request Timed Reference Pulse

The SYNC command is unlike other BDM commands because the host does not necessarily know the correct communication speed to use for BDM communications until after it has analyzed the response to the SYNC command. To issue a SYNC command, the host should perform the following steps:

- 1. Drive the BKGD pin low for at least 128 cycles at the lowest possible BDM serial communication frequency (the lowest serial communication frequency is determined by the crystal oscillator or the clock chosen by CLKSW.)

- 2. Drive BKGD high for a brief speedup pulse to get a fast rise time (this speedup pulse is typically one cycle of the host clock.)

- 3. Remove all drive to the BKGD pin so it reverts to high impedance.

- 4. Listen to the BKGD pin for the sync response pulse.

Upon detecting the SYNC request from the host, the target performs the following steps:

- 1. Discards any incomplete command received or bit retrieved.

- 2. Waits for BKGD to return to a logic 1.

- 3. Delays 16 cycles to allow the host to stop driving the high speedup pulse.

- 4. Drives BKGD low for 128 cycles at the current BDM serial communication frequency.

- 5. Drives a one-cycle high speedup pulse to force a fast rise time on BKGD.

- 6. Removes all drive to the BKGD pin so it reverts to high impedance.

The host measures the low time of this 128 cycle SYNC response pulse and determines the correct speed for subsequent BDM communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

As soon as the SYNC request is detected by the target, any partially received command or bit retrieved is discarded. This is referred to as a soft-reset, equivalent to a time-out in the serial communication. After the SYNC response, the target will consider the next falling edge (issued by the host) as the start of a new BDM command or the start of new SYNC request.

Another use of the SYNC command pulse is to abort a pending ACK pulse. The behavior is exactly the same as in a regular SYNC command. Note that one of the possible causes for a command to not be acknowledged by the target is a host-target synchronization problem. In this case, the command may not have been understood by the target and so an ACK response pulse will not be issued.

## 6.4.10 Instruction Tracing

When a TRACE1 command is issued to the BDM in active BDM, the CPU exits the standard BDM firmware and executes a single instruction in the user code. As soon as this has occurred, the CPU is forced to return to the standard BDM firmware and the BDM is active and ready to receive a new command. If the TRACE1 command is issued again, the next user instruction will be executed. This facilitates stepping or tracing through the user code one instruction at a time.

- Data associated with event B trigger modes

- Detail report mode stores address and data for all cycles except program (P) and free (f) cycles

- Current instruction address when in profiling mode

- BGND is not considered a change-of-flow (cof) by the debugger

### 7.1.2 Modes of Operation

There are two main modes of operation: breakpoint mode and debug mode. Each one is mutually exclusive of the other and selected via a software programmable control bit.

In the breakpoint mode there are two sub-modes of operation:

- Dual address mode, where a match on either of two addresses will cause the system to enter background debug mode (BDM) or initiate a software interrupt (SWI).

- Full breakpoint mode, where a match on address and data will cause the system to enter background debug mode (BDM) or initiate a software interrupt (SWI).

In debug mode, there are several sub-modes of operation.

• Trigger modes

There are many ways to create a logical trigger. The trigger can be used to capture bus information either starting from the trigger or ending at the trigger. Types of triggers (A and B are registers):

- A only

- A or B

- A then B

- Event only B (data capture)

- A then event only B (data capture)

- A and B, full mode

- A and not B, full mode

- Inside range

- Outside range

- Capture modes

There are several capture modes. These determine which bus information is saved and which is ignored.

- Normal: save change-of-flow program fetches

- Loop1: save change-of-flow program fetches, ignoring duplicates

- Detail: save all bus operations except program and free cycles

- Profile: poll target from external device

### 7.1.3 Block Diagram

Figure 7-1 is a block diagram of this module in breakpoint mode. Figure 7-2 is a block diagram of this module in debug mode.

## 9.1.2 Modes of Operation

This subsection lists and briefly describes all operating modes supported by the CRG.

• Run mode

All functional parts of the CRG are running during normal run mode. If RTI or COP functionality is required the individual bits of the associated rate select registers (COPCTL, RTICTL) have to be set to a nonzero value.

• Wait mode

This mode allows to disable the system and core clocks depending on the configuration of the individual bits in the CLKSEL register.

• Stop mode

Depending on the setting of the PSTP bit, stop mode can be differentiated between full stop mode (PSTP = 0) and pseudo-stop mode (PSTP = 1).

— Full stop mode

The oscillator is disabled and thus all system and core clocks are stopped. The COP and the RTI remain frozen.

Pseudo-stop mode

The oscillator continues to run and most of the system and core clocks are stopped. If the respective enable bits are set the COP and RTI will continue to run, else they remain frozen.

• Self-clock mode

Self-clock mode will be entered if the clock monitor enable bit (CME) and the self-clock mode enable bit (SCME) are both asserted and the clock monitor in the oscillator block detects a loss of clock. As soon as self-clock mode is entered the CRGV4 starts to perform a clock quality check. Self-clock mode remains active until the clock quality check indicates that the required quality of the incoming clock signal is met (frequency and amplitude). Self-clock mode should be used for safety purposes only. It provides reduced functionality to the MCU in case a loss of clock is causing severe system conditions.

## 9.1.3 Block Diagram

Figure 9-1 shows a block diagram of the CRGV4.

#### Chapter 9 Clocks and Reset Generator (CRGV4) Block Description

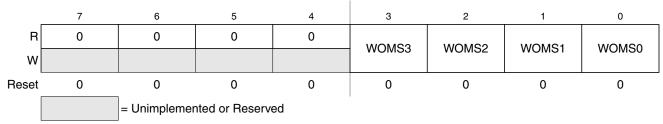

The internal reset of the MCU remains asserted while the reset generator completes the 192 SYSCLK long reset sequence. The reset generator circuitry always makes sure the internal reset is deasserted synchronously after completion of the 192 SYSCLK cycles. In case the RESET pin is externally driven low for more than these 192 SYSCLK cycles (external reset), the internal reset remains asserted too.

### 9.5.1 Clock Monitor Reset

The CRGV4 generates a clock monitor reset in case all of the following conditions are true:

- Clock monitor is enabled (CME=1)

- Loss of clock is detected

- Self-clock mode is disabled (SCME=0)

The reset event asynchronously forces the configuration registers to their default settings (see Section 9.3, "Memory Map and Register Definition"). In detail the CME and the SCME are reset to logical '1' (which doesn't change the state of the CME bit, because it has already been set). As a consequence, the CRG immediately enters self-clock mode and starts its internal reset sequence. In parallel the clock quality check starts. As soon as clock quality check indicates a valid oscillator clock the CRG switches to OSCCLK and leaves self-clock mode. Because the clock quality checker is running in parallel to the reset generator, the CRG may leave self-clock mode while completing the internal reset sequence. When the reset sequence is finished the CRG checks the internally latched state of the clock monitor fail circuit. If a clock monitor fail is indicated processing begins by fetching the clock monitor reset vector.

## 9.5.2 Computer Operating Properly Watchdog (COP) Reset

When COP is enabled, the CRG expects sequential write of 0x0055 and 0x00AA (in this order) to the ARMCOP register during the selected time-out period. As soon as this is done, the COP time-out period restarts. If the program fails to do this the CRG will generate a reset. Also, if any value other than 0x0055 or 0x00AA is written, the CRG immediately generates a reset. In case windowed COP operation is enabled

## 10.3.2.16 MSCAN Identifier Acceptance Registers (CANIDAR0-7)

On reception, each message is written into the background receive buffer. The CPU is only signalled to read the message if it passes the criteria in the identifier acceptance and identifier mask registers (accepted); otherwise, the message is overwritten by the next message (dropped).

The acceptance registers of the MSCAN are applied on the IDR0–IDR3 registers (see Section 10.3.3.1, "Identifier Registers (IDR0–IDR3)") of incoming messages in a bit by bit manner (see Section 10.4.3, "Identifier Acceptance Filter").

For extended identifiers, all four acceptance and mask registers are applied. For standard identifiers, only the first two (CANIDAR0/1, CANIDMR0/1) are applied.

| Module Base + 0x0010 (CANIDAR0)<br>0x0011 (CANIDAR1)<br>0x0012 (CANIDAR2)<br>0x0013 (CANIDAR3) |     |     |     |     |     |     |     |     |

|------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| _                                                                                              | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| R<br>W                                                                                         | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset                                                                                          | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| r                                                                                              | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| R<br>W                                                                                         | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset                                                                                          | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| F                                                                                              | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| R<br>W                                                                                         | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset                                                                                          | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| F                                                                                              | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| R<br>W                                                                                         | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset                                                                                          | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Figure 10-19. MSCAN Identifier Acceptance Registers (First Bank) — CANIDAR0–CANIDAR3

Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 10-19. CANIDAR0–CANIDAR3 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>AC[7:0] | Acceptance Code Bits — AC[7:0] comprise a user-defined sequence of bits with which the corresponding bits of the related identifier register (IDRn) of the receive message buffer are compared. The result of this comparison is then masked with the corresponding identifier mask register. |

### NOTE

Reads of this register return the most recent value written. Reads do not necessarily return the value of the currently active duty due to the double buffering scheme.

Reference Section 12.4.2.3, "PWM Period and Duty," for more information.

### NOTE

Depending on the polarity bit, the duty registers will contain the count of either the high time or the low time. If the polarity bit is 1, the output starts high and then goes low when the duty count is reached, so the duty registers contain a count of the high time. If the polarity bit is 0, the output starts low and then goes high when the duty count is reached, so the duty registers contain a count of the low time.

To calculate the output duty cycle (high time as a % of period) for a particular channel:

- Polarity = 0 (PPOLx = 0) Duty cycle = [(PWMPERx PWMDTYx)/PWMPERx] \* 100%

- Polarity = 1 (PPOLx = 1) Duty cycle = [PWMDTYx / PWMPERx] \* 100%

- For boundary case programming values, please refer to Section 12.4.2.8, "PWM Boundary Cases."

Module Base + 0x0018

Figure 12-27. PWM Channel Duty Registers (PWMDTY0)

Module Base + 0x0019

| _      | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-------|---|---|---|---|---|---|-------|

| R<br>W | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Reset  | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1     |

#### Figure 12-28. PWM Channel Duty Registers (PWMDTY1)

Module Base + 0x001A

|        | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-------|---|---|---|---|---|---|-------|

| R<br>W | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Reset  | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1     |

Figure 12-29. PWM Channel Duty Registers (PWMDTY2)

Chapter 13 Serial Communications Interface (S12SCIV2) Block Description

# 13.3 Memory Map and Registers

This section provides a detailed description of all memory and registers.

### 13.3.1 Module Memory Map

The memory map for the SCI module is given below in Figure 13-2. The Address listed for each register is the address offset. The total address for each register is the sum of the base address for the SCI module and the address offset for each register.

| Address | Name    |   | Bit 7       | 6          | 5           | 4       | 3     | 2      | 1     | Bit 0 |     |

|---------|---------|---|-------------|------------|-------------|---------|-------|--------|-------|-------|-----|

| 0x0000  | SCIBDH  | R | 0           | 0          | 0           | SBR12   | SBR11 | SBR10  | SBR9  | SBR8  |     |

| 0,0000  | COLDEN  | W |             |            |             | ODITIZ  | OBITT | OBITIO | OBIIO | ODITO |     |

| 0x0001  | SCIBDL  | R | SBR7        | SBR6       | SBR5        | SBR4    | SBR3  | SBR2   | SBR1  | SBR0  |     |

|         |         | W |             |            |             |         |       |        |       |       |     |

| 0x0002  | SCICR1  | R | LOOPS       | SCISWAI    | RSRC        | М       | WAKE  | ILT    | PE    | PT    |     |

|         |         | W |             |            |             |         |       |        |       |       |     |

| 0x0003  | SCICR2  | R | TIE         | TCIE       | RIE         | ILIE    | TE    | RE     | RWU   | SBK   |     |

|         |         | W |             |            |             |         |       |        |       |       |     |

| 0x0004  | SCISR1  | R | TDRE        | TC         | RDRF        | IDLE    | OR    | NF     | FE    | PF    |     |

| 0,0001  | 0010111 | W |             |            |             |         |       |        |       |       |     |

| 0x0005  | SCISR2  | R | 0           | 0          | 0           | 0       | 0     |        | BRK13 | TXDIR | RAF |

| 0x0005  | 301302  | w |             |            |             |         |       | DUVIS  | IADIN |       |     |

| 0x0006  | F F     |   | SCIDRH R R8 | R8         | Т8          | 0       | 0     | 0      | 0     | 0     | 0   |

| 00000   | SCIDRIT | w |             |            |             |         |       |        |       |       |     |

| 0x0007  | SCIDRL  | R | R7          | R6         | R5          | R4      | R3    | R2     | R1    | R0    |     |

| 00007   | SCIDEL  | w | T7          | T6         | T5          | T4      | T3    | T2     | T1    | Т0    |     |

|         |         | [ |             | = Unimplen | nented or R | eserved |       |        |       |       |     |

Figure 13-2. SCI Register Summary

## 13.3.2 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Writes to a reserved register location do not have any effect and reads of these locations return a zero. Details of register bit and field function follow the register diagrams, in bit order.

### Table 13-5. SCISR1 Field Descriptions (continued)

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 5<br>RDRF | <ul> <li>Receive Data Register Full Flag — RDRF is set when the data in the receive shift register transfers to the SCI data register. Clear RDRF by reading SCI status register 1 (SCISR1) with RDRF set and then reading SCI data register low (SCIDRL).</li> <li>0 Data not available in SCI data register</li> <li>1 Received data available in SCI data register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 4<br>IDLE | Idle Line Flag — IDLE is set when 10 consecutive logic 1s (if M=0) or 11 consecutive logic 1s (if M=1) appear on the receiver input. Once the IDLE flag is cleared, a valid frame must again set the RDRF flag before an idle condition can set the IDLE flag.Clear IDLE by reading SCI status register 1 (SCISR1) with IDLE set and then reading SCI data register low (SCIDRL).         0       Receiver input is either active now or has never become active since the IDLE flag was last cleared         1       Receiver input has become idle         Note: When the receiver wakeup bit (RWU) is set, an idle line condition does not set the IDLE flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 3<br>OR   | <ul> <li>Overrun Flag — OR is set when software fails to read the SCI data register before the receive shift register receives the next frame. The OR bit is set immediately after the stop bit has been completely received for the second frame. The data in the shift register is lost, but the data already in the SCI data registers is not affected. Clear OR by reading SCI status register 1 (SCISR1) with OR set and then reading SCI data register low (SCIDRL).</li> <li>0 No overrun</li> <li>1 Overrun</li> <li>Note: OR flag may read back as set when RDRF flag is clear. This may happen if the following sequence of events occurs:</li> <li>1. After the first frame is received, read status register SCISR1 (returns RDRF set and OR flag clear);</li> <li>2. Receive second frame without reading the first frame in the data register (the second frame is not received and OR flag is set);</li> <li>3. Read data register SCIDRL (returns RDRF clear and OR set).</li> <li>Event 3 may be at exactly the same time as event 2 or any time after. When this happens, a dummy SCIDRL read following event 4 will be required to clear the OR flag if further frames are to be received.</li> </ul> |  |  |  |  |  |  |  |

| 2<br>NF   | <ul> <li>Noise Flag — NF is set when the SCI detects noise on the receiver input. NF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear NF by reading SCI status register 1(SCISR1), and then reading SCI data register low (SCIDRL).</li> <li>0 No noise</li> <li>1 Noise</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| 1<br>FE   | <ul> <li>Framing Error Flag — FE is set when a logic 0 is accepted as the stop bit. FE bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. FE inhibits further data reception until it is cleared. Clear FE by reading SCI status register 1 (SCISR1) with FE set and then reading the SCI data register low (SCIDRL).</li> <li>0 No framing error</li> <li>1 Framing error</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 0<br>PF   | <ul> <li>Parity Error Flag — PF is set when the parity enable bit (PE) is set and the parity of the received data does not match the parity type bit (PT). PF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear PF by reading SCI status register 1 (SCISR1), and then reading SCI data register low (SCIDRL).</li> <li>0 No parity error</li> <li>1 Parity error</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

# Chapter 15 Timer Module (TIM16B8CV1) Block Description

| Version<br>Number | Revision Dates | Effective<br>Date | Author                                                                                | Description of Changes                                                                                                               |

|-------------------|----------------|-------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 01.03             | 06 Feb 2006    | 06 Feb 2006       | S. Chinnam                                                                            | Corrected the type at 0x006 and later in the document from TSCR2 and TSCR1                                                           |

| 01.04             | 08 July 2008   | 08 July 2008      | 8 July 2008 S. Chinnam Revised flag clearing procedure, when set when clearing flags. |                                                                                                                                      |

| 01.05             | 05 May 2010    | 05 May 2010       | Ame Wang                                                                              | -in 15.3.2.8/15-446,add Table 15-11<br>-in 15.3.2.11/15-450,TCRE bit description part,add Note<br>-in 15.4.3/15-459,add Figure 15-29 |

Table 15-1. Revision History

## 15.1 Introduction

The basic timer consists of a 16-bit, software-programmable counter driven by a seven-stage programmable prescaler.

This timer can be used for many purposes, including input waveform measurements while simultaneously generating an output waveform. Pulse widths can vary from microseconds to many seconds.

This timer contains 8 complete input capture/output compare channels and one pulse accumulator. The input capture function is used to detect a selected transition edge and record the time. The output compare function is used for generating output signals or for timer software delays. The 16-bit pulse accumulator is used to operate as a simple event counter or a gated time accumulator. The pulse accumulator shares timer channel 7 when in event mode.

A full access for the counter registers or the input capture/output compare registers should take place in one clock cycle. Accessing high byte and low byte separately for all of these registers may not yield the same result as accessing them in one word.

## 15.1.1 Features

The TIM16B8CV1 includes these distinctive features:

- Eight input capture/output compare channels.

- Clock prescaling.

- 16-bit counter.

- 16-bit pulse accumulator.

Chapter 18 32 Kbyte Flash Module (S12FTS32KV1)

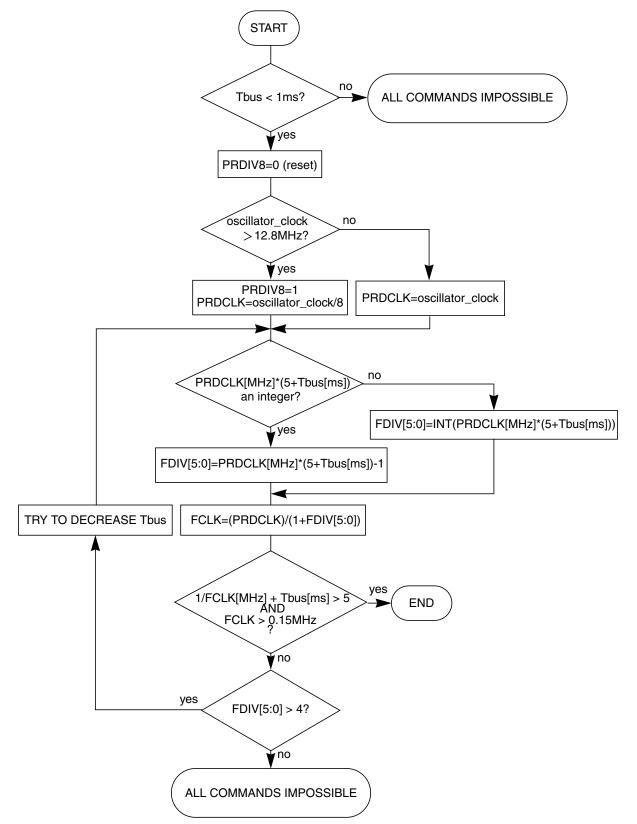

Figure 18-21. PRDIV8 and FDIV Bits Determination Procedure

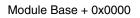

## 19.3.2.1 Flash Clock Divider Register (FCLKDIV)

The FCLKDIV register is used to control timed events in program and erase algorithms.

### Figure 19-6. Flash Clock Divider Register (FCLKDIV)

All bits in the FCLKDIV register are readable, bits 6–0 are write once and bit 7 is not writable.

#### Table 19-4. FCLKDIV Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FDIVLD      | Clock Divider Loaded         0       FCLKDIV register has not been written         1       FCLKDIV register has been written to since the last reset                                                                                                            |

| 6<br>PRDIV8      | <ul> <li>Enable Prescalar by 8</li> <li>0 The oscillator clock is directly fed into the Flash clock divider</li> <li>1 The oscillator clock is divided by 8 before feeding into the Flash clock divider</li> </ul>                                              |

| 5–0<br>FDIV[5:0] | <b>Clock Divider Bits</b> — The combination of PRDIV8 and FDIV[5:0] must divide the oscillator clock down to a frequency of 150 kHz – 200 kHz. The maximum divide ratio is 512. Refer to Section 19.4.1.1, "Writing the FCLKDIV Register" for more information. |

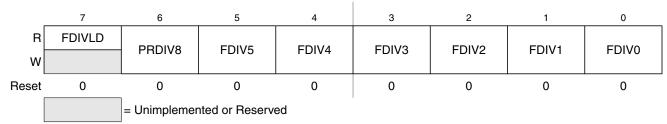

### 19.3.2.2 Flash Security Register (FSEC)

The FSEC register holds all bits associated with the security of the MCU and Flash module.

Module Base + 0x0001

### Figure 19-7. Flash Security Register (FSEC)

All bits in the FSEC register are readable but not writable.

The FSEC register is loaded from the Flash configuration field at 0xFF0F during the reset sequence, indicated by F in Figure 19-7.

Chapter 19 64 Kbyte Flash Module (S12FTS64KV4)

| From<br>Protection | To Protection Scenario <sup>(1)</sup> |   |   |   |   |   |   |   |

|--------------------|---------------------------------------|---|---|---|---|---|---|---|

| Scenario           | 0                                     | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 6                  |                                       | Х |   | Х | Х |   | Х |   |

| 7                  | х                                     | Х | Х | Х | Х | Х | Х | Х |

Table 19-13. Flash Protection Scenario Transitions

1. Allowed transitions marked with X.

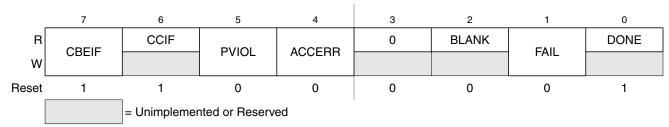

### 19.3.2.6 Flash Status Register (FSTAT)

The FSTAT register defines the status of the Flash command controller and the results of command execution.

Module Base + 0x0005

Figure 19-12. Flash Status Register (FSTAT)

In normal modes, bits CBEIF, PVIOL, and ACCERR are readable and writable, bits CCIF and BLANK are readable and not writable, remaining bits, including FAIL and DONE, read 0 and are not writable. In special modes, FAIL is readable and writable while DONE is readable but not writable. FAIL must be clear in special modes when starting a command write sequence.

Table 19-14. FSTAT Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7<br>CBEIF | <ul> <li>Command Buffer Empty Interrupt Flag — The CBEIF flag indicates that the address, data and command buffers are empty so that a new command write sequence can be started. The CBEIF flag is cleared by writing a 1 to CBEIF. Writing a 0 to the CBEIF flag has no effect on CBEIF. Writing a 0 to CBEIF after writing an aligned word to the Flash address space but before CBEIF is cleared will abort a command write sequence and cause the ACCERR flag in the FSTAT register to be set. Writing a 0 to CBEIF outside of a command write sequence will not set the ACCERR flag. The CBEIF flag is used together with the CBEIE bit in the FCNFG register to generate an interrupt request (see Figure 19-29).</li> <li>0 Buffers are full</li> <li>1 Buffers are ready to accept a new command</li> </ul> |  |  |  |  |  |  |

| 6<br>CCIF  | <ul> <li>Command Complete Interrupt Flag — The CCIF flag indicates that there are no more commands pending. The CCIF flag is cleared when CBEIF is clear and sets automatically upon completion of all active and pending commands. The CCIF flag does not set when an active commands completes and a pending command is fetched from the command buffer. Writing to the CCIF flag has no effect. The CCIF flag is used together with the CCIE bit in the FCNFG register to generate an interrupt request (see Figure 19-29).</li> <li>0 Command in progress</li> <li>1 All commands are completed</li> </ul>                                                                                                                                                                                                       |  |  |  |  |  |  |

Chapter 21 128 Kbyte Flash Module (S12FTS128K1V1)

### 21.4.1.3 Valid Flash Commands

Table 21-16 summarizes the valid Flash commands along with the effects of the commands on the Flash array.

| FCMD | Meaning         | Function on Flash Array                                                                                                                                                                            |  |  |  |  |

|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0x05 | Erase<br>Verify | Verify all bytes in the Flash array are erased.<br>If the Flash array is erased, the BLANK bit will set in the FSTAT register upon command completion.                                             |  |  |  |  |

| 0x20 | Program         | Program a word (2 bytes) in the Flash array.                                                                                                                                                       |  |  |  |  |

| 0x40 | Sector<br>Erase | Erase all 1024 bytes in a sector of the Flash array.                                                                                                                                               |  |  |  |  |

| 0x41 | Mass<br>Erase   | Erase all bytes in the Flash array.<br>A mass erase of the full Flash array is only possible when FPLDIS, FPHDIS, and FPOPEN bits in<br>the FPROT register are set prior to launching the command. |  |  |  |  |

#### Table 21-16. Valid Flash Commands

### CAUTION

A Flash word must be in the erased state before being programmed. Cumulative programming of bits within a Flash word is not allowed.

### 21.4.1.3.4 Mass Erase Command

The mass erase operation will erase all addresses in a Flash array using an embedded algorithm.

An example flow to execute the mass erase operation is shown in Figure 21-25. The mass erase command write sequence is as follows:

- 1. Write to a Flash array address to start the command write sequence for the mass erase command. The address and data written will be ignored.

- 2. Write the mass erase command, 0x41, to the FCMD register.

- 3. Clear the CBEIF flag in the FSTAT register by writing a 1 to CBEIF to launch the mass erase command.

If a Flash array to be erased contains any protected area, the PVIOL flag in the FSTAT register will set and the mass erase command will not launch. Once the mass erase command has successfully launched, the CCIF flag in the FSTAT register will set after the mass erase operation has completed unless a new command write sequence has been buffered.

**Appendix A Electrical Characteristics**

# A.2 ATD Characteristics

This section describes the characteristics of the analog-to-digital converter.

$V_{RL}$  is not available as a separate pin in the 48- and 52-pin versions. In this case the internal  $V_{RL}$  pad is bonded to the  $V_{SSA}$  pin.

The ATD is specified and tested for both the 3.3V and 5V range. For ranges between 3.3V and 5V the ATD accuracy is generally the same as in the 3.3V range but is not tested in this range in production test.

# A.2.1 ATD Operating Characteristics In 5V Range

The Table A-10 shows conditions under which the ATD operates.

The following constraints exist to obtain full-scale, full range results:  $V_{SSA} \le V_{RL} \le V_{IN} \le V_{RH} \le V_{DDA}$ . This constraint exists since the sample buffer amplifier can not drive beyond the power supply levels that it ties to. If the input level goes outside of this range it will effectively be clipped.

| Condit | tions ar | e shown in Table A-4 unless otherwise noted. Supply V                                                             | /oltage 5V-10                              | % <= V <sub>DDA</sub> <=               | =5V+10% | <b>)</b>                               |              |

|--------|----------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------|---------|----------------------------------------|--------------|

| Num    | С        | Rating                                                                                                            | Symbol                                     | Min                                    | Тур     | Мах                                    | Unit         |

| 1      | D        | Reference Potential<br>Low<br>High                                                                                | V <sub>RL</sub><br>V <sub>RH</sub>         | V <sub>SSA</sub><br>V <sub>DDA/2</sub> |         | V <sub>DDA/2</sub><br>V <sub>DDA</sub> | V<br>V       |

| 2      | С        | Differential Reference Voltage <sup>(1)</sup>                                                                     | $V_{RH}-V_{RL}$                            | 4.75                                   | 5.0     | 5.25                                   | V            |

| 3      | D        | ATD Clock Frequency                                                                                               | f <sub>ATDCLK</sub>                        | 0.5                                    | _       | 2.0                                    | MHz          |

| 4      | D        | ATD 10-Bit Conversion Period<br>Clock Cycles <sup>(2)</sup><br>Conv, Time at 2.0MHz ATD Clock f <sub>ATDCLK</sub> | N <sub>CONV10</sub><br>T <sub>CONV10</sub> | 14<br>7                                | _       | 28<br>14                               | Cycles<br>μs |

| 5      | D        | ATD 8-Bit Conversion Period<br>Clock Cycles <sup>2</sup><br>Conv, Time at 2.0MHz ATD Clock f <sub>ATDCLK</sub>    | N <sub>CONV10</sub><br>T <sub>CONV10</sub> | 12<br>6                                | _       | 26<br>13                               | Cycles<br>μs |

| 5      | D        | Recovery Time (V <sub>DDA</sub> =5.0 Volts)                                                                       | t <sub>REC</sub>                           | _                                      | _       | 20                                     | μs           |

| 6      | Р        | Reference Supply current                                                                                          | I <sub>REF</sub>                           | _                                      | —       | 0.375                                  | mA           |

#### Table A-10. ATD Operating Characteristics

1. Full accuracy is not guaranteed when differential voltage is less than 4.75V

2. The minimum time assumes a final sample period of 2 ATD clocks cycles while the maximum time assumes a final sample period of 16 ATD clocks.